1.本发明涉及多指晶体管以及功率放大电路。

背景技术:

2.在专利文献1记载了使用了晶体管的功率放大模块。在专利文献1中,在晶体管的基极,不经由dc截止电容器而被输入交流信号。

3.在先技术文献

4.专利文献

5.专利文献1:国际公开第2015/001851号

6.在放大电路中,存在使用对多个单位晶体管(也称为指)进行了电并联连接的多指晶体管的情况。所谓单位晶体管,是指构成晶体管的最小限度的结构。另外,本公开中的多指晶体管定义为,并联连接多个单位晶体管而作为一个晶体管电路起作用,发射极的数量有多个。

7.若多个单位晶体管的基极不经由dc截止电容器而电并联连接,则有可能发生如下情况,即,会在一个单位晶体管的基极流过较大的偏置电流。例如,存在由于单位晶体管各自的温度不同而单位晶体管各自的基极的输入阻抗(输入电阻)不同的情况。又例如,存在由于多个单位晶体管有个体差异而单位晶体管各自的基极的输入阻抗不同的情况。因此,在输入阻抗最小的单位晶体管的基极流过较大的偏置电流,其他单位晶体管的基极的偏置电流变小。由此,多个单位晶体管会不均等地进行动作。若多个单位晶体管不均等地进行动作,则无法得到期望的放大特性。

技术实现要素:

8.发明要解决的课题

9.本发明是鉴于上述情形而完成的,其目的在于,使多个单位晶体管均等地进行动作。

10.用于解决课题的手段

11.本发明的一个方面的多指晶体管包含:多个单位晶体管,具备与基准电位电连接的第1端子、被输入高频信号以及偏置电流的第2端子和输出对高频信号进行了放大的放大信号的第3端子;公共输入端子,将多个单位晶体管的第2端子电并联连接,被输入高频信号;公共偏置端子,将多个单位晶体管的第2端子电并联连接,被输入偏置电流;公共输出端子,将多个单位晶体管的第3端子电并联连接,输出放大信号;和多个第1电阻元件,分别电连接在多个单位晶体管的第2端子与公共输入端子之间,将偏置电流的直流分量截止。

12.本发明的一个方面的功率放大电路包含:平衡

‑

不平衡变压器,在初级绕组被输入第1高频信号,从次级绕组输出第2高频信号;和上述记载的多指晶体管,第2高频信号被输入至公共输入端子。

13.发明效果

14.根据本发明,能够使多个单位晶体管均等地进行动作。

附图说明

15.图1是示出比较例的多指晶体管的结构的图。

16.图2是示出第1实施方式的多指晶体管的结构的图。

17.图3是示出第2实施方式的功率放大电路的结构的图。

18.符号说明

19.1、12、13、14、15、16、101:多指晶体管;

20.2、102:单元;

21.3、103:单位晶体管;

22.4、5、104:电阻;

23.10、31、110:扼流电感器;

24.t1、t2、t3:平衡

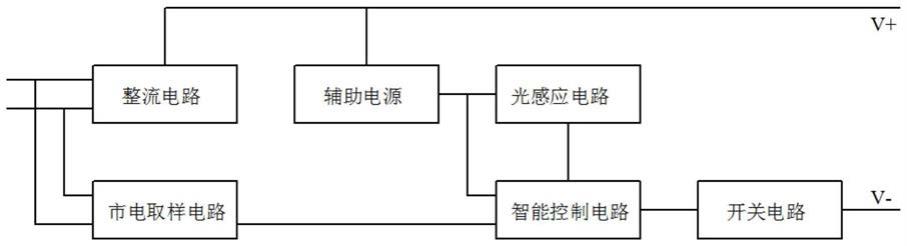

‑

不平衡变压器。

具体实施方式

25.以下,基于附图对本发明的多指晶体管以及功率放大电路的实施方式详细地进行说明。另外,本发明并不被该实施方式所限定。各实施方式是例示,能够进行在不同的实施方式中示出的结构的部分置换或组合,这是不言而喻的。在第2实施方式以后,省略关于与第1实施方式共同的事项的记述,仅对不同点进行说明。特别是,关于基于同样的结构的同样的作用效果,将不在每个实施方式中逐次提及。

26.<第1实施方式以及比较例>

27.以下,对第1实施方式进行说明,但是为了使第1实施方式容易理解,先对比较例进行说明。

28.(比较例)

29.图1是示出比较例的多指晶体管的结构的图。多指晶体管101是对多个单位晶体管进行电并联连接而成的。所谓单位晶体管,是指构成晶体管的最小限度的结构。

30.多指晶体管101具有被输入交流信号rf11的第1端子p11、被输入偏置电流bias11的第2端子p12和输出交流信号rf12的第3端子p13。第3端子p13经由扼流电感器110与电源电位vcc11电连接。

31.多指晶体管101从电源电位vcc11被供给电力,通过偏置电流bias11而被设定电偏置状态。然后,多指晶体管101对交流信号rf11进行放大,并输出放大后的交流信号rf12。

32.多指晶体管101包含n个(n为2以上的整数)单元102

‑

1~102

‑

n。单元102

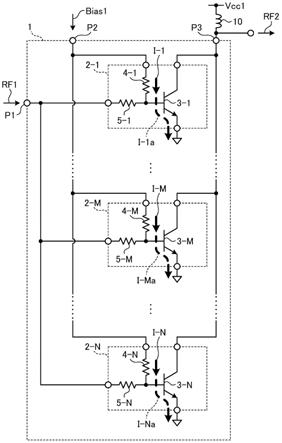

‑

1包含单位晶体管103

‑

1和电阻104

‑

1。单元102

‑

m(m为1<m<n的整数)包含单位晶体管103

‑

m和电阻104

‑

m。单元102

‑

n包含单位晶体管103

‑

n和电阻104

‑

n。作为一例,电阻104

‑

1~104

‑

n各自的电阻值设为180ω(欧姆)~200ω程度。不过,本公开不限定于此。

33.在本公开中,单位晶体管设为双极晶体管,但本公开不限定于此。双极晶体管可例示异质结双极晶体管(heterojunction bipolar transistor:hbt),但本公开不限定于此。单位晶体管例如也可以为场效应晶体管(field effect transistor:fet)。

34.各单位晶体管的发射极或者源极相当于本公开的“第1端子”。各单位晶体管的基

极或者栅极相当于本公开的“第2端子”。各单位晶体管的集电极或者漏极相当于本公开的“第3端子”。

35.各单位晶体管103的发射极与基准电位电连接。基准电位可例示接地电位,但本公开不限定于此。各单位晶体管103的基极与第1端子p11电连接。各电阻104的一端与第2端子p12电连接。各电阻104的另一端与各单位晶体管103的基极电连接。各单位晶体管103的集电极与第3端子p13电连接。

36.另外,设交流信号rf11不包含直流分量,仅包含交流分量。因此,各单元102不需要在第1端子p11与各单位晶体管103的基极之间的路径包含dc截止电容器。

37.在电阻104

‑

1流过电流i

‑

1。在电阻104

‑

m流过电流i

‑

m。在电阻104

‑

n流过电流i

‑

n。电流i

‑

1至电流i

‑

n的总和与偏置电流bias11相同。

38.如果各单位晶体管103的电特性相同,则电流i

‑

1全部流过单位晶体管103

‑

1的基极

‑

发射极路径,电流i

‑

m全部流过单位晶体管103

‑

m的基极

‑

发射极路径,电流i

‑

n全部流过单位晶体管103

‑

n的基极

‑

发射极路径。

39.但是,例如,存在由于单位晶体管103各自的温度不同而各单位晶体管103的基极的输入阻抗(输入电阻)不同的情况。又例如,存在由于多个单位晶体管103有个体差异而各单位晶体管103的基极的输入阻抗不同的情况。

40.在此,设单位晶体管103

‑

m的输入阻抗比其他单位晶体管103的输入阻抗低。即,设单位晶体管103

‑

m的输入阻抗最小。

41.于是,电流i

‑

1的一部分作为电流i

‑

1a流过单位晶体管103

‑

1的基极

‑

发射极路径,而电流i

‑

1的剩余部分作为电流i

‑

1b流过单位晶体管103

‑

m的基极

‑

发射极路径。同样地,电流i

‑

n的一部分作为电流i

‑

na流过单位晶体管103

‑

n的基极

‑

发射极路径,而电流i

‑

n的剩余部分作为电流i

‑

nb流过单位晶体管103

‑

m的基极

‑

发射极路径。

42.因此,流过单位晶体管103

‑

m的基极

‑

发射极路径的电流i

‑

ma成为电流i

‑

m与从其他单元流入的电流之和。由此,在单位晶体管103

‑

m的基极

‑

发射极路径流过较大的偏置电流,其他单位晶体管103的基极

‑

发射极路径的偏置电流变小。由此,多个单位晶体管103会不均等地进行动作。若多个单位晶体管103不均等地进行动作,则无法得到期望的放大特性。

43.(第1实施方式)

44.图2是示出第1实施方式的多指晶体管的结构的图。多指晶体管1是对多个单位晶体管进行电并联连接而成的。所谓单位晶体管,是指构成晶体管的最小限度的结构。

45.多指晶体管1具有被输入交流信号rf1的第1端子p1、被输入偏置电流bias1的第2端子p2和输出交流信号rf2的第3端子p3。第3端子p3经由扼流电感器10与电源电位vcc1电连接。

46.第1端子p1相当于本公开的“公共输入端子”的一例。第2端子p2相当于本公开的“公共偏置端子”的一例。第3端子p3相当于本公开的“公共输出端子”的一例。

47.多指晶体管1从电源电位vcc1被供给电力,通过偏置电流bias1而被设定电偏置状态。然后,多指晶体管1对交流信号rf1进行放大,并输出放大后的交流信号rf2。

48.多指晶体管1包含n个单元2

‑

1~2

‑

n。单元2

‑

1包含单位晶体管3

‑

1、电阻4

‑

1和电阻5

‑

1。单元2

‑

m包含单位晶体管3

‑

m、电阻4

‑

m和电阻5

‑

m。单元2

‑

n包含单位晶体管3

‑

n、电阻4

‑

n和电阻5

‑

n。作为一例,电阻4

‑

1~4

‑

n各自的电阻值设为180ω~200ω程度。不过,本公开不限定于此。作为一例,电阻5

‑

1~5

‑

n各自的电阻值设为1ω程度。不过,本公开不限定于此。作为一例,可例示电阻5

‑

1~5

‑

n各自的电阻值比电阻4

‑

1~4

‑

n各自的电阻值小。不过,本公开不限定于此。作为一例,可例示电阻4

‑

1~4

‑

n各自的电阻值为电阻5

‑

1~5

‑

n各自的电阻值的5倍以上。不过,本公开不限定于此。

49.电阻5相当于本公开的“第1电阻元件”的一例。电阻4相当于本公开的“第2电阻元件”的一例。

50.各单位晶体管3的发射极与基准电位电连接。各电阻5的一端与各单位晶体管3的基极电连接。各电阻5的另一端与第1端子p1电连接。各电阻4的一端与各单位晶体管3的基极电连接。各电阻4的另一端与第2端子p2电连接。各单位晶体管3的集电极与第3端子p3电连接。

51.另外,交流信号rf1仅包含交流分量。因此,各单元2不需要在第1端子p1与各单位晶体管3的基极之间的路径包含dc截止电容器。

52.在电阻4

‑

1流过电流i

‑

1。在电阻4

‑

m流过电流i

‑

m。在电阻4

‑

n流过电流i

‑

n。电流i

‑

1至电流i

‑

n的总和与偏置电流bias1相同。

53.例如,存在由于各单位晶体管3各自的温度不同而各单位晶体管3的基极的输入阻抗(输入电阻)不同的情况。又例如,存在由于单位晶体管3有个体差异而各单位晶体管3的基极的输入阻抗不同的情况。

54.在此,设单位晶体管3

‑

m的输入阻抗比其他单位晶体管3的输入阻抗低。即,设单位晶体管3

‑

m的输入阻抗最小。

55.但是,各电阻4的一端与各单位晶体管3的基极电连接,并且还与各电阻5的一端电连接。

56.因此,对于流过电阻4

‑

1的电流i

‑

1,由于电阻5

‑

1的存在从而可抑制朝向电阻5

‑

1侧流动,因而成为流过单位晶体管3

‑

1的基极

‑

发射极路径的电流i

‑

1a。同样地,对于流过电阻4

‑

m的电流i

‑

m,由于电阻5

‑

m的存在从而可抑制朝向电阻5

‑

m侧流动,因而成为流过单位晶体管3

‑

m的基极

‑

发射极路径的电流i

‑

ma。同样地,对于流过电阻4

‑

n的电流i

‑

n,由于电阻5

‑

n的存在从而可抑制朝向电阻5

‑

n侧流动,因而成为流过单位晶体管3

‑

n的基极

‑

发射极路径的电流i

‑

na。

57.由此,可抑制各单位晶体管3不均等地进行动作。因为可抑制各单位晶体管3不均等地进行动作,因此可得到期望的放大特性。

58.另外,各电阻5可例示下述内容,但本公开不限定于这些。

59.在将多指晶体管记为一个晶体管的情况下,可例示各电阻5的合成电阻的电阻值为0.5ω以上。因此,可例示与单位晶体管连接的各个电阻5的电阻值相对于单位晶体管的数量n为(0.5

×

n)ω以上的电阻值。

60.可例示各电阻5的电阻值比各单位晶体管3的发射极镇流电阻的电阻值小。发射极镇流电阻可例示200欧姆程度,但本公开不限定于此。

61.可例示各电阻5的电阻值是相当于一般与各单位晶体管3的基极连接的dc截止电容器的阻抗的电阻值,但本公开不限定于此。例如,一般地,设在交流信号rf1的频率为0.9ghz(千兆赫)频段的情况下,2pf(皮法)的dc截止电容器与各单位晶体管3的基极串联连

接。于是,相当于该dc截止电容器的阻抗(1/ωc)的电阻值成为88欧姆。

62.<第2实施方式>

63.图3是示出第2实施方式的功率放大电路的结构的图。详细地,图3是示出应用了第1实施方式的多指晶体管1的功率放大电路的结构的图。

64.功率放大电路11可以通过在一个基板上安装了多个部件(半导体芯片等)的混合ic(也可以称为模块)来实现,但本公开不限定于此。

65.功率放大电路11包含作为初级的功率放大器的多指晶体管12、作为第2级的功率放大器的多指晶体管13以及14、和作为第3级的功率放大器的多指晶体管15以及16。另外,功率放大器的级数不限定于3级,既可以为2级以下,也可以为4级以上。

66.多指晶体管12是在基极串联连接有dc截止电容器的、一般的多指晶体管。多指晶体管13~16具有与第1实施方式的多指晶体管1(参照图2)相同的电路结构。

67.多指晶体管12的各单元包含单位晶体管12a、dc截止电容器12b和电阻12c。

68.多指晶体管12的各单元的单位晶体管12a的发射极与基准电位电连接。在各单元的单位晶体管12a的基极,经由各单元的dc截止电容器12b被输入高频输入信号rfin。在各单元的单位晶体管12a的基极,经由各单元的电阻12c被输入偏置电流bias21。各单元的单位晶体管12a的集电极经由扼流电感器31与电源电位vcc21电连接。各单元的单位晶体管12a将高频信号rf21从集电极经由dc截止电容器32输出至平衡

‑

不平衡变压器(balun)t1的初级绕组的一端。

69.平衡

‑

不平衡变压器t1的初级绕组的另一端与基准电位电连接。从平衡

‑

不平衡变压器t1的次级绕组的一端,高频信号rf22被输出至多指晶体管13的基极。从平衡

‑

不平衡变压器t1的次级绕组的另一端,高频信号rf23被输出至多指晶体管14的基极。

70.多指晶体管13的各单元包含单位晶体管13a和电阻13b以及13c。

71.多指晶体管13的各单元的单位晶体管13a的发射极与基准电位电连接。在各单元的单位晶体管13a的基极,经由各单元的电阻13b被输入高频信号rf22。

72.从平衡

‑

不平衡变压器t1的次级绕组输出的高频信号rf22不包含直流分量,因此在平衡

‑

不平衡变压器t1的次级绕组与各单元的单位晶体管13a的基极之间不需要dc截止电容器。

73.在各单元的单位晶体管13a的基极,经由各单元的电阻13c被输入偏置电流bias22。各单元的单位晶体管13a的集电极与平衡

‑

不平衡变压器t2的初级绕组的一端电连接。各单元的单位晶体管13a将高频信号rf24从集电极输出至平衡

‑

不平衡变压器t2的初级绕组的一端。

74.多指晶体管14的各单元包含单位晶体管14a和电阻14b以及14c。

75.多指晶体管14的各单元的单位晶体管14a的发射极与基准电位电连接。在各单元的单位晶体管14a的基极,经由各单元的电阻14b被输入高频信号rf23。

76.从平衡

‑

不平衡变压器t1的次级绕组输出的高频信号rf23不包含直流分量,因此在平衡

‑

不平衡变压器t1的次级绕组与各单元的单位晶体管14a的基极之间不需要dc截止电容器。

77.在各单元的单位晶体管14a的基极,经由各单元的电阻14c被输入偏置电流bias23。各单元的单位晶体管14a的集电极与平衡

‑

不平衡变压器t2的初级绕组的另一端电

连接。各单元的单位晶体管14a将高频信号rf25从集电极输出至平衡

‑

不平衡变压器t2的初级绕组的另一端。

78.平衡

‑

不平衡变压器t2的初级绕组的中点与电源电位vcc22电连接。电源电位vcc22经由平衡

‑

不平衡变压器t2的初级绕组被供给至多指晶体管13以及14的集电极。

79.从平衡

‑

不平衡变压器t2的次级绕组的一端,高频信号rf26被输出至多指晶体管15的基极。从平衡

‑

不平衡变压器t2的次级绕组的另一端,高频信号rf27被输出至多指晶体管16的基极。

80.多指晶体管15的各单元包含单位晶体管15a和电阻15b以及15c。

81.多指晶体管15的各单元的单位晶体管15a的发射极与基准电位电连接。在各单元的单位晶体管15a的基极,经由各单元的电阻15b被输入高频信号rf26。

82.从平衡

‑

不平衡变压器t2的次级绕组输出的高频信号rf26不包含直流分量,因此在平衡

‑

不平衡变压器t2的次级绕组与各单元的单位晶体管15a的基极之间不需要dc截止电容器。

83.在各单元的单位晶体管15a的基极,经由各单元的电阻15c被输入偏置电流bias24。各单元的单位晶体管15a的集电极与平衡

‑

不平衡变压器t3的初级绕组的一端电连接。各单元的单位晶体管15a将高频信号rf28从集电极输出至平衡

‑

不平衡变压器t3的初级绕组的一端。

84.多指晶体管16的各单元包含单位晶体管16a和电阻16b以及16c。

85.多指晶体管16的各单元的单位晶体管16a的发射极与基准电位电连接。在各单元的单位晶体管16a的基极,经由各单元的电阻16b被输入高频信号rf27。

86.从平衡

‑

不平衡变压器t2的次级绕组输出的高频信号rf27不包含直流分量,因此在平衡

‑

不平衡变压器t2的次级绕组与各单元的单位晶体管16a的基极之间不需要dc截止电容器。

87.在各单元的单位晶体管16a的基极,经由各单元的电阻16c被输入偏置电流bias25。各单元的单位晶体管16a的集电极与平衡

‑

不平衡变压器t3的初级绕组的另一端电连接。各单元的单位晶体管16a将高频信号rf29从集电极输出至平衡

‑

不平衡变压器t3的初级绕组的另一端。

88.平衡

‑

不平衡变压器t3的初级绕组的中点与电源电位vcc23电连接。电源电位vcc23经由平衡

‑

不平衡变压器t3的初级绕组被供给至多指晶体管15以及16的集电极。

89.平衡

‑

不平衡变压器t3的次级绕组的一端与基准电位电连接。从平衡

‑

不平衡变压器t3的次级绕组的另一端输出高频输出信号rfout。

90.由此,功率放大电路11在中间级、输出级分别不构成dc截止用的电容,从而得不到基于由与偏置电路连接的电阻(例如,电阻13c、14c、15c以及16c)和电容之积决定的时间常数的滤波效应,因此不会受到调制带宽所引起的频带限制。

91.另外,上述的实施方式用于使本发明容易理解,并非用于对本发明进行限定解释。本发明能够在不脱离其主旨的情况下进行变更/改良,并且本发明还包含其等价物。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。