基于hfo2‑

zro2超晶格铁电栅介质的晶体管及其制备方法

技术领域

1.本发明涉及电子技术领域,具体涉及一种基于hfo2‑

zro2超晶格铁电栅介质的晶体管及其制备方法。

背景技术:

2.当前高度信息化的社会,人工智能和物联网正在推动新的创新,需要通信、加载和存储大数据,边缘计算使用机器学习等数据密集型算法。因此,高密度、低功耗的非易失性存储器在开发电池容量和能量收集电源有限的物联网和人工智能设备中发挥着关键作用。

3.氧化铪(hfo2)基铁电场效应晶体管存储器由于其与互补金属氧化物半导体(cmos)工艺的兼容性和场驱动操作的潜在低功耗而备受关注,为低成本和低功耗存储器提供了新的发展思路。最近提出了一种受3d垂直与非门结构启发的高密度铁电场效应晶体管(fefet)结构。从器件角度来看,垂直场效应晶体管面临的挑战是极薄多晶硅沟道的低迁移率、电荷俘获引起的阈值电压补偿和退化的亚阈值斜率、硅沟道上低介电常数界面层的电压损失。

4.金属氧化物是一种有前途的沟道材料,因为它作为沉积的非晶材料具有高迁移率、没有太多表面传导以避免电荷俘获、几乎为零的低k界面层,以及cmos工艺良好的兼容性,成为应对以上问题的措施之一。

5.最新的研究使用例如igzo、iwo等金属氧化物作为hfo2基fefet的沟道材料,利用金属氧化物在非常薄的层厚度下,迁移率足够高,同时形成低k界面层等特性来提高器件性能。尽管如此,hfo2基fefet良好的疲劳耐久性仍是目前未能解决的关键问题。

技术实现要素:

6.针对现有技术中存在的问题,本发明的目的在于提供一种基于hfo2‑

zro2超晶格铁电栅介质的晶体管及其制备方法,通过该方法能够获得与现有集成工艺兼容、泄漏电流小、铁电性能优异、可靠性良好的金属氧化物晶体管器件。

7.为了达到上述目的,本发明采用以下技术方案予以实现。

8.(一)基于hfo2‑

zro2超晶格铁电栅介质的晶体管,包括:底电极、超晶格铁电栅介质层、金属氧化物沟道、源极、漏极、绝缘电介质薄膜、栅电极和衬底;其中,所述底电极、超晶格铁电栅介质层、金属氧化物沟道在衬底依次由下至上竖直分布;所述源极、漏极分布在所述金属氧化物沟道的两侧;所述绝缘电介质薄膜、栅电极在所述金属氧化物沟道上依次由下而上垂直分布。

9.优选的,所述超晶格铁电栅介质层的厚度为6

‑

20nm。

10.进一步优选的,所述超晶格铁电栅介质层的厚度为12

‑

15nm。

11.优选的,所述超晶格铁电栅介质层中包含5层氧化铪和5层氧化锆、或者包含10层氧化铪和10层氧化锆、或者包含15层氧化铪和15层氧化锆。

12.优选的,所述底电极的厚度为20

‑

50nm。

13.进一步优选的,所述底电极的厚度为30

‑

40nm。

14.优选的,所述金属氧化物沟道的厚度为5

‑

20nm。

15.进一步优选的,所述金属氧化物沟道的厚度为8

‑

10nm。

16.优选的,所述金属氧化物沟道为铟镓锌氧化物沟道、氧化锌沟道或掺钨氧化铟沟道。

17.优选的,所述源极、漏极的厚度分别为50

‑

150nm。

18.进一步优选的,所述源极、漏极的厚度分别为100

‑

110nm。

19.优选的,所述绝缘电介质薄膜的厚度为10

‑

12nm。

20.优选的,所述栅电极的厚度为50

‑

150nm。

21.进一步优选的,所述栅电极的厚度为100

‑

110nm。

22.(二)基于hfo2‑

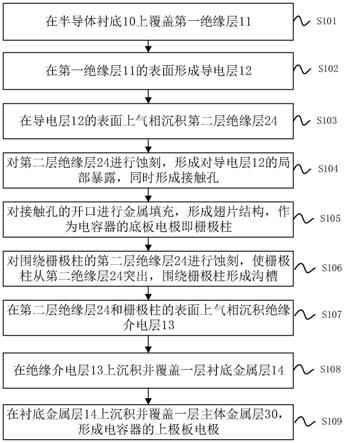

zro2超晶格铁电栅介质的晶体管的制备方法,包括以下步骤:

23.步骤1,清洗硅衬底,在所述硅衬底上方利用磁控溅射方法沉积底电极;

24.步骤2,利用原子层沉积方法,在所述底电极上方沉积hfo2‑

zro2薄膜超晶格结构薄膜作为超晶格铁电栅介质层;

25.步骤3,利用磁控溅射方法在所述超晶格铁电栅介质层上方沉积金属氧化物,形成金属氧化物沟道;

26.步骤4,利用磁控溅射方法在所述金属氧化物沟道上方沉积二氧化硅,形成绝缘电介质薄膜;

27.步骤5,利用磁控溅射方法在所述绝缘电介质薄膜上方沉积金属,形成金属层;

28.步骤6,利用光刻方法,在金属层上标定源极区域、栅极区域、漏极区域;

29.步骤7,利用刻蚀方法,在光刻胶的掩蔽作用下,将栅极区域两侧的源极区域和漏极区域刻蚀掉,在栅极区域中间形成栅电极;

30.步骤8,利用电子束沉积方法,在所述源极区域和所述漏极区域分别同时先沉积金属镍,再沉积金属铝,形成源极和漏极,完成晶体管的制作。

31.与现有技术相比,本发明的有益效果为:

32.利用原子层沉积技术沉积hfo2‑

zro2超晶格结构薄膜作为铁电栅介质层代替传统金属氧化物沟道铁电场效应晶体管中的铁电栅介质层,与现有集成电路工艺结合,极大地降低了栅极泄漏电流,提升铁电性能,通过超晶格结构对电子俘获的抑制作用,提高器件的抗疲劳特性,从而为金属氧化物沟道铁电场效应器件提供更高的耐久性。

33.2)采用igzo、iwo、zno等制成的金属氧化物沟道层与基于hfo2‑

zro2超晶格铁电栅介质相结合所得的晶体管的耐久性更好,利用金属氧化物在非常薄的层厚度下,迁移率足够高,同时形成低k界面层等特性来提高晶体管器件性能,可以实现高密度存储的同时提升晶体管的铁电性能。

附图说明

34.下面结合附图和具体实施例对本发明做进一步详细说明。

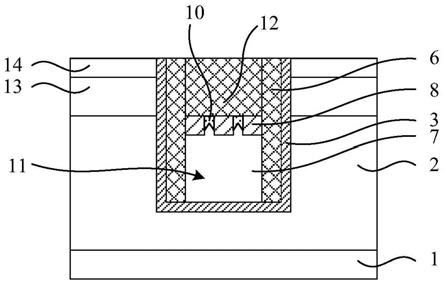

35.图1为本发明基于hfo2‑

zro2超晶格铁电栅介质的晶体管的截面结构示意图;

36.图2为现有的铁电栅介质层与本发明的超晶格铁电栅介质层的泄漏电流测试对比图;

37.图3为现有的铁电栅介质层与本发明的超晶格铁电栅介质层的铁电性能测试对比图;其中,图(a)为现有的铁电栅介质层;图(b)为本发明的基于hfo2‑

zro2超晶格结构的铁电栅介质层;

38.以上图中:1底电极;2超晶格铁电栅介质层;3金属氧化物沟道;4源极;5漏极;6绝缘电介质薄膜;7栅电极;8衬底。

具体实施方式

39.下面将结合实施例对本发明的实施方案进行详细描述,但是本领域的技术人员将会理解,下列实施例仅用于说明本发明,而不应视为限制本发明的范围。

40.参考图1,基于hfo2‑

zro2超晶格铁电栅介质的晶体管,包括:底电极1、超晶格铁电栅介质层2、金属氧化物沟道3、源极4、漏极5、绝缘电介质薄膜6、栅电极7和衬底8;其中,所述底电极1、超晶格铁电栅介质层2、金属氧化物沟道3在衬底8依次由下至上竖直分布;所述源极4、漏极5分布在所述金属氧化物沟道3的两侧;所述绝缘电介质薄膜6、栅电极7在所述金属氧化物沟道3上依次由下而上垂直分布。

41.实施例1

42.基于hfo2‑

zro2超晶格铁电栅介质的igzo沟道晶体管的制备方法,包括以下步骤:

43.步骤1,清洗硅衬底8,在所述硅衬底8上方利用磁控溅射方法,以氮化钛(tin)金属作为靶材,氩气环境下沉积12min,形成厚度为30nm的tin底电极1。

44.磁控溅射方法是利用磁控溅射设备,在电场作用下,电离出的氩原子加速轰击靶材,溅射出大量的靶材原子层,把氮化钛材料原子沉积在硅衬底上。

45.步骤2,利用原子层沉积方法,在所述底电极1上方沉积hfo2‑

zro2薄膜超晶格结构薄膜作为超晶格铁电栅介质层2。

46.具体的,利用原子层沉积方法(ald),在250℃条件下,以50%氧化铪(hfo2)和50%的氧化锆(zro2)作为源,在底电极1上交替沉积多个相同cycles的hfo2‑

zro2超晶格结构薄膜作为12nm超晶格铁电栅介质层2。原子层沉积方法为利用原子层沉积设备,将物质以单原子膜形式一层一层的镀在底电极1表面的方法,本发明是交替沉积多个相同层数的hfo2和zro2,比如先沉积10层hfo2,再沉积10层zro2,形成超晶格结构的hfo2‑

zro2薄膜。

47.步骤3,利用磁控溅射方法在所述超晶格铁电栅介质层2上方沉积igzo(铟镓锌氧化物)金属氧化物,以igzo作为靶材,在50w功率室温下,氩气环境下沉积48s,形成厚度为8nm的金属氧化物沟道3。

48.步骤4,利用磁控溅射方法在所述金属氧化物沟道3上方沉积二氧化硅,形成厚度为12nm的绝缘电介质薄膜6。

49.步骤5,利用磁控溅射方法在所述绝缘电介质薄膜6上方沉积100nm厚的铝(al)和10nm厚的镍(ni)金属,形成金属层,在n2/o2(o2:3%)的环境中,在500℃温度下进行10s的退火。

50.步骤6,利用光刻方法,在金属层上标定源极区域、栅极区域、漏极区域。

51.光刻工艺是利用光刻机通过曝光和显影在光刻胶层上刻画几何图形结构,标定要沉积金属的区域。具体是先经过110℃下前烘3min,之后以转速4000r匀胶30s,再在100℃下烘胶90s,然后曝光2.6s后在tmd 2.38%显影液中进行显影45s,最后在110℃下烘干2min。

52.步骤7,利用刻蚀方法,在光刻胶的掩蔽作用下,将栅极区域两侧的源极区域和漏极区域刻蚀掉,在栅极区域中间形成栅电极7。

53.具体的,刻蚀方法利用刻蚀机进行干法刻蚀,在氯气和三氯化硼的混合气体环境下(60sccm:60sccm),25mtorr气压,150w功率条件下,将源极、漏极区域刻蚀掉。

54.步骤8,利用电子束沉积方法,在源极4和漏极5区域同时先沉积10nm金属镍,再沉积100nm金属铝,完成晶体管的制作。

55.具体的,电子束沉积法是一种使用电子束沉积设备,利用电子束分解沉积材料的气相分子,从而在衬底上的特定位置实现沉积生长的方法。电子束沉积实验中的电子束常常由扫描电子显微镜提供。

56.实施例2

57.基于hfo2‑

zro2超晶格铁电栅介质的zno沟道晶体管的制备方法,包括以下步骤:

58.步骤1,清洗硅衬底8,在所述硅衬底8上方利用磁控溅射方法,以氮化钛(tin)金属作为靶材,氩气环境下沉积12min,形成厚度为30nm的tin底电极1。

59.步骤2,利用原子层沉积方法,在所述底电极1上方沉积hfo2‑

zro2薄膜超晶格结构薄膜作为超晶格铁电栅介质层2。

60.具体的,利用原子层沉积方法,在250℃条件下,以50%氧化铪(hfo2)和50%的氧化锆(zro2)作为源,在底电极1上交替沉积多个相同cycles的hfo2‑

zro2超晶格结构薄膜作为12nm超晶格铁电栅介质层2。原子层沉积方法为利用原子层沉积设备,将物质以单原子膜形式一层一层的镀在底电极1表面的方法,本发明是交替沉积多个相同层数的hfo2和zro2,比如15层hfo2和15层zro2,形成超晶格结构的hfo2‑

zro2薄膜。

61.步骤3,利用磁控溅射方法在所述超晶格铁电栅介质层2上方沉积zno(氧化锌)金属氧化物,以zno作为靶材,氩气环境下在铁电栅介质薄膜上淀积zno金属氧化物,形成厚度为8nm的金属氧化物沟道3。

62.步骤4,利用磁控溅射方法在所述金属氧化物沟道3上方沉积二氧化硅,形成厚度为12nm的绝缘电介质薄膜6。

63.步骤5,利用磁控溅射方法在所述绝缘电介质薄膜6上方沉积100nm厚的铝(al)和10nm厚的镍(ni)金属,形成金属层,在n2/o2(o2:3%)的环境中,在500℃温度下进行10s的退火。

64.步骤6,利用光刻方法,在金属层上标定源极区域、栅极区域、漏极区域;

65.步骤7,利用刻蚀方法,在光刻胶的掩蔽作用下,将栅极区域两侧的源极区域和漏极区域刻蚀掉,在栅极区域中间形成栅电极7;

66.步骤8,利用电子束沉积方法,源极4和漏极5区域同时先沉积10nm金属镍,再沉积100nm金属铝,完成晶体管的制作。

67.实施例3

68.基于hfo2‑

zro2超晶格铁电栅介质的iwo沟道晶体管的制备方法,包括以下步骤:

69.步骤1,清洗硅衬底8,在所述硅衬底8上方利用磁控溅射方法,以氮化钛(tin)金属作为靶材,氩气环境下沉积12min,形成厚度为30nm的tin底电极1。

70.步骤2,利用原子层沉积方法,在所述底电极1上方沉积hfo2‑

zro2薄膜超晶格结构薄膜作为超晶格铁电栅介质层2。

71.具体的,利用原子层沉积方法,在250℃条件下,以50%氧化铪(hfo2)和50%的氧化锆(zro2)作为源,在底电极1上交替沉积多个相同cycles的hfo2‑

zro2超晶格结构薄膜作为12nm超晶格铁电栅介质层2。原子层沉积方法为利用原子层沉积设备,将物质以单原子膜形式一层一层的镀在底电极1表面的方法,本发明是交替沉积多个相同层数的hfo2和zro2,比如5层hfo2和5层zro2,形成超晶格结构的hfo2‑

zro2薄膜。

72.步骤3,利用磁控溅射方法在所述超晶格铁电栅介质层2上方沉积iwo(掺钨氧化铟)金属氧化物,以iwo作为靶材,氩气环境下在铁电栅介质薄膜上淀积iwo金属氧化物,形成厚度为8nm的金属氧化物沟道3。

73.步骤4,利用磁控溅射方法在所述金属氧化物沟道3上方沉积二氧化硅,形成厚度为12nm的绝缘电介质薄膜6。

74.步骤5,利用磁控溅射方法在所述绝缘电介质薄膜6上方沉积100nm厚的铝(al)和10nm厚的镍(ni)金属,形成金属层,在n2/o2(o2:3%)的环境中,在500℃温度下进行10s的退火。

75.步骤6,利用光刻方法,在金属层上标定源极区域、栅极区域、漏极区域;

76.步骤7,利用刻蚀方法,在光刻胶的掩蔽作用下,将栅极区域两侧的源极区域和漏极区域刻蚀掉,在栅极区域中间形成栅电极7;

77.步骤8,利用电子束沉积方法,源极4和漏极5区域同时先沉积10nm金属镍,再沉积100nm金属铝,完成晶体管的制作。

78.以上实施例中,沟道层的材料为金属氧化物,栅介质层为超晶格结构铁电材料;此晶体管通过施加正向或负向电压偏置改变铁电材料的极化方向来调制阈值电压,使器件产生擦除和写入两个状态,从而实现存储“0”和“1”的功能。采用超晶格结构的铁电材料作为金属氧化物沟道3晶体管的栅极介质,降低二氧化硅层的电场,降低栅极泄露电流,提高铁电极化值,从而大幅提高器件的性能。

79.试验

80.试验1

81.对现有的铁电栅介质层与本发明的超晶格铁电栅介质层的泄漏电流进行测试,结果如图2所示;其中,现有的铁电栅介质层中包含1层hfo2和1层zro2;本发明的超晶格铁电栅介质层中包含10层hfo2和10层zro2。

82.由图2可知,本发明的超晶格铁电栅介质层的泄漏电流比现有的铁电栅介质层的泄漏电流降低了一个数量级。

83.试验2

84.对现有的铁电栅介质层与本发明的超晶格铁电栅介质层的铁电性能进行测试,结果如图3所示;其中,现有的铁电栅介质层中包含1层hfo2和1层zro2;本发明的超晶格铁电栅介质层中包含10层hfo2和10层zro2。

85.由图3可知,现有结构介质层的剩余极化值在2v电压下为11.3μc/cm2,超晶格铁电栅介质层的剩余极化值在2v电压下为16.7μc/cm2;现有结构介质层的剩余极化值在4.5v电压下为22.3μc/cm2,超晶格铁电栅介质层的剩余极化值为23.7μc/cm2。超晶格结构铁电栅介质层对铁电性能的提升有明显作用。

86.虽然,本说明书中已经用一般性说明及具体实施方案对本发明作了详尽的描述,

但在本发明基础上,可以对之作一些修改或改进,这对本领域技术人员而言是显而易见的。因此,在不偏离本发明精神的基础上所做的这些修改或改进,均属于本发明要求保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。