一种金属

‑

氧化层

‑

栅极电容器及其制备方法

技术领域

1.本发明涉及电容器制备领域,具体涉及一种金属

‑

氧化层

‑

栅极电容器及其制备方法。

背景技术:

2.电容是当今集成电路器件中的关键元件。例如,在模拟集成电路器件中,电容器就扮演着重要的角色。多晶硅

‑

多晶硅(poly

‑

to

‑

poly)以及金属

‑

氧化层

‑

栅极形成的电容器都已经在这一技术领域被广泛应用。多晶硅电容器和金属

‑

氧化层

‑

金属(metal

‑

oxide

‑

metal,mom)电容器虽然已经得到广泛的应用,但是,多晶硅与多晶硅式电容器需要复杂或者特殊的工艺,这一类电容器具有缺乏灵活性、极板耦合噪声干扰和掺杂剂扩散效应以及其他各种问题。随着后端工艺引入越来越多的金属层级,金属

‑

氧化层

‑

金属电容器(mom)得到了广泛的使用,但是,mom的最大缺点是密度低,集成和混用能力欠缺。

3.目前,radosevich等人的美国专利(u.s.pat.nos.5,576,240和5,654,581)、授予smrtic等人的美国专利(u.s.pat.no.5,479,316)、以及授予brabazon的美国专利(u.s.pat.no.5,708,55)均公开了形成金属

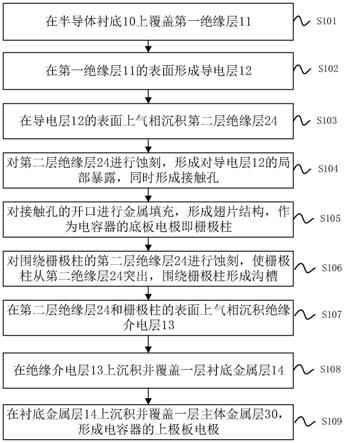

‑

氧化层栅极电容的各种方法,但是这些制备方法不仅缺乏灵活性,而且并不适宜在翅片结构,特别是金属栅极的工艺中使用。针对上述问题,chittipeddi教授的专利号为5,589,416的专利中提出了一种制备金属

‑

氧化层

‑

栅极电容的工艺,但是平板电容器的电容密度要比翅片状电容密度要低数倍。虽然,美国专利局最新的一项专利(us.pat.appl.pub.no.us2020/0194599a1)中采用了翅片结构,但是,这一工艺相当复杂,而且它是针对可编程电阻,而不是电容而设计的。

4.因此,针对上述技术问题,目前亟需设计一种可用于传统半导体平面制备和最先进的finfet制备技术的金属

‑

氧化层

‑

栅极电容器的制备方法。

技术实现要素:

5.针对现有技术中存在的缺陷,本发明的目的在于提供一种金属

‑

氧化层

‑

栅极电容器及其制备方法,制备方法灵活、简单,可用于传统半导体平面制备和最先进的finfet制备技术。

6.为实现上述目的,本发明采用的技术方案如下:

7.一种金属

‑

氧化层

‑

栅极电容器的制备方法,包括以下步骤:

8.在半导体衬底上覆盖第一绝缘层;

9.在所述第一绝缘层的表面形成导电层;

10.在所述导电层的表面上气相沉积第二层绝缘层;

11.对所述第二层绝缘层进行蚀刻,形成对所述导电层的局部暴露,同时形成接触孔;

12.对所述接触孔的开口进行金属填充,形成翅片结构,作为所述电容器的底板电极即栅极柱;

13.对围绕所述栅极柱的所述第二层绝缘层进行蚀刻,使所述栅极柱从所述第二绝缘

层突出,围绕所述栅极柱形成沟槽;

14.在所述第二层绝缘层和所述栅极柱的表面上气相沉积绝缘介电层;

15.在所述绝缘介电层上沉积并覆盖一层衬底金属层;

16.在所述衬底金属层上沉积并覆盖一层主体金属层,形成所述电容器的上极板电极。

17.进一步,如上所述的制备方法,所述半导体衬底为沟槽阵列形状,所述半导体衬底为体硅或者由外延层形成。

18.进一步,如上所述的制备方法,所述第一绝缘层由栅氧化物组成。

19.进一步,如上所述的制备方法,采用钨金属对所述接触孔的开口进行金属填充。

20.进一步,如上所述的制备方法,采用lpcvd工艺在所述第二层绝缘层和所述栅极柱的表面上气相沉积所述绝缘介电层。

21.进一步,如上所述的制备方法,所述导电层包括多晶硅或金属栅极线,所述栅极柱为多晶硅栅极柱或金属栅极柱。

22.进一步,如上所述的制备方法,所述绝缘介电层的厚度在200至400埃之间,由未掺杂硅酸盐玻璃组成。

23.进一步,如上所述的制备方法,所述衬底金属层的复合厚度在50至600埃之间,由钛或者氮化钛组成。

24.进一步,如上所述的制备方法,所述主体金属层的厚度在3000至8000埃之间,由铝或者铜组成。

25.本发明实施例中还提供了一种金属

‑

氧化层

‑

栅极电容器,采用上述的制备方法制备而成,所述电容器包括:底板电极和上极板电极;

26.在半导体衬底上覆盖第一绝缘层;

27.在所述第一绝缘层的表面形成导电层;

28.在所述导电层的表面上气相沉积第二层绝缘层;

29.对所述第二层绝缘层进行蚀刻,形成对所述导电层的局部暴露,同时形成接触孔;

30.对所述接触孔的开口进行金属填充,形成翅片结构,作为所述电容器的底板电极即栅极柱;

31.对围绕所述栅极柱的所述第二层绝缘层进行蚀刻,使所述栅极柱从所述第二绝缘层突出,围绕所述栅极柱形成沟槽;

32.在所述第二层绝缘层和所述栅极柱的表面上气相沉积绝缘介电层;

33.在所述绝缘介电层上沉积并覆盖一层衬底金属层;

34.在所述衬底金属层上沉积并覆盖一层主体金属层,形成所述电容器的上极板电极。

35.本发明的有益效果在于:本发明提供的金属

‑

氧化层

‑

栅极电容器的制备方法以及制备而成的电容器可用于传统半导体平面制备和最先进的finfet制备技术,不仅具有良好的顺畅制备流程,还能保障均匀性。

附图说明

36.图1为本发明实施例中提供的一种金属

‑

氧化层

‑

栅极电容器的制备方法的流程示

意图;

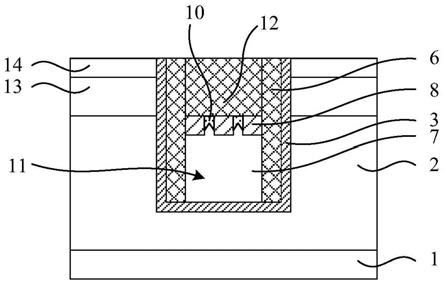

37.图2为本发明实施例中提供的半导体衬底的截面示意图;

38.图3为本发明实施例中提供的早期隔离工艺的截面示意图;

39.图4为图1中s102对应的截面示意图;

40.图5为图1中s103对应的截面示意图;

41.图6为图1中s107对应的截面示意图;

42.图7为图1中s104和s105对应的截面示意图;

43.图8为图1中s108对应的截面示意图;

44.图9为图1中s109对应的截面示意图;

45.图10为本发明实施例中提供的使用先进铜金属cmp打磨工艺而形成的效果示意图;

46.图11为本发明实施例中提供的将原有的mom结构和本发明的mop结构相结合的效果示意图。

具体实施方式

47.为使本发明解决的技术问题、采用的技术方案和达到的技术效果更加清楚,下面将结合附图对本发明实施例的技术方案作进一步的详细描述。

48.本发明实施例提供了一种金属

‑

氧化层

‑

栅极电容器的制备方法,如图1所示,该制备方法包括:

49.s101、在半导体衬底10上覆盖第一绝缘层11。

50.本发明实施例中,在制备金属

‑

氧化层

‑

栅极电容器时,首先提供第一绝缘层11作为半导体衬底10的承载层,半导体衬底10为沟槽阵列形状,半导体衬底10为体硅或者由外延层形成,如图2所示,它显示了在半导体衬底10上形成的沟槽阵列形状。图3展示了早期隔离工艺(field oxidation,fox),它是沟槽技术发明之前采用的一种技术,其中100为电容器所处的场区双氧化硅,其他场双氧化硅标为100a以示区别,半导体器件结构形成于半导体衬底之中或者之上,半导体衬底10可以是体硅或者由epi外延层形成,epi层则通过注入或者生长形成。其他半导体器件结构(图中未显示)可以在图中右侧区域生成。

51.s102、在第一绝缘层11的表面形成导电层12。

52.本发明实施例中,如图4所示,第一绝缘层11即栅氧化物作为缓冲氧化物沉积,在第一绝缘层11的表面形成由传统技术中常用作多晶硅或金属栅极线的栅材料,该栅材料作为电容器的接触孔或者底层电极。该栅材料即导电层12和12a可采用多晶硅或金属栅极线,基于导电层12形成的栅极柱则可以为多晶硅栅极柱或金属栅极柱。

53.s103、在导电层12的表面上气相沉积第二层绝缘层24。

54.本发明实施例中,如图5所示,采用等离子体气相沉积(plasma vapor deposition)(25)在导电层12的表面上沉积第二绝缘层24,例如化学气相沉积(chemical vapor deposition,cvd)生成的二氧化硅,磷硅玻璃(phosphosilicate glass,psg)或其类似物,沉积在图3中12和12a之上而后打平。例如,采用化学机械抛光(chemical mechanical polishing,cmp)获得平整的表面形状。图中的光阻剂32是用来遮盖常规电路区域并将金属

‑

氧化层

‑

多晶硅电容器区域曝光并继续进行后续工艺处理。

55.s104、对第二层绝缘层24进行蚀刻,形成对导电层12的局部暴露,同时形成接触孔。

56.s105、对接触孔的开口进行金属填充,形成翅片结构,作为电容器的底板电极即栅极柱。

57.本发明实施例中,如图7所示,采用传统的光刻和蚀刻技术,经过第二绝缘层24,生成与导电层12和12a之间的接孔开口。导电层12将形成电容器的接触孔。采用钨金属对接触孔的开口进行金属填充,形成翅片结构,作为电容器的底板电极即栅极柱。

58.s106、对围绕栅极柱的第二层绝缘层24进行蚀刻,使栅极柱从第二绝缘层24突出,围绕栅极柱形成沟槽。

59.s107、在第二层绝缘层24和栅极柱的表面上气相沉积绝缘介电层13。

60.本发明实施例中,如图6所示,曝光区的氧化物将被等离子体气相蚀刻(26),去除剩余光阻剂32,通过lpcvd(低能量等离子体化学气相沉积)沉积形成均匀的数百埃厚度的电容器极板内部绝缘介电层13。绝缘介电层13的厚度在200至400埃之间,由未掺杂硅酸盐玻璃组成。

61.s108、在绝缘介电层13上沉积并覆盖一层衬底金属层14。

62.本发明实施例中,如图8所示,采用lpcvd方法沉积一层衬底金属层14并覆盖在绝缘介电层13上,衬底金属通常使用氮化钛,接着通过cvd金属处理,例如金属钨,随后通过cmp打平,留下接触孔中的钨柱15。衬底金属层14的复合厚度在50至600埃之间,由钛或者氮化钛组成。

63.s109、在衬底金属层14上沉积并覆盖一层主体金属层30,形成电容器的上极板电极。

64.本发明实施例中,在衬底金属沉积步骤之后,通过掩膜去除多余的衬底金属。掩膜和刻蚀过程之后,在衬底金属层14上沉积并覆盖一层主体金属层30,形成电容器的上极板电极。图9为使用铝/铜的传统金属工艺,该工艺由衬底金属层14,主体金属层30和30a,以及顶层防反射镀层71组成。主体金属层30的厚度在3000至8000埃之间,由铝或者铜组成。

65.图10展示了使用先进铜金属cmp打磨工艺而形成的效果。

66.图11展示了将现有的mom(metal

‑

oxide

‑

metal)结构和本发明的mop(metal

‑

oxide

‑

poly)结构相结合,成为一个全新的三维后端电容器结构。

67.采用本发明实施例的方法,可用于传统半导体平面制备和最先进的finfet制备技术,不仅具有良好的顺畅制备流程,还能保障均匀性。

68.需要说明的是,对于前述的各方法实施例,为了简单描述,故将其都表述为一系列的动作组合,但是本领域技术人员应该知悉,本发明并不受所描述的动作顺序的限制,因为依据本发明,某些步骤可以采用其他顺序或者同时进行。其次,本领域技术人员也应该知悉,说明书中所描述的实施例均属于优选实施例,所涉及的动作和模块并不一定是本发明所必须的。

69.根据本发明实施例的另一个方面,还提供了一种采用上述的制备方法制备而成的金属

‑

氧化层

‑

栅极电容器,电容器包括:底板电极和上极板电极。如图9所示,底板电极和上极板电极形成过程如下。

70.底板电极形成过程:在半导体衬底10上覆盖第一绝缘层11;在第一绝缘层11的表

面形成导电层12;在导电层12的表面上气相沉积第二层绝缘层24;对第二层绝缘层24进行蚀刻,形成对导电层12的局部暴露,同时形成接触孔;对接触孔的开口进行金属填充,形成翅片结构,作为电容器的底板电极即栅极柱。

71.上极板电极形成过程:对围绕栅极柱的第二层绝缘层24进行蚀刻,使栅极柱从第二绝缘层24突出,围绕栅极柱形成沟槽;在第二层绝缘层24和栅极柱的表面上气相沉积绝缘介电层13;在绝缘介电层13上沉积并覆盖一层衬底金属层14;在衬底金属层14上沉积并覆盖一层主体金属层30,形成电容器的上极板电极。

72.需要说明的是,上述金属

‑

氧化层

‑

栅极电容器是采用前述金属

‑

氧化层

‑

栅极电容器的制备方法制备而成,具体的实施过程不再赘述。

73.显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其同等技术的范围之内,则本发明也意图包含这些改动和变型在内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。