利用后道工艺的集成波导式探测器的隔离

1.相关申请的交叉引用

2.本专利申请要求于2018年10月26日提交的题目为“利用后道工艺的集成波导式探测器的隔离(isolation of waveguide

‑

integrated detectors using a back end of line process)”的申请号为62/751,447号的美国临时专利申请的优先权,以及要求于2019年8月15日提交的题目为“用于线性光学量子计算机中散射缓解的热膨胀系数匹配的沟槽填充物(coefficient of thermal expansion

‑

matched trench fill for scatter mitigation in linear optical quantum computer)”的第62/887,364号的美国临时专利申请的优先权,这两件美国临时专利申请所公开的内容通过引用的方式其整体并入到本文中,以用于所有目的。

背景技术:

3.具有高敏感度的光电器件(例如单光子探测器)可以用于许多光子量子技术中,例如用于量子加密和量子计算中。由于光电探测器的高敏感度,其对噪声(例如可以通过直接或间接路径到达光电探测器的不期望的环境光或杂散光)将是非常敏感的。

技术实现要素:

4.本公开总体上涉及光电探测器。更具体地,本公开涉及用于防止背景光到达光子集成电路(pic)中的高敏感度光电探测器(例如,超导纳米线单光子探测器)以实现高敏感度和高信噪比(snr)的技术。根据某些实施例,光子集成电路可以包括使用cmos后道(beol)工艺制造的光隔离结构,以防止环境光或杂散光直接或间接地到达光电探测器。光隔离结构可以包括例如金属层、过孔阵列、空气间隙、填充有反射性或吸收性材料的沟槽等。光隔离结构可以在不同位置(例如,光子集成电路和光电探测器的输入端口和输出端口)向光电探测器和/或波导提供局部和/或全局隔离,使得来自光源或光子集成电路的任何散射的、反射的、扩散的或以其它方式泄漏的光被部分地或完全地阻挡,从而防止到达光电探测器。

5.根据一些实施例,一种器件可以包括:衬底、在衬底上的电介质层、在电介质层内的波导、在电介质层中并耦合至波导的光敏部件、以及在衬底或电介质层中的至少一者中且邻近于光敏部件的多个光隔离结构。多个光隔离结构可以被配置成反射或吸收杂散光,以防止杂散光到达光敏部件。在各种实施例中,多个光隔离结构可以例如包括:在电介质层中的金属沟槽、在电介质层中的金属过孔阵列、在电介质层中的并且在光敏部件顶部上的金属覆盖物、在衬底中的深沟槽,所述深沟槽包括气隙或填充有光反射性材料、光吸收性材料或其任何组合。在一些实施例中,金属覆盖物可以处于金属层中,并且可以与金属沟槽或金属过孔阵列对准或耦合,以形成围绕光敏部件的连续结构。在一些实施例中,波导可包括输入端口,其中金属沟槽或金属过孔阵列可以位于包括输入端口的区域处。光敏部件可以包括单光子探测器,例如超导纳米线单光子探测器。电介质层可以例如包括氧化层。

6.在一些实施例中,多个光隔离结构中的光隔离结构可以包括两个相对侧壁(每个侧壁包括光学隔离层),以及处于两个相对侧壁之间的填充材料,并且所述填充材料由与衬

底或电介质层中的至少一者的热膨胀系数(cte)匹配的cte来表征。填充材料可以是例如多晶硅或二氧化硅。在一些实施例中,所述光学隔离层可以由厚度大于使得组合的所述两个相对侧壁为光学不透明的值来表征。在一些实施例中,所述厚度可以小于60nm。在一些实施例中,光学隔离层可以包括金属氮化物,例如tin、tan、zrn或wn。

7.在一些实施例中,多个光隔离结构可以包括:处于衬底中的第一光隔离结构和电介质层中的第二光隔离结构。第一光隔离结构中的填充材料的cte可以与衬底的cte匹配,第二光隔离结构中的填充材料的cte可以与电介质层的cte匹配。第一光隔离结构可以与第二光隔离结构对准或偏离。

8.在一些实施例中,两个相对侧壁中的每一者还可以包括处于光学隔离层与电介质层或衬底中的至少一者之间的第一粘合层。第一粘合层可以由小于20nm的厚度表征。第一粘合层可以包括例如钛层。在一些实施例中,两个相对侧壁中的每一者还可以包括处于光学隔离层和填充材料之间的第二粘合层。第二粘合层可以由小于20nm的厚度表征,并且可以例如包括钛层。在一些实施例中,所述器件还可以包括处于衬底或电介质层中的未填充的沟槽,其中所述未填充的沟槽的侧壁可以是光学不透明的。

9.根据一些实施例,一种方法,可以包括:接收光子集成电路,所述光子集成电路可以包括衬底、在衬底上的电介质层、波导以及耦合至波导的光敏部件,其中波导和光敏部件处于电介质层中。该方法还可以包括:在电介质层中的蚀刻围绕光敏部件的过孔或沟槽,以暴露衬底的一部分,利用光反射性或光吸收性材料填充过孔或沟槽,在电介质层上和光敏部件的顶部上形成顶部金属覆盖物,以及从与电介质层相对的衬底的背侧蚀刻衬底,以在衬底中形成深沟槽。

10.在一些实施例中,该方法还可以包括利用光反射性或光吸收性材料填充深沟槽。在一些实施例中,所述方法还可以包括:在所述深沟槽的暴露表面上沉积薄粘合层,在所述薄粘合层上沉积薄光学隔离层,以及在所述薄光学隔离层上沉积填充材料层,其中所述填充材料层可填充所述深沟槽并且可以由与所述衬底的热膨胀系数(cte)匹配的cte来表征。在一些实施例中,顶部金属覆盖物处于金属1层中。在一些实施例中,该方法还可以包括:在电介质层上形成附加电介质层和金属层。在一些实施例中,该方法还可包括:在包括波导的输入端口的区域处在电介质层中蚀刻附加的过孔或沟槽,利用光反射性或光吸收性材料填充附加的过孔或沟槽,以及从与电介质层相对的衬底的背侧蚀刻衬底,以在包括波导的输入端口的区域处的衬底中形成附加的深沟槽。

11.根据一些实施例,一种方法,可以包括:接收光子集成电路,该光子集成电路包括衬底和衬底上的电介质层,其中电介质层可以包括光敏部件。该方法还可以包括:在邻近于光敏部件且在电介质层或衬底中的至少一者中蚀刻沟槽,在沟槽的暴露表面上沉积薄粘合层,在薄粘合层上沉积薄光学隔离层,以及在薄光学隔离层上沉积第一填充材料层。第一填充材料层可以填充沟槽,并且可以具有与衬底或电介质层中的至少一个的热膨胀系数(cte)匹配的cte。在一些实施例中,该方法还可以包括:在沉积第一填充材料层之前在薄光学隔离层上沉积第二粘合层。在一些实施例中,该方法还可以包括平面化第一填充材料层。

12.在一些实施例中,沟槽可以在衬底和电介质层两者中,并且第一填充材料层的cte可以与衬底的cte匹配。该方法还可以包括蚀刻填充沟槽的第一填充材料层的一部分,使得沟槽中的第一填充材料层的顶表面与衬底和电介质层之间的交界面对准,在沟槽中沉积第

二填充材料层,并且平面化第二填充材料层。第二填充材料层可以由与电介质层的cte匹配的cte表征。在一些实施例中,蚀刻第一填充材料层的所述一部分可包括使用干蚀刻工艺蚀刻第一填充材料层、薄粘合层和薄光学隔离层,且该方法可进一步包括在沉积第二填充材料层之前,在沟槽的暴露表面上沉积第二粘合层,以及在第二粘合层上沉积第二光学隔离层。

13.本文公开的系统、器件和方法可以通过防止不期望的光到达高敏感度光电探测器来改善光电探测器的信噪比。因此,光电探测器可以获得高敏感度并且可以具有最小量的死区时间。可以利用标准的cmos中道(middle

‑

of

‑

line,mol)工艺或后道(beol)工艺或cmos兼容的beol工艺来制造光隔离结构。一些隔离可以是局部隔离的,并且在堆叠中不需要额外的全局层或材料,因此不会向电路和器件施加额外的热负载。此外,光隔离结构可以包括薄的光学隔离层和具有与形成光隔离结构的材料的热膨胀系数(cte)匹配的cte的材料。因此,光隔离结构的总体cte可以与光子集成电路的其它部分的cte匹配,从而可以减小或最小化由热膨胀失配所引起的内部应力。

附图说明

14.本公开的各个方面以示例的方式例示。参照以下附图描述了非限制性且非穷尽性的各个方面,其中除非另有说明,在各个附图中相同的附图标记指代相同的部件。

15.图1是例示了根据某些实施例的包括光子集成电路(pic)和高敏感度光电探测器的光学器件的示例的简化框图。

16.图2例示了根据某些实施例的在光子集成电路的输入端口和/或输出端口处的杂散光隔离的示例。

17.图3例示了根据某些实施例的利用各种氧化层隔离结构来局部地隔离光电探测器的示例。

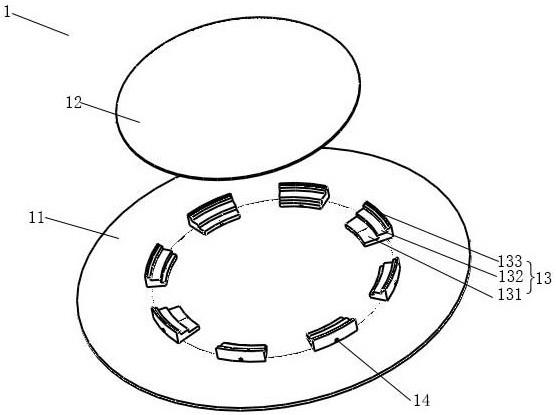

18.图4a至图4d例示了根据某些实施例的在光学器件中利用各种隔离结构来局部地隔离光电探测器的另一示例。图4a是包括光电探测器和光隔离结构的光学器件的截面图。图4b是图4a中的光学器件的立体图。图4c是图4a中的光学器件的俯视图。图4d是图4a中的光学器件的截面的俯视图。

19.图5是例示了根据某些实施例的在光子集成电路中制造各种光隔离结构的示例性方法的流程图。

20.图6是根据某些实施例的包括光电探测器并利用前道工艺制造的光子集成电路的示例的截面图。

21.图7是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路具有利用后道工艺在氧化层中蚀刻的过孔或沟槽。

22.图8是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路具有在氧化层中蚀刻的填充有反射性或吸收性材料(例如,金属)的过孔或沟槽。

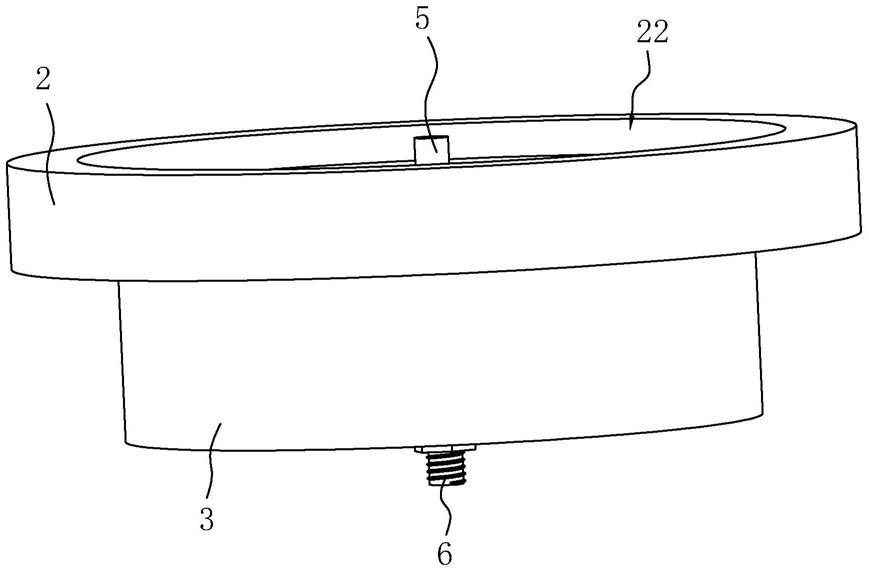

23.图9是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路具有在金属层上制造的用于局部地隔离光电探测器的金属覆盖物。

24.图10是根据某些实施例的在附加的后道工艺之后的光子集成电路的示例的截面图。

25.图11是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路包括在光子集成电路的衬底中蚀刻的深沟槽。

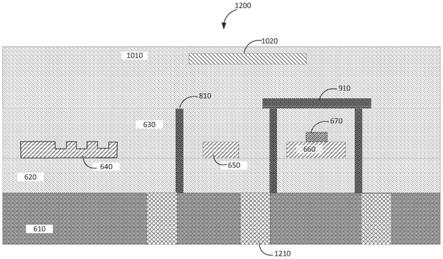

26.图12是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路包括在光子集成电路的衬底中的填充有反射性或吸收性材料的深沟槽。

27.图13是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路例示了在光子集成电路中由各种隔离结构形成的光隔离。

28.图14a例示了硅和铜之间的热膨胀系数(cte)失配。

29.图14b例示了氧化硅的热膨胀系数。

30.图15a是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路包括填充有反射性或吸收性光学隔离材料的沟槽。

31.图15b是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路包括沟槽,该沟槽填充有光学隔离材料和cte匹配材料的薄层。

32.图15c是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路包括沟槽,该沟槽填充有光学隔离材料和cte匹配材料的薄层。

33.图16a至图16g例示了根据某些实施例的制造包括薄光学隔离层和cte匹配材料的光隔离结构的方法的示例。

34.图17a至图17h例示了根据某些实施例的制造包括薄光学隔离层和cte匹配材料的光隔离结构的方法的示例。

35.图18a至图18g例示了根据某些实施例的制造包括薄光学隔离层和cte匹配材料的光隔离结构的方法的示例。

36.图19a至图19h例示了根据某些实施例的制造包括薄光学隔离层和cte匹配材料的光隔离结构的方法的示例。

37.图20是根据某些实施例的光子集成电路的示例的截面图,该光子集成电路包括填充有薄光学隔离层和衬底匹配材料的衬底中的深沟槽。

38.图21是例示了根据某些实施例的在光子集成电路中制造光隔离结构的示例性方法的流程图。

具体实施方式

39.本文公开的技术总体上涉及高敏感度光电探测器。更具体地,本文公开的技术涉及用于防止不期望的背景光(例如杂散光或环境光)到达光子集成电路(photonic integrated circuit,pic)中的高敏感度光电探测器(例如超导纳米线单光子探测器)以实现高敏感度和高信噪比(signal

‑

to

‑

noise ratio,snr)的技术。本文描述了各种包括方法、过程、系统、器件等创新性实施例。

40.在许多光子量子技术中使用的具有高光敏感度的光电探测器,例如单光子探测器(single

‑

photon detector,spd)

‑

例如超导纳米线spd(snspd),可能对多种光辐射非常敏感。在许多情况下,由于各种噪声源(例如包括在系统中的杂散光的背景光或进入系统的环境光),这些高敏感度光电探测器将不能实现它们可潜在实现的敏感度或snr。

41.根据某些实施例,为了改善光电探测器的敏感度和snr,可以利用围绕光电探测器的光隔离结构将光电探测器(例如snspd)与背景辐射(例如环境光或杂散光)光学地隔离。

该光隔离结构可以包括光反射性或吸收性材料,使得光隔离结构可以是光学不透明的。在一些实施例中,可以在pic中的背景光以其它方式传播并到达光电探测器的任何其它位置处添加额外的隔离结构,以减少可能到达光电探测器区域的杂散光子的数量。例如,由于光子集成电路中的背景光或杂散光的一个主要源是由光进入或离开pic的不完全耦合而在pic的光学输入和/或输出端口(例如,输入或输出波导耦合器)处反射、散射或漫射的光,因此可以在光学输入和/或输出端口处使用隔离结构,以防止杂散光进入到pic的内部。这样,可以显著地降低任何杂散光或环境光可进入波导或到达光电探测器区域的概率。此外,如果任何背景光可到达光电探测器所在的区域,则围绕光电探测器的局部光隔离结构可以阻挡背景光,以防止该背景光被光电探测器探测到。在各种实施例中,可以利用标准的cmos后道(back

‑

end

‑

of

‑

line,beol)工艺或其它cmos兼容的制造工艺来制造光隔离结构。

42.根据某些实施例,当pic的处理温度(例如,大于约700k)冷却到操作温度(例如,小于约4k)时,为了减小由光隔离结构中的光反射性或吸收性材料和光隔离结构的其它部分之间的热膨胀系数不匹配所引起的应力或损坏,可以在pic中的沟槽的内表面上沉积一个或多个薄的不透明层和粘合层以用于光隔离,然后可以用透明或非透明材料填充沟槽,该透明或非透明材料的cte与形成该沟槽的材料的cte大致匹配。因此,光隔离结构可以与pic的其余部分以大致相同的速率膨胀或收缩,以减少pic中的内应力和潜在的损坏或缺陷。

43.现在将参照构成本文一部分的附图来描述一些例示性的实施例。随后的描述仅提供一个或多个实施例,而并不旨在限制本公开的范围、适用性或配置。相反,一个或多个实施例的随后描述将为本领域技术人员提供用于实施一个或多个实施例的可能性描述。应当理解,在不脱离本公开的精神和范围的情况下,可以对元件的功能和布置进行各种改变。在下面的描述中,出于解释的目的,提出了具体的细节,以便提供对某些发明实施例的透彻理解。然而,显然也可以在没有这些具体细节的情况下来实践各种实施例。这些附图和描述并不旨在用于限制。本文使用的词汇“示例”或“示例性的”用于表示“用作示例、实例或例示”。在本文描述为“示例性的”或“示例”的任何实施例或设计并不必须地解释为比其它实施例或设计更优选或更有利。

44.图1是例示了根据某些实施例的包括光子集成电路(photonic integrated circuit,pic)120和高敏感度光电探测器130的光学器件100的示例的简化框图。pic 120可以包括由波导和其它有源或无源光学部件(例如滤波器、谐振器、分路器、光学放大器等)形成的光子电路。光学器件可以包括光源,例如激光器110,该激光器可以是超快(例如皮秒或飞秒)脉冲激光器。在一些实施例中,光源可以是外部源,并且可以通过例如一个或多个光纤连接到pic 120。来自光源的光可以通过耦合器(例如光栅耦合器、边缘耦合器等)耦合至pic 120中的波导中。然而,可能难以获得非常高的耦合效率。例如,在许多情况下,耦合效率将小于90%、小于75%、小于60%、或小于50%。因此,来自光源的大量光将不进入pic 120中的波导,而是可能被反射、散射或漫射,并且变成杂散光140。杂散光140将被光学器件100中的结构或部件(例如金属层、不同材料之间的交界面等)反射、折射、衍射或以其它方式偏转。因此,一部分的杂散光140将最终到达光电探测器130。此外,pic 120中的一些部分也将从期望路径泄漏光。例如,例如当波导具有急转弯或者在波导或其它光子电路中存在缺陷时,光将耦合出波导,而不是在光子电路内被引导以到达光电探测器130。从光子电路泄漏出的光将变成杂散光150,杂散光150也将至少部分地偏转到光电探测器130。在一些实

施例中,环境光也将例如通过氧化层进入到pic 120中和/或被金属层反射。

45.光电探测器130可以是高敏感度光电探测器,例如单光子探测器。例如,在一些实施例中,光电探测器130可以包括可以探测单个光子的超导纳米线单光子探测器。在一个实施例中,光电探测器130可以包括耦合至超导纳米线(例如铌锗纳米线)的波导,所述超导纳米线在超导状态下可以具有超低电阻。超导纳米线可以是光敏的或光活性的,例如对于光子具有吸收性。例如,经过波导的光子可以被超导纳米线吸收并导致超导纳米线变成非超导的(即,改变电阻或阻抗)。可以将纳米线中的电阻或阻抗变化转换成指示探测到一个或多个光子的电探测信号(例如,电流或电压信号)。

46.当至少一部分的杂散光140和150到达光电探测器130时,这将导致超导纳米线改变状态,并且光电探测器130将生成指示探测到一个或多个光子的探测信号,即使没有光子从波导到达超导纳米线,或者探测信号的大小可能不正确地指示从波导到达光电探测器的光子的数量。因此,可能由光电探测器130生成错误的探测信号或不正确的(例如,噪声)探测信号,这将降低光电探测器130的有效敏感度或信噪比。

47.根据某些实施例,可以在光学器件100的不同位置处添加光隔离结构以阻止杂散光或环境光到达光电探测器130。例如,可以在pic 120的输入端口处添加隔离结构160;可以制造隔离结构170以围绕光电探测器130;并且可以在光学器件100中的以其它方式传播背景光的任何位置添加隔离结构180。在以下示例中描述了光隔离结构及其制造工艺的一些实施例的更多细节。

48.图2示出了根据某些实施例的在光子集成电路200的输入和/或输出端口处的杂散光隔离的示例。图2示出了pic 200的截面图,pic 200可以包括在衬底205(例如,硅处理晶片)上制造的波导210。pic 200还可以包括用于波导210的输入端口220和用于波导210的输出端口230。波导210可以将光从输入端口220引导到pic 200的内部或者可以通过输出端口230将光引导出pic 200,其中一些感光部件可以位于pic 200的内部。

49.如上所述,光可能不会在输入端口220或输出端口230处完全地耦合至波导210中或从波导210耦合出。显著部分的输入光或输出光将通过路径而不是波导210进入pic 200。在一些情况下,在每个激光脉冲中,大约1012个光子将作为杂散光进入pic 200。为了防止这些光子到达pic 200的内部,可以在输入端口和/或输出端口处制造一个或多个光隔离结构。例如,如图2所示,pic 200可以包括可用作图1中所示的隔离结构160的一个或多个金属沟槽240和一个或多个深沟槽260。金属沟槽240可以包括金属层,该金属层足够厚以阻挡(例如,反射或吸收)入射光子。金属沟槽240可用作镜状阻挡层,并且可从例如金属1层(m1,其可位于波导210上方约1m处)向下延伸至衬底205(其可以位于波导210下方约2m至3m处),以阻挡将在波导210的包覆层中传播的光到达pic 200的内部。深沟槽260可以延伸经过pic 200的衬底205,并且可以是空的(即,气隙)或者可以填充反射性或吸收性材料,以至少部分地反射性或吸收将在衬底205中传播或将从衬底205散射的入射光子,使得光子不会进入到波导的包覆层。

50.在相邻的金属沟槽240之间可以存在间隙250,使得波导210可以穿过金属沟槽240之间的间隙。相邻的深沟槽260之间可以存在间隙270,使得波导210可以在间隙270处由衬底支撑。如图2所示,间隙250和间隙270可以是不对准的,并且可以彼此偏移一定距离,使得间隙250可以不在来自输入端口220的杂散光子的视线(line of sight)内,并因此来自输

入端口220的杂散光子可以不经过间隙250而可以被金属沟槽240阻挡。

51.图3例示了根据某些实施例的在光子集成电路300中利用各种隔离结构来局部地隔离光电探测器350的示例。pic 300可以包括衬底305(例如,硅处理晶片)。波导310可以形成在衬底305上,其中波导310可以包括多个转弯以改变方向。可以在pic 300中制造光隔离结构,例如顶部金属覆盖物320、金属沟槽330和深沟槽340,以围绕并隔离波导310和光电探测器350。图3所示的光隔离结构可以是图1的隔离结构170的具体实施例,并且可以形成为类似于城堡状(castle

‑

like)结构的隔离结构。

52.如图3所例示的,波导310可以将信号光从pic 300中的光子电路引导到光电探测器350(例如,snspd),在光电探测器350处可以探测信号光。类似于深沟槽260,深沟槽340可以包括完全地穿过衬底305的气隙,或者可以填充有反射性或吸收性材料。在一些实施例中,深沟槽340可以部分地穿过衬底305。深沟槽可以将光探测器350与将衬底305中传播或将从衬底305散射的光隔离。金属沟槽330可以类似于金属沟槽240,并且可以形成镜状阻挡层,该镜状阻挡层可以从m1向下延伸到衬底305,如上文关于图2描述的。在一些实施例中,金属沟槽330可以包括以光电探测器350为中心的多个嵌套环,其中内环可由一个或多个外环包围。每个环可以包括波导310可穿过的开口。每个环中的开口可以相对于相邻环的开口而位于不同侧(例如,相对侧或相邻侧)。金属沟槽330可以阻挡在波导310的包覆层中传播的光到达光电探测器350。顶部金属覆盖物320可用作光隔离结构的顶(其可以类似于城堡状结构),并且可以防止光从光探测器350和pic 300的顶部到达光探测器350。

53.图4a至图4d例示了根据某些实施例的在光学器件400中利用各种隔离结构来局部地隔离光电探测器470的另一示例。图4a是包括光电探测器470和围绕光电探测器470的光隔离结构的光学器件400的截面图。图4b是图4a中所示的光学器件400的立体图。光学器件400可以包括衬底410(例如,硅处理晶片)、阻挡氧化(box)层420(例如,二氧化硅)、形成在box层420的顶部上的波导440、以及覆盖波导440的低温氧化(lto)层430。光学器件400还可以包括过孔450阵列以及可以形成在金属1层上的顶部金属覆盖物460。

54.图4c是图4a中的光学器件400的俯视图。图4c示出了从顶部覆盖光电探测器470的顶部金属覆盖物460,使得背景光将不能从顶部到达光电探测器470,其中顶部金属覆盖物460可以是金属1层的一部分。

55.图4d是图4a中的光学器件400的截面的俯视图。图4d示出了过孔阵列450和光电探测器470的布置。如图所例示的,过孔阵列450可布置成二维阵列,其中一行(或列)中的过孔可以与相邻行(或列)中的过孔偏离,使得过孔阵列可以有效地形成壁。光电探测器470可以包括在波导440上的光活性纳米线480(例如,铌锗纳米线)。

56.图5是例示了根据某些实施例的在光子集成电路中制造各种光隔离结构的示例性方法的流程图500。即使图5以一定顺序流来描述操作,但也可以并行地或同时地执行一些操作。可以以不同的顺序来执行一些操作。操作可以具有未包括在图中的附加步骤。一些操作是可选的,因此在各种实施例中可以省略这些操作。一些操作可以与其它操作一起执行。

57.可选地,在框510处,可以在pic的阻挡氧化层(例如图4a和图4b中所示的box层420)上形成波导层。可以利用例如光刻技术对波导层进行图案化和蚀刻,以形成波导芯和/或输入/输出耦合器。在框520,可以在波导层的顶部沉积光活性层(例如铌锗层)。光活性层可以被图案化和蚀刻以在波导芯的区域上形成纳米线。在框510和框520处的处理可以是

cmos工艺中的前道(front end of line)工艺的一部分。

58.图6是根据某些实施例的光子集成电路600的示例的截面图,该光子集成电路600包括在框510和框520处利用前道工艺制造的光电探测器。pic 600可以包括衬底610(例如,硅处理晶片)、形成在衬底610上的box层620、器件层上的各种器件(例如,光学输入/输出耦合器640、波导650、以及包括波导660和含有光活性材料的纳米线670的光电探测器)、以及覆盖器件层的氧化层630。光学输入/输出耦合器640可以包括光栅耦合器。氧化层630和box层620可用作波导650的包覆层。在一个示例中,氧化层630可以具有约1m的厚度。

59.在框530,可以在氧化层中向下蚀刻过孔或沟槽至衬底。例如,可以在氧化层(例如,lto层和box层)上形成图案化的掩膜层,并且可以选择性使用湿法或干法蚀刻技术在氧化层中蚀刻过孔(洞)或沟槽,该图案化的掩膜层可以具有例如3m至4m的总厚度。

60.图7是根据某些实施例的光子集成电路700的示例的截面图,该光子集成电路700具有在框530处利用后道(back

‑

end

‑

of

‑

line,beol)工艺在氧化层中蚀刻的过孔或沟槽710。pic700可由pic 600制成。可以通过氧化层630和box层620向下蚀刻过孔或沟槽710至衬底610。

61.在框540,过孔或沟槽可以填充有反射性或吸收性材料,例如金属材料。例如,可以在氧化层上沉积金属层,并且以一个或多个周期进行选择性地蚀刻,以在过孔或沟槽中形成金属塞(metal plug)。

62.图8是根据某些实施例的光子集成电路800的示例的截面图,该光子集成电路800具有在框540处利用beol工艺在氧化层中蚀刻的填充有反射性或吸收性材料(例如金属,如铜、铝、钴、钨等)的过孔或沟槽。pic 800可由pic 700制成,其中过孔或沟槽710可以填充有金属塞810。

63.在框550,可以使用标准cmos beol处理技术在氧化层上沉积金属1层并且蚀刻金属1层,以在光电探测器顶部的区域中留下顶部金属覆盖物。顶部金属覆盖物可以与填充有反射性或吸收性材料(例如金属)的过孔或沟槽对准。因此,顶部金属覆盖物和过孔或沟槽可阻挡来自至少3个方向(例如,上侧、左侧和右侧)或5个方向(例如,上侧、左侧、右侧、前侧和后侧)的背景光。

64.图9是根据某些实施例的光子集成电路900的示例的截面图,该光子集成电路900具有顶部金属覆盖物910,该顶部金属覆盖物910被制造为金属层的一部分,以用于对在框550处利用beol工艺的光电探测器进行局部地隔离。pic 900可以由pic 800制成,并且可以包括形成为金属1层的一部分的附加的顶部金属覆盖物910。顶部金属覆盖物910可以位于包括波导660和纳米线670的光电探测器的上方(例如,在光电探测器的顶部上)。顶部金属覆盖物910可以与过孔或沟槽710中的金属塞810接触,以阻挡来自在二维截面图中的上侧、左侧和右侧方向的光。

65.可选地,在框560,可以执行其它beol工艺以形成例如附加电介质(例如氧化)层和上部金属层(例如,金属2层、金属3层等)。这些beol工艺可以包括标准cmos beol工艺。

66.图10是根据某些实施例的在框560处的附加的beol处理之后的光子集成电路1000的示例的截面图。pic 1000可以由pic 900制成,并且可以包括附加的金属层1010和上级金属层,例如金属层1020。

67.在框570,可以从背侧蚀刻衬底,以从背侧在衬底中形成深沟槽。深沟槽可以反射

在衬底材料和气隙之间的交界面处在衬底内传播的光子。例如,当光子以一定角度入射在从衬底材料到气隙的交界面上时,可能发生全内反射。

68.图11是根据某些实施例的光子集成电路1100的示例的截面图,该光子集成电路1100包括在框570处利用beol工艺在光子集成电路的衬底中蚀刻的沟槽1110。pic 1100可以由pic 1000制成,并且可以包括衬底610中的沟槽1110。沟槽1110可偏离金属塞810。例如,沟槽1110可以比金属塞810稍微远离光电探测器,以防止光从衬底610和box层620的底侧绕过金属塞810并到达光电探测器。

69.可选地,在框580,可以用可阻挡光的反射性或吸收性材料(例如金属材料)填充深沟槽。

70.图12是根据某些实施例的光子集成电路1200的示例的截面图,该光子集成电路1200包括在框580处利用工艺填充有反射性或吸收性材料的衬底中的深沟槽。pic 1200可以由pic 1100制成,并且可以包括填充在沟槽1110中的反射性或吸收性材料1210(例如金属材料)。

71.图13是根据某些实施例的光子集成电路1200的截面图,该光子集成电路1200例示了在光子集成电路中由各种隔离结构形成的光隔离。来自激光器的光可以经由输入光纤1310发送到pic 1200,输入光纤1310可以包括准直器,例如grin透镜或微透镜。来自输入光纤1310的输入光1320可以经由氧化层传播并且可以凭借光学输入/输出耦合器640部分地耦合至pic 1200中的波导中,在一些实施例中,光学输入/输出耦合器640可以包括倾斜光栅。

72.未凭借光学输入/输出耦合器640耦合至波导中的光将在各个方向上散射。例如,输入光1320的一部分可以在衬底610和box层620之间的交界面处作为光1330反射,该光1330可以进一步被金属层1020作为光1370反射,该光1370可以被金属塞810中的一者阻挡。输入光1320的一部分可以作为光1335散射,光1335可以朝向金属插头810传播并且被金属插头阻挡。输入光1320的一部分可在衬底610的底表面处散射,其中散射光1350的一部分可被沟槽1110中的反射性或吸收性材料1210阻挡,而散射光1340的另一部分可被金属塞810阻挡。

73.从波导650散射或以其它方式泄漏的光1360也可以被金属塞810阻挡而不会到达光电探测器。可以从顶部进入氧化层的环境光1380或者由各种金属层反射的杂散光可以被光电探测器顶部上的顶部金属覆盖物910阻挡,因此也不会到达光电探测器。以这种方式,只有在波导660中引导的光子可以到达光电探测器,因此可以显著地降低或基本上消除背景噪声。因此,可以通过光电探测器获得高敏感度和高snr。

74.在各个实施例中,在cmos处理过程中使用的其它电介质层可以用于替换上述的一个或多个氧化层(例如,二氧化硅层)。例如,电介质层可以包括氮化硅、碱卤化物(alkali halides)、钛酸钡、钛酸铅、氧化钽、氧化钨、氧化锆等。

75.一些上述工艺,例如氧化物和金属沉积工艺,可能需要在升高的温度(例如700k或更高)下执行。此外,可能需要在高温下将pic结合到电子集成电路和/或印刷电路板。然而,为了处于超导状态,单光子探测器中的超导纳米线可能需要在低温(例如,小于等于约4k)下操作。因此,至少围绕超导纳米线的区域可能需要在正常操作期间冷却到低温温度。因此,邻近超导纳米线的光隔离结构可能从制造环境到操作环境经历大的温度变化。

76.如上所述,诸如金属(包括铜、铝、钴、钨等)的反射性或吸收性材料可用于填充沟槽(例如沟槽1110),以阻挡杂散光或环境光到达敏感的单光子探测器。然而,大多数金属,例如铜和钨,可能具有比硅和sio2高得多的热膨胀系数(cte)。因此,当将pic从处理温度(例如,大于等于4k)冷却到操作温度(例如,小于等于4k)时,在沟槽中填充材料的热收缩量和pic的其它材料的热收缩量之间可能存在很大的差异,并且因此在沟槽附近存在可能影响pic的机械稳定性和性能的大量的诱发应变(induced strain)。

77.图14a示出了硅和铜之间的cte失配。曲线1410示出了随着接近0k到约273k的温度变化的硅(例如图13中所示的硅衬底610)的cte。对于特定温度变化(例如,在0k至273k之间),硅的热膨胀(或收缩)的总百分比可以是曲线1410以下的区域。曲线1420示出了随着从0k到约273k的温度变化的铜的cte,铜可以用作图13中所示的沟槽填充材料1210。对于特定温度变化(例如,在0k至10k之间),铜的热膨胀(或收缩)的总百分比可以是曲线1420下的区域。如图14a所示,在给定温度下,铜将具有比硅高得多的热膨胀系数。因此,对于相同的温度变化,铜的热膨胀(或收缩)的总百分比将远大于硅的热膨胀(或收缩)的总百分比。钨的cte比铜小但比硅大得多,因此对于相同的温度变化,钨的热膨胀(或收缩)的总百分比将远大于硅的热膨胀(或收缩)的总百分比。因此,如果沟槽的尺寸以及因此填充沟槽的金属材料的尺寸相对较大,则沟槽中的金属材料的总体热膨胀与相邻硅材料的总体热膨胀之间的差异将会很大。因此,将在沟槽周围诱发大的应力,这将导致pic的损坏或缺陷和/或将改变pic中的波导和其它部件的光学性质(例如,光学损耗、引导模式、偏振性质等)。

78.图14b示出了氧化硅的热膨胀系数。曲线1430示出了随着从0k到约300k的温度变化的氧化硅(例如上述的box层620或氧化层630)的cte。如图例示的,在一定温度下的氧化硅的cte将低于在相同温度下的硅的cte,并且将远低于在相同温度下的铜或钨的cte。因此,铜、钨与氧化硅之间的cte失配甚至会大于铜与硅之间的cte失配。

79.图15a是根据某些实施例的光子集成电路1500的示例的截面图,该光子集成电路1500包括填充有反射性或吸收性光学隔离材料的沟槽。作为上述pic,光子集成电路1500可以包括硅衬底1510、box层1520和包覆层1530(例如,氧化硅层)。可以在box层1520和包覆层1530中形成超导纳米线单光子探测器(superconducting nanowire single

‑

photon detector,snspd)1540。为了隔离snspd 1540,可以在邻近于snspd 1540的box层1520和包覆层1530中形成金属塞1550(类似于例如金属塞810)。金属塞1550可以包括例如填充有钨或其它金属、金属合金或金属化合物的过孔或沟槽。可以在硅衬底1510、box层1520和包覆层1530中形成额外的光隔离结构1560,以防止杂散光在各个方向上到达snspd 1540并穿过各种材料层(例如硅衬底1510)。光隔离结构1560可以填充有反射性或吸收性光学隔离材料,例如金属(如铜或钨)、金属合金或金属化合物(例如金属氮化物)。

80.如上所述,由于光隔离结构1560的尺寸可以相对较大,所以当光子集成电路1500的温度显著变化时,光隔离结构1560中的金属的热膨胀将远大于硅衬底1510中的硅和box层1520和包覆层1530中的氧化硅的热膨胀。因此,将在光子集成电路1500中引入大的机械应力。

81.根据某些实施例,当pic 1500从处理温度(例如,大于700k)冷却到操作温度(例如,小于等于约4k)时,为了减小由pic 1500的光隔离结构1560和其它部分之间的cte失配所引起的应力和潜在损坏,可以在用于光隔离结构1560(其可以具有几微米或几十微米的

线性尺寸)的沟槽的内表面上沉积一个或多个薄光学隔离层(例如,具有小于100nm(纳米)的厚度,例如,具有小于等于约50nm、约60nm或约70nm的厚度),然后可以利用具有与在其中形成沟槽的衬底或其它层的cte近似匹配的cte的材料填充沟槽。光隔离结构中的光学隔离层的组合可以是光学不透明的。因此,包括薄光学隔离层和cte匹配填充材料的光隔离结构1560可以与pic的其余部分以近似相同的速率膨胀,以减小pic中的内部应力和潜在的损坏或缺陷。

82.图15b是根据某些实施例的光子集成电路1502的示例的截面图,该光子集成电路1502包括填充有光学隔离材料和cte匹配材料的薄层的沟槽。作为光子集成电路1500,光子集成电路1502可以包括硅衬底1512、box层1522和包覆层1532(例如,氧化硅层)。可以在box层1522和包覆层1532中形成超导纳米线单光子探测器1542。为了隔离snspd 1542,可以在邻近于snspd 1542的box层1522和包覆层1532中形成金属塞1552(类似于例如金属塞810)。金属塞1552可以包括例如用钨或其它金属、金属合金或金属化合物填充的过孔或沟槽。可以在硅衬底1512、box层1522和包覆层1532中形成额外的光隔离结构1562,以防止杂散光或环境光在各个方向上到达snspd 1542并穿过各种材料层(例如硅衬底1512)。

83.每个光隔离结构1562可以在形成光隔离结构1562的沟槽的每个侧壁和底表面上包括粘合层1582(例如,具有约2nm至约10nm厚度的ti层)和光学隔离层1592(例如,具有约25nm至约60nm厚度的tin、tan、zrn或wn层)。光隔离结构1562中的两个相对侧壁中的两个光学隔离层1592的总厚度可以是例如约50nm至约120nm。因此,两个光学隔离层1592的组合可以是光学不透明的。粘合层1582可以有助于改善光学隔离层1592与硅衬底1512和氧化层(例如,box层1522和包覆层1532)之间的粘合性。可以用多晶硅填充硅衬底1512内的光隔离结构1562的一部分1563,并且可以用氧化硅填充box层1522和包覆层1532内的光隔离结构1562的一部分1572。因此,硅衬底1512内的光隔离结构1562的一部分(包括粘合层1582、光学隔离层1592和部分1563)可以具有与硅的cte近似匹配的cte,而box层1522和包覆层1532内的光隔离结构1562的一部分(包括粘合层1582、光学隔离层1592和部分1572)可以具有与氧化硅的cte近似匹配的cte。因此,光隔离结构1562可以与硅衬底1512、box层1522和包覆层1532以近似相同的速率膨胀,以减少pic中的内部应力和潜在的损坏或缺陷。

84.图15c是根据某些实施例的光子集成电路1504的示例的截面图,该光子集成电路1504包括填充有光学隔离材料和cte匹配材料的薄层的沟槽。作为光子集成电路1502,光子集成电路1504可以包括硅衬底1514、box层1524和包覆层1534(例如,氧化硅层)。可以在box层1524和包覆层1534中形成超导纳米线单光子探测器1544。为了隔离snspd 1544,可以在邻近于snspd 1544的box层1524和包覆层1534中形成金属塞1554(类似于例如金属塞810)。金属塞1554可以包括例如用钨或其它金属、金属合金或金属化合物填充的过孔或沟槽。可以在硅衬底1514、box层1524和包覆层1534中形成额外的光隔离结构1564,以防止杂散光或环境光在各个方向上到达snspd 1544并穿过各种材料层(例如硅衬底1514的)。

85.每个光隔离结构1564可以包括第一粘合层1584(例如,具有约2nm至约10nm厚度的ti层)、光学隔离层1594(例如,具有约25nm至约60nm厚度的tin、tan、zrn或wn层)、以及在形成光隔离结构1564的沟槽的每个侧壁和底表面上的第二粘合层1586。光隔离结构1562中的两个相对侧壁中的两个光学隔离层1592的总厚度可以是例如约50nm至约120nm。因此,单独或组合的两个光学隔离层1594可以是光学不透明的。第一粘合层1584可以有助于改善光学

隔离层1594与硅衬底1514或氧化层(例如,box层1524和包覆层1534)之间的粘合性。硅衬底1514内的光隔离结构1564的一部分1565可填充有多晶硅,并且box层1524和包覆层1534内的光隔离结构1564的一部分1574可填充有氧化硅。第二粘合层1586可以有助于改善沟槽中的光学隔离层1594与多晶硅(部分1565)和二氧化硅(部分1574)之间的粘合性。因此,在硅衬底1514内的光隔离结构1564的一部分(包括粘合层1586、光学隔离层1594和部分1565)可以具有与硅的cte近似匹配的cte,在box层1524和包覆层1534内的光隔离结构1564的一部分(包括粘合层1586、光学隔离层1594和部分1574)可以具有与氧化硅的cte近似匹配的cte。因此,光隔离结构1564可以与硅衬底1514、box层1524和包覆层1534以近似相同的速率膨胀,以减少pic中的内部应力和潜在的损坏或缺陷。

86.图16a至图16g例示了根据某些实施例的制造包括薄光学隔离层和cte匹配材料的光隔离结构(例如,光隔离结构1562)的方法的示例。图16a示出了在光子集成电路中形成的沟槽1650。光子集成电路包括在硅衬底1610上的氧化硅层1620,其中在氧化硅层1620中制造有超导纳米线单光子探测器1630和金属塞1640。可以利用各种选择性蚀刻技术(例如光刻和干法蚀刻技术)形成沟槽1650。可以从氧化硅层1620侧或从硅衬底1610侧蚀刻沟槽1650。在一些实施例中,沟槽1650可以蚀刻穿过氧化硅层1620和硅衬底1610两者。

87.图16b例示了具有薄粘合层1660和薄光学隔离层1662的光子集成电路,薄粘合层1660和薄光学隔离层1662共形地沉积在沟槽1650的暴露表面上和氧化硅层1620的顶表面上。如上所述,粘合层1660可有助于改善光学隔离层1662与沟槽1650的侧壁和底表面的粘合性。粘合层1660可以包括例如具有几纳米(例如约2nm至约10nm)厚度的钛(ti)层。可以利用例如原子层沉积(atomic layer deposition,ald)、化学气相沉积(chemical vapor deposition,cvd)、物理气相沉积(physical vapor deposition,pvd)等将粘合层1660沉积在沟槽1650的暴露表面上和氧化硅层1620的顶表面上。光学隔离层1662可以包括例如金属氮化物(例如tin、tan、zrn、wn或其任何组合),并且可以具有大约几十纳米(例如约25nm至约60nm)的厚度。可以利用例如ald、cvd、pvd等将光学隔离层1662沉积在粘合层1660上。

88.图16c例示了多晶硅层1670沉积在光子集成电路上并填充沟槽1650。可以例如通过cvd或pvd将多晶硅层1670沉积在光子集成电路上。图16d示出了已通过例如化学机械抛光(chemical mechanical polishing,cmp)平坦化以暴露光学隔离层1662的多晶硅层1670,其中随后可通过例如选择性湿法蚀刻将光学隔离层1662与粘合层1660一起去除。

89.图16e例示了填充沟槽1650的多晶硅层1670的一部分,该部分是可以通过湿法蚀刻工艺选择性地蚀刻到大致与硅衬底1610和氧化硅层1620之间的交交界面对准的水平的部分。因此,多晶硅层1670的一部分可保留在沟槽1650中,而多晶硅层1670的剩余部分的顶表面可以大致上与硅衬底1610与氧化硅层1620之间的交交界面对准。

90.图16f示出了沉积在氧化硅层1620上的氧化硅层1680。氧化硅层1680可再次填充沟槽1650。可以利用例如cvd或pvd将氧化硅层1680沉积在光子集成电路上。

91.图16g示出了已通过例如化学机械抛光而平坦化的氧化硅层1680。因此,光子集成电路可以包括与光隔离结构1562类似的光隔离结构1664,并且每个光隔离结构1664包括由侧壁包围的多晶硅层1670的一部分和氧化硅层1680的一部分,其中所述侧壁包括粘合层1660和光学隔离层1662。

92.图17a至图17h例示了根据某些实施例的制造包括薄光学隔离层和cte匹配材料的

光隔离结构的方法的示例。图17a示出了在光子集成电路中形成的沟槽1750。光子集成电路包括在硅衬底1710上的氧化硅层1720,其中在氧化硅层1720中制造有超导纳米线单光子探测器1730和金属塞1740。可以利用各种选择性蚀刻技术(例如光刻和干法或湿法蚀刻技术)形成沟槽1750。可以从氧化硅层1720侧或从硅衬底1710侧蚀刻沟槽1750。在一些实施例中,沟槽1750可以蚀刻穿过氧化硅层1720和硅衬底1710两者。

93.图17b例示了具有薄粘合层1760和薄光学隔离层1762的光子集成电路,薄粘合层1760和薄光学隔离层1762共形地沉积在沟槽1750的暴露表面上和氧化硅层1720的顶表面上。如上所述,粘合层1760可有助于改善光学隔离层1762与沟槽1750的侧壁和底表面的粘合性。粘合层1760可以包括例如具有几纳米(例如约2nm至约10nm)厚度的钛层。可以利用例如ald、cvd、pvd等将粘合层1760沉积在沟槽1750的暴露表面上和氧化硅层1720的顶表面上。光学隔离层1762可以包括例如金属氮化物(例如tin、tan、zrn、wn或其任何组合),并且可以具有大约几十纳米(例如约25nm至约60nm)的厚度。可以利用例如ald、cvd、pvd等将光学隔离层1762沉积在粘合层1760上。

94.图17c例示了多晶硅层1770沉积在光子集成电路上并填充沟槽1750。可以通过例如cvd或pvd将多晶硅层1770沉积在光子集成电路上。图17d示出了已通过例如化学机械抛光来平坦化以暴露光学隔离层1762的多晶硅层1770,其中随后可通过例如选择性湿法蚀刻将光学隔离层1762与粘合层1760一起去除。

95.图17e例示了填充沟槽1750的多晶硅层1770的一部分,该部分是可以通过干法蚀刻工艺(例如等离子体蚀刻(诸如rie))选择性地蚀刻到与硅衬底1710和氧化硅层1720之间的交界面更精确地对准的水平的部分。因此,可以在氧化硅层1720中形成沟槽1752,并且多晶硅层1770的一部分可以保留在沟槽1750中,而多晶硅层1770的剩余部分的顶表面可以与硅衬底1710和氧化硅层1720之间的交界面对准。

96.图17f示出了可以共形地沉积在沟槽1752的暴露表面上和氧化硅层1720的顶表面上的薄粘合层1764和薄光学隔离层1766。如上所述,粘合层1764可有助于改善光学隔离层1766与沟槽1752的侧壁和底表面的粘合性。粘合层1764可以包括例如具有几纳米(例如约2nm至约10nm)厚度的钛层。粘合层1764可以具有与粘合层1760的厚度类似的厚度。可以利用ald、cvd、pvd等在沟槽1752的暴露表面上和氧化硅层1720的顶表面上沉积粘合层1764。光学隔离层1766可以包括金属氮化物(例如tin、tan、zrn、wn或其任何组合),并且可以具有与光学隔离层1762的厚度类似的厚度。例如,光学隔离层1766的厚度可以是大约几十纳米,例如约25nm至约60nm。可以利用例如ald、cvd、pvd等将光学隔离层1766沉积在粘合层1764上。

97.图17g示出了沉积在氧化硅层1720上的氧化硅层1780。氧化硅层1780可以填充沟槽1752。可以通过例如cvd或pvd将氧化硅层1780沉积在光子集成电路上。

98.图17h示出了已通过例如化学机械抛光而平坦化的氧化硅层1780。可以例如通过选择性干法蚀刻或湿法蚀刻去除粘合层1764和光学隔离层1766。因此,光子集成电路可以包括光隔离结构1768,每个光隔离结构1768包括由侧壁包围的氧化硅层1780的一部分和多晶硅层1770的一部分,其中所述侧壁包括粘合层1760或1764和光学隔离层1762或1766。

99.如上文关于图15c所述的,为了改善光学隔离层1594与填充深沟槽以形成光隔离结构的多晶硅或氧化硅之间的粘合,可以在光学隔离层1594与填充深沟槽的多晶硅或氧化

硅之间使用第二粘合层1586。

100.图18a至图18g示出了根据某些实施例的制造包括薄光学隔离层和cte匹配材料的光隔离结构(例如,光隔离结构1564)的方法的示例。图18a示出了在光子集成电路中形成的沟槽1850。光子集成电路包括在硅衬底1810上的氧化硅层1820,其中在氧化硅层1820中制造有超导纳米线单光子探测器1830和金属塞1840。可以利用各种蚀刻技术(例如光刻和干法或湿法蚀刻技术)形成沟槽1850。可以从氧化硅层1820侧或从硅衬底1810侧蚀刻沟槽1850。在一些实施例中,沟槽1850可以蚀刻穿过氧化硅层1820和硅衬底1810两者。

101.图18b例示了具有第一粘合层1860、薄光学隔离层1862和第二粘合层1864的光子集成电路,第一粘合层1860、薄光学隔离层1862和第二粘合层1864共形地沉积在沟槽1850的暴露表面上和氧化硅层1820的顶表面上。如上所述,第一粘合层1860可有助于改善光学隔离层1862与沟槽1850的侧壁和底表面的粘合性。第一粘合层1860可以包括例如具有几纳米(例如约2nm至约10nm)厚度的钛层。可以利用例如ald、cvd、pvd等将第一粘合层1860沉积在沟槽1850的暴露表面上和氧化硅层1820的顶表面上。光学隔离层1862可以包括例如金属氮化物(例如tin、tan、zrn、wn或其任何组合),并且可以具有大约几十纳米(例如约25nm至约60nm)的厚度。可以利用例如ald、cvd、pvd等将光学隔离层1862沉积在第一粘合层1860上。第二粘合层1864可有助于改善光学隔离层1862与沟槽1850中的材料的粘合性。第二粘合层1864可以包括例如具有几纳米(例如约2nm至约10nm)厚度的钛层。可以利用例如ald、cvd、pvd等将第二粘合层1864沉积在光学隔离层1862上。

102.图18c例示了多晶硅层1870沉积在光子集成电路上并填充沟槽1850。可以通过例如cvd或pvd将多晶硅层1870沉积在光子集成电路上。

103.图18d示出了已通过例如化学机械抛光来平坦化以暴露第二粘合层1864或光学隔离层1862的多晶硅层1870,其中随后可通过例如选择性湿法蚀刻将第二粘合层1864或光学隔离层1862与第一粘合层1860一起去除。

104.图18e例示了填充沟槽1850的多晶硅层1870的一部分,该部分是可以通过例如湿法蚀刻工艺选择性地蚀刻到与硅衬底1810和氧化硅层1820之间的交界面近似对准的水平的部分。因此,多晶硅层1870的一部分可以保留在沟槽1850中,而多晶硅层1870的剩余部分的顶表面可以与硅衬底1810与氧化硅层1820之间的交界面近似对准。

105.图18f示出了沉积在氧化硅层1820上的氧化硅层1880。氧化硅层1880可再次填充沟槽1850。可以通过例如cvd或pvd将氧化硅层1880沉积在光子集成电路上。

106.图18g示出了已通过例如化学机械抛光而平坦化的氧化硅层1880。可以例如通过选择性干法蚀刻或湿法蚀刻去除第三粘合层1966、光学隔离层1968和第四粘合层1972。因此,光子集成电路可以包括类似于光隔离结构1564的光隔离结构1866,并且每个光隔离结构包括由侧壁包围的多晶硅层1870的一部分和氧化硅层1880的一部分,其中所述侧壁包括第一粘合层1860、光学隔离层1862和第二粘合层1864。

107.图19a至图19h例示了根据某些实施例的制造包括薄光学隔离层和cte匹配材料的光隔离结构的方法的示例。图19a示出了在光子集成电路中形成的沟槽1950。光子集成电路包括在硅衬底1910上的氧化硅层1920,其中在氧化硅层1920中形成超导纳米线单光子探测器1930和金属塞1940。可以利用各种蚀刻技术(例如光刻和选择性干法或湿法蚀刻技术)形成沟槽1950。可以从氧化硅层1920侧或从硅衬底1910侧蚀刻沟槽1950。在一些实施例中,沟

槽1950可以蚀刻穿过氧化硅层1920和硅衬底1910两者。

108.图19b例示了具有第一粘合层1960、薄光学隔离层1962和第二粘合层1964的光子集成电路,第一粘合层1960、薄光学隔离层1962和第二粘合层1964共形地沉积在沟槽1950的暴露表面上和氧化硅层1920的顶表面上。如上所述,第一粘合层1960可有助于改善光学隔离层1962与沟槽1950的侧壁和底表面的粘合性。第一粘合层1960可以包括例如具有几纳米(例如约2nm至约10nm)厚度的钛层。可以利用例如ald、cvd、pvd等将第一粘合层1960沉积在沟槽1950的暴露表面上和氧化硅层1920的顶表面上。光学隔离层1962可以包括例如金属氮化物(例如tin、tan、zrn、wn或其任何组合),并且可以具有大约几十纳米(例如约25nm至约60nm)的厚度。可以利用例如ald、cvd、pvd等将光学隔离层1962沉积在第一粘合层1960上。第二粘合层1964可有助于改善光学隔离层1962与沟槽1950中的材料的粘合性。第二粘合层1964可包括例如具有几纳米(例如约2nm至约10nm)厚度的钛层。可以利用例如ald、cvd、pvd等将第二粘合层1964沉积在光学隔离层1962上。

109.图19c例示了多晶硅层1970沉积在光子集成电路上并填充沟槽1950。可以通过例如cvd或pvd将多晶硅层1970沉积在光子集成电路上。

110.图19d示出了已经通过例如化学机械抛光来平坦化以暴露第二粘合层1964或光学隔离层1962的多晶硅层1970,其中随后可通过例如选择性湿法蚀刻将第二粘合层1964或光学隔离层1962与第一粘合层1960一起去除。

111.图19e例示了填充沟槽1950的多晶硅层1970的一部分,该部分可以通过干法蚀刻工艺(例如等离子体蚀刻(诸如rie))选择性地蚀刻到与硅衬底1910和氧化硅层1920之间的交界面更精确地对准的水平的部分。因此,可以在氧化硅层1920中形成沟槽1952,并且多晶硅层1970的一部分可以保留在沟槽1950中,而多晶硅层1970的剩余部分的顶表面可以与硅衬底1910和氧化硅层1920之间的交界面对准。

112.图19f示出了可以共形地沉积在沟槽1952的暴露表面上和氧化硅层1920的顶表面上的第三粘合层1966、薄光学隔离层1968和第四粘合层1972。如上所述,第三粘合层1966可有助于改善光学隔离层1968与沟槽1952的侧壁和底表面的粘合性。第三粘合层1966可以具有与第一粘合层1960的厚度类似的厚度。例如,第三粘合层1966可以包括厚度为几纳米(例如约2nm至约10nm)的钛层。可以利用例如ald、cvd、pvd等在沟槽1952的暴露表面上和氧化硅层1920的顶表面上沉积第三粘合层1966。光学隔离层1968可以包括例如金属氮化物(例如tin、tan、zrn、wn或其任何组合),并且可以具有与光学隔离层1962的厚度类似的厚度。例如,光学隔离层1968的厚度可以是大约几十纳米,例如约25纳米至约60纳米。可以利用例如ald、cvd、pvd等在第三粘合层1966上沉积光学隔离层1968。第四粘合层1972可以有助于改善光学隔离层1968与沟槽1952中的材料的粘合性。第四粘合层1972可以包括例如具有几纳米(例如约2nm至约10nm)厚度的钛层。可以利用例如ald、cvd、pvd等在光学隔离层1968上沉积第四粘合层1972。

113.图19g示出了沉积在氧化硅层1920上的氧化硅层1980。氧化硅层1980可以填充沟槽1952。可以利用例如cvd或pvd在光子集成电路上沉积氧化硅层1980。

114.图19h示出了已通过例如化学机械抛光而平坦化的氧化硅层1980。可以例如通过选择性干法蚀刻或湿法蚀刻去除第三粘合层1966、光学隔离层1968和第四粘合层1972。因此,光子集成电路可以包括光隔离结构1974,每个光隔离结构1974包括由侧壁包围的多晶

硅层1970的一部分和氧化硅层1980的一部分,其中所述侧壁包括粘合层1960和1964或粘合层1966和1972以及光学隔离层1962或1966。

115.上述技术也可用于形成用于光子集成电路中的光隔离的其它光隔离结构。例如,上述图7中所示的沟槽710和/或图11中所示的沟槽1110可以填充有薄光学隔离层和cte匹配材料,其中硅衬底610中的沟槽1110和box层620和氧化层630中的沟槽710可以是不对准的,并且可以是单独形成(例如,蚀刻)和填充的。例如,可以从氧化层630的顶部填充box层620或氧化层630中的沟槽710,而可以从硅衬底610的底表面填充硅衬底610中的沟槽1110。

116.图20是根据某些实施例的包括衬底中的深沟槽的光子集成电路2000的示例的截面图,所述深沟槽填充有薄光学隔离层和cte匹配材料。光子集成电路2000可以由光子集成电路1100制成。例如,可以在硅衬底610的暴露表面(包括沟槽1110的内表面和硅衬底610的底表面)上沉积薄粘合层2010,并且可以在薄粘合层2010上沉积薄光学隔离层2020。粘合层2010可以类似于例如粘合层1660、1760、1860或1960,并且可以包括例如具有几纳米(例如约2nm至约10nm)厚度的钛层。光学隔离层2020可以类似于例如光学隔离层1662、1762、1862或1962,并且可以包括例如金属氮化物(例如tin、tan、zrn、wn或其任何组合),并且可以具有大约几十纳米(例如约25nm至约60nm)的厚度。可以通过例如ald、cvd、pvd等沉积粘合层2010和光学隔离层2020。在一些实施例中,可以在光学隔离层2020上沉积另一粘合层(类似于例如粘合层1864或1964,图20中未示出)。在一些实施例中,多晶硅层2030可以沉积在硅衬底610上并且可以填充沟槽1110。可以通过cmp平坦化多晶硅层2030以暴露光学隔离层2020或粘合层2010,并且可以通过例如选择性干法蚀刻或湿法蚀刻去除光学隔离层2020或粘合层2010。

117.在一些实施例中,上述沟槽可以不填充cte匹配材料,因此光隔离结构可以包括由薄光学隔离层和/或粘合层包围的气隙。该气隙可允许周围材料在不受约束的情况下膨胀或收缩,因此可有助于降低热诱发的应力。

118.图21是示出根据某些实施例的在光子集成电路中制造光隔离结构的示例方法的流程图2100。即使图21以一定顺序流来描述操作,但也可以并行地或同时地执行一些操作。可以以不同的顺序来执行一些操作。操作可以具有未包括在图中的附加步骤。一些操作是可选的,因此在各种实施例中可以省略这些操作。一些操作可以与其它操作一起执行。

119.在框2105,可以获得包括衬底、衬底上的电介质层和电介质层中的光敏部件的光子集成电路。所述光敏部件可以包括单光子探测器,例如超导纳米线单光子探测器。所述光子集成电路还可以包括连接到光敏部件的波导,以及用于波导的输入耦合器或输入端口,例如光栅耦合器。

120.在框2110,可以在邻近于用于波导的光敏部件或输入端口(或输入耦合器)的区域处在电介质层或衬底中的至少一者中蚀刻沟槽。可以对沟槽钻孔、干法蚀刻或湿法蚀刻。沟槽可以在衬底、电介质层或均在这两者中。

121.在框2115处,可以在沟槽的暴露表面(包括沟槽的侧壁和底部)上沉积薄粘合层。薄粘合层的厚度可以小于20nm,例如在约2nm和约10nm之间。第一粘合层可以包括例如钛层。如上所述,可以通过例如ald、cvd、pvd等在沟槽的暴露表面上沉积薄粘合层。薄粘合层可有助于改善光学隔离材料与衬底或电介质层之间的粘合性。

122.在框2120,可以通过例如如上所述的ald、cvd、pvd等在薄粘合层上沉积薄光学隔

down

‑

conversio,spdc)的级联(或复用)预言式光子源(heralded photon source,hps)。在每个预言式光子源中,将不确定性地成对产生光子(其包括信号光子和惰性光子),其中一个光子(例如,信号光子)预言该对中的另一个光子(例如,惰性光子)的存在性。因此,如果在一个预言光子源处由高敏感度光电探测器(例如,如上所述的单光子探测器)探测到信号光子,则相应的惰性光子可用作单光子源的输出,而单光子源的级联(或复用)预言光子源中的其它预言光子源可以被旁路或关闭。

133.对于本领域技术人员来说明了的是,可以根据具体的实施方式做出实质性的变化。例如,也可以使用定制的硬件,和/或可以在硬件、软件(包括便携式软件,例如小应用程序(applet)等)或这两者中实现特定元素。此外,可以采用到例如网络输入/输出设备的其它计算设备的连接。

134.参考附图,可以包括存储器的部件可包括非瞬时性机器可读介质。本文中使用的术语“机器可读介质”和“计算机可读介质”是指参与提供使机器以特定方式操作的数据的任何存储介质。在上文提供的实施例中,各种机器可读介质可涉及向处理器和/或其它一个或多个设备提供用于执行的指令/代码。额外地或可替代地,机器可读介质可用于存储和/或携带这种指令/代码。在许多实施方式中,计算机可读介质是物理的和/或有形的存储介质。这种介质可以采取多种形式,包括但不限于非易失性介质、易失性介质和传输介质。计算机可读介质的常见形式例如包括:磁性和/或光学介质、穿孔卡、纸带、具有孔图案的任何其它物理介质、ram、可编程只读存储器(prom)、可擦除可编程只读存储器(eprom)、flash

‑

eprom、任何其它存储器芯片或磁带、如下文所述的载波、或者计算机可从中读取指令和/或代码的任何其它介质。

135.本文讨论的方法、系统和设备是示例性的。各种实施例可适当地省略、替代或添加各种过程或组件。例如,关于某些实施例描述的特征可以组合到各种其它实施例中。可以以类似的方式组合实施例的不同方面和元素。本文提供的附图中的各种部件可以以硬件和/或软件来实现。此外,技术演进以及许多元素是不将公开的范围限制为这些具体示例的示例。

136.有时出于方便,主要是出于共同使用的原因,将信号指代为比特、信息、值、元素、符号、字符、变量、术语、序号、数字等。然而,应当理解的是,所有这些或类似的术语将与适当的物理量相关联,并且仅仅是方便的标签。除非另有特别说明,如从上面讨论中明了的,应当理解,在整个本说明书讨论中使用的诸如“处理”、“估算”、“计算”、“确定”、“查明”、“识别”、“关联”、“测量”、“执行”等术语是指特定装置(例如特定目的计算机或类似特定目的电子计算设备)的动作或过程。因此,在本说明书的上下文中,特定目的计算机或类似特定目的电子计算设备能够操纵或转换信号,所述信号通常表示为特定目的计算机或类似特定目的电子计算设备的存储器、寄存器或其它信息存储设备、传输设备或显示设备中的物理电子量、电量或磁量。

137.本领域技术人员将理解的是,可以使用任何各种不同的技术和技术来表示用于传递本文描述消息的信息和信号。例如,在可以贯穿于上述描述中引用的数据、指令、命令、信息、信号、比特、符号和片段(chip)可以由电压、电流、电磁波、磁场或粒子、光场或粒子或其任何组合来表示。

138.如本文所使用的术语“和”、“或”和“/或”可以包括也期望至少部分地取决于使用

这些术语的上下文的各种含义。典型地,“或”如果用于关联列项(例如a、b或c),其意指a、b和c(此处用于包容性含义)以及a、b或c(此处用于排他性含义)。另外,如本文所使用的术语“一个或多个”可以用于描述单数形式的任何特征、结构或特性,或者可以用于描述特征、结构或特性的一些组合。然而,应当注意的是,这仅仅是说明性示例,并且所要求保护的主题并不限于该示例。此外,术语“至少一个”如果用于关联列项(例如a、b或c),可解释为指a、b和/或c的任何组合,例如a、b、c、ab、ac、bc、aa、aab、abc、aabbccc等。

139.在整个说明书中的引用“一个示例”、“示例”、“特定示例”或“示例性实施方式”意味着结合特征和/或示例描述的特定特征、结构或特征可以包括在所要求保护的主题的至少一个特征和/或示例中。因此,在整个说明书的各个地方出现的短语“在一个示例中”、“在示例中”、“在某些示例中”、“在某些实施方式中”或其它类似的短语不一定都是指相同的特征、示例和/或限制。此外,特定特征、结构或特性可以在一个或多个示例和/或特征中组合。

140.在一些实施方式中,操作或处理可以涉及物理量的物理操作。典型地,尽管不是必要地,这些量可以采取能够被存储、转移、组合、比较或以其它方式操纵的电信号或磁信号的形式。有时出于方便,主要是出于共同使用的原因,将信号指代为比特、信息、值、元素、符号、字符、变量、术语、序号、数字等。然而,应当理解的是,所有这些或类似的术语将与适当的物理量相关联,并且仅仅是方便的标签。除非另有特别说明,如从上面讨论中明了的,应当理解,在整个本说明书讨论中使用的诸如“处理”、“估算”、“计算”、“确定”等术语是指特定装置(例如特定目的计算机、特定目的计算装置、或类似特定目的电子计算设备)的动作或过程。因此,在本说明书的上下文中,特定目的计算机或类似特定目的电子计算设备能够操纵或转换信号,所述信号通常表示为特定目的计算机或类似特定目的电子计算设备的存储器、寄存器或其它信息存储设备、传输设备或显示设备中的物理电子量、电量或磁量。

141.在前面的详细描述中,提出了许多具体细节来提供对所要求保护的主题的全面理解。然而,本领域技术人员将理解的是,也可以在没有这些具体细节的情况下来实施所要求保护的主题。在其它情况下,为了避免使所要求保护的主题模糊,并没有详细描述对于普通技术人员而言已知的方法和装置。因此,所要求保护的主题并不限于所公开的特定示例,而是所要求保护的主题还可以包括落入所附权利要求及其等同物范围内的所有方面。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。