1.本发明涉及半导体技术领域,尤其涉及一种半导体结构及半导体结构的制造方法。

背景技术:

2.相关技术中,半导体结构的电容下电极通过叠成结构进行支撑,由于叠成结构本身的限定,在形成电容孔过程中,叠成结构容易被破坏,从而影响后续形成的电容下电极结构。

技术实现要素:

3.本发明提供一种半导体结构及半导体结构的制造方法,以改善半导体结构的性能。

4.根据本发明的第一个方面,提供了一种半导体结构,包括:

5.衬底;

6.多个下电极,多个下电极间隔地位于衬底上;

7.保护层,保护层位于下电极的上部,并将下电极分隔开;

8.其中,保护层的材质包括氢化非晶硬碳。

9.在本发明的一个实施例中,保护层为类金刚石薄膜层。

10.在本发明的一个实施例中,半导体结构还包括:

11.第一支撑层,第一支撑层位于下电极的中部,并将下电极分隔开。

12.在本发明的一个实施例中,保护层覆盖第一支撑层的表面。

13.在本发明的一个实施例中,保护层的厚度小于第一支撑层的厚度。

14.在本发明的一个实施例中,保护层的厚度不大于第一支撑层的厚度的一半。

15.在本发明的一个实施例中,半导体结构还包括:

16.第二支撑层,第二支撑层位于下电极的中部,并将下电极分隔开;

17.其中,第二支撑层位于第一支撑层的下方,且与第一支撑层间隔设置。

18.在本发明的一个实施例中,半导体结构还包括:

19.介质层,介质层覆盖在下电极的表面;

20.上电极,上电极覆盖在介质层的表面。

21.在本发明的一个实施例中,衬底包括多个间隔设置的接触垫,下电极与接触垫直接接触。

22.根据本发明的第二个方面,提供了一种半导体结构的制造方法,包括:

23.提供衬底;

24.在衬底上形成叠层结构;

25.在叠层结构中形成多个电容孔,电容孔暴露衬底;

26.其中,叠层结构包括保护层,保护层形成电容孔的上部,保护层的材质包括氢化非

晶硬碳。

27.在本发明的一个实施例中,叠层结构还包括在衬底上依次形成的第一牺牲层、第二支撑层、第二牺牲层以及第一支撑层;

28.其中,保护层形成于第一支撑层上。

29.在本发明的一个实施例中,半导体结构的制造方法,还包括:

30.在电容孔中形成下电极,下电极的底部与衬底直接接触。

31.在本发明的一个实施例中,保护层的厚度小于第一支撑层的厚度。

32.在本发明的一个实施例中,半导体结构的制造方法,还包括:

33.形成电容孔之后,

34.去除保护层;

35.在电容孔中形成下电极,下电极的底部与衬底直接接触。

36.在本发明的一个实施例中,半导体结构的制造方法,还包括:

37.形成下电极之后,

38.去除第一牺牲层和第二牺牲层;

39.在下电极的表面形成介质层;

40.在介质层的表面形成上电极。

41.本发明实施例的半导体结构包括衬底、多个下电极以及保护层,通过使得保护层的材质包括氢化非晶硬碳,即保护层的硬度较高,因此在形成电容孔的过程中不会对保护层形成破坏,所以可以保证形成的下电极的质量,从而改善半导体结构的性能。

附图说明

42.通过结合附图考虑以下对本发明的优选实施方式的详细说明,本发明的各种目标,特征和优点将变得更加显而易见。附图仅为本发明的示范性图解,并非一定是按比例绘制。在附图中,同样的附图标记始终表示相同或类似的部件。其中:

43.图1是根据一示例性实施方式示出的一种半导体结构的制造方法的流程示意图;

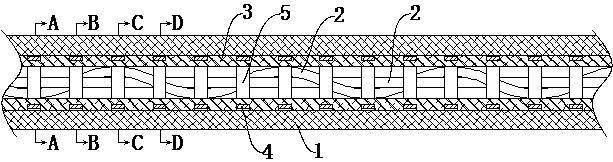

44.图2是根据一示例性实施方式示出的一种半导体结构的制造方法形成电容孔的结构图;

45.图3是根据一示例性实施方式示出的一种半导体结构的制造方法形成下电极的结构图;

46.图4是根据一示例性实施方式示出的一种半导体结构的制造方法去除第一牺牲层和第二牺牲层的结构图;

47.图5是根据一示例性实施方式示出的一种半导体结构的制造方法形成介质层的结构图;

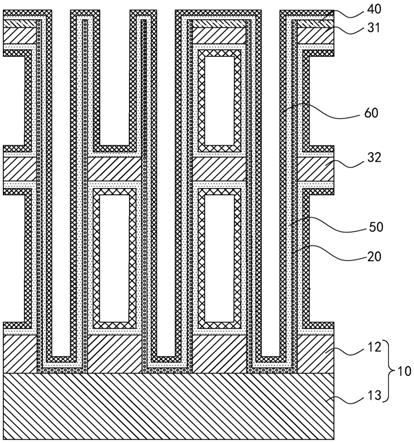

48.图6是根据一示例性实施方式示出的一种半导体结构的结构示意图。

49.附图标记说明如下:

50.10、衬底;11、电容孔;12、阻挡层;13、基底;20、下电极;30、叠层结构;31、第一支撑层;32、第二支撑层;33、第一牺牲层;34、第二牺牲层;40、保护层;50、介质层;60、上电极。

具体实施方式

51.体现本发明特征与优点的典型实施例将在以下的说明中详细叙述。应理解的是本发明能够在不同的实施例上具有各种的变化,其皆不脱离本发明的范围,且其中的说明及附图在本质上是作说明之用,而非用以限制本发明。

52.在对本公开的不同示例性实施方式的下面描述中,参照附图进行,附图形成本公开的一部分,并且其中以示例方式显示了可实现本公开的多个方面的不同示例性结构、系统和步骤。应理解的是,可以使用部件、结构、示例性装置、系统和步骤的其他特定方案,并且可在不偏离本公开范围的情况下进行结构和功能性修改。而且,虽然本说明书中可使用术语“之上”、“之间”、“之内”等来描述本公开的不同示例性特征和元件,但是这些术语用于本文中仅出于方便,例如根据附图中的示例的方向。本说明书中的任何内容都不应理解为需要结构的特定三维方向才落入本公开的范围内。

53.本发明的一个实施例提供了一种半导体结构的制造方法,请参考图1,半导体结构的制造方法包括:

54.s101,提供衬底10;

55.s103,在衬底10上形成叠层结构30;

56.s105,在叠层结构30中形成多个电容孔11,电容孔11暴露衬底10;

57.其中,叠层结构30包括保护层40,保护层40形成电容孔11的上部,保护层40的材质包括氢化非晶硬碳。

58.本发明一个实施例的半导体结构的制造方法在叠层结构30中形成电容孔11,叠层结构30包括保护层40,且保护层40形成电容孔11的上部,通过使得保护层40的材质包括氢化非晶硬碳,即保护层40的硬度较高,因此在形成电容孔11的过程中不会对保护层40形成破坏,可以保证后续形成下电极20的质量,从而改善半导体结构的性能。

59.需要说明的是,氢化非晶硬碳形成的保护层40为类金刚石薄膜,类金刚石薄膜兼具了金刚石和石墨的优良特性,而具有高硬度,高热导率,高电阻率,良好光学性能以及优秀的摩擦学特性,所以由类金刚石而来的dlc膜同样是一种亚稳态长程无序的非晶材料,碳原子间的键合方式是共价键。

60.需要说明的是,衬底10可以包括基底13和阻挡层12,阻挡层12上形成叠层结构30,形成的电容孔11暴露基底13,即阻挡层12形成了电容孔11的下部。对于电容孔11的成型工艺此处不作限定,可以采用相关技术中的工艺,如间距倍增技术形成电容孔11,在形成电容孔11的过程中,由于类金刚石薄膜的硬度较大,因此不会被破坏。

61.基底13可以包括由含硅材料形成的部分。基底13可以由任何合适的材料形成,例如,包括硅、单晶硅、多晶硅、非晶硅、硅锗、单晶硅锗、多晶硅锗以及碳掺杂硅中的至少一种。阻挡层12可以包括氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)等。

62.在一个实施例中,如图2所示,叠层结构30还包括在衬底10上依次形成的第一牺牲层33、第二支撑层32、第二牺牲层34以及第一支撑层31;其中,保护层40形成于第一支撑层31上,保护层40可以形成对第一支撑层31的保护,避免形成电容孔11的过程中对第一支撑层31形成破坏。

63.具体的,在基底13上形成阻挡层12,在阻挡层12上形成第一牺牲层33,在第一牺牲层33上形成第二支撑层32,并在第二支撑层32上形成第二牺牲层34,在第二牺牲层34上形

成第一支撑层31,最后在第一支撑层31上形成保护层40,即形成了叠层结构30,然后在叠层结构30内形成电容孔11,此时电容孔11暴露基底13,具体如图2所示。

64.针对上述实施例,需要说明的是,阻挡层12、第一牺牲层33、第二支撑层32、第二牺牲层34、第一支撑层31以及保护层40可以通过采用物理气相沉积工艺、化学气相沉积工艺或原子层沉积工艺等形成。

65.阻挡层12、第二支撑层32以及第一支撑层31可以采用相同的材料,如氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)等。或者,阻挡层12、第二支撑层32以及第一支撑层31也可以采用不同的材料。

66.可选的,半导体结构的制造方法,还包括:在电容孔11中形成下电极20,下电极20的底部与衬底10直接接触,此时下电极20覆盖保护层40的侧表面,且下电极20的底部与基底13直接接触,具体如图3所示。

67.进一步的,保护层40的厚度小于第一支撑层31的厚度,保护层40主要起到保护作用,因此可以尽量降低保护层40的厚度,以此降低半导体结构的制造成本。

68.可选的,半导体结构的制造方法,还包括:形成电容孔11之后,去除保护层40;在电容孔11中形成下电极20,下电极20的底部与衬底10直接接触。即在形成电容孔11的过程中,保护层40实现了对第一支撑层31保护,而在形成电容孔11之后,可以将保护层40去除,而保护层40的材质包括氢化非晶硬碳,因此也容易去除。

69.在一个实施例中,半导体结构的制造方法,还包括:形成下电极20之后,去除第一牺牲层33和第二牺牲层34;在下电极20的表面形成介质层50;在介质层50的表面形成上电极60。

70.具体的,在形成如图2所示的结构后,在电容孔11中形成下电极20,如图3所示,并将第一牺牲层33和第二牺牲层34进行去除,保护层40、第一支撑层31、第二支撑层32以及阻挡层12实现对下电极20的支撑,如图4所示。并在下电极20的表面形成介质层50,介质层50还覆盖保护层40的上表面,如图5所示。最后在介质层50的表面形成上电极60,具体可以参见图6所示的半导体结构。

71.可选的,在形成电容孔11之后,如果将保护层40进行了去除,则形成的介质层50覆盖第一支撑层31的上表面。

72.可选的,基底13包括多个分立的接触垫,而下电极20与接触垫直接接触。其中,接触垫的材料包括但不限于钨(w)。

73.需要说明的是,第一牺牲层33和第二牺牲层34可以采用湿法刻蚀工艺去除。对于下电极20、介质层50以及上电极60的形成工艺可以是相关技术中的物理气相沉积工艺、化学气相沉积工艺或原子层沉积工艺等,此处不作限定。

74.下电极20的材料包括但不限于氮化钛。

75.上电极60的材料包括但不限于氮化钛。

76.介质层50的材料包括高k材料;其中,高k材料包括但不限于氧化铝、氧化锆和氧化铪中的至少一种。

77.本发明的一个实施例还提供了一种半导体结构,请参考图6,半导体结构包括:衬底10;多个下电极20,多个下电极20间隔地位于衬底10上;保护层40,保护层40位于下电极20的上部,并将下电极20分隔开;其中,保护层40的材质包括氢化非晶硬碳。

78.本发明一个实施例的半导体结构包括衬底10、多个下电极20以及保护层40,通过使得保护层40的材质包括氢化非晶硬碳,即保护层40的硬度较高,因此在形成电容孔11的过程中不会对保护层40形成破坏,所以可以保证形成的下电极20的质量,从而改善半导体结构的性能。

79.在一个实施例中,保护层40为类金刚石薄膜层,具有高硬度,高热导率,高电阻率,良好光学性能以及优秀的摩擦学特性。

80.可选的,保护层40包括的氢化非晶硬碳可以掺杂其他材料,如,氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)等,以此方便与叠层结构30的其他结构进行连接。

81.需要说明的是,衬底10可以包括基底13和阻挡层12,阻挡层12形成了电容孔11的下部。

82.基底13可以包括由含硅材料形成的部分。基底13可以由任何合适的材料形成,例如,包括硅、单晶硅、多晶硅、非晶硅、硅锗、单晶硅锗、多晶硅锗以及碳掺杂硅中的至少一种。阻挡层12可以包括氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)等。

83.在一个实施例中,半导体结构还包括:第一支撑层31,第一支撑层31位于下电极20的中部,并将下电极20分隔开。第一支撑层31可以进一步实现对下电极20起到支撑作用。

84.可选的,第一支撑层31和保护层40间隔设置。

85.可选的,保护层40覆盖第一支撑层31的表面,即保护层40可以实现对第一支撑层31的有效保护,避免第一支撑层31在蚀刻形成电容孔11的过程中被破坏。

86.在一个实施例中,保护层40的厚度小于第一支撑层31的厚度。

87.可选的,保护层40的厚度不大于第一支撑层31的厚度的一半。即较薄的一层类金刚石薄膜就可以实现对第一支撑层31的有效保护,且保护层40在与第一支撑层31相接触时,第一支撑层31就可以实现对下电极20的有效支撑,因此可以使得保护层40较薄。

88.在一个实施例中,如图6所示,半导体结构还包括:第二支撑层32,第二支撑层32位于下电极20的中部,并将下电极20分隔开;其中,第二支撑层32位于第一支撑层31的下方,且与第一支撑层31间隔设置。

89.具体的,如图6所示,保护层40、第一支撑层31以及第二支撑层32沿高度方向依次设置,且保护层40和第一支撑层31相接触,而第一支撑层31以及第二支撑层32间隔设置,保护层40、第一支撑层31以及第二支撑层32实现了对下电极20的支撑。

90.阻挡层12、第二支撑层32以及第一支撑层31可以采用相同的材料,如氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)等。或者,阻挡层12、第二支撑层32以及第一支撑层31也可以采用不同的材料。

91.需要说明的是,第一支撑层31和第二支撑层32的厚度关系此处不作限定,第一支撑层31的厚度可以等于第二支撑层32的厚度,或者,第一支撑层31的厚度可以小于第二支撑层32的厚度,或者,第一支撑层31的厚度可以大于第二支撑层32的厚度。

92.在一个实施例中,如图6所示,半导体结构还包括:介质层50,介质层50覆盖在下电极20的表面;上电极60,上电极60覆盖在介质层50的表面。

93.衬底10可以包括基底13和阻挡层12,阻挡层12与保护层40、第一支撑层31以及第二支撑层32实现了对下电极20和上电极60的支撑作用。

94.可选的,下电极20和上电极60之间设置有介质层50,介质层50的材料包括高k材

料;其中,高k材料包括但不限于氧化铝、氧化锆和氧化铪等高k材料或其任意组合物。

95.可选的,下电极20的材料包括但不限于氮化钛。

96.可选的,上电极60的材料包括但不限于氮化钛。

97.在一个实施例中,衬底10包括多个间隔设置的接触垫,下电极20与接触垫直接接触,从而保证下电极20与接触垫之间电连接。。

98.具体的,接触垫的材料包括但不限于钨(w)。多个下电极20与多个接触垫一一相对应地设置。

99.需要说明的是,本实施例中的半导体结构可以由上述的半导体结构的制造方法获得,对于本实施例中半导体结构的其他材料以及结构均可以参考上述半导体结构的制造方法。

100.本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本发明的其它实施方案。本发明旨在涵盖本发明的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本发明的一般性原理并包括本发明未公开的本技术领域中的公知常识或惯用技术手段。说明书和示例实施方式仅被视为示例性的,本发明的真正范围和精神由所附的权利要求指出。

101.应当理解的是,本发明并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。本发明的范围仅由所附的权利要求来限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。