1.本技术涉及电子器件领域,具体涉及一种整流器件及集成芯片。

背景技术:

2.碳化硅由于具有优异的物理性能,受到了半导体领域的关注,基于碳化硅的器件也在不断的出现,比如sbd、jbs和mosfet等,这些器件的研发和生产,将部分替代硅基器件,在未来具有很大的市场。异质结是构建很多器件的基本结构,其中包括肖特基结、pn结、nn结和pp结等。其中,整流器件,就是基于这些异质结构的,整流器件中,常见的是利用肖特基结和pn结。整流器件在工业设备和电子器件中应用的也相当广泛。作为新兴的半导体材料,碳化硅在构建器件方面的潜力还有很大的开发空间,以及潜在的市场前景。

3.目前碳化硅单晶可以实现p型和n型掺杂,n型衬底已经商业化。氧化镓ga2o3材料,在不掺杂的情况下,呈现自然的n型导电特性。而且,由于氧化镓具有很好的化学稳定性和高的击穿场强,在功率器件中也具有一定的应用前景。

4.背景技术部分的内容仅仅是公开人所知晓的技术,并不代表本领域的现有技术。

技术实现要素:

5.本技术提供一种整流器件,该整流器件具有氧化镓薄膜,该氧化镓薄膜具有良好的氧化镓薄膜,该氧化镓薄膜结晶性能良好,具有良好的整流特性。

6.根据本技术一个方面,该整流器件包括:衬底;氧化镓薄膜,形成于所述衬底上;电极层,形成于所述氧化镓薄膜上;下电极层,形成于与所述氧化镓薄膜相对的所述衬底的另一侧。

7.根据本技术一些实施例,所述衬底的等效直径为2至6英寸。

8.根据本技术一些实施例,所述衬底包括碳化硅单晶材料。

9.根据本技术一些实施例,所述碳化硅单晶材料包括:(001)面取向的n型4h

‑

碳化硅,斜切4

°

或8

°

。

10.根据本技术一些实施例,所述氧化镓薄膜厚度为100纳米至500 纳米。

11.根据本技术一些实施例,所述氧化镓薄膜包括纯度在99.99%及以上的氧化镓。

12.根据本技术一些实施例,所述电极层包括金属钛层和金属金层,所述金属金层覆盖所述金属钛层。

13.根据本技术一些实施例,所述金属钛层厚度为5至20纳米。

14.根据本技术一些实施例,所述金属金层厚度为50至100纳米。

15.根据本技术一些实施例,所述电极层还包括金属铝层,覆盖所述金属金层。

16.根据本技术一些实施例,所述金属铝层厚度为1至5微米。

17.根据本技术一些实施例,所述下电极层包括金属钛层及金属金层,所述金属金层覆盖所述金属钛层。

18.根据本技术一些实施例,所述金属钛层厚度为5至20纳米。

19.根据本技术一些实施例,金属金层厚度为50至100纳米。

20.根据本社情另一方便,还提供一种集成芯片,包括如上所述的整流器件。

21.根据一些实施例,本技术所提供的整流器件,该整流器件的氧化镓薄膜结晶性能良好,整流特性良好,可用于芯片集成制备技术。并且,该整流器件的制备技术操作步骤简单、成本低廉,适用于现在的半导体生产线批量化生产。

附图说明

22.构成本技术的一部分的附图用来提供对本技术的进一步理解,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

23.图1为本技术示例性实施例的整流器件剖面结构示意图;

24.图2为本技术另一示例性实施例的整流器件的制备方法流程图;

25.图3a

‑

3f为本技术示例性实施例的整流器件制备过程图;

26.图4为本技术示例性实施例的整流器件的氧化镓薄膜xrd图;

27.图5为本技术示例性实施例的整流器件的整流比随电压的变化特性示意图。

具体实施方式

28.以下结合附图和实施例,对本技术的具体实施方式进行更加详细的说明,以便能够更好地理解本技术的方案以及其各个方面的优点。然而,以下描述的具体实施方式和实施例仅是说明的目的,而不是对本技术的限制。

29.所描述的特征、结构或特性可以以任何合适的方式结合在一个或更多实施例中。在下面的描述中,提供许多具体细节从而给出对本公开的实施例的充分理解。然而,本领域技术人员将意识到,可以实践本公开的技术方案而没有这些特定细节中的一个或更多,或者可以采用其它的方式、组元、材料、装置或等。在这些情况下,将不详细示出或描述公知结构、方法、装置、实现、材料或者操作。

30.附图中所示的流程图仅是示例性说明,不是必须包括所有的内容和操作/步骤,也不是必须按所描述的顺序执行。例如,有的操作/步骤还可以分解,而有的操作/步骤可以合并或部分合并,因此实际执行的顺序有可能根据实际情况改变。

31.本技术的说明书和权利要求书及所述附图中的术语“第一”、“第二”、“第三”和“第四”等是用于区别不同对象,而不是用于描述特定顺序。此外,术语“包括”和“具有”以及它们任何变形,意图在于覆盖非排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备没有限定于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元,或可选地还包括对于这些过程、方法、产品或设备固有的其它步骤或单元。

32.在本文中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本技术的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

33.整流器件用于把交流电转换成直流电的装置中,例如,供电装置及侦测无线电信号装置等。整流器件也可用于给蓄电池提供充电电压。

34.整流器件一般为平面型硅二极管,用于各种电源整流电路中。选用整流二极管时,

主要考虑其最大整流比、击穿电压等。

35.氧化镓是一种宽禁带半导体,禁带宽度eg=4.9ev,使其击穿电场强度很大,相当于碳化硅及氮化镓的两倍以上。此外,氧化镓导电性能和发光性能良好,因此其在光电子器件方面有广阔的应用前景。

36.有鉴于此,本技术提供一种具有氧化镓薄膜的整流器件及其制备方法,下面参考具体实施例,对本技术进行说明。

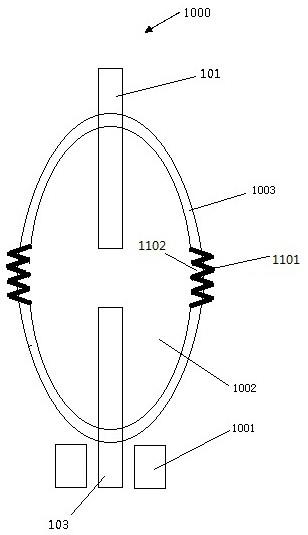

37.图1为本技术示例性实施例的整流器件剖面结构示意图。

38.参见图1,根据一些实施例,衬底101,衬底可以选用碳化硅单晶衬底。碳化硅同质异形晶体结构有200多种,其中六方结构的碳化硅具有高临界击穿电场、高电子迁移率等优势,是制造优良半导体的材料。

39.根据一些实施例,衬底101可选用碳化硅单晶材料,等效直径在2 至6英寸。优选地,可选用(001)面取向的n型4h

‑

碳化硅,斜切4

ꢀ°

或8

°

。在本实施例中,衬底碳化硅衬底尺寸为0.5厘米

×

1厘米,电阻率为2.1mω﹒cm。

40.如图1所示,根据示例性实施例,氧化镓薄膜103厚度在100纳米至500纳米之间。

41.根据一些实施例,三氧化二镓是一种在光学器件方面有很广阔的应用,多用在紫外线滤光片中。在本技术中,经过大量实验证实氧化镓ga2o3在不掺杂的情况下,即,含量在99.99%及以上的氧化镓,呈现自然的n型导电特性,将氧化镓用于整流器件中具有很好的化学稳定性和高击穿场强。

42.如图1所示,根据示例性实施例,氧化镓薄膜上形成金属电极105,电极层包括5

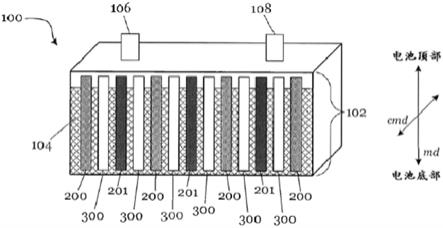

‑

20纳米厚的金属钛层106和50

‑

100纳米厚的金属金层 107。电极层还包括金属铝层108,铝层厚度范围为1

‑

5微米,作为上电极。在一些实施例中,金属铝可以用于封装时,能够用于超声焊接。

43.参见图1,根据示例性实施例,电极层还包括:形成于与氧化镓层相对的衬底另一侧的下电极。下电极包括钛层309和金层310。在本实施例中,下电极金属钛层厚度范围为5

‑

20纳米,金属金层厚度范围为 50

‑

100纳米。

44.下面参照图2及图3a

‑

3e描述本技术示例性实施例整流器件的制备方法。

45.在s201中,根据示例性实施例,准备衬底301,如图3a所示,清洗并干燥。

46.根据一些实施例,衬底301可选择碳化硅单晶材料,优选地,衬底301可以为(001)面取向的n型4h

‑

碳化硅,斜切4

°

或8

°

。

47.在本实施例中,衬底碳化硅衬底尺寸为0.5厘米

×

1厘米,电阻率为2.1mω﹒cm。选好衬底301后,转入s203中。

48.在s203中,根据示例性实施例,将氧化镓粉末压制成靶材。在一些实施例中,选用纯度大于等于99.99%的氧化镓粉末。

49.在本实施例中,使用氧化镓陶瓷靶材,直径约为25毫米,厚度约为3毫米。形成靶材后转入s205中。

50.在s205中,根据一些实施例,沉积氧化镓薄膜303,将衬底与靶材放入沉积室,利用脉冲激光技术,在衬底上沉积氧化镓薄膜图形阵列,如图3b所示。

51.根据示例性实施例,脉冲激光能量包括300

‑

600mj,脉冲激光频率包括1

‑

10hz。在一些实施例中,沉积过程中,衬底温度包括600℃

‑

750 ℃。在本实施例中,衬底301温度保持

在750℃。

52.根据一些实施例,氧化镓靶材与衬底之间的距离包括4

‑

6厘米。在本实施例中,靶基距(靶材与衬底之间的距离)为5厘米,脉冲次数为5000次,在沉积过程中,衬底处于旋转状态,腔体的基准压力优选为1

×

10

‑6pa~1

×

10

‑3pa。

53.在一些实施例中,利用掩膜版控制氧化镓薄膜303的尺寸,并可以每个晶圆上可以做出阵列图形,沉积氧化镓薄膜303。

54.根据示例性实施例,掩膜版包括光刻掩模版或镂空模板。在本实施例中,可以通过镂空模板形成具有图形阵列的氧化镓薄膜。此外,根据另一些实施例,在衬底上利用光学曝光技术制备光刻胶图形,通过等离子刻蚀形成氧化镓薄膜图形阵列。此处需要说明的是,还包括掩膜版还可以包括光水解掩膜版,本技术此处不做限制。

55.根据一些实施例,图形阵列单元格规格可以为2mm

×

2mm,氧化镓薄膜厚度包括100nm至500nm。然后转入s207中。

56.在s207中,根据一些实施例,沉积形成氧化镓薄膜后,在氧气氛围下原位退火0.5

‑

1小时。退火的作用在于消除应力,减少氧空位,获得高质量的氧化镓薄膜。在本实施例中,沉积后退火1小时后,转入步骤s209中。

57.在s209中,根据示例性实施例,参见图3c,形成电极层305,包括,在氧化镓薄膜上形成的电极层305。

58.根据一些实施例,将沉积好氧化镓薄膜的基板样品从沉积室中取出后,利用光刻掩模版,在氧化镓薄膜上制备光刻胶图形,进行等离子刻蚀后,移除光刻胶。然后再利用电极层掩膜版,在磁控溅射沉积室中沉积电极层。

59.根据一些实施例,参见图3d,沉积电极层包括5

‑

20纳米厚的金属钛306和50

‑

100纳米厚的金属金307。在本实施例中,沉积电极层为 20纳米的钛和100纳米的金电极层,金层上方还设置有铝层308。

60.根据示例性实施例,铝层厚度范围为1

‑

5微米,作为上电极。金属铝是用于封装时,能够用于超声焊接。

61.根据一些实施例,形成电极层还包括形成下电极。

62.根据示例性实施例,参见图3e,依次沉积钛309和金310于衬底的下表面,形成下电极。在本实施例中,下电极金属钛层厚度范围为 5

‑

20纳米,金属金层厚度范围为50

‑

100纳米。形成电极层之后,转入步骤s211中。

63.在s211中,根据示例性实施例,按照氧化镓薄膜图形阵列进行切割,获得整流器件,如图3f所示。

64.根据一些实施例,图形阵列单元规格在2mm

×

2mm,切割后形成的各个整流器件可以用于芯片集成制备技术中。

65.图4为本技术示例性实施例的整流器件的氧化镓薄膜xrd图。

66.根据示例性实施例,整流器件的氧化镓薄膜xrd图,可以看出本技术氧化镓薄膜103的晶体结构是单斜相的β

‑

ga2o3,取向为(

‑

201)。

67.根据示例性实施例,由该示例性实施例的整流器件氧化镓薄膜反射高能电子衍射(rheed)图可以看出氧化镓薄膜103具有良好的结晶性。

68.图5为本技术示例性实施例的整流器件的整流比随电压的变化特性示意图。

69.参见图5,根据示例性实施例,基于材料的特性,未掺杂的氧化镓材料具有电子型导电(n型)特征,可以与具有n型导电特征的碳化硅材料构建nn结。由于两种材料费米面和带隙不同,当两种材料接触后,会产生结效应,在一定电压范围内会具有很好的整流特性。

70.如图5所示,根据一些实施例,本技术整流器件的整流比随电压的变化特性,可以看出该整流器件具有良好的整流特性,当电压大于 3v时,器件整流比迅速增加,室温下整流比达到103。

71.以上对本技术实施例进行了详细描述和解释。应清楚地理解,本技术描述了如何形成和使用特定示例,但本技术不限于这些示例的任何细节。相反,基于本技术公开的内容的教导,这些原理能够应用于许多其它实施例。

72.通过对示例实施例的描述,本领域技术人员易于理解,根据本技术实施例的技术方案至少具有以下优点中的一个或多个。

73.根据一些实施例,可以在碳化硅衬底上形成n型氧化镓薄膜。利用xrd检测薄膜的晶体结构,图如4所示,可以看出薄膜的晶体结构是单斜相β

‑

ga2o3,取向为(

‑

201)晶型。再利用反射高能电子衍射 (rheed)监测薄膜生产质量,从测试结果可以看出薄膜结晶性能良好。用过测试电流电压曲线,参见图5,可以看出该器件具有很好的整流特性,在3v时器件整流比迅速增加,室温下整流比达到103。本技术所提供的整流器件可以用于芯片集成制备技术中。并且这种整流器件的制备技术,操作步骤简单、成本低廉,适用于现在的半导体生产线批量化生产。

74.显然,上述实施例仅是为清楚地说明本技术所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本技术的保护范围之中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。