技术特征:

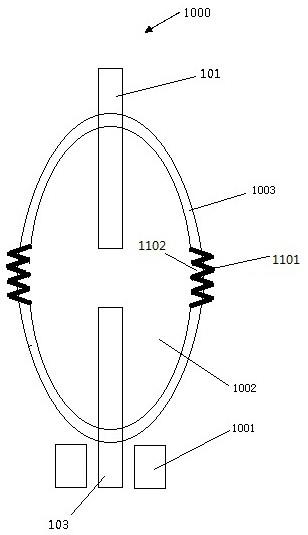

1.一种半导体结构,其特征在于,包括:第一衬底,所述第一衬底包括若干第一有源区组和若干第二有源区组,若干第一有源区组和若干第二有源区组沿第一方向间隔排列,每个第一有源区组包括沿第二方向排列的若干第一有源区,每个第二有源区组包括沿第二方向排列的若干第二有源区,所述第一方向和第二方向互相垂直,所述第一有源区在第一衬底表面具有第一投影,所述第二有源区在第一衬底表面具有第二投影,所述第一投影和第二投影是形状相同的矩形,并且,相邻的第一投影和第二投影的中心线在第二方向上不重合;位于若干第一有源区和若干第二有源区之间的第一隔离层;相互独立的若干字线栅结构,所述字线栅结构位于所述第一衬底和第一隔离层内,所述字线栅结构沿第一方向延伸且沿第二方向排布,每个字线栅结构沿第一方向贯穿在所述第二方向上相邻的1排第一有源区和1排第二有源区;若干位线结构,每个位线结构位于1个第一有源区组或1个第二有源区组上;位于若干第一有源区和若干第二有源区上的若干电容结构,并且,所述电容结构和位线结构分别位于第一衬底相对的两个表面上。2.如权利要求1所述的半导体结构,其特征在于,还包括:位于第一衬底内的若干第二隔离结构,在垂直于第一衬底表面的方向上,第二隔离结构的高度小于第一隔离层的高度,所述第二隔离结构位于相邻的字线栅结构之间,并且,每个第二隔离结构沿第一方向贯穿1排第一有源区或1排第二有源区。3.如权利要求2所述的半导体结构,其特征在于,所述第一衬底包括相对的第一面和第二面,所述位线结构位于所述第一面上,所述电容结构位于所述第二面上,所述第二面暴露出所述第二隔离结构的底面。4.如权利要求3所述的半导体结构,其特征在于,位于每个第一有源区和每个第二有源区的第一面的第一掺杂区,并且,在所述第二方向上,每个位线结构与1列第一有源区或1列第二有源区的第一掺杂区电连接。5.如权利要求3所述的半导体结构,其特征在于,所述第二隔离结构在朝向第一面的方向上的顶面高于所述字线栅结构高度的二分之一。6.如权利要求3所述的半导体结构,其特征在于,在若干电容结构中,每2个电容结构位于1个第一有源区或1个第二有源区的第二面上,并且,在所述第二方向上,所述2个电容结构分别位于贯穿所述1个第一有源区或1个第二有源区的第二隔离结构的两侧。7.如权利要求6所述的半导体结构,其特征在于,位于每个第一有源区和每个第二有源区的第二面的第二掺杂区,在所述第二方向上,所述第二掺杂区位于所述第二隔离结构的两侧,在垂直于第二面的方向上,所述第二掺杂区的深度小于所述第二隔离结构的高度,并且,每个电容结构与所述第二隔离结构的两侧中的一侧的第二掺杂区电连接。8.如权利要求7所述的半导体结构,其特征在于,所述电容结构在第二面的投影与所述第二掺杂区至少部分重合。9.如权利要求2所述的半导体结构,其特征在于,所述第一衬底包括相对的第一面和第二面,所述电容结构位于所述第一面上,所述位线结构位于所述第一面上,所述第一面暴露出所述第二隔离结构的顶面。10.如权利要求9所述的半导体结构,其特征在于,位于每个第一有源区和每个第二有

源区的第二面的第一掺杂区,并且,在所述第二方向上,每个位线结构与1列第一有源区或1列第二有源区的第一掺杂区电连接。11.如权利要求9所述的半导体结构,其特征在于,所述第二隔离结构在朝向第二面的方向上的底面低于所述字线栅结构高度的二分之一。12.如权利要求9所述的半导体结构,其特征在于,在若干电容结构中,每2个电容结构位于1个第一有源区或1个第二有源区的第一面上,并且,在所述第二方向上,所述2个电容结构分别位于贯穿所述1个第一有源区或1个第二有源区的第二隔离结构的两侧。13.如权利要求12所述的半导体结构,其特征在于,位于每个第一有源区和每个第二有源区的第一面的第二掺杂区,在所述第二方向上,所述第二掺杂区位于所述第二隔离结构的两侧,在垂直于第一面的方向上,所述第二掺杂区的深度小于所述第二隔离结构的高度,并且,每个电容结构与所述第二隔离结构的两侧中的一侧的第二掺杂区电连接。14.如权利要求13所述的半导体结构,其特征在于,所述电容结构在第一面的投影与所述第二掺杂区至少部分重合。15.如权利要求4或10所述的半导体结构,其特征在于,还包括:位于每个第一掺杂区上的第一导电结构。16.如权利要求8或14所述的半导体结构,其特征在于,还包括:位于每个电容结构与第二掺杂区之间的第二导电结构。17.如权利要求1所述的半导体结构,其特征在于,所述字线栅结构的顶面低于所述第一隔离层的顶面,所述半导体结构还包括:位于字线栅结构顶面的覆盖介质层,所述覆盖介质层还位于所述第一隔离层内。18.如权利要求1所述的半导体结构,其特征在于,相邻的第一投影的中心之间、相邻的第二投影的中心之间沿第一方向具有相等的间距w1,所述间距w1=2t1,所述t1是相邻的位线投影沿第一方向同一侧的边缘之间的间距,所述位线投影是位线结构在第一衬底表面的投影。19.如权利要求1所述的半导体结构,其特征在于,相邻的第一投影的中心之间、相邻的第二投影的中心之间沿第二方向具有相等的间距w2,所述间距w2=2t2,所述t2是相邻的字线投影沿第二方向同一侧的边缘之间的间距,所述字线投影是字线栅结构在第一衬底表面的投影。20.一种半导体结构的形成方法,其特征在于,包括:提供第一衬底,所述第一衬底包括若干第一有源区组和若干第二有源区组,若干第一有源区组和若干第二有源区组沿第一方向间隔排列,每个第一有源区组包括沿第二方向排列的若干第一有源区,每个第二有源区组包括沿第二方向排列的若干第二有源区,所述第一方向和第二方向互相垂直,所述第一有源区在第一衬底表面具有第一投影,所述第二有源区在第一衬底表面具有第二投影,所述第一投影和第二投影是形状相同的矩形,并且,相邻的第一投影和第二投影的中心线在第二方向上不重合;在若干第一有源区和若干第二有源区之间形成第一隔离层;在所述第一衬底和第一隔离层内形成相互独立的若干字线栅结构,所述字线栅结构沿第一方向延伸且沿第二方向排布,每个字线栅结构沿第一方向贯穿在所述第二方向上相邻的1排第一有源区和1排第二有源区;

在形成所述字线栅结构之后,形成若干位线结构,每个位线结构位于1个第一有源区组或1个第二有源区组上;在形成所述字线栅结构之后,在若干第一有源区和若干第二有源区上形成若干电容结构,并且,所述电容结构和位线结构分别位于第一衬底相对的两个表面上。21.如权利要求20所述的半导体结构的形成方法,其特征在于,若干所述字线栅结构的形成方法包括:在第一隔离层、若干第一有源区和若干第二有源区内形成若干第一凹槽,若干第一凹槽沿第一方向延伸且沿第二方向排列,第一凹槽的深度小于第一隔离层的高度,每个第一凹槽的内壁面暴露出所述第一隔离层、以及在第二方向上相邻的1排第一有源区和1排第二有源区;在若干第一凹槽内形成若干所述字线栅结构。22.如权利要求20所述的半导体结构的形成方法,其特征在于,所述字线栅结构的顶面低于所述第一隔离层的顶面,所述半导体结构的形成方法还包括:在形成若干字线栅结构之后,在所述第一凹槽内形成覆盖介质层,所述覆盖介质层位于所述字线栅结构顶面。23.如权利要求20所述的半导体结构的形成方法,其特征在于,在垂直于第一衬底表面的方向上,所述第一衬底包括相对的第一面和第二面,所述位线结构位于所述第一面上,所述电容结构位于所述第二面上。24.如权利要求23所述的半导体结构的形成方法,其特征在于,还包括:在形成所述字线栅结构之后,且在形成所述位线结构之前,在每个第一有源区和每个第二有源区的第一面形成第一掺杂区。25.如权利要求24所述的半导体结构的形成方法,其特征在于,还包括:提供第二衬底;在形成所述位线结构之后,键合所述第一衬底和第二衬底,所述第一面朝向所述第二衬底的表面。26.如权利要求25所述的半导体结构的形成方法,其特征在于,还包括:键合所述第一衬底和第二衬底后,自所述第二面平坦化所述第一衬底,直至暴露出第一隔离层底面;自所述第二面平坦化所述第一衬底后,在所述第一衬底内形成若干第二隔离结构,所述第二面暴露出所述第二隔离结构,在垂直于第二面的方向上,第二隔离结构的高度小于第一隔离层的高度,所述第二隔离结构位于相邻的字线栅结构之间,并且,每个第二隔离结构沿第一方向贯穿1排第一有源区或1排第二有源区。27.如权利要求26所述的半导体结构的形成方法,其特征在于,还包括:在形成所述第二隔离结构之后,且在形成若干电容结构之前,在每个第一有源区和每个第二有源区的第二面形成第二掺杂区,在所述第二方向上,所述第二掺杂区位于所述第二隔离结构的两侧,在垂直于第二面的方向上,所述第二掺杂区的深度小于所述第二隔离结构的高度。28.如权利要求20所述的半导体结构的形成方法,其特征在于,所述第一衬底包括相对的第一面和第二面,所述电容结构位于所述第一面上,所述位线结构位于所述第二面上。29.如权利要求28所述的半导体结构的形成方法,其特征在于,还包括:在形成所述字线栅结构之后,且在形成所述电容结构之前,在所述第一衬底内形成若干第二隔离结构,所述第一面暴露出所述第二隔离结构,在垂直于第一面的方向上,第二隔离结构的高度小于第一隔离层的高度,所述第二隔离结构位于相邻的字线栅结构之间,并且,每个第二隔离结构沿第一方向贯穿1排第一有源区或1排第二有源区。30.如权利要求29所述的半导体结构的形成方法,其特征在于,还包括:在形成第二隔

离结构之后,且在形成电容结构之前,在每个第一有源区和每个第二有源区的第一面形成第二掺杂区,在所述第二方向上,所述第二掺杂区位于所述第二隔离结构的两侧,并且,在垂直于第一面的方向上,所述第二掺杂区的深度小于所述第二隔离结构的高度。31.如权利要求30所述的半导体结构的形成方法,其特征在于,还包括:提供第二衬底;在形成所述电容结构之后,键合所述第一衬底和第二衬底,所述第一面朝向所述第二衬底的表面。32.如权利要求31所述的半导体结构的形成方法,其特征在于,还包括:键合所述第一衬底和第二衬底后,自所述第二面平坦化所述第一衬底,直至暴露出第一隔离层底面;自所述第二面平坦化所述第一衬底后,且在形成位线结构之前,在每个第一有源区和每个第二有源区的第二面形成第一掺杂区。33.如权利要求24或32所述的半导体结构的形成方法,其特征在于,还包括:在形成位线结构之前,在每个第一掺杂区上形成第一导电结构。34.如权利要求27或30所述的半导体结构的形成方法,其特征在于,还包括:在形成电容结构之前,在所述第二隔离结构沿第二方向每一侧的第二掺杂区上形成第二导电结构。

技术总结

一种半导体结构及其形成方法,所述半导体结构包括:第一衬底,第一衬底包括沿第一方向间隔排列的若干第一有源区组和若干第二有源区组,第一有源区组包括若干第一有源区,第二有源区组包括若干第二有源区,第一投影和第二投影是形状相同的矩形;位于若干第一有源区和若干第二有源区之间的第一隔离层;相互独立的若干字线栅结构,字线栅结构位于第一衬底和第一隔离层内;若干位线结构,每个位线结构位于1个第一有源区组或1个第二有源区组上;若干电容结构,电容结构和位线结构分别位于第一衬底相对的两个表面上。所述半导体结构能够改善动态随机存取存储器的性能,降低形成动态随机存取存储器的工艺难度。取存储器的工艺难度。取存储器的工艺难度。

技术研发人员:余兴 华文宇 刘藩东

受保护的技术使用者:芯盟科技有限公司

技术研发日:2021.07.14

技术公布日:2021/10/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。