1.本公开涉及半导体元件的制造方法。

背景技术:

2.目前,要求省电技术的开发,期待功率器件的低损耗化。功率器件搭载于在混合动力车、电动汽车搭载的变换器等所有的电力变换器。

3.为了实现低损耗的功率器件,能期待实现比现状的硅(si)更高耐压、低损耗的功率器件的sic、gan等新的宽带隙半导体材料受到关注,正在活跃地进行研究开发。其中,氧化镓与sic、gan相比,由于以更大的带隙为代表的物性,在应用于功率器件的情况下,期待进一步的高耐压、低损耗化等优异的器件特性。

4.专利文献1涉及半导体元件的制造方法,公开了在向氧化镓单晶层离子注入mg后进行活性化退火而形成高电阻区域,之后,在高电阻区域上配置金属电极层。

5.现有技术文献

6.专利文献

7.专利文献1:日本特开2016

‑

039194号公报

技术实现要素:

8.发明所要解决的课题

9.在向氧化镓系单晶半导体层通过离子注入而掺杂掺杂剂从而形成了高电阻区域的情况下,有时会在进行了离子注入的部分产生晶体缺陷等损伤。该损伤即使通过后续的退火处理也难以完全恢复。

10.因此,在采用专利文献1所公开的制造方法时,会在产生了这样的损伤的氧化镓系单晶半导体层的表面配置金属电极层,存在由该损伤引起的故障的风险。

11.本公开的目的在于,提供能够降低如上所述的故障的风险的半导体元件的制造方法。

12.用于解决课题的技术方案

13.本公开人发现了能够通过以下的技术方案达成上述课题:

14.《方案1》

15.一种半导体元件的制造方法,包括以下步骤:

16.提供半导体元件前驱体,所述半导体元件前驱体是在氧化镓系单晶半导体层的表面上形成有金属电极层并且在所述氧化镓系单晶半导体层的表面上的、没有层叠所述金属电极层的露出部的至少一部分掺杂有掺杂剂;和

17.对所述半导体元件前驱体进行退火处理,由此使所述掺杂剂向所述氧化镓系单晶半导体层中的与所述金属电极层在层叠方向上重叠的部分扩散。

18.《方案2》

19.根据方案1所述的制造方法,

20.提供所述半导体元件前驱体的步骤包括以下步骤:

21.在氧化镓系单晶半导体层的表面上的一部分层叠所述金属电极层;和

22.在层叠了所述金属电极层后,通过将所述掺杂剂向所述氧化镓系单晶半导体层的表面上的、没有层叠所述金属电极层的所述露出部的至少一部分进行离子注入而掺杂所述掺杂剂。

23.《方案3》

24.根据方案2所述的制造方法,包括以下步骤:

25.通过至少将所述金属电极层的一部分作为掩模而将所述掺杂剂进行离子注入,向所述露出部中的至少与层叠有所述金属电极层的部分相邻的部分掺杂所述掺杂剂。

26.《方案4》

27.根据方案2或3所述的制造方法,

28.向所述氧化镓系单晶半导体层离子注入的所述掺杂剂的剂量是5

×

10

13

cm

‑2~5

×

10

14

cm

‑2。

29.《方案5》

30.根据方案1~4中任一项所述的制造方法,

31.所述氧化镓系单晶半导体层具有基材层及形成在所述基材层上的漂移层,

32.所述金属电极层形成在所述漂移层的表面上,并且,

33.在所述漂移层的表面上的、没有层叠所述金属电极层的露出部的至少一部分掺杂有掺杂剂。

34.《方案6》

35.根据方案5所述的制造方法,

36.所述漂移层的厚度是0.5μm~20.0μm。

37.《方案7》

38.根据方案1~6中任一项所述的制造方法,

39.所述金属电极层是由选自ti、mo、ni及pt的至少一种金属形成的层。

40.《方案8》

41.根据方案1~7中任一项所述的制造方法,

42.所述掺杂剂是受主。

43.《方案9》

44.根据方案8所述的制造方法,

45.所述受主是mg。

46.《方案10》

47.根据方案1~9中任一项所述的制造方法,

48.在1000℃~1200℃的温度下进行所述退火处理。

49.发明效果

50.根据本公开,能够提供能够降低故障的风险的半导体元件的制造方法。

附图说明

51.图1a是在按照本公开的实施方式的制造方法中示出在氧化镓系单晶半导体层10

的表面上进行金属电极体层20的成膜2的状态的示意图。

52.图1b是在按照本公开的实施方式的制造方法中示出金属电极体层20的成膜2后的状态的示意图。

53.图1c是在按照本公开的实施方式的制造方法中示出在氧化镓系单晶半导体层10的表面上离子注入3的状态的示意图。

54.图1d在按照本公开的实施方式的制造方法中示出离子注入3后的状态的示意图。

55.图1e是在按照本公开的实施方式的制造方法中示出退火处理的状态的示意图。

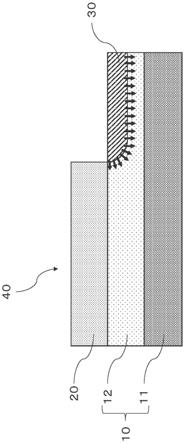

56.图1f是示出由按照本公开的实施方式的制造方法制造的半导体元件50的示意图。

57.图2a是在与本公开的实施方式不同的制造方法中示出在氧化镓系单晶半导体层10的表面上离子注入3的状态的示意图。

58.图2b是在与本公开的实施方式不同的制造方法中示出离子注入3后且退火处理后的状态的示意图。

59.图2c是在与本公开的实施方式不同的制造方法中示出在氧化镓系单晶半导体层10的表面上进行金属电极体层20的成膜的状态的示意图。

60.图3是示出通过动态二次离子质谱分析法(d

‑

sims)测定了实施例1的试样的刚离子注入后及退火处理后的从漂移层的表面起的厚度方向的mg的扩散状态的结果的坐标图。

61.图4是示出通过动态二次离子质谱分析法(d

‑

sims)测定了实施例1的试样的露出部中的从漂移层的表面起的厚度方向的mg的扩散状态的结果的坐标图。

62.图5是示出通过动态二次离子质谱分析法(d

‑

sims)测定了实施例1的试样的从金属电极体层的端部向面内方向内侧25μm的位置处的从漂移层的表面起的厚度方向的mg的扩散状态的结果的坐标图。

63.标号说明

64.1 成膜用抗蚀剂掩模

65.2 金属电极层的成膜

66.3 离子注入

67.4 离子注入用抗蚀剂掩模

68.10 氧化镓系单晶半导体层

69.11 基材层

70.12 漂移层

71.20 金属电极层

72.30 高电阻区域

73.40 半导体元件前驱体

74.50 半导体元件

具体实施方式

75.以下,对本公开的实施方式进行详述。此外,本公开不限于以下的实施方式,能够在公开的主旨的范围内进行各种变形来实施。

76.本公开的制造方法是半导体元件的制造方法,包括以下步骤:提供在氧化镓系单晶半导体层的表面上形成有金属电极层且在上述氧化镓系单晶半导体层的表面上的、没有

层叠上述金属电极层的露出部的至少一部分掺杂有掺杂剂的半导体元件前驱体;及对上述半导体元件前驱体进行退火处理,由此,使上述掺杂剂向上述氧化镓系单晶半导体层中的与上述金属电极层在层叠方向上重叠的部分扩散,在上述氧化镓系单晶半导体层与上述金属电极层之间形成肖特基结。

77.此外,在本公开中,“层叠方向”意味着氧化镓系单晶半导体层与金属电极层的层叠方向。

78.另外,由本公开的制造方法制造的半导体元件也可以在氧化镓系单晶半导体层的表面中的层叠有金属电极层20的表面的相反侧的表面进一步配置有其它层(例如另外的半导体层、金属电极层)。

79.本发明人得到了以下见解:在向氧化镓系单晶半导体层进行离子注入而使掺杂剂掺杂后,若在预定的温度下进行退火处理,则在氧化镓系单晶半导体层内掺杂剂扩散。

80.本发明人基于上述见解而发现了:通过提供在氧化镓系单晶半导体层的表面上形成有金属电极层且在氧化镓系单晶半导体层的表面上的没有层叠金属电极层的露出部的至少一部分掺杂有掺杂剂的半导体元件前驱体,对该半导体元件前驱体在预定的温度下进行退火处理,从而使掺杂剂向氧化镓系单晶半导体层内的与金属电极层在层叠方向上重叠的部分扩散,在该部分形成高电阻区域。

81.在本公开的制造方法中,在半导体元件前驱体中,金属电极层配置于氧化镓系单晶半导体层的表面中的没有进行掺杂剂的掺杂的部分。并且,通过退火处理,掺杂剂向氧化镓系单晶半导体层内的与金属电极层在层叠方向上重叠的部分扩散,在该部分形成高电阻区域。

82.因而,与如专利文献1所公开的那样在高电阻区域上形成金属电极层的情况不同,能够降低由伴随于基于离子注入等的掺杂剂的掺杂而在氧化镓系单晶半导体层产生的损伤引起的故障的风险,并在氧化镓系单晶半导体层中的与金属电极层在层叠方向上重叠的部分形成高电阻区域。

83.使用图1a~图1f更具体地说明。

84.图1a~图1f是示出按照本公开的实施方式的制造方法的示意图。

85.在按照本公开的实施方式的制造方法中,通过进行图1a~图1d所示的一系列工序而提供半导体元件前驱体,之后,通过图1e所示的退火处理而得到如图1f所示的半导体元件。

86.在按照本公开的实施方式的制造方法中,在半导体元件前驱体的提供中,如图1a所示,使用具有基材层11及配置在基材层11上的漂移层12的氧化镓系单晶半导体层10。

87.如图1a所示,在半导体元件前驱体的提供中,首先,将用于金属电极层20形成的成膜用抗蚀剂掩模1配置在漂移层12的表面上,通过蒸镀等而进行金属电极层20的成膜2。

88.之后,如图1b所示,使成膜用抗蚀剂掩模1剥离。

89.接着,如图1c所示,将层叠于漂移层12的表面上的金属电极层20作为离子注入用抗蚀剂掩模,将掺杂剂进行离子注入3。由此,如图1d所示,向没有层叠金属电极层20的露出部的至少一部分掺杂掺杂剂而形成高电阻区域30。

90.通过以上,提供在漂移层12的表面上形成有金属电极层20且在漂移层12的表面上的没有层叠金属电极层20的露出部的至少一部分形成有高电阻区域30的半导体元件前驱

体40。

91.接着,如图1e所示,在预定的温度下对半导体元件前驱体40进行退火处理。由此,如黑的箭头所示,掺杂于漂移层12内的掺杂剂向漂移层12中的与金属电极层20在层叠方向上重叠的部分扩散。即,高电阻区域30在层叠方向上与金属电极层20重叠。

92.通过以上,制造如图1f所示的半导体元件50。此外,半导体元件50也可以在层叠有金属电极层20的表面的相反侧即基材层11的表面上进一步配置有其它的层,例如另外的半导体层、金属电极层,但在图1f中省略。

93.在按照本公开的实施方式的制造方法中,金属电极层20配置于氧化镓系单晶半导体层10的漂移层12的表面中的没有进行离子注入的位置。并且,通过退火处理,掺杂剂向漂移层12中的与金属电极层20在层叠方向上重叠的部分扩散。由此,高电阻区域30在层叠方向上与金属电极层20重叠。因而,漂移层12中的与金属电极层20在层叠方向上重叠的部分没有晶体缺陷等损伤。

94.此外,图1a~图1f并非旨在限定本公开的制造方法。

95.相对于此,在与本公开的实施方式不同的制造方法中,通过进行图2a~图2c所示的一系列工序来得到半导体元件。

96.在与本公开的实施方式不同的制造方法中,如图2a所示,使用具有基材层11及配置在基材层11上的漂移层12的氧化镓系单晶半导体层10。如该图所示,在与本公开的实施方式不同的制造方法中,首先将离子注入用抗蚀剂掩模4配置在漂移层12的表面上,通过离子注入而向漂移层12内掺杂掺杂剂。然后,如图2b所示,通过使离子注入用抗蚀剂掩模4剥离而在漂移层12内形成高电阻区域30。

97.接着,如图2c所示,为了在漂移层12的表面上的与高电阻区域30重叠的部分形成金属电极层20,将成膜用抗蚀剂掩模1配置于漂移层12的表面上,通过蒸镀等进行金属电极层20的成膜2。

98.然后,通过使成膜用抗蚀剂掩模1剥离,制造与图1f所示半导体元件50的同样的半导体元件50。

99.在采用了图2a~图2c所示的制造方法的情况下,由于金属电极层20形成于与高电阻区域30重叠的部分即进行了离子注入的部分的表面上,所以漂移层12中的与金属电极层在层叠方向上重叠的部分具有晶体缺陷等损伤。

100.《半导体元件前驱体的提供》

101.在本公开的制造方法中,半导体元件前驱体是在氧化镓系单晶半导体层的表面上形成有金属电极层且在氧化镓系单晶半导体层的表面上的没有层叠金属电极层的露出部的至少一部分掺杂有掺杂剂的材料。

102.半导体元件前驱体,可以通过使用已经制作出的半导体元件前驱体或者在实施本公开的制造方法时制作而提供。

103.<氧化镓系单晶半导体层>

104.氧化镓系单晶半导体层在没有层叠金属电极层的露出部的至少一部分掺杂有掺杂剂。

105.掺杂剂可以是能够向氧化镓系单晶半导体层掺杂的任意的掺杂剂。掺杂剂可以是受主。作为受主的例子,例如能够举出mg,但没有特别的限定。

106.氧化镓系单晶半导体层能够是α

‑

ga2o3单晶、β

‑

ga2o3单晶或具有其他的晶体结构的ga2o3单晶,优选是β

‑

ga2o3单晶。

107.另外,氧化镓系单晶半导体层能够具有基材层及形成于基材层上的漂移层,金属电极层形成于漂移层的表面上,且能够在漂移层的表面上的没有层叠金属电极层的露出部的至少一部分掺杂有掺杂剂。

108.在此,漂移层是作为半导体元件构成且在使用时供漂移电流流动的层,例如能够通过在由氧化镓系单晶形成的基材层上通过公知的方法使其外延生长而形成。

109.漂移层的厚度可以是0.5μm~20.0μm。

110.漂移层的厚度会对退火处理中的掺杂剂的面内方向上的扩散的程度造成影响。在退火处理中,掺杂剂主要在漂移层中扩散,不容易向基材层扩散。因而,通过调节漂移层的厚度及掺杂量,能够调节高电阻区域的漂移层的面内方向上的扩展。

111.漂移层的厚度可以为0.5μm以上、1.0μm以上、2.5μm以上或5.0μm以上,可以为20.0μm以下、15.0μm以下、10.0μm以下或5.0μm以下。

112.<金属电极层>

113.金属电极层形成于氧化镓系单晶半导体层的表面上。在氧化镓系单晶半导体层具有基材层及漂移层的情况下,金属电极层形成于漂移层的表面上。金属电极层与氧化镓系单晶半导体层接合而形成了肖特基结。

114.金属电极层能够由能够通过与氧化镓系单晶半导体层接合而形成肖特基结且融点比退火处理中的温度高的任意的材料形成。

115.金属电极层例如可以是融点为1000℃以上的金属的层,更具体而言,可以是由选自ti、mo、ni及pt的至少一种金属形成的层。

116.<半导体元件前驱体的制造>

117.在本公开的制造方法中,提供半导体元件前驱体的步骤能够包括以下步骤:在氧化镓系单晶半导体层的表面上的一部分层叠金属电极层;及在层叠了金属电极层后,通过将掺杂剂向氧化镓系单晶半导体层的表面上的没有层叠金属电极层的露出部的至少一部分进行离子注入而掺杂掺杂剂。

118.此外,在上述半导体元件前驱体的制造中,由于离子注入在金属电极层的层叠后进行,所以可理解为:通过离子注入而向氧化镓系单晶半导体层掺杂的掺杂剂向氧化镓系单晶半导体层中的在层叠方向上与金属电极层重叠的部分不掺杂或者实质上不掺杂。

119.(金属电极层的层叠)

120.金属电极层的层叠方法可以是用于形成半导体元件的金属电极层、更具体而言是与半导体形成肖特基结的金属电极层的公知的方法。作为这样的方法,例如能够举出公知的物理蒸镀法或化学蒸镀法等。

121.(掺杂剂的离子注入)

122.掺杂剂可以通过离子注入向没有层叠金属电极层的露出部的至少一部分进行掺杂。此外,掺杂剂的离子注入方法没有特别的限定,能够通过公知的方法来进行。

123.氧化镓系单晶半导体层的表面上的掺杂剂的离子注入的位置优选包括与金属电极层相邻的部分。若将掺杂剂的离子注入对这样的位置进行,则通过之后的退火处理,容易使掺杂剂扩散至氧化镓系单晶半导体层内的在层叠方向上与金属电极层重叠的部分,容易

将高电阻区域形成至该部分。

124.掺杂剂的离子注入也可以通过至少将金属电极层的一部分作为掩模而向露出部中的至少与层叠有金属电极层的部分相邻的部分掺杂掺杂剂来进行。

125.通过将金属电极层的一部分作为掩模而掺杂掺杂剂,容易向与层叠有金属电极层的部分相邻的部分掺杂掺杂剂。由此,在后续的退火处理中容易使掺杂剂向与金属电极层在层叠方向上重叠的部分扩散,能够更精密地控制金属电极层与高电阻区域的重叠宽度。

126.另外,通过将金属电极层的一部分设为掩模,能够省略形成另外的离子注入用抗蚀剂掩模的工序,能够使生产性提高。

127.向氧化镓系单晶半导体层注入的掺杂剂的剂量可以是5

×

10

13

cm

‑2~5

×

10

14

cm

‑2。

128.掺杂剂的剂量会对退火处理中的掺杂剂的面内方向上的扩散的程度造成影响。在退火处理中,掺杂剂主要在漂移层中扩散,不容易向基材层扩散。因而,通过调节漂移层的厚度及掺杂量,能够调节高电阻区域的漂移层的面内方向上的扩展。

129.向氧化镓系单晶半导体层注入的掺杂剂的剂量可以为5

×

10

13

cm

‑2以上、6

×

10

13

cm

‑2以上或7

×

10

13

cm

‑2以上,可以为5

×

10

14

cm

‑2以下、4

×

10

14

cm

‑2以下、3

×

10

14

cm

‑2以下或2

×

10

14

cm

‑2以下。

130.《退火处理》

131.在本公开的制造方法中,对半导体元件前驱体进行退火处理,由此,使掺杂剂向氧化镓系单晶半导体层中的与金属电极层在层叠方向上重叠的部分扩散。

132.退火处理的条件是:在掺杂于氧化镓系单晶半导体层内的掺杂剂会扩散至与金属电极层在层叠方向上重叠的部分的程度的温度及时间下进行。

133.退火处理的温度例如可以为1000℃以上。这是因为,若退火处理的温度为1000℃以上,则掺杂剂容易扩散至氧化镓系单晶半导体层的深部。

134.另外,退火处理的温度可以为1200℃以下。通过将退火处理的温度设为1200℃以下,能够在氧化镓系单晶半导体层的晶体结构特别稳定的状态下使掺杂剂扩散。

135.因此,退火处理的温度优选是1000℃~1200℃。

136.退火处理的温度可以为1000℃以上、1050℃以上、1100℃以上或1150℃以上,可以为1200℃以下、1150℃以下、1100℃以下或1050℃以下。

137.退火处理的时间优选为5分钟以上,更优选为15分钟以上,进一步优选为30分钟以上。通过退火处理的时间是这样的范围,能够使掺杂剂从氧化镓系单晶半导体层的表面更均匀地扩散至内部。

138.退火处理的时间的上限没有特别的限定,但从生产性的观点来看可以设为3小时以内。退火处理中的气氛能够是氮气氛。

139.【实施例】

140.《实施例1》

141.<试样的制备>

142.如以下这样制备了实施例1的试样。

143.作为氧化镓系单晶半导体层,准备了β

‑

ga2o3单晶板。所准备的ga2o3单晶板在β

‑

ga2o3单晶基板上通过外延生长而形成了作为漂移层的β

‑

ga2o3单晶层。此外,漂移层的厚度是5.0μm。

144.使用蒸镀法,在漂移层上作为金属电极层而成膜了直径500μm的ni层。接着,将ni层作为离子注入用掩模,向漂移层中的包括在层叠方向上与ni层相邻的部分的露出部掺杂了作为掺杂剂的mg。之后,在1000℃下进行了30分钟的退火处理。

145.<mg的扩散状态的评价>

146.通过动态二次离子质谱分析法(d

‑

sims),测定了实施例1的试样的刚离子注入后及退火处理后的漂移层的预定位置处的mg的深度方向的扩散状态。

147.将测定结果在图3中示出。

148.如图3所示,在刚离子注入后的试样中,mg集中于从漂移层的表面起的小于1.0μm的深度的区域。相对于此,在退火处理后的试样中,mg扩散至从漂移层的表面起的约5.0μm的深度的区域。这表示着:在退火处理后的试样中,形成了约5.0μm的厚度的高电阻区域。

149.接着,通过动态二次离子质谱分析法(d

‑

sims),测定了退火处理后的实施例1的试样的露出部中的从金属电极体层的端部向面内方向内侧25μm的位置处的从漂移层的表面起的深度方向的mg的扩散状态及从漂移层的表面起的深度方向的mg的扩散状态。

150.将测定结果在图4及图5中示出。

151.图4及图5分别是示出通过动态二次离子质谱分析法(d

‑

sims)测定了实施例1的试样的露出部中的从漂移层的表面起的深度方向的mg的扩散状态的结果及测定了从金属电极体层的端部向面内方向内侧25μm的位置处的从漂移层的表面起的深度方向的mg的扩散状态的结果的坐标图。

152.如图4及图5所示,退火处理后的实施例1的试样的从金属电极体层的端部向面内方向内侧25μm的位置处的mg的深度方向上的扩散状态与露出部中的mg的深度方向上的扩散状态大致相同,不管在哪个位置处,mg都至少从漂移层的表面扩散至深度方向3.0μm附近。

153.该结果表示了:通过退火处理,mg扩散至漂移层中的金属电极体层的下侧部分,即高电阻区域形成到漂移层中的金属电极体层的下侧部分。

154.此外,在图4及图5中,在从漂移层的表面起的深度方向0.1μm附近处mg的浓度尤其高,可认为这是由于在金属电极体层的成膜前就存在的漂移层的表面附着物的影响。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。