具有过孔保护层的半导体装置

1.本技术要求于2020年4月22日在韩国知识产权局提交的第10-2020-0048644号韩国专利申请的优先权的权益,该韩国专利申请的公开内容通过引用全部包含于此。

技术领域

2.公开涉及一种具有过孔保护层的半导体装置。

背景技术:

3.随着其中多个半导体芯片安装在单个半导体装置中的三维(3d)封装件已经被积极地开发,用于形成穿过基底或裸片的竖直电连接的贯穿硅过孔(tsv,又称为“硅通孔”)技术已经被认为是非常重要的。tsv形成工艺包括用于暴露tsv的化学机械抛光(cmp)工艺。需要用于防止在cmp工艺期间对tsv的损坏的技术。

技术实现要素:

4.公开的示例性实施例提供了一种包括过孔保护层的半导体装置。

5.根据公开的示例性实施例的半导体装置可以包括:过孔钝化层,设置在基底的非活性表面上并且包括凹部;贯穿电极,竖直穿透基底和过孔钝化层;以及过孔保护层,与过孔钝化层和贯穿电极水平地叠置并且填充所述凹部。所述凹部形成在过孔钝化层的顶表面中并且与贯穿电极相邻。在水平剖视图中,过孔保护层可以具有围绕贯穿电极的带状。

6.根据公开的示例性实施例的半导体装置可以包括:过孔钝化层,设置在基底的非活性表面上并且包括第一凹部和第二凹部;第一贯穿电极和第二贯穿电极,竖直穿透基底和过孔钝化层,第二贯穿电极具有比第一贯穿电极的水平宽度大的水平宽度;第一过孔保护层,填充第一凹部;以及第二过孔保护层,填充第二凹部。第一凹部和第二凹部形成在过孔钝化层的顶表面中,第一凹部与第一贯穿电极相邻,并且第二凹部与第二贯穿电极相邻。在水平剖视图中,第一过孔保护层可以具有围绕第一贯穿电极的带状,第二过孔保护层可以具有围绕第二贯穿电极的带状。

7.根据公开的示例性实施例的半导体装置可以包括:基底,包括非活性表面和与非活性表面相对形成的活性表面;层间绝缘层,设置在活性表面下方;布线结构,设置在层间绝缘层下方;下钝化层,包括设置在非活性表面上的下水平部、连接到下水平部的下竖直部以及形成在下水平部与下竖直部之间的下凹部;上钝化层,设置在下钝化层上,上钝化层包括设置在下水平部上的上水平部、连接到上水平部的上竖直部以及形成在上水平部与上竖直部之间的上凹部,上竖直部与下竖直部的侧表面接触;贯穿电极,竖直穿透基底、下钝化层、上钝化层和层间绝缘层;以及过孔保护层,与上水平部、上竖直部和贯穿电极水平地叠置并且填充上凹部。在水平剖视图中,过孔保护层可以具有围绕贯穿电极的带状。

8.根据公开的示例性实施例的制造半导体装置的方法可以包括:形成竖直穿透基底的通孔;在通孔中形成贯穿电极;蚀刻基底以暴露贯穿电极的一部分;形成覆盖基底和贯穿电极的过孔钝化层;形成覆盖过孔钝化层并填充过孔钝化层中的凹部的过孔保护材料;以

及执行抛光工艺,以通过使贯穿电极、过孔钝化层和过孔保护材料平坦化形成过孔保护层。

附图说明

9.在考虑以下结合附图的详细描述时,发明构思的以上和其它目的、特征和优点对于本领域技术人员将变得更加明显。

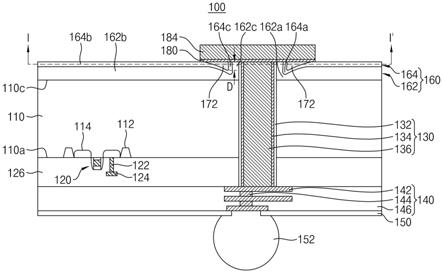

10.图1是根据发明构思的示例实施例的半导体装置的竖直剖视图。

11.图2是图1中所示的半导体装置的沿着线i-i'截取的水平剖视图。

12.图3至图6是根据发明构思的示例实施例的半导体装置的竖直剖视图。

13.图7至图8是根据发明构思的示例实施例的半导体装置的水平剖视图。

14.图9是根据发明构思的示例实施例的半导体装置的竖直剖视图。

15.图10是图9中所示的半导体装置的沿着线ii-ii'截取的水平剖视图。

16.图11至图22是按工艺顺序示出根据发明构思的示例实施例的制造半导体装置的方法的竖直剖视图。

17.图23是根据发明构思的示例实施例的半导体装置的竖直剖视图。

18.图24是图23中所示的半导体装置的沿着线iii-iii'截取的水平剖视图。

19.图25至图26是根据发明构思的示例实施例的半导体封装件的竖直剖视图。

具体实施方式

20.图1是根据发明构思的示例实施例的半导体装置的竖直剖视图。

21.图2是图1中所示的半导体装置的沿着线i-i'截取的水平剖视图。

22.参照图1和图2,半导体装置100可以包括基底110、晶体管120、贯穿电极130、布线结构140、绝缘层150、外部连接端子152、过孔钝化层160、过孔保护层172和导电垫184。

23.基底110可以包括活性表面110a和非活性表面110c,非活性表面110c是与活性表面110a相对形成的表面。非活性表面可以是不包括任何器件的表面,活性表面可以是其上形成器件的表面。基底110可以包括形成在活性表面110a上的器件隔离层112和杂质区114。器件隔离层112可以形成为与杂质区114的外侧表面相邻。基底110可以包括半导体材料。例如,基底110可以是硅基底、锗基底、硅锗基底或绝缘体上硅(soi)基底。在示例实施例中,基底110可以包括iv族半导体、iii-v族化合物半导体或ii-vi族氧化物半导体。

24.晶体管120可以设置在基底110的活性表面110a上,以与杂质区114相邻。例如,杂质区114可以形成在晶体管120的两侧上。半导体装置100还可以包括接触插塞122、内部线124和层间绝缘层126。接触插塞122可以连接到杂质区114,并且内部线124可以连接到接触插塞122。层间绝缘层126可以覆盖基底110的活性表面110a、晶体管120、接触插塞122和内部线124。

25.贯穿电极130可以竖直地穿透基底110、层间绝缘层126和过孔钝化层160。贯穿电极130可以包括过孔绝缘层132、过孔阻挡层134和导电过孔136。过孔阻挡层134可以覆盖并接触导电过孔136的侧表面,过孔绝缘层132可以覆盖并接触过孔阻挡层134的侧表面。在水平剖视图中,贯穿电极130可以具有圆形形状,但不限于此。在示例实施例中,贯穿电极130的水平宽度可以在1μm至5μm的范围内。例如,贯穿电极130的直径可以在1μm至5μm的范围内。

26.布线结构140可以设置在层间绝缘层126的底表面上。布线结构140可以由单层或多层组成。例如,布线结构140可以包括布线层142、将布线层142彼此连接的接触插塞144以及覆盖布线层142和接触插塞144的层间绝缘层146。布线层142可以电连接到贯穿电极130。

27.绝缘层150可以设置在布线结构140的底表面上。绝缘层150可以覆盖层间绝缘层146的底表面,并且可以暴露布线层142的一部分。

28.外部连接端子152可以连接到布线层142的被绝缘层150暴露的部分。外部连接端子152可以经由布线结构140电连接到贯穿电极130。

29.过孔钝化层160可以设置在基底110的非活性表面110c上,并且可以覆盖贯穿电极130的侧表面。过孔钝化层160可以包括下钝化层162和上钝化层164。下钝化层162可以与基底110的非活性表面110c和贯穿电极130的侧表面接触。在竖直剖视图中,下钝化层162可以具有弯曲形状。例如,下钝化层162可以包括形成在其顶表面中的下凹部162a、在水平方向上延伸的下水平部162b以及与贯穿电极130接触的下竖直部162c。下凹部162a可以设置为与贯穿电极130相邻。例如,下凹部162a可以形成在下水平部162b与下竖直部162c之间的拐角中。下凹部162a可以沿着贯穿电极130的外周延伸,并且可以具有圆形的剖面。在水平剖视图中,下竖直部162c的顶表面可以具有带状、环状、甜甜圈形状或环形形状,并且可以围绕贯穿电极130。

30.上钝化层164可以设置在下钝化层162上。在一些实施例中,上钝化层164可以共形地形成在下钝化层162的顶表面上。上钝化层164的一部分可以位于比下钝化层162的水平低的水平处。例如,上钝化层164的一部分可以位于比下钝化层162的下水平部162b的顶表面的竖直水平低的竖直水平处。在竖直剖视图中,上钝化层164可以具有弯曲形状。例如,上钝化层164可以包括形成在其顶表面中的上凹部164a、在水平方向上延伸的上水平部164b以及与下竖直部162c接触的上竖直部164c。上凹部164a可以设置为与贯穿电极130相邻。下竖直部162c可以设置在贯穿电极130与上竖直部164c之间。例如,上凹部164a可以形成在上水平部164b与上竖直部164c之间的拐角中。上凹部164a可以沿着下凹部162a的外周延伸,并且可以具有圆形剖面。在水平剖视图中,上竖直部164c的顶表面可以具有带状、环状、甜甜圈形状或环形形状,并且可以围绕下竖直部162c。在水平剖视图中,上水平部164b可以围绕过孔保护层172。上竖直部164c的顶表面和上水平部164b的顶表面可以位于基本相同的水平处。在本说明书中,下凹部162a和上凹部164a可以统称为凹部。在示例实施例中,过孔钝化层160可以由一个层组成,并且可以包括原硅酸四乙酯(teos)。在示例实施例中,下钝化层162和上钝化层164可以包括sio

x

/sin、sin/sio

x

、sio

x

/sicn或sin/sicn的组合。

31.过孔保护层172可以设置在过孔钝化层160的顶表面上。例如,过孔保护层172可以填充上凹部164a。过孔保护层172可以与贯穿电极130和过孔钝化层160共面。例如,贯穿电极130的顶表面、下竖直部162c的顶表面、上竖直部164c的顶表面、过孔保护层172的顶表面和上水平部164b的顶表面可以彼此共面。过孔保护层172可以与贯穿电极130的一部分和过孔钝化层160的一部分水平地叠置。过孔保护层172的顶表面可以是基本平坦的,并且过孔保护层172的底表面可以是向下凸出的弯曲表面。在水平剖视图中,过孔保护层172可以围绕贯穿电极130,具体来说,可以围绕上竖直部164c。过孔保护层172可以具有带状、环状、甜甜圈形状或环形形状,但不限于此。过孔保护层172可以包括具有比过孔钝化层160的硬度低的硬度的材料。在示例实施例中,过孔保护层172可以具有比上钝化层164的强度低的强

度,并且可以包括聚合物。在水平剖视图中,过孔保护层172的顶表面的宽度w1可以是10μm或更小。从过孔保护层172的顶表面到其下端的深度d可以是0.3μm或更小。

32.导电垫184可以设置在贯穿电极130上。半导体装置100还可以包括设置在导电垫184的底表面上的导电层180。导电垫184的侧表面和导电层180的侧表面可以彼此对齐,使得导电垫184和导电层180在水平剖面中具有相同的宽度。导电垫184可以经由贯穿电极130和布线结构140电连接到外部连接端子152。在示例实施例中,过孔保护层172的外径可以小于导电垫184的宽度。例如,导电垫184可以覆盖过孔保护层172,但不限于此。

33.图3至图6是根据发明构思的示例实施例的半导体装置的竖直剖视图。可以省略与图1和图2中所示的半导体装置的组件相同或类似的组件的详细描述。

34.参照图3,半导体装置200可以包括设置在过孔钝化层260的顶表面上并且围绕贯穿电极130的过孔保护层272。过孔钝化层260可以包括下钝化层262和上钝化层264。下钝化层262可以包括形成在其顶表面中的下凹部262a、在水平方向上延伸的下水平部162b以及与贯穿电极130接触的下竖直部162c。上钝化层264可以包括形成在其顶表面中的上凹部264a、在水平方向上延伸的上水平部164b以及与下竖直部162c接触的上竖直部164c。在示例实施例中,半导体装置200中的下凹部262a和上凹部264a可以形成为比半导体装置100中的下凹部162a和上凹部164a深。过孔保护层272的外径w2可以大于导电垫184的水平宽度。例如,过孔保护层272的一部分可以不被导电垫184覆盖。

35.参照图4,半导体装置300可以包括设置在过孔钝化层360的顶表面上并且围绕贯穿电极130的过孔保护层372。过孔钝化层360可以包括下钝化层362和上钝化层364。下钝化层362可以包括形成在其顶表面中的下凹部362a、在水平方向上延伸的下水平部162b以及与贯穿电极130接触的下竖直部162c。上钝化层364可以包括形成在其顶表面中的上凹部364a、在水平方向上延伸的上水平部164b以及与下竖直部162c接触的上竖直部164c。在示例实施例中,在竖直剖视图中,下凹部362a的深度和上凹部364a的深度可以不均匀。例如,下凹部362a和上凹部364a的定位在贯穿电极130的左边的部分可以形成为比下凹部362a和上凹部364a的定位在贯穿电极130的右边的部分深。在竖直剖视图中,过孔保护层372的尺寸可以不均匀。例如,过孔保护层372的定位在贯穿电极130的左边的部分可以形成为比过孔保护层372的定位在贯穿电极130的右边的部分深且宽。

36.参照图5,半导体装置400可以包括设置在过孔钝化层460的顶表面上并且围绕贯穿电极130的过孔保护层172。过孔钝化层460可以包括围绕贯穿电极130的下钝化层462和上钝化层164。在示例实施例中,下钝化层462可以沿着基底110的非活性表面110c和贯穿电极130的侧表面共形地设置,并且上钝化层164可以不共形地设置。下钝化层462的位于下水平部162b与下竖直部162c之间的拐角可以形成大致直角。

37.参照图6,半导体装置500可以包括设置在过孔钝化层560的顶表面上并且围绕贯穿电极130的过孔保护层172。过孔钝化层560可以包括围绕贯穿电极130的下钝化层162和上钝化层564。在示例实施例中,下钝化层162可以不共形地设置,并且上钝化层564可以共形地设置在下钝化层162上。

38.图7至图8是根据发明构思的示例实施例的半导体装置的水平剖视图。

39.参照图7,半导体装置600可以包括设置在上竖直部164c与上水平部164b之间并且围绕上竖直部164c的过孔保护层672。在示例实施例中,过孔保护层672的水平宽度可以不

均匀。例如,过孔保护层672可以具有不对称的环状,并且可以具有第一宽度w3和第二宽度w4。第二宽度w4可以小于第一宽度w3。

40.参照图8,半导体装置700可以包括设置在上竖直部164c与上水平部164b之间并且围绕上竖直部164c的过孔保护层772。在水平剖视图中,过孔保护层772可以具有不规则形状。例如,过孔保护层772可以包括多个突起部772a和多个凹入部772b。

41.图9是根据发明构思的示例实施例的半导体装置的竖直剖视图。图10是图9中所示的半导体装置的沿着线ii-ii'截取的水平剖视图。

42.参照图9和图10,半导体装置800可以包括设置在过孔钝化层160上的过孔保护层872。在示例实施例中,过孔保护层872可以在水平方向上延伸,并且上钝化层164的上水平部164b可以不被暴露。贯穿电极130的顶表面、下竖直部162c的顶表面、上竖直部164c的顶表面和过孔保护层872的顶表面可以彼此共面。过孔保护层872的位于上水平部164b上的厚度t可以是2μm或更小。

43.图11至图22是按工艺顺序示出根据发明构思的示例实施例的制造半导体装置的方法的竖直剖视图。

44.参照图11,制造半导体装置100的方法可以包括在基底110上形成器件隔离层112、杂质区114、晶体管120、接触插塞122、内部线124、层间绝缘层126和蚀刻停止层128,并且在基底110和层间绝缘层126中形成通孔h。

45.基底110可以包括活性表面110a和非活性表面110b,非活性表面110b是与活性表面110a相对形成的表面。可以在基底110的活性表面110a上形成器件隔离层112和杂质区114。基底110可以包括半导体材料。在示例实施例中,基底110可以包括硅。在示例实施例中,器件隔离层112可以包括由例如氧化硅或氮化硅制成的绝缘层。杂质区114可以包括n型杂质或p型杂质。

46.可以在基底110的活性表面110a上设置晶体管120,以与杂质区114相邻。可以在杂质区114上形成接触插塞122,并且可以在接触插塞122上形成内部线124。可以形成层间绝缘层126以覆盖晶体管120、接触插塞122和内部线124。在示例实施例中,接触插塞122和内部线124可以包括金属、金属氮化物、金属硅化物、金属氧化物、导电碳、多晶硅或它们的组合。层间绝缘层126可以包括氧化硅、氮化硅、氮氧化硅或它们的组合。

47.可以在层间绝缘层126上形成蚀刻停止层128,并且通孔h可以穿透层间绝缘层126并且可以在基底110中形成到预定深度。形成通孔h的步骤可以包括执行反应离子蚀刻(rie)工艺或激光钻孔工艺。

48.参照图12,该方法可以包括形成过孔绝缘材料132a。可以沿着蚀刻停止层128的顶表面和通孔h的内壁形成过孔绝缘材料132a。过孔绝缘材料132a可以包括氧化硅、氮化硅、聚合物或它们的组合。在示例实施例中,过孔绝缘材料132a可以通过化学气相沉积(cvd)工艺形成,并且可以包括氧化硅。

49.参照图13,该方法可以包括形成过孔阻挡材料134a和过孔导电材料136a。可以在过孔绝缘材料132a上形成过孔阻挡材料134a。过孔阻挡材料134a可以形成为包括w、wn、ti、tin、ta、tan和ru中的至少一种的单层或多层结构。在示例实施例中,可以通过物理气相沉积(pvd)工艺、cvd工艺或原子层沉积(ald)工艺共形地形成过孔阻挡材料134a。可以在过孔阻挡材料134a上形成过孔导电材料136a。形成过孔导电材料136a的步骤可以包括执行镀覆

工艺。例如,可以通过cvd工艺或pvd工艺在过孔阻挡材料134a上形成种子层(未示出),并且可以使用种子层作为种子通过镀覆工艺形成过孔导电材料136a。在示例实施例中,过孔导电材料136a可以包括cu、cusn、cumg、cuni、cuzn、cupd、cuau、cuw、w或w合金。

50.参照图14,该方法可以包括执行化学机械抛光(cmp)工艺。例如,可以通过cmp工艺去除图13的产品的上部。可以去除蚀刻停止层128,并且可以暴露层间绝缘层126。可以去除过孔绝缘材料132a的一部分、过孔阻挡材料134a的一部分和过孔导电材料136a的一部分,使得过孔绝缘层132、过孔阻挡层134和导电过孔136保留。过孔绝缘层132、过孔阻挡层134和导电过孔136可以形成贯穿电极130。

51.参照图15,该方法可以包括形成连接到贯穿电极130的布线结构140。可以在层间绝缘层126和贯穿电极130上形成布线结构140。布线结构140可以形成为单层或多层结构。例如,布线结构140可以包括布线层142、将布线层142彼此连接的接触插塞144以及覆盖布线层142和接触插塞144的层间绝缘层146。在示例实施例中,布线层142和接触插塞144可以包括cu。层间绝缘层146可以包括诸如氧化硅或聚合物的低介电材料。

52.参照图16,该方法可以包括形成绝缘层150和外部连接端子152。绝缘层150可以形成在层间绝缘层146上,并且可以暴露布线结构140的布线层142的一部分。外部连接端子152可以形成在绝缘层150上,并且可以连接到布线层142。外部连接端子152可以经由布线结构140电连接到贯穿电极130。

53.参照图17,该方法可以包括蚀刻基底110以暴露贯穿电极130。可以将载体(未示出)附着到绝缘层150和外部连接端子152,使得基底110的非活性表面110b被翻转为向上定位。可以蚀刻非活性表面110b以形成非活性表面110c。蚀刻基底110的步骤可以包括选择性地蚀刻硅的工艺,并且可以进一步执行cmp工艺和研磨工艺。贯穿电极130的一部分可以暴露在基底110的非活性表面110c上方。

54.参照图18,该方法可以包括形成覆盖非活性表面110c和贯穿电极130的下钝化层162。可以通过cvd工艺沉积下钝化层162。在示例实施例中,可以不共形地形成下钝化层162。例如,可以不在基底110的非活性表面110c与贯穿电极130接触的部分上充分地沉积下钝化层162。下钝化层162的顶表面可以包括沿着贯穿电极130的外周形成的下凹部162a。可以在基底110的非活性表面110c与贯穿电极130接触的区域中形成下凹部162a。在示例实施例中,下钝化层162可以包括氧化硅。在另一示例性实施例中,下钝化层162可以共形地沉积。

55.参照图19,该方法可以包括形成覆盖下钝化层162的上钝化层164。可以通过cvd工艺沉积下钝化层162。在示例实施例中,可以不共形地形成上钝化层164。例如,可以不在下钝化层162中的下凹部162a上充分地沉积上钝化层164。上钝化层164的顶表面可以包括沿着下凹部162a形成的上凹部164a。下钝化层162和上钝化层164可以一起构成过孔钝化层160。在示例实施例中,上钝化层164可以包括氮化硅。在另一示例性实施例中,上钝化层164可以共形地沉积。

56.参照图20,该方法可以包括形成过孔保护材料170。过孔保护材料170可以覆盖上钝化层164。过孔保护材料170可以包括具有比下钝化层162或上钝化层164的流动性高的流动性的材料。例如,过孔保护材料170可以包括聚合物,诸如聚酰亚胺、聚羟基苯乙烯(phst)、聚苯并噁唑(pbo)或聚酰胺。过孔保护材料170可以包括具有比过孔钝化层160的强

度低的强度的材料。在示例实施例中,过孔保护材料170可以包括具有比上钝化层164的强度低的强度的材料。

57.该方法还可以包括使过孔保护材料170固化。可以在80℃至400℃的温度下执行固化工艺,并且可以通过固化工艺使过孔保护材料170固化。

58.参照图21,该方法可以包括执行抛光工艺以暴露导电过孔136和过孔钝化层160。可以通过抛光工艺使下钝化层162、上钝化层164和过孔保护材料170与贯穿电极130一起平坦化。可以通过抛光工艺赋予过孔钝化层160弯曲形状。例如,下钝化层162可以包括下凹部162a、在水平方向上延伸的下水平部162b和在竖直方向上延伸的下竖直部162c。下凹部162a可以设置在下水平部162b与下竖直部162c之间。上钝化层164可以包括上凹部164a、在水平方向上延伸的上水平部164b和在竖直方向上延伸的上竖直部164c。上凹部164a可以设置在上水平部164b与上竖直部164c之间。

59.可以使过孔保护材料170平坦化,使得过孔保护层172保留在上钝化层164的第一顶表面与上钝化层164的水平部分之间。进一步参照图2,在平面图中,下钝化层162的下竖直部162c可以围绕贯穿电极130。上钝化层164的上竖直部164c可以围绕下钝化层162的下竖直部162c,并且过孔保护层172可以围绕上钝化层164的上竖直部164c。上钝化层164的上水平部164b可以围绕过孔保护层172。贯穿电极130的顶表面、下竖直部162c的顶表面、上竖直部164c的顶表面、过孔保护层172的顶表面和上水平部164b的顶表面可以彼此共面。

60.如图18和图19中所示,可以通过用过孔保护材料170覆盖过孔钝化层160来降低要通过cmp工艺蚀刻的表面的纵横比。因此,能够防止或最小化抛光工艺期间摩擦力的产生。另外,能够防止或最小化贯穿电极130的断裂。

61.参照图22,该方法可以包括形成导电层180和掩模图案182。可以在图21的产品上沉积导电层180。例如,导电层180可以接触贯穿电极130的顶表面、下竖直部162c的顶表面、上竖直部164c的顶表面、过孔保护层172的顶表面和上水平部164b的顶表面。导电层180可以用作凸块下金属,并且可以包括cr/cr-cu/cu、ti-w/cu、al/ni/cu或镍。掩模图案182可以形成在导电层180上,并且可以暴露导电层180的与贯穿电极130对应的部分。掩模图案182可以包括光致抗蚀剂。

62.返回参照图1,该方法可以包括形成导电垫184。形成导电垫184的步骤可以包括执行镀覆工艺。在示例实施例中,导电垫184可以包括ni、au、cu、al或它们的组合。该方法可以包括去除掩模图案182和选择性地去除导电层180。可以在形成导电垫184之后去除掩模图案182。可以选择性地去除导电层180的未被导电垫184覆盖的部分以暴露过孔钝化层160。

63.图23是根据发明构思的示例实施例的半导体装置的竖直剖视图。图24是图23中所示的半导体装置的沿着线iii-iii'截取的水平剖视图。

64.参照图23和图24,半导体装置900可以包括第一贯穿电极930、第二贯穿电极931、过孔钝化层960、第一过孔保护层972和第二过孔保护层973。在示例实施例中,半导体装置900可以包括具有不同的相应尺寸并且竖直穿透基底110、层间绝缘层126和过孔钝化层960的贯穿电极。半导体装置900的贯穿电极可以是第一贯穿电极930和第二贯穿电极931。例如,第二贯穿电极931的水平宽度可以大于第一贯穿电极930的水平宽度。第一贯穿电极930的水平宽度和第二贯穿电极931的水平宽度可以在1.0μm至12.0μm的范围内。

65.过孔钝化层960可以设置在基底110的非活性表面110c上,并且可以包括下钝化层

962和设置在下钝化层962上的上钝化层964。下钝化层962可以包括第一下凹部962a、下水平部962b、第一下竖直部962c、第二下凹部963a和第二下竖直部963c。

66.下水平部962b可以在基底110的非活性表面110c上沿水平方向延伸。第一下凹部962a可以设置为与第一贯穿电极930相邻。例如,第一下凹部962a可以形成在下水平部962b与第一下竖直部962c之间的拐角中。第一下凹部962a可以沿着第一贯穿电极930的外周延伸,并且可以具有圆形剖面。第二下凹部963a可以设置为与第二贯穿电极931相邻。例如,第二下凹部963a可以形成在下水平部962b与第二下竖直部963c之间的拐角中。第二下凹部963a可以沿着第二贯穿电极931的外周延伸,并且可以具有圆形剖面。在水平剖视图中,第一下竖直部962c可以围绕第一贯穿电极930,并且第二下竖直部963c可以围绕第二贯穿电极931。

67.上钝化层964可以包括第一上凹部964a、上水平部964b、第一上竖直部964c、第二上凹部965a和第二上竖直部965c。

68.上水平部964b可以在下水平部962b上沿水平方向延伸。第一上凹部964a可以形成在上水平部964b与第一上竖直部964c之间的拐角中。第一上凹部964a可以沿着第一下竖直部962c的外周延伸,并且可以具有圆形剖面。第二上凹部965a可以形成在上水平部964b与第二上竖直部965c之间的拐角中。第二上凹部965a可以沿着第二下竖直部963c的外周延伸,并且可以具有圆形剖面。在水平剖视图中,第一上竖直部964c可以围绕第一下竖直部962c,并且第二上竖直部965c可以围绕第二下竖直部963c。在本说明书中,可以将第一下凹部962a和第一上凹部964a统称为第一凹部,可以将第二下凹部963a和第二上凹部965a统称为第二凹部。

69.第一过孔保护层972可以设置在过孔钝化层960的顶表面上。例如,第一过孔保护层972可以填充第一上凹部964a。第一过孔保护层972可以与第一贯穿电极930和过孔钝化层960共面。在水平剖视图中,第一过孔保护层972可以围绕第一上竖直部964c。

70.第二过孔保护层973可以设置在过孔钝化层960的顶表面上。例如,第二过孔保护层973可以填充第二上凹部965a。第二过孔保护层973可以与第二贯穿电极931和过孔钝化层960共面。在水平剖视图中,第二过孔保护层973可以围绕第二上竖直部965c。在示例实施例中,第二过孔保护层973的内径w5可以大于第一过孔保护层972的内径w6。在水平剖视图中,第二过孔保护层973的宽度w7可以大于第一过孔保护层972的宽度w8。第二过孔保护层973可以形成为比第一过孔保护层972深。例如,从第二过孔保护层973的顶表面到其下端的深度可以大于从第一过孔保护层972的顶表面到其下端的深度。

71.连接到第一贯穿电极930和第二贯穿电极931的导电垫184可以具有基本相同的尺寸。

72.图25至图26是根据发明构思的示例实施例的半导体封装件的竖直剖视图。

73.参照图25,半导体封装件1000可以包括第一半导体芯片1010、第二半导体芯片1020、粘合层1022、贯穿电极1030、连接构件1040和包封材料1050。例如,半导体封装件1000可以包括竖直堆叠在第一半导体芯片1010上的多个第二半导体芯片1020。第一半导体芯片1010可以包括形成在其中的贯穿电极1012和形成在其底表面上的外部连接端子1014。贯穿电极1012可以电连接到外部连接端子1014。

74.多个第二半导体芯片1020可以堆叠成堆叠结构。尽管第二半导体芯片1020的数量

被示出为四个,但是公开不限于此。第二半导体芯片1020之间的空间以及第一半导体芯片1010与第二半导体芯片1020之间的空间可以填充有粘合层1022。第二半导体芯片1020可以包括形成在其中的贯穿电极1030。第二半导体芯片1020可以经由连接构件1040彼此连接。例如,连接构件1040可以电连接到贯穿电极1030。包封材料1050可以覆盖第一半导体芯片1010和第二半导体芯片1020。包封材料1050可以包括环氧模塑料(emc)。

75.第一半导体芯片1010和第二半导体芯片1020可以具有与图1和图2中所示的半导体装置100的构造类似的构造。例如,第一半导体芯片1010和第二半导体芯片1020可以包括分别与层间绝缘层126、贯穿电极130、布线结构140、过孔钝化层160和过孔保护层172相同或类似的组件。

76.在示例实施例中,第一半导体芯片1010可以包括应用处理器(ap)芯片(诸如微处理器或微控制器)或逻辑芯片(诸如cpu、gpu、调制解调器、专用ic(asic)或场可编程门阵列(fpga))。第二半导体芯片1020可以包括诸如dram、sram、pram、mram或闪存的存储器芯片。

77.参照图26,半导体封装件1100可以包括中介层1110、第一半导体芯片1150、第二半导体芯片1152、粘合层1156、连接构件1154和包封材料1160。中介层1110可以包括外部连接端子1112、基底1120、贯穿电极1130和器件层1140。外部连接端子1112可以设置在中介层1110的底表面上。基底1120可以是硅基底或印刷电路板。在另一示例性实施例中,基底1120可以包括绝缘材料,诸如聚酰亚胺或预浸料。器件层1140可以设置在基底1120的底表面上。器件层1140可以包括例如金属氧化物半导体场效应晶体管(mosfet)、系统大规模集成(lsi)器件、图像传感器、有源器件或无源器件。

78.中介层1110可以具有与图1和图2中所示的半导体装置100的构造类似的构造。例如,中介层1110可以包括分别与层间绝缘层126、贯穿电极130、布线结构140、过孔钝化层160和过孔保护层172相同或类似的组件。

79.第一半导体芯片1150和第二半导体芯片1152可以安装在中介层1110上。第一半导体芯片1150可以经由中介层1110电连接到第二半导体芯片1152。连接构件1154可以将第一半导体芯片1150和第二半导体芯片1152连接到中介层1110。第一半导体芯片1150和第二半导体芯片1152中的每个与中介层1110之间的空间可以填充有粘合层1156。包封材料1160可以覆盖中介层1110、第一半导体芯片1150和第二半导体芯片1152。包封材料1160可以包括emc。

80.如从以上描述明显的,根据公开的示例性实施例,能够最小化或防止贯穿电极的断裂。

81.尽管已经参照附图描述了公开的实施例,但是本领域技术人员应该理解的是,在不脱离公开的范围并且不改变其必要特征的情况下,可以进行各种修改。因此,上述实施例应该仅以描述性的含义去考虑,而不是出于限制的目的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。