1.本技术涉及显示技术领域,尤其涉及一种显示屏和电子设备。

背景技术:

2.随着显示屏技术的发展,显示屏应用的越来越广泛。但在显示屏的应用过程中,光线的强弱会对应用带来一定的困难。例如,在较暗的环境下使用时,会感到显示屏的亮度太强,容易引起疲劳,而在阳光比较充足的户外时,显示屏的亮度又太低,造成看不清楚屏幕。所以,需要显示屏的亮度可以随着光线强度的改变而改变。因此,需要在显示屏内设置感光单元。而目前感光单元通常设置在显示屏的刘海区,从而降低了电子设备的屏占比。

技术实现要素:

3.本技术实施例提供一种显示屏和电子设备,用于缩小显示屏的刘海区,提高电子设备的屏占比。

4.为达到上述目的,本技术采用如下技术方案:

5.本技术实施例的第一方面,提供一种显示屏,该显示屏具有显示区,该显示屏包括设置于显示区的感光单元和多个亚像素。其中,亚像素具有有效显示区,感光单元包括至少一个感光控制电路。此外,感光控制电路包括开关晶体管和与开关晶体管相耦接的光敏元件,而感光控制电路位于相邻两个亚像素的有效显示区之间。基于此,光敏元件用于对入射至显示屏的光线进行光电转换,并生成电信号。感光控制电路用于在开关晶体管处于导通状态时,输出所述电信号。从而根据获取的电信号对显示屏的亮度进行调节,实现根据光线的亮度调节设备亮度的功能。同时,相比与将光线传感器设置于刘海区的方式,由于该感光单元中的各个感光控制电路设置于亚像素的有效显示区内,可以增大显示屏内用于布局亚像素的区域的面积,从而能够缩小或者去除显示屏的刘海区,提高电子设备的屏占比。

6.可选的,该显示屏还包括第一衬底基板、像素界定层、多个发光器件和第二衬底基板。其中,像素界定层设置于第一衬底基板上,且包括多个像素分隔墙。此外,多个像素分隔墙横纵交叉围设成多个开口,一个发光器件位于一个开口内。而第二衬底基板设置于发光器件远离第一衬底基板的一侧。基于此,感光控制电路在第一衬底基板上的垂直投影位于像素分隔墙在第一衬底基板上的垂直投影的范围内,从而可以避免感光控制电路对像素光路的干扰。

7.可选的,感光控制电路设置于第一衬底基板靠近发光器件的一侧表面上,基于此,可以与第一衬底基板相同,采用mask工艺制作感光控制电路,方便生产,简化生产过程中的工位变更及设备变更。同时也可以方便使感光控制电路在第一衬底基板上的垂直投影位于像素分隔墙在第一衬底基板上的垂直投影的范围内,从而避免感光控制电路对像素光路的干扰。

8.可选的,感光控制电路设置于像素界定层远离第一衬底基板的一侧表面上,可以方便使感光控制电路在第一衬底基板上的垂直投影位于像素分隔墙在第一衬底基板上的

垂直投影的范围内,从而避免感光控制电路对像素光路的干扰。

9.可选的,该显示屏还包括第一衬底基板、第二衬底基板、液晶层和黑矩阵,其中,液晶层设置于第一衬底基板和第二衬底基板之间。黑矩阵位于第二衬底基板靠近第一衬底基板的一侧表面上。基于此,感光控制电路在第二衬底基板上的垂直投影位于黑矩阵在第二衬底基板上的垂直投影的范围内,从而可以避免感光控制电路对像素光路的干扰。

10.可选的,感光控制电路设置于第二衬底基板远离第一衬底基板的一侧表面上,如此一来,可以与第二衬底基板相同,采用mask工艺制作感光控制电路,方便生产,简化生产过程中的工位变更及设备变更。同时也可以方便使感光控制电路位于相邻两个亚像素的有效显示区之间,从而避免感光控制电路对像素光路的干扰。

11.可选的,该显示屏还包括触控层。其中,触控层设置于第二衬底基板远离第一衬底基板的一侧,基于此,感光控制电路设置于触控层远离第一衬底基板的一侧表面上,可以方便使感光控制电路位于相邻两个亚像素的有效显示区之间,从而避免感光控制电路对像素光路的干扰。

12.可选的,该显示屏还包括上偏光片。其中,上偏光片设置于第二衬底基板远离第一衬底基板的一侧,基于此,感光控制电路设置于上偏光片远离第一衬底基板的一侧表面上,可以方便使感光控制电路位于相邻两个亚像素的有效显示区之间,从而避免感光控制电路对像素光路的干扰。

13.可选的,该显示屏还包括盖板。其中,盖板设置于第二衬底基板远离第一衬底基板的一侧,基于此,感光控制电路设置于盖板远离第一衬底基板的一侧表面上,可以方便使感光控制电路位于相邻两个亚像素的有效显示区之间,从而避免感光控制电路对像素光路的干扰。

14.可选的,显示屏还包括横纵交叉的选通信号线和读取信号线。其中,光敏元件包括光敏三极管,光敏三极管的栅极与开关晶体管的第一极相耦接,光敏三极管的第一极与读取信号线相耦接,光敏三极管的第二极与第一电压端相耦接。此外,开关晶体管的栅极与选通信号线相耦接,开关晶体管的第二极与第二电压端相耦接。

15.基于此,当开关晶体管的栅极加载高电压时,开关晶体管导通,此时,光敏三极管的栅极加载高电压,光敏三极管导通,从而将入射至显示屏的光线进行光电转换,并生成电信号,感光控制电路在开关晶体管处于导通状态时,输出电信号,从而实现可以根据读取到的电信号调整显示屏的亮度。

16.可选的,显示屏还包括横纵交叉的选通信号线和读取信号线。其中,光敏元件包括光敏二极管或光敏电阻。光敏元件的第一端与开关晶体管的第一极相耦接,光敏元件的第二端与读取信号线相耦接。此外,开关晶体管的栅极与选通信号线相耦接,开关晶体管的第二极与第一电压端相耦接。

17.基于此,当开关晶体管的栅极加载高电压时,开关晶体管导通,从而将入射至显示屏的光线进行光电转换,并生成电信号,感光控制电路在开关晶体管tc处于导通状态时,输出电信号,从而实现可以根据读取到的电信号调整显示屏的亮度。

18.可选的,感光控制电路还包括电阻。该电阻的第一端与读取信号线相耦接,电阻的第二端与第三电压端相耦接。其中,第一电压端的电压大于第三电压端的电压。如此一来,第一电压端和第三电压端之间可以形成电场,在电场的作用下,光敏三极管将入射至显示

屏的光线进行光电转换,通过测试电阻两端的电压,获取光敏三极管的阻抗变化情况。从而将阻抗的变化情况传输至读取信号线,根据获取的阻抗变化情况调整显示屏的亮度。

19.可选的,显示屏还包括滤光层。该滤光层设置于光敏元件的入光面所在的一侧,且覆盖光敏元件的入光面。其中,滤光层用于对入射至显示屏的光线进行过滤,滤光层包括层叠的氧化硅层、氧化钛层。基于此,通过调整滤光层中氧化硅层和氧化钛层的层数和折射率,使用滤光层可以过滤掉光敏元件的非响应波段。

20.可选的,显示屏还包括挡光结构。该挡光结构设置于光敏元件的入光面所在的一侧,且绕光敏元件的一周设置。从而可以遮挡显示屏自身发出的光线,避免其对感光控制电路采集结果的干扰。

21.可选的,光敏元件的入光面为圆形。此外,光敏元件的入光面半径r与所述挡光结构的高度h的比值为r/h=tanθ,其中,该角度θ为入射光与光敏元件的入光面法线之间的夹角。角度θ在5

°

~30

°

范围内。基于此,缩小了入射光的入射范围,避免了非检测光线射入,从而可以使得检测结果更加准确。

22.可选的,开关晶体管为顶栅型晶体管,显示屏还包括遮光层。其中,遮光层位于开关晶体管的栅极远离开关晶体管的有源层的一侧,且遮光层覆盖开关晶体管的栅极。从而可以避免外界光线对开关晶体管有源层的破坏。

23.本技术实施例的第二方面,提供一种电子设备,该电子设备包括如上所述的任意一种显示屏,该电子设备具有与前述实施例提供的显示屏相同的技术效果,此处不再赘述。

附图说明

24.图1a为本技术实施例提供的一种电子设备的结构示意图;

25.图1b为本技术实施例提供的一种显示屏的结构示意图;

26.图1c为本技术实施例提供的另一种显示屏的结构示意图;

27.图1d为本技术实施例提供的另一种显示屏的结构示意图;

28.图2a为本技术实施例提供的另一种电子设备的结构示意图;

29.图2b为本技术实施例提供的一种感光单元的设置位置示意图;

30.图3a为本技术实施例提供的一种感光控制电路的电路图;

31.图3b为本技术实施例提供的另一种感光控制电路的电路图;

32.图3c为本技术实施例提供的具有感光控制电路的显示屏的一种局部结构示意图;

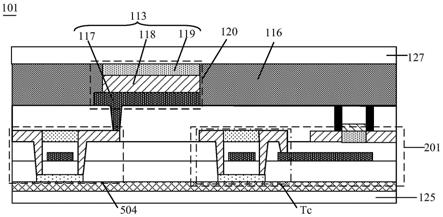

33.图3d为图3c中w区域的局部结构示意图;

34.图3e为图3d中挡光结构的一种结构示意图;

35.图4a为本技术实施例提供的另一种电子设备的结构示意图;

36.图4b为本技术实施例提供的另一种电子设备的结构示意图;

37.图4c为相关技术方案提供的一种电子设备的结构示意图;

38.图4d为沿图4c中的虚线a-a进行剖切的到的剖视图;

39.图4e为本技术实施例提供的一种电子设备的截面结构示意图;

40.图5a为本技术实施例提供的具有感光控制电路的显示屏的另一种局部结构示意图;

41.图5b为本技术实施例提供的具有感光控制电路的显示屏的另一种局部结构示意

图;

42.图5c为本技术实施例提供的具有感光控制电路的显示屏的另一种局部结构示意图;

43.图6a为本技术实施例提供的另一种感光控制电路的电路图;

44.图6b为本技术实施例提供的具有感光控制电路的显示屏的另一种局部结构示意图;

45.图7为本技术实施例提供的另一种感光控制电路的电路图;

46.图8a为本技术实施例提供的另一种显示屏的结构示意图;

47.图8b为沿图8a中的虚线o-o进行剖切的到的剖视图;

48.图8c为本技术实施例提供的另一种显示屏的结构示意图;

49.图8d为本技术实施例提供的另一种显示屏的结构示意图;

50.图8e为本技术实施例提供的另一种显示屏的结构示意图;

51.图9为本技术实施例提供的另一种显示屏的结构示意图;

52.图10a为本技术实施例提供的另一种显示屏的结构示意图;

53.图10b为本技术实施例提供的另一种显示屏的结构示意图;

54.图10c为本技术实施例提供的另一种显示屏的结构示意图;

55.图10d为本技术实施例提供的另一种显示屏的结构示意图。

56.附图标记:

57.01-电子设备;10-显示模组;11-中框;12-后壳;13-感光单元;101-显示屏;202-像素单元;130-衬底;104-像素电路;105-亚像素;105r-红色亚像素;105g-绿色亚像素;105b-蓝色亚像素;aa-有效显示区;106-非有效显示区;220-感光像素;rg-光敏电阻;317-氧化硅(siox)层;318-氧化钛(tiox)层;113-发光器件;116-像素分隔墙;125-第一衬底基板;126-像素界定层;127-第二衬底基板;117-阳极;118-发光层;119-阴极;201-感光控制电路;s-源极;d-漏极;g-栅极;314-开关晶体管的有源层;gl-栅线;tc-开关晶体管;bg-光敏三极管;rl-读取信号线;311-缓冲层;312-栅极绝缘层;302-第一栅极;313-中间层;320-第一凹槽;321-第二凹槽;303-遮光层;322-第三凹槽;323-第四凹槽;324-第五凹槽;304-挡光结构;305-滤光层;310-钝化层;308-光敏晶体管有源层;307-第二栅极;h-挡光结构高度;r-光敏晶体管入光面半径;504-晶体管;120-开口;vd-光敏二极管;501-触控层;502-上偏光片;503-盖板;602-黑矩阵;603-液晶分子;601-液晶层;604-彩膜基板;100-刘海区;200-光线传感器。

具体实施方式

58.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。

59.以下,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,除非另有说明,“多个”的含义是两个或两个以上。

60.此外,本技术中,“上”、“下”等方位术语可以包括但不限于相对附图中的部件示意

置放的方位来定义的,应当理解到,这些方向性术语可以是相对的概念,它们用于相对于的描述和澄清,其可以根据附图中部件附图所放置的方位的变化而相应地发生变化。

61.在本技术中,除非另有明确的规定和限定,术语“连接”应做广义理解,例如,“连接”可以是固定连接,也可以是可拆卸连接,或成一体;可以是直接相连,也可以通过中间媒介间接相连。此外,术语“耦接”可以是实现信号传输的电性连接的方式。“耦接”可以是直接的电性连接,也可以通过中间媒介间接电性连接。

62.本技术实施例提供一种电子设备。该电子设备包括手机(mobile phone)、平板电脑(pad)、电脑、电视、智能穿戴产品(例如,智能手表、智能手环)、虚拟现实(virtual reality,vr)终端设备、增强现实(augmented reality ar)等具有显示功能的电子产品。本技术实施例对上述电子设备的具体形式不做特殊限制。

63.为了方便说明,以下以电子设备01为如图1a所示的手机为例。在此情况下,上述电子设备01主要包括显示模组10、中框11以及后壳12。中框11位于显示模组10和后壳12之间。显示模组10、后壳12分别与中框11相连接。其中,后壳12和中框11之间形成的容纳腔用于容纳电池、摄像头(图1a中未示出),以及如图1a所示的印刷电路板(printed circuit board,pcb)等电子元器件。

64.此外,显示模组10用于显示图像,其包括如图1b所示的显示屏101,该显示屏101具有多个像素(pixel)单元202。在本技术的一些实施例中,像素排布可以如图1b所示,一个像素单元202包括一个红(red,r)色亚像素105r、一个绿(green,g)色亚像素105g以及一个蓝(blue,b)色亚像素105b。示例的,红色亚像素105r和绿色亚像素105g沿x方向位于同一行,蓝色亚像素105b位于另一行,且与红色亚像素105r沿y轴方向位于同一列。对于图1b所示的像素排布方式,蓝色亚像素105b的右侧,绿色亚像素105g的下方可以不用设置亚像素。从而使得沿y方向位于同一列的相邻两个绿色亚像素105g之间具有一定的间隙。

65.需要说明的是,图1b是以同一像素单元202中红色亚像素105r和绿色亚像素105g沿x轴方向位于同一行,蓝色亚像素105b位于下一行为例进行的说明。在本技术的另一些实施例中,同一像素单元202中红色亚像素105r和蓝色亚像素105b可以沿x轴方向位于同一行,而绿色亚像素105g位于下一行,或者绿色亚像素105g和蓝色亚像素105b可以沿x轴方向位于同一行,红色亚像素105r位于下一行三种组合。

66.在本技术的另一些实施例中,显示屏101的像素排布方式还可以如图1c所示,同一个像素单元202中的红色亚像素105r、绿色亚像素105g和蓝色亚像素105b可以沿x轴方向依次排布于同一行。需要说明的是,关于红、绿、蓝三原色亚像素105的排列方式可以根据需求而定,本技术对此不做限定。例如,上述显示屏101的亚像素105的排列方式还可以为红色亚像素、蓝色亚像素以及绿色亚像素面积不相等的pentile像素排列方式(也可以称为p排列)、rgb-delta像素排列方式(也可以称为d排列)等。

67.对于图1b或图1c所示的任意一种像素排布方式,任意一个亚像素105具有有效显示区(active area,aa),以及位于该aa区周边的非有效显示区106。上述亚像素105的aa区为该亚像素105中真正用于显示图像的区域。在此情况下,上述任意两个相邻的亚像素105的aa区之间的非有效显示区106不用于显示图像。

68.通常情况下,在较暗的环境下使用显示屏101时,会感到显示屏101的亮度太强,容易引起疲劳,而在阳光比较充足的户外时,显示屏101的亮度又太低,造成看不清楚屏幕,给

应用带来困难。

69.基于此,本技术实施例提供的电子设备01还具有能够根据光线对显示屏101的亮度进行调节的功能。在此情况下,该电子设备01还可以包括如图2a中的感光单元13。其中,感光单元13可以包括至少一个如图2b所示的感光像素220。需要说明的是,图2b是以感光单元13包括多个感光像素220为例进行的说明,上述任意一个感光像素220中设置有感光控制电路201。

70.由上述可知,相邻两个亚像素aa区之间的区域为非有效显示区106,该非有效显示区106不会显示图像。因此,为了避免感光单元13中各个感光控制电路201对显示屏显示的图像造成干扰,上述感光单元13中的各个感光控制电路201可以间隔设置。在本技术的一些实施例中,感光控制电路201可以位于相邻两个亚像素105的有效显示区aa之间的非有效显示区106内(例如图1b和图1c所标识的位置)。或者,在本技术的另一些实施例中,如图1d所示,感光控制电路201可以位于相邻两个像素单元202之间的非有效显示区106内。

71.如图3a所示,每个感光控制电路201包括开关晶体管tc和与开关晶体管tc相耦接的光敏元件(例如,图3a所示的光敏三极管bg)。其中,开关晶体管tc可以为薄膜晶体管(thin filmtransistor,tft)或者mos管。以下为了方便说明,均是以开关晶体管tc为tft为例进行的说明。

72.需要说明的是,本技术实施例中,任意一个tft可以包括栅极(gate,g)、有源层(active layer,al)以及第一极,例如为源极(source,s)以及第二极,例如为漏极(drain,d)。或者,晶体管的第一极可以为漏极d,第二极为源极s。本技术对此不做限定,为了方便举例说明,以下均是以晶体管的第一极为漏极d,第二极为源极s为例进行的说明。

73.此外,当开关晶体管tc为tft时,开关晶体管tc可以为顶栅型晶体管或者底栅型晶体管,当其为顶栅型晶体管时,开关晶体管tc的栅极g相对于有源层al更远离衬底。在此情况下,为了避免开关晶体管tc的有源层314受到外界光线的破坏,显示屏101还可以包括遮光层,其中,遮光层位于开关晶体管tc的栅极g远离开关晶体管tc的有源层al的一侧,且遮光层覆盖开关晶体管tc的栅极g。当其为顶栅型晶体管时,开关晶体管tc的栅极g相对于有源层al更靠近衬底。本技术对此不做限定,为了方便举例说明,以下均是以开关晶体管tc为顶栅型晶体管为例进行的说明。

74.基于此,在本技术的一些实施例中,如图3a所示,光敏元件可以为光敏三极管bg。其中,光敏三极管bg的结构与开关晶体管tc类似,即可以为tft或者mos管。当光敏三极管bg为tft时,该光敏三极管bg可以为顶栅型或者底栅型晶体管。为了方便说明,以下是以光敏三极管bg为顶栅型为例进行的说明。此外,光敏三极管bg和开关晶体管tc不同之处在于光敏三极管bg的有源层处接入了一个光敏二极管。上述中开关晶体管tc和光敏元件相耦接是指光敏三极管bg的栅极g与开关晶体管tc的第一极相耦接。

75.在此情况下,显示屏101还可以包括如图2b所示的横纵交叉的选通信号线gl和读取信号线rl。其中,光敏三极管bg的第一极,例如,图3a中光敏三极管bg的漏极(drain,d)与读取信号线rl相耦接,开关晶体管tc的栅极(gate,g)与选通信号线gl相耦接。此外,光敏三极管bg的第二极与第一电压端v1相耦接,开关晶体管tc的第二极,例如图3a中光敏三极管bg的源极(source,s)与第二电压端v2相耦接。

76.基于此,gl的输入信号可以控制开关晶体管tc的导通,当选通信号线gl接收选通

信号后,开关晶体管tc导通,此时,v2的电压可以加载到光敏三极管bg的栅极g,使光敏三极管bg导通。

77.此外,在本技术的另一些实施例中,上述v1和v2的电压可以不同。此时,v1可以大于v2,v1也可以小于v2,只要能够起到导通开关晶体管tc和光敏三极管bg即可。或者,在本技术的另一些实施例中,如图3b所示,上述v1和v2的电压可以相同。此时,开关晶体管tc和光敏三极管bg的第一极可以连接同一个电压端v1。

78.如图3c(沿图1b中的虚线e-e进行剖切得到的剖视图,仅为显示屏101中具有感光控制电路201所在的部分)所示,当光线射至光敏三极管bg的表面时,会导致光敏三极管bg中的有源层308发生光电转换效应,使光敏三极管bg有源层308的阻抗发生变化,而在光敏三极管bg有源层308的两端形成电荷的累积或者消耗(如图3c所示,有源层308的左侧为正电荷,右侧为负电荷)。

79.在本技术的另一些实施例中,如图3a,感光控制电路201还可以包括电阻r,其中,电阻r的第一端c与读取信号线rl相耦接,电阻r的第二端d与第三电压端v3相耦接,此外,第一电压端v1的电压大于第三电压端v3的电压。在本技术的一些实施例中,第三电压端v3可以接地。

80.如此一来,当选通信号线gl按照一定的频率开启时,第一电压端v1和第三电压端v3之间可以形成电场。在电场的作用下,上述光敏三极管bg有源层308两端累积的电荷之间可以形成电流(如图3c所示,电流的方向为正电荷指向负电荷的方向),而从rl端输出电信号。其中,一定的频率例如可以是20hz,或者根据需求设定,从而达到满足精确度和功耗等要求。在本实施例中,可以通过测试电阻r两端的电压,获取光敏三极管bg的阻抗变化情况。

81.之后,cpu可以根据获取的阻抗变化情况调整显示屏101的亮度。例如,调整脉冲宽度调制(pulse widthmodulation,pwm)中的占空比,当需要增加亮度时,可以减少占空比的值,当需要降低亮度时,可以增大占空比的值。由于此为本领域技术人员的现有技术,此处不再赘述。

82.需要说明的是,cpu内部需要提前设置阻抗和显示屏亮度之间的对应关系。另外,需要在电子设备01处于初始状态时,测试基准电压,作为后期电压测试的基准。具体如下:

83.初始状态下,开关晶体管tc的栅极g设置为0偏压,此时,开关晶体管tc关闭,v1和v2设置为正偏压。需要说明的是,此处v1也可以设定为负偏压,或者根据需求进行设定,本技术对此不做限定。而v2用于在开关晶体管tc打开的状态下开启光敏三极管bg。

84.然后,选通信号线gl接收选通信号,给开关晶体管tc的栅极g加载高电压(以开关晶体管tc为n型晶体管为例),使开关晶体管tc导通,光敏三极管bg在开关晶体管tc导通后,提供给光敏三极管bg高电压,使光敏三极管bg导通,然后在rl端读出电阻r两端的电压值,作为基准电压。

85.基于此,由上述可知,光线入射至光敏三极管bg表面时,会转换成电信号,然而,外界光线中的某部分光线进入光敏三极管bg表面后,不容易引起光敏三极管bg发生光电转化。所以为了解决上述问题。在本技术的一些实施例中,如图3c所示,显示屏101还可以包括滤光层305。

86.该滤光层305设置于光敏三极管bg的入光面所在的一侧,且覆盖光敏三极管bg的入光面,滤光层305用于对入射至显示屏101的光线进行过滤,从而过滤掉光敏三极管bg的

非响应波段,提高感光控制电路201光信号采集的准确性。其中,如图3d所示(图3c中w部分对应的放大图),滤光层305可以包括层叠的氧化硅(siox)层317、氧化钛(tiox)层318(图中仅是氧化硅(siox)层317和氧化钛(tiox)318堆叠方式的一种示例),通过调整氧化硅(siox)层317和氧化钛(tiox)318的层数和折射率,调整滤光层305可过滤的光线波段。例如,当感光控制电路201中的上述光敏元件对红外波段不响应时,可以通过调整氧化硅(siox)317层和氧化钛(tiox)318的层数和折射率,使得滤光层305可以过滤掉红外波段的光线。

87.需要说明的是,本技术对siox和tiox的层数、堆叠方式和折射率不做限定,本领域技术人员可以通过实验、测试、仿真等方式对siox和tiox的层数、堆叠方式和折射率进行设置,只要能够根据光敏三极管bg对光线波长的要求滤除非响应波段即可。

88.此外,由上述可知,感光单元13的各个感光控制电路201位于相邻两个aa区之间的非显示区域106,然而aa区由上述可知,能够显示图像,当该aa区显示图像时,该aa区发出的光线,会存在入射至非显示区域106的可能,从而导致影响感光控制电路201的采集结果。为了解决上述问题,显示屏101还可以包括如图3c所示的挡光结构304,该挡光结构304设置于光敏三极管bg的入光面所在的一侧,且绕光敏三极管bg的一周设置(如图3e所示),从而可以遮挡亚像素105的光线入射至光敏三极管bg。

89.在本技术的一些实施例中,光敏三极管bg的入光面可以为如图3e所示的圆形,此时,如图3d所示,光敏三极管bg的入光面的半径r与挡光结构304的高度h的比值为r/h=tanθ,当角度θ在5

°

~30

°

范围内时,可以缩小入射光的入射范围,避免非检测光线的射入,从而使得检测结果更加准确。其中,角度θ为入射光与光敏元件,例如光敏三极管bg的入光面法线之间的夹角。例如,在本技术的一些实施例中,上述角度θ可以为5

°

、10

°

、15

°

、20

°

或者30

°

。

90.需要说明的是,以上述感光单元13包括如图4a所示的四个感光控制电路201为例,上述四个感光控制电路201可以分别设定在如图4a所示的显示屏101的四个顶角对应的位置,此时,相比于如图4c所示相关技术中,电子设备01中设置刘海区100(刘海区100是指在显示屏101的显示区挖一个槽,用于设定其他电子元件,例如,摄像头,home键等)设置一个光线传感器200的方式,精确度更高。

91.或者,在本技术的另一些实施例中,以上述感光单元13包括如图4b所示的八个感光控制电路201,显示屏101的两侧可以分别设置四个感光控制电路201,此时,感光单元13中的各个感光控制电路201既可以测试光线强度,对显示屏101的亮度进行调节,又可以检测手部遮挡位置,从而判断手部所在进行的操作。本技术对感光控制电路201的设定位置不做限定,可根据需求进行设定。

92.由上述可知,在本技术的实施例中,显示屏101可以包括设置于显示区的多个感光控制电路201和多个亚像素,其中,亚像素具有有效显示区。上述多个感光控制电路201可以构成用于对环境光进行检测的感光单元13。此外,感光控制电路201包括开关晶体管tc和与开关晶体管tc相耦接的光敏元件,在此情况下,感光控制电路201位于相邻两个亚像素的有效显示区之间。基于此,光敏元件用于对入射至显示屏101的光线进行光电转换,并生成电信号,感光控制电路201用于在开关晶体管tc处于导通状态时,输出所述电信号。从而根据获取的电信号对显示屏的亮度进行调节,实现根据光线的亮度调节设备亮度的功能。

93.此外,由上述可知如图4c所示的相关方案中,光线传感器200设置于电子设备01的刘海区100,因此如图4d(沿图4c中的a-a进行剖切得到的剖视图)所示,电子设备01的盖板503下方,在上述刘海区100所在位置因为设置有光线传感器200,会使得刘海区100内无法设置亚像素105,导致屏幕的屏占比下降。然而相比于图4c所示的方案,本技术的方案如图4e所示,可以将感光控制电路201设置于相邻两个像素单元202之间的非有效显示区106内。或者,将感光控制电路201设置于相邻两个亚像素105之间的非有效显示区106内,因此可以增加盖板503下方能够布局亚像素105的区域的面积,所以可以缩小或者去除显示屏101的刘海区,从而提高电子设备01的屏占比。

94.以下以图3b为例对制备显示屏101中感光控制电路201的制作过程的工艺进行说明。

95.首先,如图5a所示,在衬底130上,用化学气相沉积(chemical vapor deposition,cvd)的方法形成缓冲层311,之后,用物理气相沉积(physical vapor deposition,pvd)的方法在缓冲层311远离衬底130的一侧表面形成开关晶体管tc的有源层314。

96.然后,在形成有缓冲层311的衬底上,采用cvd工艺形成栅极绝缘层312。该栅极绝缘层312覆盖开关晶体管tc的有源层314。接下来,在栅极绝缘层312远离衬底130的一侧表面用pvd工艺,可以同时形成tc的第一栅极302和bg的第二栅极307。之后,采用cvd工艺形成覆盖在第一栅极302和第二栅极307上的中间层313。

97.之后,利用干法刻蚀工艺在开关晶体管tc的有源层314的两端形成第一凹槽320和第二凹槽321,以及在第二栅极307的一端形成第三凹槽322。使第一凹槽320和第二凹槽321贯穿中间层313和栅极绝缘层312至开关晶体管tc的有源层314。使第三凹槽322贯穿中间层313至第二栅极307。

98.接下来,如图5b所示,通过pvd工艺在开关晶体管tc的有源层314的两端分别形成源极s和漏极d。

99.由于光敏三极管bg的源极s和漏极d与开关晶体管tc的源极s和漏极d同层同材料,因此,在制作开关晶体管tc的源极s和漏极d时,可以使用同一个掩模版,同时制作光敏三极管bg的源极s和漏极d。此外,开关晶体管tc的漏极d与光敏三极管bg的源极s之间绝缘。构成光敏三极管bg的源极s和漏极d与开关晶体管tc的源极s和漏极d的材料可以是铜(cu)、铝(al)、金(au)等金属材料。

100.需要说明的是,本技术实施例中,“同层”指的是采用同一成膜工艺(例如涂覆工艺)形成用于形成特定图形的膜层,然后利用同一掩模板(mask)通过一次构图工艺形成的层结构。根据特定图形的不同,同一构图工艺可能包括多次曝光、显影或刻蚀工艺,而形成的层结构中的特定图形可以是连续的也可以是不连续的,这些特定图形还可能处于不同的高度或者具有不同的厚度。

101.之后,在开关晶体管tc的源极s和漏极d之间形成遮光层303,且遮光层303与开关晶体管tc的源极s和漏极d相连接,其中,构成该遮光层303的材料可以是黑色吸光材料(例如黑色光刻胶)或者表面镀层绝缘的金属(例如铝(al)、钛(ti)等),可以分别利用光刻或者金属溅射的方法制备。

102.然后,在光敏三极管bg的源极s和漏极d之间形成光敏三极管bg的有源层308,使得光敏三极管bg的有源层308与光敏三极管bg的源极s和漏极d分别连接,其中,构成光敏三极

管bg的有源层308的材料可以是半导体材料,例如多晶硅、非晶硅等,可以通过cvd工艺制备,也可以是有机半导体材料,例如并五苯、异丙基硅炔基并五苯等,可以通过光刻与涂覆方法制备。

103.接下来,为了保证感光控制电路201采集光信号的准确性,如图5c所示,可以在光敏三极管bg有源层308远离第一衬底基板125的一侧表面通过cvd工艺形成滤光层305,过滤掉光敏三极管bg非响应波段。

104.之后,用钝化层310覆盖滤光层305,再用干法刻蚀工艺在钝化层310内形成第四凹槽323和第五凹槽324,其中,第四凹槽323和第五凹槽324贯穿钝化层310。

105.最后,在第四凹槽323和第五凹槽324内形成挡光结构304,其中,构成挡光结构304的材料可以是黑色吸光材料(例如黑色光刻胶)或者表面镀层绝缘的金属(例如铝(al)、钛(ti)等),同样,可以分别利用光刻或者金属溅射的方法制备。

106.在本技术的另一些实施例中,感光控制电路201中的光敏元件可以为光敏二极管vd。

107.如图6a所示,光敏二极管vd的第一端a与开关晶体管tc的第一极相耦接,光敏二极管vd的第二端b与读取信号线rl相耦接,此外,开关晶体管tc的栅极与选通信号线gl相耦接,开关晶体管tc的第二极与第一电压端v1相耦接。

108.在本技术的另一些实施例中,感光控制电路201还可以包括电阻r。

109.在本示例中,其工作原理与上述方案(光敏元件为光敏三极管bg的方案)基本相同,不同之处在于:上述方案中,需要给第一栅极302加载高电压,使开关晶体管tc导通,光敏三极管bg在开关晶体管tc导通后,提供给第二栅极307高电压,使光敏三极管bg导通,即光敏三极管bg是在开关晶体管tc导通后才导通,此时,光敏三极管bg具有放大电流的作用。而本示例中,光敏二极管vd本来就是导通的,第一栅极302只起到打开开关晶体管tc的作用,光敏二极管vd也不具有放大电流的作用,其他过程同上所述,此处不再赘述。

110.图6b为图1b中沿虚线e-e进行剖切得到的具有上述光敏二极管vd的显示屏101的剖视图,与上述方案不同之处在于:开关晶体管tc的第一极不与第二栅极307连接,开关晶体管tc的第一极与光敏二极管vd的a端相连。其他设置方式同上所述,此处不再赘述。

111.制备上述感光控制电路201的工艺与当光敏元件为光敏三极管bg的方案的制备工艺的不同之处在于:本示例中没有在第二栅极307的一端形成第三凹槽322,且开关晶体管tc的第一极与光敏二极管vd的a端相连。其他过程同上所述,此处不再赘述。

112.需要说明的是,本示例中,第二栅极307不起作用,只是为了与上述当光敏元件为光敏三极管bg时的方案保持一致,如此一来,可使本示例与上述方案使用同一个掩模版,从而方便同时生产上述两种类型的产品,简化工艺。此外,在本示例中也可以没有第二栅极307。

113.在本技术的另一些实施例中,感光控制电路201中的光敏元件可以为光敏电阻rg。如图7所示,光敏电阻rg的第一端i与开关晶体管tc的第一极相耦接,光敏电阻rg的第二端g与读取信号线rl相耦接,此外,开关晶体管tc的栅极与选通信号线gl相耦接,开关晶体管tc的第二极与第一电压端v1相耦接。

114.在本技术的另一些实施例中,感光控制电路201还可以包括电阻r。其工作原理与当光敏元件为光敏二极管vd的方案相同,此处不再赘述。

115.此外,图1b中沿虚线e-e进行剖切得到的具有上述光敏电阻rg的感光控制电路201的剖视图与图6b相同,只是将图6b中的光敏二极管vd更换成光敏电阻rg,此处不再赘述。

116.上述是对显示屏101中感光控制电路201的制作过程进行的说明,以下对具有该感光控制电路201的显示屏101的结构进行举例说明。

117.示例一

118.本示例中,显示屏101为能够自发光的显示屏101。

119.如图8a所示,上述能够自发光的显示屏101可以具有阵列排布的多个亚像素(sub pixel)105。此外,上述显示屏101包括位于亚像素105内像素电路104和发光器件113。像素电路104驱动发光器件113发光,以使得显示屏101中的各个亚像素105能够按照预设的灰阶进行显示。

120.在本技术的一些实施例中,上述发光器件113可以为有机发光二极管(organic light emitting diode,oled)。或者,在本技术的另一些实施例中,上述发光器件113可以为微型的发光二极管(light emittingdiode,led),例如micro led,或者mini led。本技术对发光器件113的类型不做限定,只要发光器件113能够在像素电路104的驱动下进行发光即可。以下为了方便说明,均是以发光器件113为oled为例进行的举例说明。

121.在此情况下,显示屏101还可以包括如图8b(沿图8a中的虚线o-o进行剖切得到的剖视图)所示的,第一衬底基板125、第二衬底基板127。上述发光器件113设置于第一衬底基板125与第二衬底基板127之间。第一衬底基板125用于承载上述发光器件113,该第二衬底基板127用于防止空气中的水、氧进入发光器件113,而对发光器件113产生不良影响。

122.基于此,在本技术的一些实施例中,如图8b所示,上述感光控制电路201可以设置于第一衬底基板125靠近第二衬底基板127的一侧。或者,在本技术的另一些实施例中,可以将感光控制电路201设置于第二衬底基板127远离第一衬底基板125的一侧。以下描述中会对感光控制电路201的设置方式进行详细的举例说明。

123.在本技术的一些实施例中,上述显示屏101可以为柔性显示屏。此时,构成第一衬底基板125的材料可以为柔性材料,例如有机材料。上述第二衬底基板127可以为封装层,该封装层包括用于作为柔性基材的多层有机薄膜封装层,以及用于阻隔水、氧的多层无机薄膜封装层。有机薄膜封装层和无机薄膜封装层交叉设置,且该封装层靠近空气和靠近发光器件113的一层薄膜为无机薄膜封装层。或者,在本技术的另一些实施例中,当上述显示屏101为硬质显示屏时,构成第一衬底基板125和第二衬底基板127的材料可以均为硬质的透明材料。例如,玻璃、蓝宝石、硬质的树脂材料等。在此情况下,上述第二衬底基板127可以为封装盖板。

124.此外,显示屏101还可以包括如图8c所示的设置于该第一衬底基板125上的像素界定层(pixel definitionlayer,pdl)126。上述像素界定层126可以包括多个像素分隔墙116,多个像素分隔墙116横纵交叉围设成多个开口120(图5a中可看出像素分隔墙116为横纵交叉设置)。上述显示屏101的多个发光器件113中的一个上述发光器件113可以设置于上述多个开口120中的一个开口120中。

125.其中,发光器件113所在位置即为亚像素105的有效显示区(active area,aa)。发光器件113包括依次远离第一衬底基板125一侧的阳极117、发光层118和阴极119。在此情况下,阴极119和阳极117通电后,发光层118在阴极119和阳极117形成的电场的作用下发出光

线。像素分隔墙116用于将相邻的亚像素105隔离开,界定出亚像素105的区域。此外,构成像素分隔墙116的材料可以是氧化硅(siox)、氮化硅(sinx)等,像素分隔墙116可以透过光线。

126.需要说明的是,从图8c中可以看出,像素电路104在远离第一衬底基板125的一侧设置有像素分隔墙116,即像素分隔墙116覆盖于像素电路104的表面,为了方便说明,在图8a中,像素电路104的表面并未显示出像素分隔墙116。

127.在此情况下,为了避免感光控制电路201对像素光路的干扰,感光控制电路201可以位于相邻两个亚像素105的有效显示区之间,由上述可知,有效显示区即为与发光器件113对应的位置。而为了使感光控制电路201可以位于相邻两个亚像素105的有效显示区之间,感光控制电路201在第一衬底基板125上的垂直投影需位于像素分隔墙116在第一衬底基板125上的垂直投影的范围内。

128.在本技术的一些实施例中,为了将感光控制电路201设置于第一衬底基板125靠近第二衬底基板127的一侧,如图8d所示,可以直接在第一衬底基板125靠近第二衬底基板127的一侧的表面上制作上述感光控制电路201中的开关晶体管tc和光敏元件。感光控制电路201在第一衬底基板125上的垂直投影位于像素分隔墙116在第一衬底基板125上的垂直投影的范围内,具体设置方式同上所述,此处不再赘述。

129.其中,感光控制电路201中的开关晶体管tc和像素电路104中的晶体管504可以共用,也可以不共用(图中显示的为不共用的方案),可根据需求设定,本技术不做限定。当感光控制电路201中的开关晶体管tc和像素电路104中的晶体管504共用时,可以通过像素电路104,既控制像素,又控制感光控制电路201。当不共用时,可根据需要采集数据的频率,设定开关晶体管tc通断的频率,从而达到降低功耗的目的。

130.需要说明的是,上述是以感光控制电路201中光敏元件为光敏三极管bg为例进行的说明,在本示例中,光敏元件还可以是光敏二极管vd或者光敏电阻,此时,在显示屏101的上述剖视图中,只是将图8d中光敏三极管bg更换成光敏二极管vd或者光敏电阻,具体设置同上所述,此处不再赘述。

131.在本技术的另一些实施例中,为了将该感光控制电路201设置于第二衬底基板127远离第一衬底基板125的一侧,如图8e所示,可以直接在第二衬底基板127远离第一衬底基板125一侧的表面上,制作上述感光控制电路201中的开关晶体管tc和光敏元件。为了避免感光控制电路201对像素光路的干扰,感光控制电路201在第一衬底基板125上的垂直投影需位于像素分隔墙116在第一衬底基板125上的垂直投影的范围内,从而使得感光控制电路201位于相邻两个亚像素105的有效显示区之间。

132.在本实施例中,光敏元件也可以设置为光敏三极管bg、光敏二极管vd或光敏电阻(图8e中以光敏元件为光敏三极管bg为例),关于感光控制电路201的设置方式,相比于上述感光控制电路201设置于第一衬底基板125靠近发光器件113的一侧表面的方式,只是将第一衬底基板125换成第二衬底基板127,其他相同,具体设置同上所述,此处不再赘述。

133.在本技术的另一些实施例中,感光控制电路201可以设置于像素界定层126远离第一衬底基板125的一侧表面上。为了避免感光控制电路201对像素光路的干扰,感光控制电路201在第一衬底基板125上的垂直投影需位于像素分隔墙116在第一衬底基板125上的垂直投影的范围内,从而使得感光控制电路201位于相邻两个亚像素105的有效显示区之间。

134.在本实施例中,光敏元件也可以设置为光敏三极管bg、光敏二极管vd或光敏电阻,

关于感光控制电路201的设置方式,相比于上述感光控制电路201设置于第一衬底基板125靠近发光器件113的一侧表面的方式,只是将第一衬底基板125换成像素界定层126,其他相同,具体设置同上所述,此处不再赘述。

135.在本技术的另一些实施例中,如图9所示,在显示屏101还包括触控层501,该触控层501设置于第二衬底基板127远离第一衬底基板125的一侧,此时,感光控制电路201可以设置于触控层128远离第一衬底基板125的一侧表面上。为了避免感光控制电路201对像素光路的干扰,感光控制电路201在第一衬底基板125上的垂直投影需位于像素分隔墙116在第一衬底基板125上的垂直投影的范围内,从而使得感光控制电路201位于相邻两个亚像素105的有效显示区之间。

136.在本实施例中,光敏元件也可以设置为光敏三极管bg、光敏二极管vd或光敏电阻,关于感光控制电路201的设置方式,相比于上述感光控制电路201设置于第一衬底基板125靠近发光器件113的一侧表面的方式,只是将第一衬底基板125换成触控层501,其他相同,具体设置同上所述,此处不再赘述。

137.在本技术的另一些实施例中,如图9所示,显示屏101还可以包括上偏光片502,该上偏光片502设置于第二衬底基板127远离第一衬底基板125的一侧,此时,感光控制电路201可以设置于上偏光片502远离第一衬底基板125的一侧表面上。为了避免感光控制电路201对像素光路的干扰,感光控制电路201在第一衬底基板125上的垂直投影需位于像素分隔墙116在第一衬底基板125上的垂直投影的范围内,从而使得感光控制电路201位于相邻两个亚像素105的有效显示区之间。

138.在本实施例中,光敏元件也可以设置为光敏三极管bg、光敏二极管vd或光敏电阻,关于感光控制电路201的设置方式,相比于上述感光控制电路201设置于第一衬底基板125靠近发光器件113的一侧表面的方式,只是将第一衬底基板125换成上偏光片502,其他相同,具体设置同上所述,此处不再赘述。

139.在本技术的另一些实施例中,如图9所示,显示屏101还包括盖板503,该盖板503设置于第二衬底基板127远离第一衬底基板125的一侧,此时,感光控制电路201可以设置于盖板503远离第一衬底基板125的一侧表面上。为了避免感光控制电路201对像素光路的干扰,感光控制电路201在第一衬底基板125上的垂直投影需位于像素分隔墙116在第一衬底基板125上的垂直投影的范围内,从而使得感光控制电路201位于相邻两个亚像素105的有效显示区之间。

140.在本实施例中,光敏元件也可以设置为光敏三极管bg、光敏二极管vd或光敏电阻,关于感光控制电路201的设置方式,相比于上述感光控制电路201设置于第一衬底基板125靠近发光器件113的一侧表面的方式,只是将第一衬底基板125换成盖板503,其他相同,具体设置同上所述,此处不再赘述。

141.需要说明的是,由于第一衬底基板125和第二衬底基板127与感光控制电路201相同,都采用mask工艺制作。因此,当感光控制电路201设置于第二衬底基板127远离第一衬底基板125的一侧表面上或者第二衬底基板127远离第一衬底基板125的一侧表面上时,可以方便工艺生产,简化生产过程中的工位变更及设备变更。所以,在设置感光控制电路201时,为优选方案。

142.示例二

143.本示例中,显示屏101为液晶显示屏(liquid crystal display,lcd)101。由于液晶显示屏不能自发光,因此需要背光模组(back light unit,blu)向液晶显示屏101提供光源,以使得液晶显示屏101中如图10a所示的各个亚像素(sub pixel)105能够发光,从而实现图像显示。

144.上述lcd101可以包括如图10b(沿图10a中的虚线f-f进行剖切得到的剖视图)所示的,第一衬底基板125、彩膜(color filter,cf)基板604、液晶层601、第二衬底基板127,以及依次远离第二衬底基板127的触控层501、上偏光片502以及盖板503。在第一衬底基板125上,每个亚像素105内设置有像素(pixel)电路(图中未示出)。像素电路可以用于控制液晶层601中,与该像素电路所在的亚像素105位置处对应的液晶分子603的偏转角度,从而可以控制blu提供的光线穿过该亚像素105的量,达到控制亚像素105显示灰阶的目的。

145.为了避免不同有效显示区aa之间的干扰,不同有效显示区aa之间设置有黑矩阵602,其中,黑矩阵602之间的区域即为有效显示区。此外,第一衬底基板125和第二衬底基板127之间形成有用于容纳液晶层601的液晶盒(cell)。第二衬底基板127用于避免空气中的水、氧进入液晶层601,对液晶分子603产生破坏。构成第一衬底基板125和第二衬底基板127的材料可以均为硬质的透明材料。例如,玻璃、蓝宝石、硬质的树脂材料等。在此情况下,上述第二衬底基板127可以为封装盖板。

146.在此情况下,在上述电子设备01具有能够根据光线对显示屏101的亮度进行调节的功能时,该电子设备01还包括感光控制电路201,为了避免感光控制电路201对像素光路的干扰,感光控制电路201可以位于相邻两个亚像素105的有效显示区之间。

147.由上述可知,相邻两个亚像素105的有效显示区之间的位置即为与黑矩阵602对应的位置。而为了使感光控制电路201可以位于相邻两个亚像素105的有效显示区之间,感光控制电路201在第二衬底基板127上的垂直投影需位于黑矩阵602在第二衬底基板127上的垂直投影的范围内。

148.在本技术的一些实施例中,如图10b所示,感光控制电路201可以设置于第二衬底基板127远离第一衬底基板125的一侧。具体的,如图10c所示,可以直接在第二衬底基板127远离第一衬底基板125一侧的表面上,制作上述感光控制电路201中的开关晶体管tc和光敏元件。

149.在本示例中,感光控制电路201在第二衬底基板127上的垂直投影位于黑矩阵602在第二衬底基板127上的垂直投影的范围内,其他设置同上所述,此处不再赘述。

150.此外,本示例中,光敏元件也可以设置为光敏二极管vd或光敏电阻,此时,在显示屏101的上述剖视图中,只是将图10c中光敏三极管bg更换成光敏二极管vd或者光敏电阻,具体设置同上所述,此处不再赘述。

151.在本技术的另一些实施例中,如图10d所示,显示屏101还可以包括触控层501,该触控层501设置于第二衬底基板127远离第一衬底基板125的一侧,此时,感光控制电路201可以设置于触控层501远离第一衬底基板125的一侧表面上。为了避免感光控制电路201对像素光路的干扰,感光控制电路201在第二衬底基板127上的垂直投影需位于黑矩阵602在第二衬底基板127上的垂直投影的范围内,从而使得感光控制电路201位于相邻两个亚像素105的有效显示区之间。

152.在本示例中,光敏元件也可以设置为光敏三极管bg、光敏二极管vd或光敏电阻,关

于感光控制电路201的设置方式,相比于上述将感光控制电路201设置于第二衬底基板127远离第一衬底基板125的一侧表面上的方式,只是将第二衬底基板127换成触控层501,其他相同,具体设置同上所述,此处不再赘述。

153.在本技术的另一些实施例中,如图10d所示,显示屏101还可以包括上偏光片502,该上偏光片502设置于第二衬底基板127远离第一衬底基板125的一侧,此时,感光控制电路201可以设置于上偏光片502远离第一衬底基板125的一侧表面上。为了避免感光控制电路201对像素光路的干扰,感光控制电路201在第二衬底基板127上的垂直投影需位于黑矩阵602在第二衬底基板127上的垂直投影的范围内,从而使得感光控制电路201位于相邻两个亚像素105的有效显示区之间。

154.在本实施例中,光敏元件也可以设置为光敏三极管bg、光敏二极管vd或光敏电阻,关于感光控制电路201的设置方式,相比于上述将感光控制电路201设置于第二衬底基板127远离第一衬底基板125的一侧表面上的方式,只是将第二衬底基板127换成上偏光片502,其他相同,具体设置同上所述,此处不再赘述。

155.在本技术的另一些实施例中,如图10d所示,显示屏101还可以包括盖板503,该盖板503设置于第二衬底基板127远离第一衬底基板125的一侧,此时,感光控制电路201可以设置于盖板503远离第一衬底基板125的一侧表面上,且为了避免感光控制电路201对像素光路的干扰,感光控制电路201在第二衬底基板127上的垂直投影需位于黑矩阵602在第二衬底基板127上的垂直投影的范围内,从而使得感光控制电路201位于相邻两个亚像素105的有效显示区之间。

156.在本实施例中,光敏元件也可以设置为光敏三极管bg、光敏二极管vd或光敏电阻,关于感光控制电路201的设置方式,相比于上述将感光控制电路201设置于第二衬底基板127远离第一衬底基板125的一侧表面上的方式,只是将第二衬底基板127换成盖板503,其他相同,具体设置同上所述,此处不再赘述。

157.需要说明的是,由于像素电路104可以控制液晶层601中液晶分子603的偏转角度,从而使得穿过亚像素105的光线的量不同,达到控制亚像素105显示灰阶的目的,因此,液晶层下方存在不透光的情况。所以,为了方便制作,当显示屏101为液晶显示屏时,本技术优先考虑将感光控制电路201设置在液晶层601的上方。

158.本技术实施例还提供一种电子设备,该电子设备包括如上所述的任意一种显示屏,该电子设备具有与前述实施例提供的显示屏相同的技术效果,此处不再赘述。

159.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何在本技术揭露的技术范围内的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。