1.本发明涉及一种快闪存储器(flash memory)等半导体装置,尤其涉及待机(standby)模式或深度省电(deep power down)模式下的运行。

背景技术:

2.与非(nand)型快闪存储器能以页面(page)为单位来进行读出或编程,而且能以块(block)为单位来进行擦除。例如,专利文献(日本专利特开2006

‑

252748号公报)所示的快闪存储器公开了下述技术:在待机模式与常规(normal)运行模式下,对页面缓冲器(page buffer)/感测电路供给不同的电源电压,由此来减少待机模式的消耗电力。

3.快闪存储器中,有响应来自用户的命令来进行读出、编程、擦除等的主动(active)模式与可受理来自用户的命令的待机模式。在待机模式下,内部电路的运行受到限制,以使消耗电力达到一定以下,但在从用户输入有命令时,必须立即响应此命令。因此,虽说是待机模式,但在逻辑(logic)电路或寄存器(register)等易失性电路中仍会产生截止泄漏(off leak)电流,截止泄漏电流会随着元件尺寸的收缩(shrink)而增加,而且,在使用内部电源电压的情况下,必须使内部电源电压检测电路运行,从而会消耗一定程度的电力。即,难以削减待机模式下的消耗电流。

4.为了进一步削减待机模式下的消耗电力,有时根据快闪存储器不同,搭载有深度省电模式(以下称作dpd模式)。在dpd模式下,关停(cut off)对用于待机模式的一部分内部电路的内部供给电源,而削减截止泄漏电流。dpd模式例如是通过dpd开始命令来进入所述模式,并通过dpd解除命令来从所述模式恢复。dpd模式为了使关停的电路正常运行而需要一定的时间,但取代于此,具有能够大幅降低消耗电力的优点(merit)。

5.图1表示搭载有串行外设接口(serial peripheral interface,spi)功能的nand型快闪存储器向dpd模式转变时的运行波形的一例。在待机模式时,通过将芯片选择(chip select)信号/cs设为低电平(low level)来选择快闪存储器,在此期间,与时钟(clock)信号同步地从数据输入端子di输入dpddpd命令(89h)。快闪存储器在从dpd命令的输入开始经过了一定期间tdp的时刻t

dpd

,转变至dpd模式,而阻断对特定的内部电路的内部供给电压。在时刻t

dpd

之前的期间,消耗待机模式的电流,在时刻t

dpd

之后的期间,消耗dpd模式的电流。

6.图2表示现有的快闪存储器的支持dpd模式的待机用内部电压生成电路的一例。内部电压生成电路10包含串联连接在外部电源电压vcc(例如3.3v)与gnd电位之间的p沟道金属氧化物半导体(p

‑

channel metal oxide semiconductor,pmos)晶体管(transistor)p1及pmos晶体管p2、电阻梯(ladder)lad、以及对电阻梯lad的经电阻分割的电压va与基准电压vref进行比较的比较器cmp,对于晶体管p1的栅极,施加有dpd使能(enable)信号dpden,对于晶体管p2的栅极施加比较器cmp的比较结果,在晶体管p2与电阻梯之间连接有电压供给节点intvdd。

7.待机模式时,dpd使能信号dpden为l电平,晶体管p1、晶体管p2导通。为了降低由电阻梯lad所消耗的电流,电阻梯lad被设定为高电阻。另外,在电压供给节点intvdd输出目标

电压时,选择电压va的分接(tap)位置,以使va=vref。另外,在非待机模式时运行的通常的内部电压生成电路的电阻比图2的电阻梯lad低,在电压供给节点intvdd,例如生成2.4v的电压。

8.当用户依据图1所示的序列来输入dpd命令时,快闪存储器的控制器在从命令的输入计起的tdp时间以内,使dpd使能信号dpden由l电平变为h电平,使晶体管p1断开,阻断外部电源电压vcc。由此,不对连接于电压供给节点intvdd的电路供给电力,较待机模式进一步节省消耗电力。

9.这样,在现有的快闪存储器中存在下述问题:为了从待机模式转变至dpd模式,用户必须输入dpd命令,若是不支持dpd命令的快闪存储器,便无法进行向dpd模式的转变。此种问题并不限于快闪存储器,在其它半导体装置中也同样。

技术实现要素:

10.本发明的半导体装置包括:半导体集成电路,能够响应来自外部的输入信号而运行;测量部件,对从半导体装置进入待机模式的时间点开始的时间进行测量;检测部件,检测所述测量部件的测量时间已到达一定时间的情况;以及生成部件,当由所述检测部件检测到一定时间时,生成用于使所述待机模式的消耗电力进一步降低的省电使能信号。

11.根据本发明,能够不进行用于向省电模式转变的命令等的输入,而从待机模式自动转变至省电模式。因此,即使是不支持用于向省电模式转变的命令等的半导体装置,也能转变至省电模式。

附图说明

12.图1是表示现有的快闪存储器向dpd模式转变时的运行波形的一例的图;

13.图2是表示现有的快闪存储器的支持dpd模式的待机模式用内部电压生成电路的一例的图;

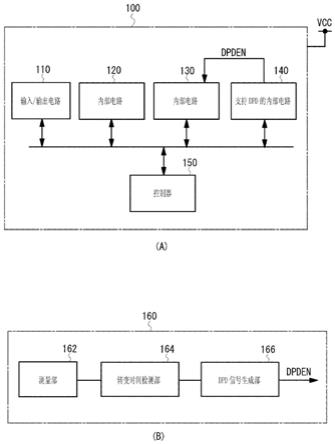

14.图3的(a)是表示本发明的实施例的半导体装置的概略构成的图,图3的(b)是表示支持dpd的内部电路的dpd判定部的功能构成的图;

15.图4是表示本发明的实施例的支持dpd模式的待机模式用内部电压生成电路的构成的图;

16.图5是表示图4所示的内部电压生成电路的各部的运行波形的图;

17.图6是表示本发明的实施例的内部电压生成电路的另一构成例的图;

18.图7是表示适用本发明的实施例的nand型快闪存储器的构成的图。

19.[符号的说明]

[0020]

10、200:内部电压生成电路

[0021]

100:半导体装置

[0022]

110:输入/输出电路

[0023]

120、130、140:内部电路

[0024]

150:控制器

[0025]

160:dpd判定部

[0026]

162:测量部

[0027]

164:转变时间检测部

[0028]

166:dpd信号生成部

[0029]

180_1:第一内部电路

[0030]

180_2:第二内部电路

[0031]

200_1:第一内部电压生成电路

[0032]

200_2:第二内部电压生成电路

[0033]

210、230:逻辑

[0034]

220:计数器

[0035]

300:快闪存储器

[0036]

310:存储单元阵列

[0037]

320:输入/输出缓冲器

[0038]

330:地址寄存器

[0039]

340:控制器

[0040]

350:字线选择电路

[0041]

360:页面缓冲器/感测电路

[0042]

370:列选择电路

[0043]

380:内部电压产生电路

[0044]

ax:行地址信息

[0045]

ay:列地址信息

[0046]

cmp、cmp1、cmp2:比较器

[0047]

/cs:芯片选择信号

[0048]

di:数据输入端子

[0049]

diva:第一电压

[0050]

divb:第二电压

[0051]

dpdclk:时钟信号

[0052]

dpden:dpd使能信号

[0053]

intvdd、intvdd_1、intvdd_2:电压供给节点lad:电阻梯

[0054]

p1、p2、q:pmos晶体管

[0055]

t1、t2、t3、t

dpd

:时刻

[0056]

tdp:一定期间

[0057]

va:电压

[0058]

vcc:外部电源电压

[0059]

vdden:切换控制信号

[0060]

vers:擦除电压

[0061]

vpass:通过电压

[0062]

vpgm:写入电压

[0063]

vread:读出通过电压

[0064]

vref:基准电压

具体实施方式

[0065]

本发明的半导体装置并无特别限定,例如在nand型或者或非(nor)型快闪存储器、动态随机存取存储器(dynamic random access memory,dram)、静态随机存取存储器(static random access memory,sram)、逻辑、专用集成电路(application specific integrated circuit,asic)、数字信号处理器(digital signal processor,dsp)等中实施。

[0066]

接下来,参照附图来详细说明本发明的实施例。图3的(a)及图3的(b)是表示本实施例的半导体装置100的构成例的图。半导体装置100是包含输入/输出电路110、内部电路120、内部电路130、内部电路140、控制器150而构成。这些电路是被集成在半导体基板上的集成电路。控制器150可经由输入/输出电路110而从外部接收命令、控制信号、数据、地址等输入信号,并基于所接收的命令或控制信号等输入信号来控制内部电路120、内部电路130、内部电路140的运行。另外,经内部电路120、内部电路130、内部电路140处理的数据可经由输入/输出电路110而输出至外部。内部电路120、内部电路130、内部电路140所进行的处理的内容为任意,并无特别限定。控制器150是使用硬件和/或软件而构成,例如可为微控制器(micro controller)、可编程逻辑(programmable logic)、状态机(state machine)等。

[0067]

对于半导体装置100,供给外部电源电压vcc(例如3.3v),内部的集成电路被供给外部电源电压vcc或者由外部电源电压vcc而生成的内部供给电压vdd。一实施方式中,半导体装置100可包含多个电力消耗模式。主动模式下,内部电路能够全规格(full specification)运行而无消耗电力的限制。待机模式下,能够依据所决定的要求来降低内部电路的消耗电力,并能响应命令等输入信号。待机模式例如是在内部电路结束了所决定的运行时、或者响应来自外部的命令或控制信号而决定,此种待机模式是在半导体装置100中预先定义。待机模式下,例如停止升压电路(电荷泵(charge pump)电路),或者停止时钟振荡器,或者间歇地进行内部供给电压vdd的生成,或者将互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)逆变器设为三态(tristate)状态。dpd模式下,能够阻断特定的内部电路的电力供给,以进一步降低待机模式的消耗电力。

[0068]

现有的半导体装置中,为了从待机模式向dpd模式转变,需要来自外部的命令的输入。与此相对,本实施例的半导体装置100不需要用于从待机模式向dpd模式转变的命令或控制信号的输入,而能够自动进入dpd模式。dpd模式的解除例如是通过来自外部的任意命令或控制信号的输入而实施。

[0069]

如图3的(a)所示,半导体装置100包含支持dpd的内部电路140。所述支持dpd的内部电路140至少在待机模式时运行。一实施方式中,支持dpd的内部电路140也可在进入待机模式时,响应来自控制器150的使能信号而运行。另外,在另一实施方式中,支持dpd的内部电路140也可贯穿主动模式及待机模式而持续运行。

[0070]

本实施例的支持dpd的内部电路140具备判定是否从待机模式向dpd模式转变的功能,在判定为要向dpd模式转变时,生成用于阻断电力供给的dpd使能信号dpden。图3的(a)及图3的(b)的示例中,由支持dpd的内部电路140所生成的dpd使能信号dpden被供给至其它的内部电路130,内部电路130响应dpd使能信号dpden而阻断供给至自身的电力(外部电源电压vcc或内部电压vdd中的任一个皆可)。由此,在dpd模式下,半导体装置的消耗电力较待机模式进一步降低。另外,此处,表示了dpd使能信号dpden被供给至一个内部电路130的示

例,但dpd使能信号dpden也可被供给至多个内部电路。

[0071]

图3的(b)是表示支持dpd的内部电路140中所含的dpd判定部的功能构成的图。dpd判定部160为了判定是否从待机模式向dpd模式转变,而包含测量部162、转变时间检测部164及dpd信号生成部166。dpd判定部160是使用硬件和/或软件来实施。

[0072]

测量部162对从进入待机模式的时间点开始的时间进行测量。若支持dpd的内部电路140在待机模式时启动,则进入待机模式的时间点可为支持dpd的内部电路140开始运行的时刻,或者,若支持dpd的内部电路140从控制器150被通知待机模式,则进入待机模式的时间点可为由表示所述待机模式的信号所确定的时刻。测量部162并不特别限定此构成,例如可包含对时钟信号进行计数的计数器。

[0073]

转变时间检测部164对由测量部162所测量的时间进行监测,对向dpd模式转变的时间进行检测。具体而言,当测量时间与预定的时间一致时,判定为要向dpd模式转变。换言之,当待机模式经过了预定的时间时,判定为要向dpd模式转变。

[0074]

当由转变时间检测部164监测到向dpd模式的转变时间时,dpd信号生成部166生成用于阻断电力供给的dpd使能信号dpden。图3的(a)的示例中,dpd使能信号dpden被供给至内部电路130。

[0075]

接下来说明支持dpd的内部电路140的具体电路。图4是表示支持dpd的内部电压生成电路的构成的图。支持dpd的内部电压生成电路200是由外部电源电压vcc(例如3.3v)来生成内部电压vdd(例如2.4v)的电路,如此图所示,包含两个比较器cmp1、cmp2、逻辑210、pmos晶体管q、电阻梯lad、计数器220及逻辑230而构成。

[0076]

在外部电源电压vcc与gnd之间的电流路径,串联连接有pmos晶体管q与包含多个串联电阻的电阻梯lad。对于晶体管q的栅极,施加从逻辑210输出的切换控制信号vdden,当切换控制信号vdden为l电平时,晶体管q导通,从外部电源电压vcc供给电力。在晶体管q与电阻梯lad之间,连接有电压供给节点intvdd,从电压供给节点intvdd供给内部电压vdd。在电压供给节点intvdd,连接有一个或多个负载电路。

[0077]

电阻梯lad连接于电压供给节点intvdd与gnd之间。若内部电压生成电路200仅在待机模式时运行,则为了抑制待机模式时的消耗电力,电阻梯lad包含高电阻的电阻。另外,在电阻梯lad的经电阻分割的、第一选择的分接位置生成第一电压diva,在第二选择的分接位置生成第二电压divb。第一电压diva大于第二电压divb(diva>divb)。

[0078]

比较器cmp1在非反相输入端子(

‑

)输入基准电压vref,在反相输入端子( )输入第一电压diva,并将表示比较结果的h或l电平的输出提供给逻辑210。另一个比较器cmp2在非反相输入端子(

‑

)输入基准电压vref,在反相输入端子( )输入第二电压divb,并将表示比较结果的h或l电平的输出提供给逻辑210。

[0079]

逻辑210基于比较器cmp1及比较器cmp2的比较结果来生成切换控制信号vdden。一实施方式中,逻辑210在进入待机模式的时间点,使切换控制信号vdden迁移至h电平,将晶体管q设为非导通。通过停止外部电源电压vcc的供给,从而电压供给节点intvdd的电压经由电阻梯lad而放电至gnd。此时的电压供给节点intvdd的电压随着电阻梯lad的电阻与连接于电压供给节点intvdd的负载的电容的rc时间常数而变化。由于存在第一电压diva>第二电压divb的关系,因此在比较器cmp1的比较结果由h电平迁移至l电平后,比较器cmp2的比较结果由h电平迁移至l电平。

[0080]

当比较器cmp1、比较器cmp2的比较结果均变为l电平时,逻辑210将切换控制信号vdden由h电平迁移至l电平,使晶体管q导通。由此,从外部电源电压vcc供给电力,第一电压diva及第二电压divb上升,比较器cmp1、比较器cmp2的比较结果均变为h电平,逻辑210响应于此而将切换控制信号vdden由l电平迁移至h电平,将晶体管q设为非导通。

[0081]

直至第一电压diva及第二电压divb变得小于基准电压vref为止的时间,即,直至比较器cmp1、比较器cmp2的比较结果均变为l电平为止的时间是根据rc时间常数而决定。若内部电压生成电路200仅在待机模式时运行,则通过将电阻梯lad设为高电阻而加大rc时间常数,从而能够延长直至使晶体管q导通为止的时间,且降低供给有外部电源电压vcc时的消耗电力。

[0082]

逻辑210进而基于比较器cmp1、比较器cmp2的比较结果来生成时钟信号dpdclk,并将其提供给计数器220。具体而言,当检测到第一电压diva及第二电压divb均变得小于基准电压vref时,响应于此而生成具备一定的脉宽的时钟信号dpdclk。例如,时钟信号dpdclk可为与切换控制信号vdden同步的时钟信号。

[0083]

计数器220对时钟信号dpdclk的时钟进行计数,并将其计数结果提供给逻辑230。计数器220在dpd模式被解除时,通过重置(reset)信号而重置。逻辑230接收计数器220的计数值,检测计数值是否已到达预定的次数,当已到达时,生成用于阻断电力供给的dpd使能信号dpden。另外,逻辑230在dpd模式被解除时,响应重置信号而将dpd使能信号设为失效(disable)。

[0084]

接下来,将内部电压生成电路200的运行波形示于图5,说明此电路的运行。假定在时刻t1,半导体装置100由主动模式转变为待机模式。当内部电压生成电路200以主动模式运行时,从外部电源电压vcc供给有电力,第一电压diva及第二电压divb大于基准电压vref,比较器cmp1、比较器cmp2的比较结果处于h电平的状态。此时,逻辑210也可响应表示待机模式的stby而开始运行。即,逻辑210与比较器cmp1、比较器cmp2的比较结果无关地使切换控制信号vdden迁移至h电平,将晶体管q设为非导通。由此,外部电源电压vcc的电力供给被阻断,电压供给节点intvdd的电压逐渐变小。

[0085]

在时刻t2,当第一电压diva及第二电压divb变得小于基准电压vref时,逻辑210使切换控制信号vdden迁移至l电平,使晶体管q导通。由此,从外部电源电压vcc供给电力,电压供给节点intvdd的电压上升。在时刻t3,当第一电压diva及第二电压divb变得大于基准电压vref时,逻辑210将切换控制信号vdden迁移至h电平,将晶体管q设为非导通。逻辑210生成使切换控制信号vdden反相的时钟信号dpdclk,此时钟由计数器220进行计数。

[0086]

以后,反复同样的运行,当由逻辑230检测到计数器220对时钟信号dpdclk的时钟的计数数量与预定的数量一致时,生成用于阻断电力供给的dpd使能信号dpden,将此信号供给至特定的内部电路。所述特定的内部电路响应dpd使能信号dpden而阻断外部电源电压vcc或内部电压vdd的电力供给。

[0087]

这样,根据本实施例,能够不从外部输入用于向dpd模式转变的命令,而从待机模式自动转变为dpd模式。因此,即使是不支持用于向dpd模式转变的命令的半导体装置,也能够利用dpd模式,另外,用户便利性提高。

[0088]

所述实施例中,时钟信号dpdclk的脉宽是根据rc时间常数来决定。通常,电阻梯lad的电阻是根据待机模式的消耗电流的要求来规定,电压供给节点intvdd的负载电容是

基于负载的大小或稳定性来规定。因此,没有用于对时钟信号dpdclk的脉宽进行控制的灵活性(flexibility)。

[0089]

因此,如图6所示,本实施例的变形例包括两个分离的第一内部电压生成电路200_1及第二内部电压生成电路200_2,第一内部电压生成电路200_1经由电压供给节点intvdd_1来对第一内部电路180_1供给内部电压vdd1,第二内部电压生成电路200_2经由电压供给节点intvdd_2来对第二内部电路180_2供给内部电压vdd2。

[0090]

第一内部电压生成电路200_1及第二内部电压生成电路200_2具有与图4所示的内部电压生成电路200同样的构成,但第一内部电压生成电路200_1具备dpd判定功能,而第二内部电压生成电路200_2不具备dpd判定功能。第一内部电压生成电路200_1及第二内部电压生成电路200_2均在待机模式下运行,但第一内部电压生成电路200_1构成为,调整rc时间常数以使其适合于时钟信号dpdclk所要求的脉宽,且将以此种rc时间常数而生成的内部电压vdd1供给至第一内部电路180_1。另一方面,第二内部电压生成电路200_2不生成时钟信号dpdclk,因此规定电阻梯lad的电阻以使其适合于在待机模式下所要求的消耗电流,且对于电压供给节点intvdd_2的负载电容不产生限制。

[0091]

这样,根据本变形例,将在待机模式下运行的多个内部电压生成电路中的一个内部电压生成电路的rc时间常数设定为适合于时钟信号dpdclk所要求的脉宽,因此能够容易地设定用于向dpd模式转变的时间。另外,通过加大rc时间常数,能够延长脉宽,由此,能够延长计数器220的运行周期,实现用于dpd判定的运行所需的电力的降低。

[0092]

所述实施例中,表示了内部电压生成电路由外部电源电压vcc生成内部电压vdd的示例,但这只是一例,并不限定于此种形态。即,本实施例的内部电压生成电路也可由第一内部电压vdd1来生成第二内部电压vdd2。

[0093]

接下来,将搭载本实施例的自动dpd模式的nand型快闪存储器的一例示于图7。快闪存储器300是包含下述部分而构成,即:存储单元阵列310,由多个存储单元呈矩阵状地排列而成;输入/输出缓冲器320,连接于外部输入/输出端子i/o;地址寄存器330,从输入/输出缓冲器320接收地址数据;控制器340,从输入/输出缓冲器320接收命令数据等,对各部进行控制;字线选择电路350,从地址寄存器330接收行地址信息ax,对行地址信息ax进行解码,并基于解码结果来进行块的选择及字线的选择等;页面缓冲器/感测电路360,保持从由字线选择电路350所选择的页面读出的数据,或者保持应编程至所选择的页面的输入数据;列选择电路370,从地址寄存器330接收列地址信息ay,对列地址信息ay进行解码,并基于所述解码结果来选择页面缓冲器/感测电路360内的列地址的数据;以及内部电压产生电路380,生成数据的读出、编程及擦除等所需的各种电压(写入电压vpgm、通过电压vpass、读出通过电压vread、擦除电压vers等)。

[0094]

一实施方式中,快闪存储器300能够从外部端子输出用于告知内部的运行状态(编程、擦除、读出等)的忙碌信号/就绪信号。控制器340响应忙碌信号/就绪信号的输出而变为待机模式,如利用所述实施例所说明那样,对从进入待机模式的时间点开始的时间进行测量,当测量时间到达一定时间时,生成dpd使能信号dpden,并将其供给至内部的周边电路。收到dpd使能信号dpden的周边电路阻断电力供给。

[0095]

另外,另一实施方式中,内部电压产生电路380包含图4或图6所示的内部电压生成电路200,响应忙碌信号/就绪信号,对从进入待机模式的时间点开始的时间进行测量,当测

量时间到达一定时间时,生成dpd使能信号dpden,并将其供给至内部的周边电路。

[0096]

对本发明的优选实施方式进行了详述,但本发明并不限定于特定的实施方式,能够在权利要求所记载的发明主旨的范围内进行各种变形、变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。