1.本发明涉及集成电路技术领域,尤其涉及一种基于片上数字反馈自校准系统的真随机数发生器。

背景技术:

2.随着人工智能、5g、智能语音识别和自动驾驶等新兴领域的应用进一步拓展下,物联网产业将迎来更高速的发展,深入智能办公,智能医疗,可穿戴设备,移动支付等不同领域,为我们的生活提供便利和质量保障。然而,物联网在方便人们生活的同时,也存在着被黑客攻击的风险,导致一系列的隐私问题和安全隐患,比如物理跟踪、个人特征侧写和非授权访问。在医学上的部分应用,如血压监测仪、糖尿病监测器和心脏起搏器等,被远距离侵入和篡改的后果甚至会危害生命安全。

3.针对这一系列问题,传统的防侵入解决方案主要有两种:基于软件加密和基于硬件加密。软件加密常用的认证协议有aes、des和rsa,具有易维护、易实施的优点,但其安全性较低。如现有技术方法中可使用硬币大小的蓝牙设备对基于软件加密的物联网设备发送并嵌入唯一标识符,成功侵入设备,证明了攻击此类加密方式的简易性。此外,软件加密往往需要建立在操作系统上,这对物联网设备来说无疑增加了额外的成本。硬件加密通过在芯片内建立复杂的电路,将软件层的算法移植到硬件层来实现,从而减少了对操作系统的依赖。然而,基于硬件电路生成的密钥最终也要存储在非易失型存储器(non

‑

volatile memory, nvm)中使用,容易遭受破解泄露密钥。而且,算法本身的复杂性也导致了电路需要消耗大量的硬件资源,增加了制造成本。因此,为物联网设备提供安全可靠、低成本、低功耗的加密方案仍然是非常值得研究的技术。

4.物理不可克隆函数(physically unclonable function, puf)和真随机数发生器(true random number generator, trng)是近年来受到学术界广泛关注的基于硬件的物联网安全解决方案。puf是一项基于纳米尺寸器件工艺偏差的硬件安全原语技术,为物联网设备加密问题提供了良好的解决方案。在制造工艺中,由于局部的掺杂浓度、光刻尺寸、薄膜生长厚度等无法避免的纳米尺度工艺误差,相同版图制造的晶体管在阈值电压、宽长比、等效阻抗等物理参数上是有差异。在制造完成后,芯片内部的物理特性就已经确定,puf利用这种硬件上的物理特性生成了随机的密钥。与直接存储在nvm的密钥不同,puf的输出取决于随机的工艺偏差,这就使得puf的输出不会像nvm一样容易被擦除和篡改。puf如同芯片的dna,在芯片制造完成后输出就已经确定,并且将物理参数隐藏在芯片内部,防止泄露信息。trng是一项利用纳米尺寸电路中的随机物理过程来获取随机数的硬件安全原语技术,这些物理过程包括热噪声、时钟漂移、抖动、外部电磁、量子现象等。由于在纳米尺寸电路中,这种物理过程难以捕捉和预测,所以trng具有不可预测性。在密码学上,trng是对称加密、非对称加密等数据加密技术提升安全性的关键模块。数据在传输和存储过程中,用真随机数对原始数据进行处理,从而将数据承载的信息被隐藏起来,即使攻击者窃取了数据也获取不到有用的信息。此外,在puf实施阶段,trng也可被用于切断puf激励与响应的直接关

系,混淆强puf的激励与响应之间的关系,从而抵抗机器学习攻击。

5.然而现有的trng通常仅能在稳定电压及常温下生成稳定的真随机数,若输入电压出现波动或温度发生变化,现有的trng所输出的真随机数的随机性会出现偏差,基于trng输出的真随机数进行后续加密处理的可靠性受到影响。因此现有技术方法中的真随机数发生器存在使用可靠性不足的问题。

技术实现要素:

6.本发明实施例提供了一种基于片上数字反馈自校准系统的真随机数发生器,旨在解决现有技术方法中的真随机数发生器所存在的使用可靠性较差的问题。

7.本发明实施例提供了基于片上数字反馈自校准系统的真随机数发生器,其中,包括噪声数字化电路、偏置判断电路、自校准逻辑电路及后处理电路;所述噪声数字化电路包括第一反向单元、第二反向单元、仲裁器、第一电容阵列及第二电容阵列;所述第一反向单元的输入端与所述第二反向单元的输入端相连接并作为信号输入端接收时钟信号;所述第一反向单元的输出端与所述仲裁器的第一输入端及所述第一电容阵列的一端相连接,所述第一电容阵列的另一端接地,所述第二反向单元的输出端与所述仲裁器的第二输入端及所述第二电容阵列的一端相连接,所述第二电容阵列的另一端接地,所述仲裁器的输出端用于输出初始随机数;所述噪声数字化电路用于将两路反相器链在输入所述时钟信号作用下产生的抖动和噪声的延迟差异输出为初始随机数;所述后处理电路的第一输入端连接所述仲裁器的输出端、其第二输入端连接所述信号输入端、其输出端用于输出增强随机数信号;所述后处理电路用于对所述初始随机数进行算法处理得到增强随机数信号并输出;所述偏置判断电路的第一输入端连接所述仲裁器的输出端、其第二输入端连接初始化信号输入端、其第一偏置输出端用于输出第一偏置信号、其第二偏置输出端用于输出第二偏置信号,所述偏置判断电路的第二输入端用于输入初始化信号;所述偏置判断电路用于对原始随机数进行检测判断偏置方向从而输出第一偏置信号及第二偏置信号;所述自校准逻辑电路的第一输入端及第二输入端均连接所述仲裁器的输出端、其第三输入端连接所述信号输入端、其第四信号输入端连接所述第二偏置输出端、其第五信号输入端连接所述第一偏置信号输出端;其第一控制输出端连接所述第一电容阵列的控制开关,通过输出第一控制信号控制接入所述第一反相单元的电容以补偿所述第一反相单元的额外延迟时间,其第二控制输出端连接所述第二电容阵列的控制开关,通过输出第二控制信号控制接入所述第二反相单元的电容以补偿所述第二反相单元的额外延迟时间,从而将所述第一反向单元及所述第二反向单元因工艺误差造成的延迟时间补偿至相等;所述自校准逻辑电路用于根据时钟信号及初始随机数对所述第一偏置信号及所述第二偏置信号进行校准得到第一控制信号及第二控制信号。

8.所述的基于片上数字反馈自校准系统的真随机数发生器,其中,所述第一反向单元及所述第二反向单元均由多个反相器进行串联组成。

9.所述的基于片上数字反馈自校准系统的真随机数发生器,其中,所述第一电容阵列及所述第二电容阵列均由数量相等的多个电容对组成,且所述第一电容阵列或所述第二电容阵列包含的电容对所对应的延迟时间依次成倍数增长。

10.所述的基于片上数字反馈自校准系统的真随机数发生器,其中,所述电容对均包含一个一端通过第一控制开关与所述第一反向单元的输出端相连接、另一端接地的第一电容,以及一个一端通过第二控制开关与所述第二反向单元的输出端相连接、另一端接地的第二电容;所述第一电容阵列的每一电容对中的第一电容尺寸依次增加,每一电容对中第二电容的尺寸均相等;所述第二电容阵列的每一电容对中第一电容的尺寸均相等,每一电容对中第二电容的尺寸依次增加。

11.所述的基于片上数字反馈自校准系统的真随机数发生器,其中,所述第一电容阵列的每一电容对中的第一控制开关及第二控制开关均与所述第一控制输出端相连接,以接收所述第一控制输出端输入的第一控制信号并对所述第一电容阵列中每一电容对分别进行通断控制,从而控制所述第一电容阵列对所述第一反向单元及所述第二反向单元的额外延迟时间的补偿时长;所述第二电容阵列的每一电容对中的第一控制开关及第二控制开关均与所述第二控制输出端相连接,以接收所述第二控制输出端输入的第二控制信号并对所述第二电容阵列中每一电容对分别进行通断控制,从而控制所述第二电容阵列对所述第一反向单元及所述第二反向单元的额外延迟时间的补偿时长。

12.所述的基于片上数字反馈自校准系统的真随机数发生器,其中,所述电容对中的电容均为nmos晶体管的栅极电容。

13.所述的基于片上数字反馈自校准系统的真随机数发生器,其中,所述噪声数字化电路、所述偏置判断电路、所述自校准逻辑电路及所述后处理电路均采用互补型金属氧化物半导体工艺制作得到。

14.所述的基于片上数字反馈自校准系统的真随机数发生器,其中,所述偏置判断电路包括触发器、第一或非门及第二或非门;所述触发器的第一输入端连接所述仲裁器的输出端、其第二输入端连接所述初始化信号输入端、其第一输出端连接所述第一或非门的第一输入端、其第二输出端连接所述第二或非门的第二输入端;所述第一或非门的第二输入端与所述第二或非门的第一输入端相连接用于输入重置信号;所述第一或非门的输出端作为所述偏置判断电路的第一偏置输出端输出第一偏置信号,所述第二或非门的输出端作为所述偏置判断电路的第二偏置输出端输出第二偏置信号。

15.所述的基于片上数字反馈自校准系统的真随机数发生器,其中,所述自校准逻辑电路包括第一加减计数器、第二加减计数器、复位逻辑器、第三或非门及第四或非门;所述第一加减计数器的第一输入端连接所述仲裁器的输出端、其第二输入端连接所述信号输入端、其第三输入端与第一输出端之间串联设置所述复位逻辑器、其第四输出端连接所述第二加减计数器的第二输入端;所述第二加减计数器的第一输入端连接所述仲裁器的输出端、其第一输出端连接所述第三或非门的第二输入端、其第二输出端连接所述第四或非门的第一输入端;所述第三或非门的第一输入端连接所述第二偏置输出端、输出端连接所述第一电

容阵列;所述第四或非门的第二输入端连接所述第一偏置输出端、输出端连接所述第二电容阵列。

16.所述的基于片上数字反馈自校准系统的真随机数发生器,其中,所述第一加减计数器为四位加减计数器,所述第二加减计数器为十位加减计数器。

17.本发明实施例提供了一种基于片上数字反馈自校准系统的真随机数发生器,包括噪声数字化电路、偏置判断电路、自校准逻辑电路及后处理电路,噪声数字化电路包括第一反向单元、第二反向单元、仲裁器、第一电容阵列及第二电容阵列,噪声数字化电路用于将两路反相器链在输入时钟信号作用下产生的抖动和噪声的差异输出为初始随机数,后处理电路用于对初始随机数进行算法处理得到增强随机数信号并输出,偏置判断电路用于对原始随机数进行检测判断偏置方向从而输出第一偏置信号及第二偏置信号,自校准逻辑电路用于根据产生的第一偏置信号及第二偏置信号对两条反相器链因工艺误差而产生的信号延迟进行校准得到第一控制信号及第二控制信号。上述的真随机数发生器,可在输入电压大范围波动及温度大范围变化的情况下依然确保高随机性,大幅提高了使用可靠性。

附图说明

18.为了更清楚地说明本发明实施例技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

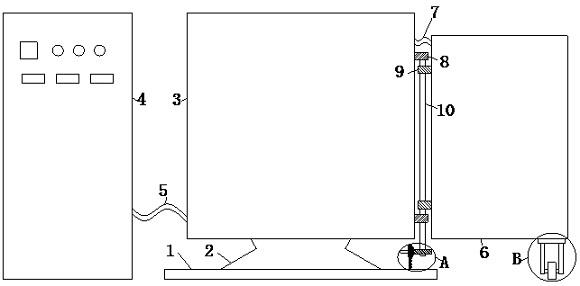

19.图1为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的整体电路结构图;图2为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的局部电路结构图;图3为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的局部电路结构图;图4为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的效果示意图;图5为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的效果示意图;图6为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的效果示意图;图7为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的结构版图;图8为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的自校准逻辑流程图;图9为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的效果示意图;图10为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的效果示意图;

图11为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的效果示意图。

具体实施方式

20.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

21.应当理解,当在本说明书和所附权利要求书中使用时,术语“包括”和“包含”指示所描述特征、整体、步骤、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整体、步骤、操作、元素、组件和/或其集合的存在或添加。

22.还应当理解,在本发明说明书中所使用的术语仅仅是出于描述特定实施例的目的而并不意在限制本发明。如在本发明说明书和所附权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一”、“一个”及“该”意在包括复数形式。

23.还应当进一步理解,在本发明说明书和所附权利要求书中使用的术语“和/ 或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

24.请参阅图1及图3,图1为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的整体电路结构图;图2为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的局部电路结构图;图3为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的局部电路结构图。如图所示,一种基于片上数字反馈自校准系统的真随机数发生器,包括噪声数字化电路11、偏置判断电路12、自校准逻辑电路13及后处理电路h0。

25.所述噪声数字化电路11包括第一反向单元i、第二反向单元i’、仲裁器z0、第一电容阵列cm1及第二电容阵列cm2;所述第一反向单元i的输入端与所述第二反向单元i’的输入端相连接并作为信号输入端接收时钟信号clk,时钟信号即为一定频率的方形波信号,其波形如图2左侧所示波信号,所述第一反向单元i的输出端与所述仲裁器z0的第一输入端及所述第一电容阵列cm1的一端相连接,所述第一电容阵列cm1的另一端接地,所述第二反向单元i’的输出端与所述仲裁器z0的第二输入端及所述第二电容阵列cm2的一端相连接,所述第二电容阵列cm2的另一端接地,所述仲裁器z0的输出端用于输出初始随机数out’;所述噪声数字化电路用于将两路反相器链在输入所述时钟信号clk作用下产生的抖动和噪声的延迟差异输出为初始随机数out’,第一反向单元i及第二反向单元i’即分别对应上述的两条反相器链。

26.具体的,噪声数字化电路11的基础结构如图2所示,第一反向单元i即可接收一路震荡噪声,第二反向单元i

’ꢀ

可接收另一路震荡噪声,经过若干级反相器振荡后,第一反向单元i及第二反向单元i’的末端将会得到积累了反相器振荡噪声的两个时钟信号clka和clkb,并且将所得到的两个时钟信号clka和clkb分别输入至仲裁器z0的两个输入端,仲裁器z0的作用是根据clka和clkb每一次上升沿来的先后顺序来输出高电平或低电平。

27.图4为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的效果示意图,图4是基于图2的噪声数字化电路11中clka和clkb在噪声影响下仿真的1000组延

迟差异统计分布图,其中延迟时间单位为皮秒(ps),拟合的曲线符合高斯分布,此高斯分布可采用公式(1)进行表示;

ꢀꢀ

(1);其中,μ为0.01ps(理想情况下应为0 ps),σ为7.74ps。在不考虑工艺误差的理想情况下,某个clk周期下当小于0时,意味着在噪声作用下,clka的上升沿比clkb先到达仲裁器z0,仲裁器z0输出的初始随机数out’为低电平信号,反之为初始随机数out’为高电平信号。此时,out’输出为0的概率p(0)将接近50%,并且在nist区域内(图4中虚线框内)符合随机数的要求(

±

0.24σ)。

28.在更具体的实施例中,所述第一反向单元i及所述第二反向单元i’均由多个反相器进行串联组成,如图2所示,第一反向单元i由反相器i1、反相器i2、

…

及反相器i

n

串联组成,反相器i1的输入端即作为第一反向单元i的输入端,反相器i

n

的输出端即作为第一反向单元i的输出端,同样地,第二反相单元i’由反相器i

’1、反相器i

’2、

…

及反相器i’n

串联组成,第一反相单元i及第二反向单元i’的所包含反相器的数量相等,如本案具体实施例中第一反相单元i及第二反向单元i’所包含的反相器的数量均为n。

29.具体的,所述第一电容阵列cm1及所述第二电容阵列cm2均由数量相等的多个电容对组成,且所述第一电容阵列cm1或所述第二电容阵列cm2包含的电容对所对应的延迟时间依次成倍数增长。其中,所述电容对均包含一个一端通过第一控制开关与所述第一反向单元i的输出端相连接、另一端接地的第一电容,以及一个一端通过第二控制开关与所述第二反向单元i’的输出端相连接、另一端接地的第二电容,如图3所示,第一电容阵列cm1包含十个电容对,每一电容对均包含两个电容,如第一电容对由第一电容ca0和第二电容ca

’0组成,第一电容ca0的一端通过第一控制开关k与所述第一反向单元i的输出端(a端)相连接、另一端接地,第二电容ca

’0的一端通过第一控制开关k’与所述第二反向单元i’的输出端(b端)相连接、另一端接地。所述第一电容阵列cm1的每一电容对中的第一电容ca0尺寸依次增加,每一电容对中第二电容ca

’0的尺寸均相等;所述第二电容阵列cm2的每一电容对中第一电容ca0的尺寸均相等,每一电容对中第二电容ca

’0的尺寸依次增加。

30.在更具体的实施例中,所述第一电容阵列cm1的每一电容对中的第一控制开关k及第二控制开关k’均与所述第一控制输出端相连接,以接收所述第一控制输出端输入的第一控制信号s_a[9:0](其中包含十个子信号)并对所述第一电容阵列cm1中每一电容对分别进行通断控制,从而控制所述第一电容阵列cm1对所述第一反向单元i及所述第二反向单元i’的额外延迟时间的补偿时长,第一电容阵列cm1中每一电容对的第一控制开关及第二控制开关即组成为第一电容阵列的控制开关;所述第二电容阵列cm2的每一电容对中的第一控制开关k及第二控制开关k’均与所述第二控制输出端相连接,以接收所述第二控制输出端输入的第二控制信号s_b[9:0] (其中包含十个子信号)并对所述第二电容阵列cm2中每一电容对分别进行通断控制,从而控制所述第二电容阵列cm2对所述第一反向单元i及所述第二反向单元i’的额外延迟时间的补偿时长,第二电容阵列cm2中每一电容对的第一控制开关及第二控制开关即组成为第一电容阵列的控制开关。具体的,所述电容对中的电容均为nmos晶体管的栅极电容。其中,所述噪声数字化电路11、所述偏置判断电路12、所述自校准

逻辑电路13及所述后处理电路h0均采用互补型金属氧化物半导体工艺制作得到,从而实现与其他采用互补型金属氧化物半导体工艺制作的电路元器件进行兼容,在更具体的实施例中,可采用65nm 、1.2v低漏电工艺(low leakage)互补型金属氧化物半导体工艺(cmos工艺)制作得到本方案中涉及的各电路单元。

[0031]

对于65nm的互补型金属氧化物半导体工艺(umc65工艺),制作得到最小的栅极电容(晶体管)尺寸为w/l=80nm/60nm(宽度为80nm,长度为60nm),电容的尺寸即决定了延迟时间,电容尺寸越大则延迟时间越长。若使用电容直接作为最小的延迟单元,通过二进制数控制电容阵列的精度约为82ps/bit,这一精度较低,难以实现精确地将输出的电平信号控制在nist区域内的目的。本方案中采用了一种补偿式的电容阵列设计,图4所示即为第一电容阵列cm1(第二电容阵列cm2与第一电容阵列cm1对称设计),在给第一反向单元i的输出端增加电容时,同时在第二反相单元i’的输出端补偿一个更小的电容,则第一控制信号s_a[9:0]中的每一个子信号可同时控制一个电容对的通断,也即是一个电容对中包含的两个电容同时接入电路或同时断开,则最终每一电容对所增加的电容精度为该电容对中所包含的两个电容的差值,电容值越大则所补偿的额外延迟时间也越长,则第一电容阵列cm1中的每一电容对在第一反向单元i的输出端所补偿的额外延迟时间,即为电容对对第一反向单元及第二反向单元的额外延迟时间的补偿时长的差值,则第二电容阵列cm2中的每一电容对在第二反向单元i的输出端所补偿的额外延迟时间,即为电容对对第一反向单元及第二反向单元的额外延迟时间的补偿时长的差值。

[0032]

本设计为满足反相器延迟链的误差需求,设计了十位二进制电容阵列,也即是第一电容阵列cm1及第二电容阵列cm2均包含十个电容对,以为第一电容阵列cm1例,其所包含的十个主延迟晶体管(图4中第一排电容)的栅极宽(w值)依次为90 nm、100 nm、120 nm、160 nm、240 nm、400 nm、720 nm、1360 nm、2640和5200nm,长度均为60nm,其所包含的十个延迟补偿晶体管(图4中第二排电容)的栅极宽均为80(单位均为nm),长度均为60nm,则图4中第一个电容对可补偿至第一反向单元i的输出端的额外延迟时间即与两个电容的栅极宽差90

‑

80=10nm相对应,第二电容对可补偿至第一反向单元i的输出端的额外延迟时间即与两个电容的栅极宽差100

‑

80=20nm相对应,第三电容对可补偿至第一反向单元i的输出端的额外延迟时间即与两个电容的栅极宽差120

‑

80=40nm相对应,以此类推。第二电容阵列cm2中电容的设计尺寸与第一电容阵列cm1相对称,也即是第二电容阵列cm2中第一排电容为十个延迟补偿晶体管(尺寸均相同),第二排电容为十个主延迟晶体管(尺寸依次增加)。

[0033]

图5为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的效果示意图,在s_a[9:0](其中10个子信号按顺序组合即可表示成10位二进制数)从0计数到1023的过程中,其作用下的clka和clkb延迟变化如图5所示,由图中可知第一电容阵列cm1的晶体管电容带来延迟时间的增长基本随s_a[9:0]数值的增长线性增加,且斜率约为0.9ps/bit,这一精度大大优于传统技术方法中的82ps/bit。

[0034]

所述后处理电路h0的第一输入端连接所述仲裁器z0的输出端、其第二输入端连接所述信号输入端、其输出端用于输出增强随机数信号out;则初始随机数out’由第一输入端输入至后处理电路h0,时钟信号clk由第二输入端输入至后处理电路h0,所述后处理电路h0用于对所述初始随机数out’进行算法处理得到增强随机数信号out并输出。其中,后处理电路h0可以是由八个异或门进行串联连接所组成的八级异或链。

[0035]

所述偏置判断电路12的第一输入端连接所述仲裁器z0的输出端、其第二输入端连接初始化信号输入端、其第一偏置输出端用于输出第一偏置信号reset_s_a、其第二偏置输出端用于输出第二偏置信号reset_s_b,所述偏置判断电路12的第二输入端用于输入初始化信号clk_i;所述偏置判断电路用于对原始随机数out’进行检测判断偏置方向从而输出第一偏置信号reset_s_a及第二偏置信号reset_s_b。

[0036]

在更具体的实施例中,所述偏置判断电路12包括触发器cf、第一或非门nor1及第二或非门nor2;所述触发器cf的第一输入端cf_d连接所述仲裁器z0的输出端、其第二输入端cf_e连接所述初始化信号输入端、其第一输出端cf_q连接所述第一或非门nor1的第一输入端、其第二输出端cf_q_n连接所述第二或非门nor2的第二输入端;所述第一或非门的第二输入端与所述第二或非门的第一输入端相连接用于输入重置信号r;所述第一或非门nor1的输出端作为所述偏置判断电路12的第一偏置输出端输出第一偏置信号reset_s_a,所述第二或非门nor2的输出端作为所述偏置判断电路12的第二偏置输出端输出第二偏置信号reset_s_b。其中,触发器cf的第二输入端cf_e用于输入初始化信号clk_i,初始化信号clk_i可作为触发器cf的开关信号,初始化信号clk_i在触发器cf开始工作时置于高电平并一直保持。

[0037]

偏置判断电路12的作用是判断在第一反向单元i及第二反向单元i’末端未加电容情况下clka和clkb上升沿先后顺序,以此来决定通过第一电容阵列cm1及第二电容阵列cm2中电容接通的具体位置(在上升沿来得更快的反向单元的一端增加电容,从而增加延迟时间),从而让clka和clkb上升沿到来的时间更接近。

[0038]

所述自校准逻辑电路13的第一输入端及第二输入端均连接所述仲裁器z0的输出端、其第三输入端连接所述信号输入端、其第四信号输入端连接所述第二偏置输出端、其第五信号输入端连接所述第一偏置信号输出端;其第一控制输出端连接所述第一电容阵列cm1以输出第一控制信号s_a[9:0]控制第一电容阵列cm1的延迟时间,其第二控制输出端连接所述第二电容阵列cm2以输出第二控制信号s_b[9:0]控制第二电容阵列cm2的延迟时间;所述自校准逻辑电路13用于根据时钟信号clk及初始随机数out’对所述第一偏置信号reset_s_a及所述第二偏置信号reset_s_b进行校准得到第一控制信号s_a[9:0]及第二控制信号s_b[9:0]。其中,第一控制信号s_a[9:0]及第二控制信号s_b[9:0]均由十个子信号组成,每一子信号可采用“0”或“1”进行表示,则10个子信号按顺序组合即可表示成10位二进制数,10位二进制数的数值范围为[0,1023]。

[0039]

在更具体的实施例中,所述自校准逻辑电路13包括第一加减计数器j1、第二加减计数器j2、复位逻辑器f、第三或非门nor3及第四或非门nor4;所述第一加减计数器j1的第一输入端j

1_

a/s连接所述仲裁器z0的输出端、其第二输入端j

1_

e连接所述信号输入端、其第三输入端j

1_

reset与第一输出端j

1_

t之间串联设置所述复位逻辑器f、其第四输出端j

1_

co连接所述第二加减计数器j2的第二输入端j

2_

e;所述第二加减计数器j2的第一输入端j

2_

a/s连接所述仲裁器z0的输出端、其第一输出端j

2_

q连接所述第三或非门nor3的第二输入端、其第二输出端j

2_

q_n连接所述第四或非门nor4的第一输入端;所述第三或非门nor3的第一输入端连接所述第二偏置输出端、输出端连接所述第一电容阵列cm1;所述第四或非门nor4的第二输入端连接所述第一偏置输出端、输出端连接所述第二电容阵列cm2。其中,所述第一加减计数器j1为四位加减计数器,所述第二加减计数器j2为十位加减计数器。

[0040]

具体的,将图1中的r信号置1,此时第一偏置信号reset_s_a和第二偏置信号reset_s_b均为1,再经过第一或非门nor1及第二或非门nor2后,第一控制信号s_a[9:0]及第二控制信号s_b[9:0]均被置为低电平(数值均为0),进而断开了第一电容阵列cm1及第二电容阵列cm2中所包含的所有电容。然后,输入方波clk,若初始随机数out’为低电平,则表明clka快于clkb,应当在第一反向单元i的输出端增加电容,反之则在第二反向单元i

’ꢀ

的输出端增加电容。通过触发器cf的一个上升沿,初始随机数 out’将会被保存在触发器cf内。最后,使r信号置0,就能通过第一偏置信号reset_s_a和第二偏置信号reset_s_b选择关闭第一电容阵列cm1的输出端或第二电容阵列cm2的输出端中某一端的全部电容。

[0041]

自校准逻辑电路13包含两个加减计数器组成,第一加减计数器的位数为四位,第二加减计数器的位数为十位。四位加减计数器输出cnt4[3:0]的作用是统计初始随机数out’输出0和1的偏置情况,而十位加减计数器输出的cnt10[9:0]及cnt10_n[9:0],在分别与reset_s_a及reset_s_b进行或非逻辑运算后,可以得到控制电容阵列的第一控制信号s_a[9:0]和第二控制信号s_b[9:0]。图8为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的自校准逻辑流程图,如图8所示,在偏置判断电路12完成判断后,假设clka快于clkb,则初始随机数out’为0,reset_s_a和reset_s_b分别为0、1,使s_b[9:0] (b端电容开关)恒等于10’b0(10位二进制数表示的0),关闭了b端所有的电容,而s_a[9:0](a端电容开关)从10’b0(10位二进制数表示的0)开始计数。四位计数器起始值为4’b0(4位二进制数表示的0),由于开始时判断了初始随机数out’是偏向输出0,计数器做加法。当四位计数器的值为4’b1000(4位二进制数表示的1000)时,通过复位逻辑将四位计数器复位为4’b0,同时其通过第四输出端j

1_

co输出一个进位脉冲给十位计数器的第二输入端j

2_

e,十位计数器的第一输出端j

2_

q将根据此时的初始随机数out’(为0)对cnt10[9:0]做加法,而其第二输出端j

2_

q_n将对cnt10_n[9:0]做减法,经过第三或非门nor3及第四或非门nor4后,将对s_a[9:0] 做加法,从而使第一反向单元i的输出端电容值增加。只要初始随机数out’的输出偏向于0,这个过程将一直持续,电容值将一直增加,延迟时间也将一直增加,直到clka和clkb两者的相位相差接近,p(0)很接近50%,进入nist区域。此时初始随机数out’输出0、1将在四位计数器里进行博弈,而十位计数器的输出值cnt10[9:0]及cnt10_n[9:0]也只在一两位之间进行变化,达到相对稳定状态。另外,若clkb快于clka,则初始随机数out’为1,偏置判断阶段将使reset_s_a和reset_s_b分别为1、0,关闭第一反向单元i的输出端的所有电容,此时,由于cnt10[9:0]初始化为10’b0,与reset_s_b或非后将得到s_b[9:0]为10’d1023,即第二反向单元i’的输出端的电容全部打开。原本clkb快于clka的状态将在这些电容的作用下使得clka快于clkb,初始随机数out’还是输出0,十位计数器的第一输出端j

2_

q对cnt10[9:0]做加法,经过或非门后得到的s_b[9:0]将做减法,使b端电容减小,直到p(0)趋近于50%。

[0042]

图6为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的效果示意图,如图6所示,其中展示了偏置判断初始随机数out’为0时,cnt10[9:0]和p(1)在校准过程中随时间变化情况,其中深色线为cnt10[9:0]的十进制值,浅色线为p(1),p(1)的值是对每两百个初始随机数out’输出比特进行统计的概率结果。从图中可以观察到,cnt10[9:0]在电路校准开始后增加,经过一段时间后能保持稳定,此时clka和clkb之间的固有延迟基本已经被校正。从图中可以看到,p(1)偶尔会偏移nist区域(两条横向虚线的中间区

域),主要原因有两个:第一、每次统计的数据总量较少,仅200bits;第二、电路中一些非随机因素影响了初始随机数out’输出。因此,在初始随机数out’的基础上,使用后处理电路h0(八级异或链)对其进行后处理,使输出的0、1值更加均匀,并减少非随机因素的影响,得到最终输出增强随机数信号out。

[0043]

图7为本发明实施例提供的基于片上数字反馈自校准系统的真随机数发生器的结构版图,如图7所示,本方案中的trng(真随机数发生器)使用65nm 1.2v标准的cmos工艺进行制作得到,长和宽分别为112um、23um,整体面积约为2576um2。通过模拟瞬态噪声,并且使用蒙特卡洛仿真模拟工艺误差,可进一步获取基于上述工艺制作得到的trng的性能。

[0044]

真随机数发生器(trng)的随机性是其在安全加密应用中的基本要求,是衡量其他性能的前提。评估trng输出序列与评估puf响应位随机性的方法类似,主要包括前面提到的nist测试、自相关检测和最小熵值h(x)。在vdd=1.2v&t=27℃下,通过蒙特卡洛仿真得到了500kbits的连续序列,并使用nist pub 800套件来评估其随机性,结果如表1所示。从表中可以看出,所有项目的p值均大于0.01,并且全部项目通过了nist测试,证明了该trng在常温常压下输出序列的随机性是符合要求的。

[0045]

表1此外,将该增强随机数信号out作为输出序列输入用于自相关检测中得到图9的结果,在95%的置信区间(图9中两条横向直线之间的区域),σ的值为0.0016,证明trng输出序列并无明显相关性。具体的,输出序列中共包含n个数值,取输出序列作为样本x

t

,该样本包含{ x1, x2, x3, ..., x

n },从该输出序列中取另一样本x

t 1

,该样本包含{ x2, x3, x4..., x

n

}。在平稳性条件下,这两组样本的均值均可采用公式(2)计算得到:

ꢀꢀꢀꢀꢀꢀꢀ

(2);则x

t

与 x

t k

的自相关系数即为=自协方差/ k=0时的自协方差,分母也等于 x

t

的方差。自相关系数的估计值为r

k

,r

k

可采用公式(3)计算得到:

ꢀꢀꢀꢀꢀꢀꢀ

(3);其中,r

0 永远等于“1”,r

k

称为样本自相关函数(acf)。对于样本x

t

与x

t k

之间的自相关系数,可将k从0到n的自相关系数r

k

求出,所得到的计算值即为图9中的纵坐标值,k值两组样本之间的间隔值,也即是图9中横坐标值lag。

[0046]

同时,通过测试证明,上述技术方案中的trng能够在电源电压0.8至1.4v&温度范围

‑

40至120℃的工作条件下正常工作。我们通过每0.2v取一个电源电压(即vdd=0.8v、vdd=1.0v、vdd=1.2v和vdd=1.4v)、每40℃取一个温度点(即t=

‑

40℃、t=0℃、t=40℃、t=80℃和t=120℃)组合成20种工作条件进行仿真,每个条件下获得10kbits的01序列,分别用于nist pub 800套件进行随机性检测,最终均通过检测。图10展示了trng在各个电压和温度条件下生成随机数散斑图,其中黑色斑点为高电平,白色斑点为低电平。从图10中可以看到,在电源电压范围vdd为0.8

‑

1.4v&温度范围为

‑

40

‑

120℃的条件下,trng能通过校准逻辑来补偿两个反相单元的工艺偏差,从而将两个反相单元运行过程中的噪声和抖动数字化,最终输出无规律的01序列(增强随机数信号out),这说明了本文设计的trng能够抵抗一定范围的电源电压和温度变化,并且输出的01序列(增强随机数信号out)仍能保证较好的随机性。

[0047]

吞吐率衡量了单位时间内trng输出随机序列的速度,而能效则是trng每输出单位bit消耗的能量,它的大小为trng的整体功率与吞吐率的比值。在随机性达到要求的情况下,trng还应尽可能地有更高的吞吐率和更低的能效,从而满足低功耗物联网设备中高速的数据传输要求。图11中给出了在常温常压下(1.2v&27℃)下,trng的功率、能效与吞吐率之间的变化关系。其中,在吞吐率为488kbps时,trng的能效为1.23pj/bit。随着吞吐率的升高,能效逐渐降低。值得一提的是, trng的最高吞吐率达到250mbps,此时电路的功率为60.5uw,能效为0.24pj/bit。

[0048]

表2为本方案设计的trng与现有技术中的trng设计的性能对比。

[0049]

表2从表2数据的中可以看到,本方案设计的trng可以在电源电压和温度分别为0.8至1.4v、

‑

40至120℃的范围内正常工作,具有良好的速度和能效表现,且可靠性更佳。且本方案trng的最高吞吐率大小为250mbps,总体能效为0.24pj/bit,能效在表中列出的各个设计中表现最好。

[0050]

在本发明实施例所提供的基于片上数字反馈自校准系统的真随机数发生器,包括噪声数字化电路、偏置判断电路、自校准逻辑电路及后处理电路,噪声数字化电路包括第一反向单元、第二反向单元、仲裁器、第一电容阵列及第二电容阵列,噪声数字化电路用于将两路反相器链在输入时钟信号作用下产生的抖动和噪声的差异输出为初始随机数,后处理电路用于对初始随机数进行算法处理得到增强随机数信号并输出,偏置判断电路用于对原始随机数进行检测判断偏置方向从而输出第一偏置信号及第二偏置信号,自校准逻辑电路用于根据产生的第一偏置信号及第二偏置信号对两条反相器链因工艺误差而产生的信号延迟进行校准得到第一控制信号及第二控制信号。上述的真随机数发生器,可在输入电压大范围波动及温度大范围变化的情况下依然确保高随机性,大幅提高了使用可靠性。

[0051]

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。