中断控制器和管理中断控制器的方法

1.相关申请的交叉引用

2.本技术要求于2020年04月14日提交的法国专利申请号2003733的权益,该申请通过引用以其整体并入本文。

技术领域

3.本发明的实施例和实施方式涉及一种中断控制器和管理中断控制器的方法。

背景技术:

4.传统上,中断控制器被配置成接收从一项或多项外部装备发出的中断信号。当一项外部装备想要向处理核(例如微处理器)发信号通知特定事件需要要求在处理核的一部分上进行特定行动时,中断信号由(多项)外部装备发射。然后,中断控制器管理对拦截信号的接收,以便例如对其进行序列化并且将其顺序传送给处理核。

5.一些微控制器可以是安全的,也就是说,包括安全域。安全域可以包括:包括有安全处理核的处理核,其安全程序代码;以及安全装备,该安全设备必须例如仅由安全处理核访问。但是,这种微控制器也可以包括不安全域。不安全域可以包括不安全处理核和不安全装备,不安全处理核包括不安全程序代码。

6.在微控制器的操作期间,不安全处理核可能会在执行其不安全程序代码期间尝试访问一项安全装备。这导致安全故障,考虑到向安全处理核的传送,通过从外部装备朝向中断控制器发出中断信号,该安全故障将被转换。并且在这种安全应用中,重要的是中断控制器不错过任何安全故障。

7.在这方面,当前提供了连续地操作中断控制器,也就是说连续地向中断控制器递送时钟信号。然而,当微控制器改变为低消耗模式时,这是有问题的。

8.因此,需要在低消耗模式下不对微控制器的消耗不利,同时确保中断控制器有效地处理所接收的所有中断信号(例如安全故障信号),而不遗漏任何中断信号。

技术实现要素:

9.根据一个实施例,一种电子设备包括:中断控制器,具有输出以及用于接收控制器时钟信号的输入,中断控制器被配置成:当控制器时钟信号有效时,在输出上递送输出中断信号;以及控制电路,包括:输入接口,用于接收有可能从设备外部的至少一项装备发出的至少一个中断信号;时钟输入,用于接收外部时钟信号,以及第一控制器,被连接到输入接口和时钟输入,第一控制器被配置成从至少一个中断信号被断言时直到递送对应的输出中断信号为止,根据外部时钟信号自动生成控制器时钟信号。

10.根据另一个实施例,一种用于管理中断控制器的方法,包括:接收至少一个中断信号;接收外部时钟信号;从至少一个中断信号被断言时直到递送对应的输出中断信号为止,根据外部时钟信号生成控制器时钟信号;以及将控制器时钟信号提供给中断控制器的输入,其中中断控制器被配置成在接收到控制器时钟信号时,递送对应的输出中断信号。

11.根据另外的实施例,一种电路,包括:门控控制电路,具有:第一输入;第二输入,被配置成与中断控制器的输出耦合;以及被配置成与中断控制器的输入耦合的输出,门控控制电路被配置成在第一输入处接收到断言的输入中断信号时断言门控控制信号,并且在第二输入处接收到断言的输出中断信号时解除断言门控控制信号;以及时钟门控电路,具有:控制输入,被耦合到门控控制电路的输出;时钟输入,被配置成接收输入时钟信号;以及被配置成向中断控制器的输入提供门控的时钟信号的输出。

附图说明

12.通过检查以下对非限制性实施例和实施方式的详细描述以及附图,本发明的其他优点和特征将变得明显,其中:

13.图1图示了示出电子设备的一个实施例的框图;

14.图2图示了根据图1的实施例的定时图;

15.图3图示了示出电子设备的一个实施例的框图;

16.图4图示了根据图3的实施例的定时图;以及

17.图5图示了实施例微控制器的框图。

具体实施方式

18.本发明的一些实施例和实施方式涉及中断控制器,特别涉及中断控制器操作的管理,并且特别涉及被包含在安全微控制器内的中断控制器,安全微控制器被配置成处理安全故障信号。

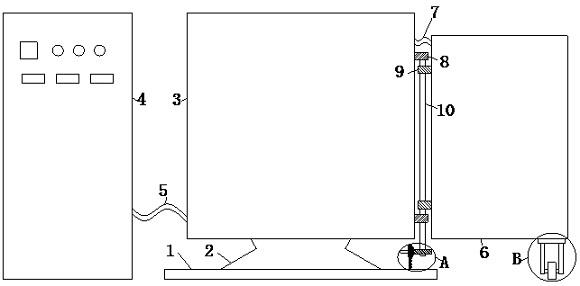

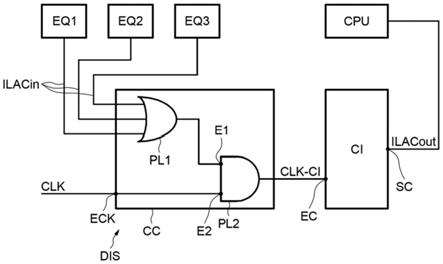

19.图1图示了示出电子设备dis的一个实施例的框图,电子设备dis包括链接到控制电路cc的中断控制器ci。

20.根据一个方面,电子设备包括:中断控制器,拥有输出以及用于接收控制器时钟信号的输入,并且被配置成在控制器时钟信号存在的情况下,在输出上递送输出中断信号;以及控制电路,具有输入接口,用于接收有可能从设备外部的至少一项装备发出的至少一个中断信号,并且具有时钟输入,用于接收外部时钟信号,以及控制器,连接到输入接口和时钟输入,并且被配置成在至少一个中断信号存在的情况下直到递送对应的输出中断信号为止,根据外部时钟信号自动生成控制器时钟信号。

21.换句话说,根据这个方面,外部时钟信号(并且因此,控制器时钟信号)自动地(也就是说,用户无需编程任何东西)递送给中断控制器,其将使得中断控制器能够递送输出中断信号,输出中断信号例如旨在用于处理器,并且一旦输出中断信号已被递送,对控制器时钟信号的递送就会停止。

22.因此,借助于控制电路,中断控制器在以下时段之间接收形成控制器时钟的时钟信号:由控制电路对中断信号的接收、与由中断控制器对对应的输出中断信号的递送。因此,在限制中断控制器的消耗的同时,没有中断信号被遗漏。

23.根据一个实施例,输入接口被配置成接收分别有可能从多项不同的外部装备发出的多个中断信号,并且控制器被配置成在中断信号中的至少一个中断信号存在的情况下,根据外部时钟信号自动生成控制器时钟信号。

24.因此,输入接口可以接收多个中断信号,多个中断信号使得控制器能够生成控制

器时钟信号以用于由输入接口接收的每个中断信号。

25.例如,输入接口包括或门,或门的输入被配置成接收不同的中断信号,并且或门的输出连接到控制器。实际上,或门的每个输入可以连接到不同的多项外部装备。因此,如果仅一个中断信号由输入接口的或门的输入中的仅一个输入接收,则或门的输出将发出一信号,该信号使得控制器能够生成控制器时钟信号。

26.根据一个实施例,控制器包括逻辑,该逻辑拥有被连接到输入接口的第一输入,并且具有被连接到时钟输入的第二输入,并且该逻辑被配置成通过门控外部时钟信号来进行控制,以通过使外部时钟信号的不中断或中断,来自动生成或不生成控制器时钟信号。

27.因此,控制器时钟信号是根据外部时钟信号生成的,并且因此逻辑使得可以通过外部时钟信号门进行控制(该技术通常被称为“时钟门控”)而不中断或中断控制器时钟信号。例如,逻辑包括与门,该与门耦合到第一输入和第二输入。

28.一些中断控制器可以在控制器时钟信号的一个周期中生成输出中断信号。其他中断控制器要求控制器时钟信号的多个周期来生成输出中断信号。

29.根据一个实施例,其中中断控制器被配置成在控制器时钟信号的一个周期中递送输出中断信号,并且逻辑的第一输入直接连接到输入接口,以便在中断信号的发生期间,在第一输入上递送至少一个中断信号从而授权生成控制器时钟信号,并且在中断信号的发生之后,通过外部时钟信号的中断来禁止递送控制器时钟信号。

30.因此,直接连接到输入接口的逻辑使得能够自动生成仅一个控制器时钟周期。

31.根据一个备选实施例,其中中断控制器被配置成在控制器时钟信号的多个周期中递送输出中断信号,控制器包括控制级,控制级连接在输入接口、逻辑的第一输入以及中断控制器的输出之间。

32.控制级可以被配置成在至少一个中断信号的发生期间,只要对应的输出中断信号尚未被递送,就在逻辑的第一输入上递送逻辑信号从而授权生成控制器时钟信号,以及一旦该输出中断信号已被递送,就通过中断外部时钟信号来禁止递送控制器时钟信号。

33.因此,在中断外部时钟信号之前,控制级使得能够等待待被递送输出中断信号。然后,控制器时钟信号在多个周期期间生成,从而使得控制器能够递送输出中断信号。

34.根据一个实施例,控制级包括存储器(例如锁存器),存储器由外部时钟信号控制,并且被配置成在存储器中存储至少一个中断信号的存在,直到生成输出中断信号为止。

35.根据一个实施例,控制级包括与门,该与门具有连接到中断控制器的输出的第一反相输入,并且具有连接到存储器的输出的第二输入。

36.根据一个实施例,中断控制器是安全中断控制器,并且至少一个中断信号是至少一个安全故障信号。

37.根据另一方面,提出了一种微控制器,其包括:包含有不安全处理核的不安全域,不安全处理核包含不安全程序代码;包含有至少一个安全处理核的安全域,安全处理核包含安全程序代码(诸如上面描述的设备),其被配置成将潜在的(多个)输出中断信号递送给安全处理核;以及设备外部的至少一项不安全装备;以及控制模块,与至少一项外部安全装备相关联,并且被配置成在由不安全处理核尝试访问至少一项安全装备的情况下,将安全故障信号递送给设备。

38.根据另一方面,一种用于管理中断控制器的方法,包括:接收至少一个中断信号;

接收外部时钟信号;在中断控制器的输入上递送控制器时钟信号,在控制器时钟信号存在的情况下,中断控制器递送输出中断信号。在至少一个中断信号存在的情况下,直到输出中断信号被递送为止,控制器时钟信号可以根据外部时钟信号自动生成。

39.根据一个实施方式,该方法包括:分别接收多个中断信号,以及在中断信号中的至少一个中断信号存在的情况下,根据外部时钟信号自动生成控制器时钟信号。

40.根据一个实施方式,该方法包括生成或不生成控制器时钟信号,包括:通过门控外部时钟信号来不中断或中断外部时钟信号,从而进行控制。

41.根据一个实施方式,该方法包括:中断控制器在控制器时钟信号的一个周期中递送输出中断信号,并且在中断信号的发生期间,通过不中断外部时钟信号来生成控制器时钟信号,以及在中断信号的发生之后,通过中断外部时钟信号来禁止递送控制器时钟信号。

42.根据一个实施方式,该方法包括:在至少一个中断信号的发生期间,只要对应的输出中断信号尚未被递送,通过不中断外部时钟信号,中断控制器在控制器时钟信号的多个周期中递送输出中断信号和控制器时钟信号;以及一旦该输出中断信号已被递送,则通过中断外部时钟信号来禁止递送控制器时钟信号。

43.控制电路cc被配置成:取决于是否接收到源自多项外部装备eq1、eq2、eq3中的至少一项外部装备的中断信号ilacin,在中断控制器ci的输入ec上递送或不递送控制器时钟信号clk

‑

ci。

44.在由控制电路cc接收到中断信号ilacin之后,在该实施例中,中断控制器ci能够在控制器时钟信号clk

‑

ci的仅一个周期中,在输出sc上递送输出中断信号ilacout。

45.在这方面,设备的中断控制器ci可以是例如与stmicroelectronics的以stm32l5来指代的中断控制器类似的类型。

46.输出中断信号ilacout随后旨在例如被递送给处理核cpu,诸如微处理器。

47.处理核cpu可以是安全处理核,其被配置成处理从安全装备发出的诸如安全故障的中断信号。图5图示的实施例将在下文进行描述。

48.如果再次参考图1,可以看出,控制电路cc包括输入接口pl1,输入接口pl1连接到外部装备eq1、eq2、eq3。由此可以理解,可以存在连接到控制电路cc的输入接口的任意数目项外部装备。

49.多项外部装备中的至少一项外部装备被配置成发出中断信号ilacin,该中断信号ilacin由控制电路cc的输入接口接收。输入接口在此包括以pl1来指代的或门,或门的每个输入连接到多项外部装备eq1、eq2、eq3中的一项外部装备。

50.通常,控制电路cc包括控制器,用于在至少一个中断信号ilacin存在的情况下,根据外部时钟信号clk自动生成控制器时钟信号clk

‑

ci,该外部时钟信号clk在控制电路cc的时钟输入eck上被接收,例如由石英或锁相环递送。

51.在这方面,控制器包括逻辑,在此以pl2指代的与门,与门的第一输入e1连接到或门pl1的输出,并且与门的第二输入e2连接到时钟输入eck。

52.与门pl2的输出连接到中断控制器ci的输入ec。

53.现在更具体地参考图2,图2以与根据参考图1描述的实施例的设备dis的操作有关的定时图的形式,图示了根据本发明的方法的一个实施方式。

54.根据此处呈现的实施方式,在接收到中断信号ilacin之后,设备dis的中断电路ci

能够在控制器时钟信号clk

‑

ci的仅一个周期中,递送输出中断信号ilacout。

55.下文公开了操作设备dis的步骤。

56.一旦设备dis在操作中,外部时钟信号clk由控制电路cc的时钟输入eck接收。外部时钟信号因此被连续地递送给与门pl2的第二输入e2。

57.设备dis在操作中,中断信号ilacin可以由控制电路cc接收。

58.此处,由多项外部装备中的一项外部装备发出的中断信号的存在通过在信号ilacin的高状态处的脉冲来进行转换,而中断信号的不存在通过信号ilacin的低状态来进行转换。中断信号ilacin在控制电路cc的输入接口pl1的输入中的一个输入上接收。

59.一旦中断信号ilacin被接收,中断信号ilacin就被直接传送到与门pl2的第一输入e1。

60.在中断信号ilacin存在或不存在的情况下,逻辑(这里,与门pl2)分别自动实施对外部时钟信号clk的不中断或中断(该技术通常被称为“时钟门控”),以便自动生成或不生成控制器时钟信号clk

‑

ci。

61.当输出中断信号ilacout已经被发射时,该信号回落到低状态,这与回落到中断信号ilacin的低状态相一致并且因此外部时钟信号clk的中断,这是由于信号ilacout在控制器时钟信号clk

‑

ci的一个周期中被生成。

62.换句话说,在中断信号ilacin存在的情况下并且直到递送对应的输出中断信号为止,根据外部时钟信号clk自动生成控制器时钟信号clk

‑

ci。

63.图3图示了示出包括中断控制器c1的电子设备的一个实施例的框图,中断控制器c1链接到控制电路cc,但是在该实施例中被配置成在控制器时钟信号clk

‑

ci的多个周期之后,在输出scle上递送输出中断信号ilacout。

64.与图1中的实施例相关,除逻辑门pl2之外,控制电路cc的控制器还包括控制级etc,控制级etc连接在输入接口pl1的输出(在此为以pl1指代的或门的输出)与以pl2指代的与门的第一输入e1之间。

65.在一个实施例中,在一方面,控制级etc被配置成将从一项外部装备发出的中断信号ilacin的存在存储在存储器中,直到递送对应的输出中断信号ilacout为止,并且在另一方面,被配置成取决于中断信号ilacin的存在、并且根据中断信号ilacin在存储器中的存储,在门pl2的第一输入上递送逻辑信号en,逻辑信号en授权门pl2递送控制器时钟信号clk

‑

ci。

66.在这方面,控制级etc包括存储器bsc(在此,锁存器),使得能够将中断信号ilacin的存在存储在存储器中。存储器被设置到外部时钟信号clk的速率。

67.附加地,控制级etc通过反馈回路连接到中断控制器ci的输出sc。

68.更具体地,控制级etc包括以pl3指代的与门,其具有连接到中断控制器ci的输出sc的第一反相输入。与门pl3的第二输入e4连接到存储器bsc的输出sb。

69.锁存器bsc的输出sb递送信号en

‑

ctrl。

70.与门pl3的输出连接到以pl4指代的第一或门的第一输入e5。

71.第一或门pl4的第二输入e6连接到输入接口pl1的输出。第二第一或门pl4的输出连接到存储器bsc的输入eb。

72.以pl5指代的第二或门的第一输入e7连接到存储器bsc的输出sb,并且第二或门

pl5的第二输入e8连接到输入接口pl1的输出。第二或门pl5的输出连接到与门pl2的第一输入e1。

73.因此,控制级在与门pl2的第一输入e1上递送逻辑信号en。

74.只要逻辑信号en处于高状态,门pl2就不中断外部时钟信号clk,这使得可以生成中断控制器ci的控制器时钟信号clk

‑

ci。

75.当逻辑信号en处于低状态时,门pl2然后中断外部时钟信号clk,从而禁止递送控制器时钟信号clk

‑

ci。

76.现在更具体地参考图4,图4以与根据参考图3描述的实施例的设备的操作有关的定时图的形式,图示了根据本发明的方法的另一实施方式。

77.根据在此呈现的实施方式,在控制器时钟信号clk

‑

ci的多个周期之后,中断电路ci递送输出中断信号ilacout。

78.下文公开了操作设备dis的步骤。

79.一旦设备dis在操作中,外部时钟信号clk由控制电路cc的时钟输入eck接收。外部时钟信号被连续递送给与门pl2的第二输入e2。

80.中断信号ilacin可以由控制电路cc接收。

81.再次,由多项外部装备中的一项外部装备发出的中断信号的存在通过在信号ilacin的高状态处的脉冲进行转换,而中断信号的不存在通过信号的低状态来进行转换。

82.当中断信号ilacin由输入接口接收时(信号ilacin的高状态),逻辑信号en在或门pl5的输出上改变为高状态。

83.在外部时钟信号clk的一个周期之后,存储器bsc在存储器中存储中断信号ilacin的存在,并且信号en

‑

ctrl改变为高状态,而中断信号ilacin回落到低状态。

84.此外,由于输出中断信号ilacout尚未被递送,所以门pl3的反相输入e3以与输入e4相同的方式处于高状态。

85.门pl3的输出处于高状态,这将锁存器bsc的输入eb维持在高状态。

86.尽管不存在中断信号ilacin,信号en仍保持高状态,从而不导致外部时钟信号clk的中断。

87.随后,在多个控制器时钟周期之后,中断控制器ci递送输出中断信号ilacout。输出中断信号ilacout由与门pl3的反相输入接收,其然后改变为低状态。

88.然后,锁存器bsc的输入eb变为低状态,并且信号en

‑

ctrl在一个时钟周期clk后变为低状态,这与信号ilacout的回落到低状态相一致,并且从而导致信号en变为低状态,并且因此导致通过与门pl2来中断外部时钟信号clk。

89.贯穿在逻辑信号en处于高状态期间的整个时间,生成控制器时钟信号clk

‑

ci。

90.从中断信号ilacin的发生以来,并且只要对应的输出中断信号ilacout尚未被递送,逻辑信号en就处于高状态。

91.换句话说,再次,在中断信号ilacin存在的情况下并且直到对应的输出中断信号的递送为止,根据外部时钟信号clk自动生成控制器时钟信号clk

‑

ci。

92.图5图示了微控制器mcu,微控制器mcu特别地包括不安全域和安全域。

93.微控制器可以是stmicroelectronics中以stm32来指代的微控制器家族。

94.例如,不安全域在这里包含不安全处理核cpu(诸如微处理器),不安全处理核cpu

包含不安全程序代码以及一项不安全装备eq2ns(为简单起见,仅示出了一项不安全装备,但当然可以提供多项不安全装备)。

95.安全域包含至少一个安全处理核cpus,至少一个安全处理核cpus以与参考图1或图3描述的设备dis相同的方式包含安全程序代码,并且包含被认为安全的中断控制器。

96.安全域还包括一项外部安全装备eq1s(为简单起见,仅示出了一项安全装备,但当然可以提供多项安全装备)。

97.处理核cpu、cpus、设备dis和多项安全或不安全的外部装备通过常规结构的互连网络itc互连,并且本身是已知的。

98.与每项安全或不安全装备相关联的是控制模块ms1、ms2以及寄存器rg1、rg2,寄存器rg1、rg2被配置成包含指示对应项的装备是否安全的信息。

99.控制模块ms1被配置成在由不安全处理核cpu尝试访问第一项外部安全装备eq1s的情况下,递送安全故障信号(中断信号)。

100.实际上,控制模块ms1会将寄存器rg1的内容与旨在用于一项装备eq1s的事务的字段进行比较,该字段包含表示不安全事务的指示。所发出的安全故障将被发送到设备dis。设备的安全中断控制器随后将输出中断信号递送给安全处理核cpus。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。