具有混合精度运算的处理单元

背景技术:

1.处理器采用一个或多个处理单元,所述一个或多个处理单元被专门设计和配置成代表处理器执行指定的运算。例如,一些处理器采用通常实现多个处理元件(也称为处理器内核或计算单元)的图形处理单元(gpu)和其他并行处理单元,所述处理元件同时在多个数据集上执行单个程序的多个实例,以执行图形、矢量和其他计算处理运算。处理器的中央处理单元(cpu)向gpu提供命令,并且gpu的命令处理器(cp)将命令解码为一个或多个运算。gpu的执行单元,诸如一个或多个算术逻辑单元(alu),执行运算以执行图形和矢量处理运算。

附图说明

2.通过参考附图,可更好地理解本公开,并且本公开的众多特征和优点对本领域技术人员来说变得显而易见。在不同附图中使用的相同附图标记指示相似或相同项。

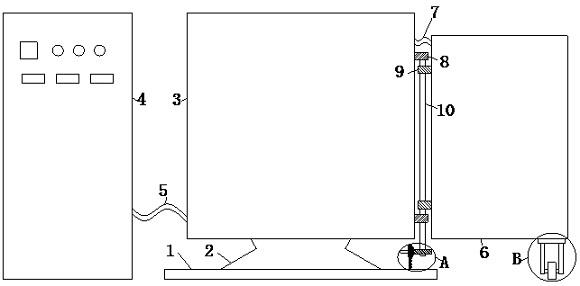

3.图1是根据一些实施方案的采用用于混合精度运算的运算码的处理单元的一部分的框图。

4.图2是根据一些实施方案的图1的处理单元的混合精度浮点执行路径的框图。

5.图3是根据一些实施方案的图1的处理单元的另一混合精度浮点执行路径的框图。

6.图4是根据一些实施方案的图1的处理单元的混合精度整数执行路径的框图。

具体实施方式

7.图1至图4示出了技术,其中并行处理单元,在本示例中为图形处理单元(gpu),实现具有相关联的运算码的运算以执行混合精度数学运算。gpu包括具有不同执行路径的算术逻辑单元(alu),其中每个执行路径执行不同的混合精度运算。通过响应于指定描述运算的运算码而实现alu处的混合精度运算,gpu在减少执行开销的同时高效地提高了指定的数学运算的精度。

8.举例说明,在执行指令的过程中,gpu执行由与指令相关联的运算码指定的数学运算。运算码至少部分地通过指定用于数学运算的操作数的大小来指示数学运算的精度。例如,一些运算码指定将以16位操作数执行的16位浮点运算,而其他运算码指定将以32位操作数执行的32位运算。照惯例,该运算使用的所有操作数都具有相同的大小,并且因此具有相同的精度。然而,对于一些运算,诸如采用具有相同大小的操作数的一些矢量处理数学运算,会导致运算的总体精度损失。例如,其中所有操作数限制为16位的点积运算的结果对于一些应用具有相对较低的精度。使用本文所描述的技术,gpu响应于对应的运算码而以混合精度操作数执行数学运算,由此高效地支持增加的数学精度。

9.图1示出了根据一些实施方案的支持混合精度运算的gpu 100。出于描述的目的,假设gpu 100是执行指令集(例如,计算机程序)以代表电子装置实施任务的处理器的一部分。因此,在不同的实施方案中,gpu 100是诸如台式计算机、笔记本计算机、服务器、平板电脑、智能电话、游戏控制台等电子装置的一部分。此外,假设包括gpu100的处理器包括执行

指令集的中央处理单元(cpu)。

10.gpu 100被设计和制造成代表cpu实施指定的运算。特别地,gpu 100代表cpu执行图形和矢量处理运算。例如,在一些实施方案中,在执行指令的过程中,cpu生成与图形和矢量处理运算相关联的命令。cpu向gpu 100提供命令,该gpu采用命令处理器(未示出)将命令解码成指令集以在gpu 100处执行。

11.为了有助于指令的执行,gpu 100包括解码级102和alu 104。在一些实施方案中,解码级102是包括支持指令执行的额外级的指令流水线(未示出)的一部分,包括从指令缓冲器提取指令的提取级、附加解码级、除alu 104之外的执行单元、以及退出执行的指令的退出级。解码级102包括用于将从提取级接收到的指令(例如,指令101)解码为一个或多个运算(例如,运算105)并且根据运算的类型将这些运算分派到执行单元中的一个的电路。在一些实施方案中,由对应的运算码识别每个运算,并且解码级基于运算码而识别执行单元,并向执行单元提供指示运算码的信息。执行单元采用运算码或基于运算码的信息来确定要执行的运算的类型,并执行所指示的运算。

12.例如,一些运算和相关联的运算码指示算术运算。响应于识别出接收到的指令指示算术运算,解码级102确定用于该运算的运算码并将该运算码连同诸如要用于算术运算的操作数等其他信息一起提供给alu 104。alu 104使用存储在寄存器文件110处的指示的操作数来执行由运算码指示的运算。在一些实施方案中,由alu 104提供的运算指示操作数的精度和要执行的运算。例如,在一些实施方案中,解码级102使用16位操作数为16位乘法运算提供一个运算(和对应的运算码),并使用32位操作数为32位乘法运算提供另一运算(和对应的运算码)。

13.另外,解码级102为混合精度数学运算生成具有对应运算码的运算,其中混合精度运算采用不同大小的操作数。例如,在一些实施方案中,解码级基于对应的指令而生成乘法

‑

累加(macc)运算,该运算将一种大小(例如,16位)的操作数相乘并将结果与不同大小(例如,32位)的操作数相加。在一些实施方案中,这些运算包括:1)混合精度点积运算(定名为dot4_f32_f16),将两组四个16位浮点操作数相乘,并将乘法结果彼此相加并与32位浮点操作数相加;2)混合精度点积运算(定名为dot2_f32_f16),将两组两个16位浮点操作数相乘,并将乘法结果彼此相加并与32位浮点操作数相加;以及3)混合精度点积运算(定名为dot_i32_i16),将两组四个16位整数操作数相乘,并将乘法结果彼此相加并与32位整数操作数相加。

14.alu 104包括不同的执行路径来执行每个混合精度运算。在一些实施方案中,不同的执行路径共享电子部件或模块,诸如寄存器、加法器、乘法器等。在其他实施方案中,一些或所有不同的执行路径是独立的并且不共享算术电路或模块。在绘示的实施方案中,alu 104包括执行dot4_f32_f16运算的路径106、执行dot2_f32_f16运算的路径107和执行dot4_i32_i16运算的路径108。响应于接收到用于混合精度运算的运算码或其他指示符,alu 104使用对应的执行路径来执行运算,并将结果存储在寄存器文件110的寄存器处。在一些实施方案中,每个混合精度运算由单个运算码指定。也就是说,alu104不需要多个运算码或运算来执行混合精度运算,从而在支持提高精度的同时减少了处理开销。

15.图2图示了根据一些实施方案的dot4_f32_f16执行路径106。如上所述,dot4_f32_f16运算将一组四个16位操作数(出于描述的目的定名为a0、a1、a2和a3)与另一组四个16位

操作数(出于描述目的定名为b0、b1、b2和b3)中的对应操作数相乘,并将结果与第三个32位操作数(定名为c)相加。因此,dot4_f32_f16运算由以下公式表示:

16.d.f32=a.f16[0]*b.f16[0] a.f16[1]*b.f16[1] a.f16[2]*b.f16[2] a.f16[3]*b.f16[3] c.f32

[0017]

此外,dot_f32_f16运算的功能用如下伪代码表示:

[0018]

[0019][0020]

要实现该运算,执行路径106包括:一组16位寄存器(例如,寄存器212),用于存储操作数a0、a1、a2和a3以及操作数b0、b1、b2和b3;以及32位寄存器,用于存储操作数c。这些操作

数中的每个表示为包括尾数和指数的浮点数。执行路径106还包括一组加法器(例如,加法器216)和乘法器(例如,乘法器218),其中每个加法器将对应的一对a和b操作数的指数相加,并且每个乘法器将对应的一对a和b操作数的尾数相乘。因此,例如,加法器216将操作数a0和b0的指数相加,而乘法器218将操作数a0和b0的尾数相乘。

[0021]

执行路径106还包括指数比较模块220和尾数排序和对准模块222。指数比较模块220从加法器接收求和的指数,并比较这些和以确定指数中的任何失配,并确定用于随后归一化的结果d.f32的临时指数值,如下所述。指数比较模块220向尾数排序和对准模块222提供指示识别出的失配的控制信令。尾数排序和对准模块222从乘法器接收尾数乘积,并基于由指数比较模块提供的信息。基于指数失配信息,尾数排序和对准模块222使尾数乘积移位,使得移位后的每个尾数乘积由相同的指数值表示。尾数排序和对准模块222由此对准尾数乘积以进行相加。

[0022]

要将对准的尾数乘积相加,执行路径106包括融合加法器224。在一些实施方案中,要提高精度,融合加法器224将具有比a、b和c操作数更大的位大小的值相加。例如,在一些实施方案中,a和b操作数是16位值,c操作数是32位值,并且尾数排序和对准模块222生成为82位宽的尾数值。在这些实施方案中,融合加法器224能够将82位(或更大)的值相加,由此防止尾数相加期间的精度损失。

[0023]

融合加法器224将尾数值相加以生成d.f32的尾数的临时值,并将临时尾数值提供给归一化模块226,该归一化模块对临时尾数值进行归一化。例如,在一些实施方案中,归一化模块226将临时尾数值移位,以移除尾数中的任何前导零。在一些实施方案中,归一化模块226调整临时尾数以促使临时尾数的整数部分为指定值(例如,1)。基于对尾数所做的调整,归一化模块调整由指数比较模块220提供的临时指数值,以保留临时尾数的总体值。另外,归一化模块基于从尾数排序和对准模块222接收到的尾位229而为尾数设置粘滞位。

[0024]

归一化模块226将d.f32的经调整的尾数值和指数值提供给舍入模块228。舍入模块228基于指定的舍入规则而对尾数值进行舍入,诸如将d.f32舍入到最接近的偶数值,由此生成d.f32的最终值。舍入模块228将最终的d.f32值提供给寄存器文件110,以存储在由接收到的运算所指示的寄存器处。

[0025]

图3图示了根据一些实施方案的dot2_f32_f16执行路径107。如上所述,dot2_f32_f16运算将一组2个16位操作数(出于描述的目的定名为a0和a1)与另一组两个16位操作数(出于描述目的定名为b0和b1)中的对应操作数相乘,并将结果与第三个32位操作数(定名为c)相加。因此,dot2_f32_f16运算由以下公式表示:

[0026]

d.f32=a.f16[0]*b.f16[0] a.f16[1]*b.f16[1] c.f32

[0027]

要实现该运算,执行路径107包括一组32位寄存器(寄存器320、321和323)来存储操作数a0、a1、b0、b1和操作数c。在一些实施方案中,将操作数存储在寄存器320、321和323中的不同寄存器中,取决于正被执行的特定指令或运算。例如,对于dot2_f32_f16运算的一个实例,寄存器320存储a操作数,寄存器321存储b操作数,而寄存器323存储c操作数。对于dot2_f32_f16运算的另一实例,寄存器320存储c操作数,寄存器321存储b操作数,而寄存器323存储a操作数。此外,对于dot2_f32_f16运算的不同实例,32位寄存器的不同部分存储16位操作数中的不同操作数。例如,对于一些实例,将a0操作数存储在寄存器320、321和323中的一个的上16位中,而对于其他实例,将a0操作数存储在寄存器320、321和323中的一个的

低16位中。执行路径106还包括操作数选择模块,用于基于由接收到的运算提供的控制信息而从寄存器320、321和323中选择操作数。

[0028]

将操作数中的每个表示为包括尾数和指数的浮点数。执行路径107包括一组预归一化模块(例如,预归一化模块324)以通过例如将16位操作数转换成32位操作数(诸如,通过转换16位操作数的指数值)来预归一化16位操作数a0、a1、b0、b1。另外,执行路径107包括非归一化刷新模块326,该非归一化刷新模块在c操作数是非归一值时将c的值刷新为零。

[0029]

要将a和b操作数相乘,执行路径107包括一组“与”门(例如,“与”门328)、一组加法器(例如,加法器330)和一组乘法器(例如,乘法器332)。每个“与”门对对应的一对预归一化的a和b操作数的符号位执行逻辑“与”运算,以生成用于对应乘法运算的符号位。因此,例如,在一个实例中,“与”门328对预归一化操作数a0和b0的符号位执行“与”运算,以生成用于a0*b0运算的符号位。每个加法器将对应的一对预归一化的a和b操作数的指数相加,并且每个乘法器将对应的一对预归一化的a和b操作数的尾数相乘。因此,例如,加法器216将预归一化的操作数a0和b0的指数相加,而乘法器218将预归一化的操作数a0和b0的尾数相乘。

[0030]

要将由“与”门、乘法器和加法器生成的乘积相加,执行路径107包括融合加法器334。在一些实施方案中,要提高精度,融合加法器224将具有比a、b和c操作数更大的位大小的值相加。例如,在一些实施方案中,a和b操作数是16位值,c操作数是32位值,加法器生成7位指数,而乘法器生成22位尾数乘积。在这些实施方案中,融合加法器334能够将52位的值相加,由此防止尾数相加期间的精度损失。

[0031]

融合加法器224将尾数乘积值相加以生成d.f32的尾数的临时值,并将临时尾数值和指数值提供给归一化模块336,该归一化模块对临时d.f32值进行归一化。例如,在一些实施方案中,归一化模块336将临时尾数值移位,以移除尾数中的任何前导零。在一些实施方案中,归一化模块336调整临时尾数以促使临时尾数的整数部分为指定值(例如,1)。基于对尾数所做的调整,归一化模块调整临时指数值,以保留d.f32的总体值。

[0032]

归一化模块336将d.f32的经调整的尾数值和指数值提供给舍入模块338。舍入模块338基于指定的舍入规则而对尾数值进行舍入,诸如将d.f32舍入到最接近的偶数值,由此生成d.f32的最终值。舍入模块228将最终的d.f32值提供给寄存器文件110以进行存储。

[0033]

图4示出了根据一些实施方案的dot2_i32_i16执行路径108。如上所述,dot2_i32_i16运算将一组2个16位整数操作数(出于描述的目的定名为a0和a1)与另一组两个16位整数操作数(出于描述目的定名为b0和b1)中的对应整数操作数相乘,并将结果与第三个32位整数操作数(定名为c)相加。因此,dot2_i32_i16运算由以下公式表示:

[0034]

d.i32=a.i16[0]*b.i16[0] a.i16[1]*b.i16[1] c.i32

[0035]

要实现该运算,执行路径108包括一组32位寄存器(寄存器440、441和443)以存储操作数a0、a1、b0、b1和操作数c。在一些实施方案中,将操作数存储在寄存器440、441和443中的不同寄存器中,取决于正被执行的特定指令或运算,与上面关于图3所描述的执行路径107相似。执行路径108还包括操作数选择模块,用于基于由接收到的运算提供的控制信息而从寄存器440、441和443中选择操作数。

[0036]

要将a和b操作数相乘,执行路径108包括乘法器444和446。乘法器444和446中的每个将对应的各对16位操作数相乘以生成32位乘积。执行路径108还包括32位加法器,该加法器将由乘法器444和446生成的乘积彼此相加并与c操作数相加以生成d.i32的临时值。执行

路径108包括接收d.i32的临时值以及钳位值(定名为clmp)的饱和模块450。饱和模块450将临时d.i32值与clmp值进行比较。响应于超过clmp值的d.i32值,饱和模块450将最终d.i32值设置为clmp值,否则将最终d.i32值设置为临时d.i32值。饱和模块450将最终d.i32值提供给寄存器文件110以进行存储。

[0037]

如本文所述,在一些实施方案中,一种方法包括:在处理单元处解码第一指令以识别第一多精度运算;以及通过使用不同精度的操作数执行第一数学运算,在算术逻辑单元(alu)处执行第一多精度运算。在一个方面,第一数学运算包括浮点乘法

‑

累加运算。在另一方面,浮点乘法

‑

累加运算将两组n个第一精度的操作数相乘,并将与第一精度不同的第二精度的操作数相加。在一个方面,n至少为二。在另一方面,n至少为四。

[0038]

在一个方面,第一数学运算包括整数乘法

‑

累加运算。在另一方面,该方法包括:在处理单元处解码第二指令以识别与第一多精度运算不同的第二多精度运算;以及通过使用不同精度的操作数执行第二数学运算,在alu处执行第二多精度运算,所述第二数学运算与第一数学运算不同。在另一方面,执行第一多精度运算包括在alu的第一执行路径处执行第一多精度运算;并且执行第二多精度运算包括在alu的第二执行路径处执行第二多精度运算,所述第二执行路径与第一执行路径不同。

[0039]

在一些实施方案中,一种处理单元包括:解码级,用于解码第一指令以识别第一多精度运算;以及算术逻辑单元(alu),用于通过使用不同精度的操作数执行第一数学运算来执行第一多精度运算。在一个方面,第一数学运算包括浮点乘法

‑

累加运算。在另一方面,浮点乘法

‑

累加运算将两组n个第一精度的操作数相乘,并将与第一精度不同的第二精度的操作数相加。在一个方面,n至少为二。在另一方面,n至少为四。

[0040]

在一个方面,第一数学运算包括整数乘法

‑

累加运算。在另一方面,解码级将解码第二指令以识别与第一多精度运算不同的第二多精度运算;而alu将通过使用不同精度的操作数执行第二数学运算在alu处执行第二多精度运算,所述第二数学运算与第一数学运算不同。在另一方面,alu包括:第一执行路径,用于执行第一多精度运算;以及第二执行路径,用于执行第二多精度运算,所述第二执行路径与第一执行路径不同。

[0041]

在一些实施方案中,处理单元包括:算术逻辑单元(alu),所述算术逻辑单元(alu)包括:第一执行路径,用于通过使用不同精度的操作数执行第一数学运算来执行第一多精度运算;以及第二执行路径,用于通过使用不同精度的操作数执行第二数学运算来执行第二多精度运算,所述第二数学运算与第一执行路径不同。在一个方面,第一数学运算包括第一浮点乘法

‑

累加运算,而第二数学运算包括第二浮点乘法

‑

累加运算。在另一方面,第一浮点乘法

‑

累加运算将两组n个第一精度的操作数相乘,并将具有与第一精度不同的第二精度的操作数相加,并且其中第二浮点乘法

‑

累加运算将两组m个第一精度的操作数相乘,并将第二精度的操作数相加。在一个方面,n至少为二,且m至少为四。

[0042]

在一些实施方案中,上文所描述的技术的某些方面可由执行软件的处理系统的一个或多个处理器实现。软件包括存储或以其他方式有形地体现在非暂时性计算机可读存储介质上的一个或多个可执行指令集。软件包括在由一个或多个处理器执行时操纵一个或多个处理器来执行上文所描述的技术的一个或多个方面的指令和某些数据。非暂时性计算机可读存储介质包括例如磁盘或光盘存储装置、固态存储装置(诸如快闪存储器、高速缓存、随机存取存储器(ram)或一个或多个其他非易失性存储器装置)等。存储在非暂时性计算机

可读存储介质上的可执行指令可呈现源代码、汇编语言代码、对象代码或由一个或多个处理器解译或以其它方式执行的其它指令格式。

[0043]

应注意,并不需要上文以一般描述所描述的所有活动或元件,具体活动或装置的一部分可能是不需要的,并且可执行一个或多个其他活动,或者可包括除所描述的那些元件之外的元件。此外,列出活动的顺序不一定是执行活动的顺序。而且,已经参考具体实施方案描述了概念。然而,本领域中的普通技术人员会了解,可在不背离所附权利要求中阐述的本公开范围的情况下,做出各种修改和改变。因此,本说明书和附图将被视为说明性而非限制性的,并且所有此类修改都意在被包括在本公开的范围内。

[0044]

上文已经参照具体实施方案描述了益处、其他优点以及问题的解决方案。然而,所述益处、优点、问题解决方案以及可致使任何益处、优点或问题解决方案出现或变得更突出的任何特征都不应被解释为是任何或所有权利要求的关键、必需或必要特征。此外,以上所公开的特定实施方案仅是说明性的,因为所公开的主题可按受益于本文教义的本领域技术人员显而易见的不同但等效的方式来修改和实践。除了如所附权利要求中所描述的之外,并不意在限制本文所示出的构造或设计的细节。因此,明显的是可更改或修改以上所公开的特定实施方案,并且所有此类变化形式被认为在所公开的主题的范围内。因此,本文所寻求的保护如所附权利要求中所阐述。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。