1.本发明是关于一种侦错装置(debug device)及其操作方法,特别是利用侦错装置的存储器在未执行侦错程序时作为电子装置的外部储存装置及其对应的操作方法。

背景技术:

2.在产品开发过程中,对于新开发的产品,都会进行各种测试或检验,在这些测试的过程中,会产生各种侦错数据或者异常状况的记录,这些数据都必须将其储存以供开发者做进一步的分析,来调整或变更现有的设计。现有的数据保存方式,大多是将其储存在装置内部原有的快闪存储器空间当中,也就是在储存相关测试程序等数据外的剩余空间当中。对此,若需要进行长时间的电性测试或是温湿度环境可靠度测试,原有的剩余存储器空间恐不足以储存长时间测试所产生大量的侦错数据。

3.为解决上述侦错数据储存的问题,就必须寻求外部的储存空间,现有的解决手段是通过有线或无线的方式将侦错数据传送到外部的储存空间,以避免数据遗失。然而,在进行上述可靠度测试的同时,待测试装置可能无法连接其他数据传输线,亦即无法通过有线方式将数据送出。若是要通过无线方式传输,原本开发的装置上势必要加装额外的无线传输装置,增加操作上的困难度,且并非所有产品都能适用。

4.综观前所述,现有的侦错数据保存方式仍然具有相当的改进空间,因此,本发明藉由设计一种侦错装置及其操作方法,针对现有技术的缺失加以改善,进而增进产业上的实施利用。

技术实现要素:

5.有鉴于上述现有技术的问题,本发明的目的就是在提供一种侦错装置及其操作方法,藉由侦错装置的存储器在未执行侦错程序时作为电子装置的外部储存装置,解决储存空间不足的问题。

6.根据本发明的一目的,提出一种侦错装置,用以连接具有序列线侦错(serial wire debug,swd)接口的电子装置。侦错装置包含存储器、处理单元、序列线侦错接口以及通用序列汇流排(universal serial bus,usb)接口,处理单元连接于存储器,序列线侦错接口连接至序列线侦错接口,当通用序列汇流排接口连接至电脑,处理单元将电脑的侦错指令传送至电子装置,当通用序列汇流排接口断开时,存储器成为电子装置的外部储存装置。

7.较佳地,存储器可包含快闪存储器(flash)或静态随机存取存储器(static random access memory,sram)。

8.较佳地,侦错装置可进一步包含发光二极管(light emitting diode,led)以及计数器(counter)的至少一者。

9.较佳地,外部储存装置的储存数据可包含电子装置的侦错数据或异常记录。

10.较佳地,存储器的储存数据可包含侦错指令或侦错指令的转换程序。

11.较佳地,存储器的储存数据可包含电子装置的离线测试指令。

12.根据本发明的另一目的,提出一种侦错装置的操作方法,其包含以下步骤:设置侦错装置,侦错装置包含存储器、处理单元、序列线侦错接口以及通用序列汇流排接口;将序列线侦错接口连接至电子装置的序列线侦错接口,并将通用序列汇流排接口连接至电脑的通用序列汇流排接口,藉由处理单元将电脑的侦错指令传送至电子装置;以及断开通用序列汇流排接口,将存储器作为电子装置的外部储存装置。

13.较佳地,存储器可包含快闪存储器或静态随机存取存储器。

14.较佳地,侦错装置可包含发光二极管以及计数器的至少一者。

15.较佳地,外部储存装置可储存电子装置的侦错数据或异常记录。

16.较佳地,存储器可储存侦错指令或侦错指令的转换程序。

17.较佳地,存储器可储存电子装置的离线测试指令。

18.承上所述,依本发明的侦错装置及其操作方法,其可具有一或多个下述优点:

19.(1)此侦错装置及其操作方法可利用侦错装置在断开通用序列汇流排接口时切换成电子装置的外部储存装置,增加保存电子装置侦错数据或异常记录等数据的储存空间,避免数据遗失也同时增加数据存取的便利性。

20.(2)此侦错装置及其操作方法能在电子装置的侦错过程中以原本连接的侦错装置提供外部储存空间,无须连接额外传输线或无线传输装置来传输数据,降低硬体设置成本,也避免影响侦错流程的环境设定。

21.(3)此侦错装置及其操作方法能利用侦错装置本身元件所具备的功能来提供电子装置的侦错流程所需的软硬体支援,例如计数器、发光二极管等,提升电子装置进行侦错时的操作效率。

附图说明

22.图1为本发明实施例的侦错装置的方块图。

23.图2为本发明实施例的侦错装置的示意图。

24.图3为本发明另一实施例的侦错装置的示意图。

25.图4为本发明实施例的侦错装置操作方法的流程图。

26.附图标记:

27.11、21、31:侦错装置

28.12:电子装置

29.13、23:电脑

30.24:服务器

31.111:存储器

32.112:处理单元

33.113、211、311:序列线侦错接口

34.114、212、312:通用序列汇流排接口

35.115、318:发光二极管

36.116:计数器

37.121、221:序列线侦错接口

38.122、222:芯片

39.131、231:通用序列汇流排接口

40.132:处理器

41.133:储存装置

42.223:测试基板

43.313:控制基板

44.314:外壳

45.315:微处理器

46.316:快闪存储器

47.317:静态随机存取存储器

48.s1~s3:步骤

具体实施方式

49.为利贵审查委员了解本发明的技术特征、内容与优点及其所能达成的功效,兹将本发明配合附图,并以实施例的表达形式详细说明如下,而其中所使用的图式,其主旨仅为示意及辅助说明书之用,未必为本发明实施后的真实比例与精准配置,故不应就所附的图式的比例与配置关系解读、局限本发明于实际实施上的权利范围,合先叙明。

50.请参阅图1,图1为本发明实施例的侦错装置的方块图。如图所示,侦错装置11包含存储器111、处理单元112、序列线侦错接口113以及通用序列汇流排接口114,处理单元112可为微处理器,连接于存储器111以存取存储器111当中的程序或数据。序列线侦错接口113与通用序列汇流排接口114连接于处理单元112,两种不同接口可连接于不同的数据传输接口。在本实施例中,序列线侦错接口113连接电子装置12的序列线侦错接口121,而通用序列汇流排接口114则是连接至电脑13的通用序列汇流排接口131。

51.电子装置12包含芯片122,芯片122可为新开发的系统芯片、驱动芯片或控制芯片等,其可安装于各种装置内的主机板、印刷电路板上。芯片122在测试时必须将接脚连接至电路板或测试板上的线路,并进一步连接至序列线侦错接口121,才能进行相关的侦错程序。序列线侦错接口121是用来进行芯片侦错程序的操作接口,相较于联合测试行动小组(joint test action group,jtag)协议的侦错模式,序列线侦错接口121需要的接脚较少,且适用于高速及大数据量的侦错程序。另一方面,电脑13包含处理器132及储存装置133,处理器132可为桌上型电脑、笔记型电脑的中央处理器,连接至硬盘等储存装置133来存取各种侦错或测试程序,并通过电脑13的通用序列汇流排接口131传送至侦错装置11。

52.侦错装置11的设置是为了将电脑13当中所编辑的侦错程序,转换成芯片122能读取的侦错指令,因此在侦错装置11当中的存储器111,可储存侦错指令的转换程序,当侦错装置11由通用序列汇流排接口114连接至电脑13时,电脑13可将侦错程序传送到侦错装置11,通过转换程序转换成芯片122可执行的侦错指令,再通过序列线侦错接口113将侦错指令直接传送至电子装置12,对芯片122进行侦错程序。在另一实施例中,侦错指令也可预先储存于侦错装置11的存储器111当中,待侦错装置11连接至电子装置12后再对芯片122进行侦错程序。

53.如同背景技术所述,芯片122在进行这些侦错程序的测试时,会产生相关的侦错数

据及异常状态记录,当原本芯片122内部所具有的储存空间不足以储存上述的侦错数据时,就需要进一步寻找额外的储存空间。在本实施例中,当侦错装置11的通用序列汇流排接口114断开与电脑13的连接时,也就是侦错装置11不再接收电脑13传送的数据时,侦错装置11本身的存储器111即可成为电子装置12的外部储存装置。当芯片122在执行侦错指令后,产生的相关数据,可通过序列线侦错接口121传送至侦错装置11保存,当侦错程序完成后,操作者可将侦错装置11连接至电脑13或储存数据的服务器,将侦错数据或异常记录等储存数据传送至电脑13,让开发者能检视这些数据,进而调整或修改产品开发的相关软硬体设置。

54.除此之外,侦错装置11还可包含发光二极管115及计数器116,分别连接至处理单元112,当侦错装置11通过通用序列汇流排接口114连接至电脑13时,发光二极管115可作为数据传输时的指示灯号,而计数器116可协助处理单元112控制传输量。当侦错装置11断开通用序列汇流排接口114的连线时,侦错装置11的存储器111可作为电子装置12的外部储存装置,此时发光二极管115可作为侦错程序时的指示灯号,而计时器116也可作为侦错程序当中的计数装置,提供侦错程序所需的软硬体支援。

55.请参阅图2,图2为本发明实施例的侦错装置的示意图。如图所示,侦错装置21具备适用于两种不同连接接口的接口,分别为序列线侦错接口211以及通用序列汇流排接口212。上述接口可分别为对应不同传输接口的接头,序列线侦错接口211对应于序列线侦错接口221,通用序列汇流排接口212对应于通用序列汇流排接口231。芯片222可设置在测试基板223上,测试基板223可为类似电子装置的主机板或印刷电路板,包含相关的被动元件,通过测试基板223上的线路,可将芯片222连接至序列线侦错接口221,进而连接至侦错装置21进行侦错程序。序列线侦错接口221为延伸至电子装置或测试板外的插槽,其可对应于侦错装置21的序列线侦错接口211,由于侦错装置21包含此序列线侦错(swd)的传输接口,与一般的通用序列汇流排(usb)外接装置有所不同。

56.在本实施例中,通用序列汇流排接口231可为电脑23的通用序列汇流排插槽,这里所述的电脑23可为笔记型电脑、桌上型电脑或是测试工作站上的相关测试装置,操作者可于电脑23上编辑侦错程序后,将侦错程序传送至侦错装置21,侦错装置21进一步将侦错程序转换成芯片222可执行的侦错指令,再经由序列线侦错接口221将侦错指令传送至芯片222执行,藉此执行上述侦错程序。当侦错装置21的通用序列汇流排接口212断开与电脑23的连接时,也就是通用序列汇流排接口212不再供电时,侦错装置21可产生一支援码,并将支援码传送至芯片222,藉此让芯片222将侦错装置21作为外接的储存装置。例如,侦错装置21可将存储器的储存空间容量或者预先规划的储存位置等信息传送至芯片222,提供芯片222上传数据时所需的讯息。

57.设定通用序列汇流排接口212断开电脑23为切换机制的设定,主要是当芯片222在进行侦错程序时,其测试的环境需要考量静电、温湿度等设定,难以在连线于电脑23的状态下进行,因此在侦错装置21一端断开电脑23的情况下,即可让存储器当中储存的离线测试指令继续进行芯片222的侦错程序,而侦错装置21剩余的存储器空间则成为芯片222的外部储存装置,增加储存空间但不影响侦错程序的设定及进行。当完成侦错程序后,储存于侦错装置21当中的侦错数据及异常记录,可再次连接至电脑23,藉由电脑23来存取上述储存的数据,并进一步将这些侦错数据及异常记录上传到服务器24的数据库中储存,或者当侦错装置21直接连接至服务器24的装置接口时,直接将侦错装置21当中储存的数据上传至数据

库中,以保存所述芯片222于侦错程序中产生的侦错数据或异常记录。

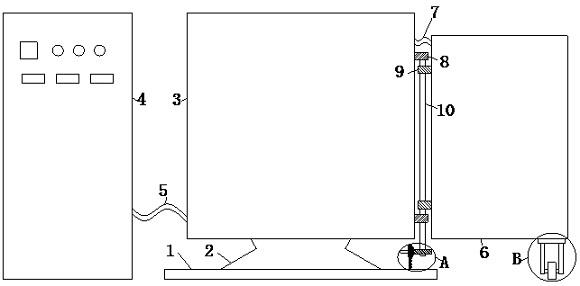

58.请参阅图3,图3为本发明实施例的侦错装置的示意图。如图所示,侦错装置31的两端分别包含序列线侦错接口311及通用序列汇流排接口312,其接口如同前述实施例,是分别对应于序列线侦错(swd)接口及通用序列汇流排(usb)接口,相同内容不再重复描述。在侦错装置31当中,设有控制基板313,控制基板313可为印刷电路板,且控制基板313可设置在侦错装置31的外壳314当中,控制基板313上的线路分别连接至序列线侦错接口311及通用序列汇流排接口312。控制基板313上包含微处理器315以及存储器装置,在本实施例当中,存储器装置可包含快闪存储器316或静态随机存取存储器317,但本揭露不以此为限,存储器装置也可为其他类型的储存装置。除此之外,控制基板313上可进一步设置一或多个发光二极管318,作为侦错装置31操作时的状态显示灯号。

59.如同前述实施例所述,当侦错装置31的通用序列汇流排接口312断开与电脑的连线时,侦错装置31当中的快闪存储器316或静态随机存取存储器317可作为芯片侦错程序进行时的外部储存装置,储存侦错数据及异常记录。除此之外,当作为外部储存装置时,侦错装置31当中的微处理器315也可提供芯片测试时所需的硬体支援,例如于控制基板313上设置计数器,让微处理器315连接至计数器,在侦错程序中可提供计数功能。原本作为侦错装置31操作状态显示灯号的发光二极管318,也可作为芯片侦错程序当中,显示操作状态的灯号。

60.请参阅图4,图4为本发明实施例的侦错装置操作方法的流程图。此操作方法适用于前述实施例的侦错装置,相关装置架构及连接关系请参阅前述实施例的说明。如图所示,侦错装置操作方法包含以下步骤(s1~s3):

61.步骤s1:设置侦错装置。设置侦错装置,藉由侦错装置连接电子装置与编辑侦错程序的电脑,其中,侦错装置包含存储器、处理单元、序列线侦错接口以及通用序列汇流排接口。这里所述的存储器可包含快闪存储器或静态随机存取存储器。

62.步骤s2:将序列线侦错接口连接至电子装置的序列线侦错接口,并将通用序列汇流排接口连接至电脑的通用序列汇流排接口,藉由处理单元将电脑的侦错指令传送至电子装置。将侦错装置的序列线侦错接口连接至芯片测试基板上的序列线侦错插槽,而侦错装置的通用序列汇流排接口则连接电脑的通用序列汇流排插槽,使得电脑中的侦错程序能通过存储器中储存的侦错指令转换程序,将侦错指令转换成芯片可执行的指令格式,再将侦错指令传送至包含芯片的电子装置中以进行侦错程序。在另一实施例中,存储器也可预先储存芯片的侦错指令或是离线测试指令,将其传送至电子装置来进行侦错程序。

63.步骤s3:断开通用序列汇流排接口,将存储器作为电子装置的外部储存装置。当侦错装置的通用序列汇流排接口断开与电脑的连接时,侦错装置可传送支援码至芯片,使芯片将侦错装置作为电子装置的外部储存装置,当电子装置中的芯片进行侦错程序时,各个侦错数据或异常状态的记录,都能储存于侦错装置的存储器中,藉此增加储存数据的空间,且电子装置无需增加额外的硬体连接。

64.在本实施例中,侦错装置当中的处理单元,也能将其他硬体资源分享给电子装置使用,例如藉由计数器提供计数的功能,或者将发光二极管转为侦错程序中的状态显示灯号,皆能提供电子装置更佳的操作功效。

65.以上所述仅为举例性,而非为限制性者。任何未脱离本发明的精神与范畴,而对其

进行的等效修改或变更,均应包含于前附的权利要求书范围中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。