1.本发明是关于计算方法及计算装置,且更特定而言,是关于一种存储 器内运算方法及装置。

背景技术:

2.相较于传统机器学习方法,循环神经网络(recurrent neural network; 简称rnn)已展示其在诸如图像识别及语音增强的若干领域上达成较大 准确度的能力。然而,在当前范纽曼(von

‑

neumann)架构上进行rnn 时已出现若干挑战。举例而言,在全连接状神经网络中,在进行rnn时 处理单元与芯片外存储器单元之间的过度数据移动,将引发效能限制及高 功率消耗。

3.为桥接计算单元与存储器单元之间的隔阂,存储器内计算的概念被广 泛地提出,且具有电阻性随机存取存储器(resistive random

‑

accessmemory;reram)的忆阻器为最密集研究的解决方案之一。reram(新 兴的非易失性存储器(non

‑

volatile memory;简称nvm)之一)通过改变 单元的电阻来存储数据,且经过证明拥有计算及存储的两种能力。具体而 言,忆阻器通过设定不同输入电压及电阻值以分别表示输入值及权重值, 而对模拟态样进行数字rnn运算,亦即乘加(multiply

‑

and

‑

accumulate; 简称mac)运算。

4.举例而言,图1绘示通过使用忆阻器进行mac运算的计算的实例, 此实例旨在计算∑(v

n

×

g

n

)的结果。在此实例中,每一字线通过位在3d 空间中交叉点处的reram单元连接至每一位线。通过克希荷夫电流定律 (kirchhoffs current law;简称kcl),在给定对应字线的电压v1及v2的 情况下,每一reram单元的通过电导g1、g2、g3、g4感应的出现的电 流i1、i2、i3、i4瞬时地与对应位在线的电流i5及i6相加。通过感测每 一位在线的电流同时撷取mac运算的结果,其中i5的值等于v1

×

g1 v2

×

g2且i6的值等于v1

×

g3 v2

×

g4。

5.然而,归因于忆阻器中总电流的重叠分布,rnn的准确度显著降低。

6.举例而言,图2绘示忆阻器中的所有单元的输出电流的分布。当将预 定义电压施加至输入线时,所有单元的输出电流的可能分布所绘示的x轴 指示电流且y轴指示频率的图2中。当更多单元用于mac运算时,分布 变得更宽。如图2中所绘示,当16个单元用于mac运算时,如图2中所 绘示的分布,将呈现输入值的17个可能组合,其中绘示于图2左侧的分 布22可代表零值,此分布在总电流变得更大时会变得更宽。因此,重叠 变化误差的几率变得更高。

技术实现要素:

7.鉴于上述内容,本发明提供一种能够减少重叠变化误差且增大计算的 准确度的存储器内运算方法及存储器内运算装置。

8.本发明提供一种存储器内运算方法,适于处理器对具有交叉开关架构 的存储器进行乘加(mac)运算。所述存储器包括彼此交叉的多个输入线 及多个输出线,多个单元分别配置于输入线及输出线的相交点处,且多个 感测放大器分别连接至输出线。在所述方法

中,通过截断多个权重的二进 制数据的分数位的至少一部分及计算二进制数据的剩余位的补码,将二进 制数据的格式自浮点格式变换成量化格式,且将多个权重的经过变换的二 进制数据编程至多个单元中。接着执行调整程序,其中包括将多个输入信 号的二进制数据迭代地输入至多个输入线中,对由感测放大器感测到的输 出进行整合,以及基于整合的输出来调整编程至单元中的多个权重的二进 制数据,持续多个迭代。在多个迭代之后,基于减少每一权重的二进制数 据中值为一的位的几率来重塑(reshaping)多个权重的二进制数据,且重 复调整程序直至满足结束条件为止。

9.在本发明的一实施例中,计算二进制数据的剩余位的补码的步骤包括 计算剩余位的2的补码且反转所计算出的2的补码的值。

10.在本发明的一实施例中,基于所整合的输出来调整编程至单元中的多 个权重的二进制数据的步骤包括计算所整合的输出与输入信号的参考信 号之间的差,且根据所述差来调整待编程至单元中的多个权重的经过变换 的二进制数据。

11.在本发明的一实施例中,基于减少每一权重的二进制数据中值为一的 位的几率来重塑多个权重的二进制数据的步骤包括根据所整合的输出与 输入信号的参考信号之间的差来计算准确度,并响应于所计算出的准确度 大于第一阈值而提前重塑。

12.在本发明的一实施例中,基于减少每一权重的二进制数据中值为一的 位的几率来重塑多个权重的二进制数据的步骤包括计算多个权重的二进 制数据中值为一的位与值为零的位的比,并响应于所计算出的比大于第二 阈值而提前重塑。

13.在本发明的一实施例中,基于减少每一权重的二进制数据中的值为一 的位的几率来重塑多个权重的二进制数据的步骤包括通过将每一权重的 十进制值移位任意数以最大化权重的二进制数据中值为一的位的减少与 所移位的数的商,且将此商除以基于多个权重的数据分布所判定的因子, 以计算器率,以及回应于所述商大于或等于阈值而根据所计算出的几率将 每一权重的十进制值移位。

14.本发明提供一种存储器内运算装置,其包括存储器及处理器。所述存 储器具有交叉开关架构,其中包括彼此交叉的多个输入线及多个输出线、 分别配置于输入线及输出线的相交点处的多个单元,以及分别连接至输出 线的多个感测放大器。所述处理器耦接至存储器且经配置以通过截断多个 权重的二进制数据的分数位的至少一部分及计算二进制数据的剩余位的 补码,将二进制数据的格式自浮点格式变换成量化格式,且将多个权重的 经过变换的二进制数据编程至多个单元中,并执行调整程序,其中包括将 多个输入信号的二进制数据迭代地输入至多个输入线中,对由感测放大器 感测到的输出进行整合,以及基于整合的输出来调整编程至所述单元中的 多个权重的二进制数据,持续多个迭代,以及在多个迭代之后,基于减少 每一权重的二进制数据中值为一的位的几率来重塑多个权重的二进制数 据,且重复调整程序直至满足结束条件为止。

15.在本发明的一实施例中,处理器计算剩余位的2的补码且反转所计算 出的2的补码的值。

16.在本发明的一实施例中,处理器计算整合的输出与输入信号的参考信 号之间的差,且根据所述差来调整待编程至单元中的多个权重的经过变换 的二进制数据。

17.在本发明的一实施例中,处理器根据所述整合的输出与输入信号的参 考信号之间的差来计算准确度,且响应于所计算出的准确度大于第一阈值 而提前重塑。

18.在本发明的一实施例中,处理器计算多个权重的二进制数据中值为一 的位与值为零的位的比,且响应于所计算出的比大于第二阈值而提前重 塑。

19.在本发明的一实施例中,处理器通过将每一权重的十进制值移位任意 数以最大化权重的二进制数据中值为一的位的减少与所移位的数的商,且 将所述商除以基于多个权重的数据分布所判定的因子,且响应于所述商大 于或等于阈值而根据所计算出的几率将每一权重的十进制值移位,以计算 器率。

20.在本发明的一实施例中,所述调整程序包括神经网络的训练,其中将 多个输入信号的二进制数据设定为神经网络的输入,将多个权重设定为神 经网络中的多个计算层中的权重,且将整合的输出设定为神经网络的输 出。

21.在本发明的一实施例中,每一权重的具有浮点格式的二进制数据在32 位二进制数据中包括一个符号位、八个指数位以及二十三个分数位。

22.为使本发明的前述特征及优势更可理解,下文详细描述随附附图的实 施例。

附图说明

23.图1绘示通过使用忆阻器进行mac运算的计算的实例。

24.图2绘示忆阻器中的所有单元的输出电流的分布。

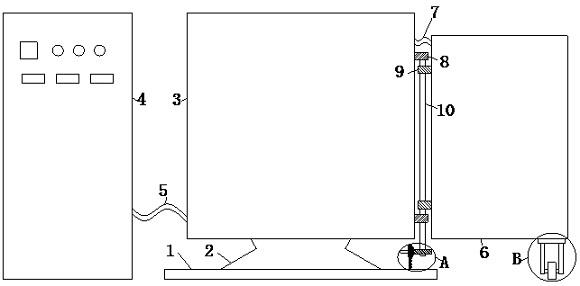

25.图3为根据本发明的实施例的存储器内运算装置的示意图。

26.图4为根据本发明的实施例的存储器内运算方法的流程图。

27.图5为根据本发明的实施例的二进制数据的浮点格式。

28.图6a及图6b为分别绘示根据本发明的实施例的在量化9位二进制 数据中及在反转的量化9位二进制数据中的位「0」与位「1」的比的示意 图。

29.图7为示出根据本发明的实施例的神经网络的训练的示意图。

30.图8为示出根据本发明的实施例的数据重塑的示意图。

31.图9为根据本发明的实施例的存储器内运算方法的流程图。

32.【符号说明】

33.20:图

34.22:分布

35.30:计算装置

36.32:存储器

37.34:处理器

38.50:浮点格式

39.52:符号位

40.54:指数位

41.56:分数位

42.70:神经网络

43.72:语音信号

44.74:增强语音信号

45.76:干净语音信号

46.g1、g2、g3、g4:电导

所描述。存储器内运算可实施至各种人工智能(artificial intelligent;简称 ai)应用,诸如全连接层、卷积层(convolution layer)、多层感知、支持 向量机或使用忆阻器实施的其他应用,此在本发明中不受限制。

61.图4为根据本发明的实施例的存储器内运算方法的流程图。参看图3 及图4,本实施例的方法适合于上述计算装置30,且将在下文参考计算装 置30的各种装置及元件描述本实施例的存储器内运算方法的详细步骤。

62.首先,在步骤s402中,处理器34通过截断多个权重的二进制数据的 分数位的至少一部分及计算所述二进制数据的剩余位的补码,将所述二进 制数据的格式自浮点格式变换成量化格式,且将多个权重的经过变换的二 进制数据编程至多个单元中。在一些实施例中,每一权重的具有浮点格式 的二进制数据在32位二进制数据中包括一个符号位、八个指数位以及二 十三个分数位,且处理器34可截断所有二十三个分数位或是仅截断这些 分数位的一部分,以便减少位「1」的数目。

63.在一些实施例中,处理器34可在截断之后计算剩余位的2的补码, 并反转所计算的2的补码的值,以便减少位「1」的数目且最大化位「0」 的数目,且因此减少重叠变化误差。

64.举例而言,图5为根据本发明的实施例的二进制数据的浮点格式。参 考图5,32位二进制数据x的浮点格式50为通过ieee组织标准化的格 式,且包含一个符号位52、八个指数位54以及二十三个分数位56。详言 之,32位二进制数据的正负号由单一位表示,其中位「0」指示负数,且 位「1」指示正数。32位二进制数据的指数存储为具有127的偏置的8位 无正负号整数。32位二进制数据的浮点数(mantissa)存储为23位无正负 号整数。以1.101

×25

的数目作为实例,正负号为正,浮点数为「1.101」, 且指数为「5」。

65.在一些实施例中,在全精度训练中,位「0」的比接近位「1」的比。 当将二进制数据量化至9位(亦即截断所有分数位)时,位「0」的比减 小,而位「1」的比升高,但训练误差未显著受量化影响。由于当量化二 进制数据时会增加位「1」的比,故提出用于翻转位「1」的值的方法,以 减少位「1」的数目且最大化位「0」的数目,以便减少重叠变化误差且增 加训练的准确度。

66.在一些实施例中,进行称为「反转2的补码」的方法,其中计算出浮 点格式的二进制数据中的8位指数的2的补码且反转所计算出的2的补码 的值。举例而言,对于十进制值「

‑

1」,「

‑

1」的指数的2的补码为「01111110」, 且反转后的2的补码为「00000001」,其包含更少的位「1」。

67.图6a及图6b为分别绘示根据本发明的实施例的在量化9位二进制 数据中及在反转的量化9位二进制数据中的位「0」与位「1」的比的示意 图。图6a绘示量化9位二进制数据中的每一位的位「0」与位「1」的比, 其中,在量化9位二进制数据的大部分位中,位「1」的比大于位「0」的 比,尤其在位2至位5中。参考图6b,由于图6a中的量化9位二进制数 据的位反转,故位「0」的比变为大于位「1」的比,尤其在位2至位5中。 关于位6至位8,本发明实施例提出数据重塑的方法,以进一步减小位「1」 的比,其将稍后示出。

68.返回图4的流程,在步骤s404中,处理器34通过以下操作来进行调 整程序:将多个输入信号的二进制数据迭代地输入至多个输入线il

i

中; 对由感测放大器sa感测到的输出(亦即电流i

j

)进行整合;以及基于整 合的输出来调整编程至单元中的多个权重的二进制数据,持续多个迭代。

69.在一些实施例中,调整程序包括神经网络的训练,其中将多个输入信 号的二进制数据设定为神经网络的输入,将多个权重设定为神经网络中的 多个计算层中的权重,且将整合的输出设定为神经网络的输出。

70.举例而言,图7为示出根据本发明的实施例的神经网络的训练的示意 图。参考图7,本实施例创建全连接的神经网络80,诸如循环神经网络 (rnn)、深度神经网络(deep neural network;简称dnn)或全卷积网络 (fully convolutional network;简称fcn),其中包括在输入层与输出层之 间设置多个中间层,并为这些层设置多个权重。根据上文所示出的计算方 法,将神经网络80中的权重的格式变换成量化格式且接着编程至存储器 的单元。将充当输入信号的多个噪声语音信号82输入至存储器的输入线 以在神经网络中进行正向传播。经神经网络80处理的语音信号82将作为 增强语音信号84输出,且与充当语音信号82的参考信号的干净语音信号 86相比较以计算损失函数(loss function),诸如均方误差(mean squareerror,简称mse)。接着,在神经网络80中进行反向传播以调整神经网络 80的计算层中的权重。将调整后的权重编程至存储器的单元以用于下一迭 代的训练。在一些实施例中,训练将持续许多迭代,以便使由神经网络80 输出的增强语音信号84接近于干净语音信号86,而经过训练的神经网络 80可在实际实施时用于对输入至神经网络80的任何语音信号进行噪声过 滤。

71.返回至图4的流程,在步骤s406中,处理器34在多个迭代之后将基 于减少每一权重的二进制数据中值为一的位的几率,来重塑多个权重的二 进制数据,且重复调整程序直至满足结束条件为止。

72.在一些实施例中,处理器34通过将每一权重的十进制值移位任意数 以最大化权重的二进制数据中值为一的位的减少与移位的数的商,且将所 述商除以基于多个权重的数据分布来判定的因子,以计算器率,且回应于 权重的所计算出的几率大于阈值而将权重的十进制值移位。

73.举例而言,图8为示出根据本发明的实施例的数据重塑的示意图。参 考图8,假定十进制值120为在调整程序的迭代之后获得的权重的指数值, 则可将所述指数值移位任意数(例如,小于阈值x的整数)以获得诸如 117或123的移位值。因此,分别计算出在移位指数值的二进制数据中的 位「1」的减少数r及在十进制中的指数值的移位数x,且如下计算权重的 二进制数据中的位「1」的减少数r与移位数x的商y。

74.y=r/x.

ꢀꢀꢀ

(1)

75.举例而言,对于等于3的阈值x,可将指数值120(二进制中的 「00000110」)移位至122(二进制中的「00000100」)。其中位「1」的减少 数r等于1而指数值的移位数x等于2,因此,商y等于「1/2」。

76.为了尽可能地减少位「1」,应最大化商y,且将其与阈值比较以便判 定是否触发数据重塑。在一些实施例中,如下基于通过将所计算出的商y 除以基于多个权重的数据分布来判定的因子α而计算出的可能性p来进行 数据重塑。

77.p=y

×

100%/α

ꢀꢀꢀ

(2)

78.对于以上将指数值120(二进制中的「00000110」)移位至122(二进 制中的「00000100」)的实例,商y等于1/2,且可能性p=0.5

×

100%/5 =10%,其表示进行数据重塑的可能性为10%且不进行数据重塑的可能性 为90%。当基于可能性进行数据重塑时,可很

好地实现神经网络的效能与 准确度的权衡。

79.图9为根据本发明的实施例的存储器内运算方法的流程图。参考图3 及图9,本实施例的方法适合于上述计算装置30,且将在下文参考计算装 置30的各种装置及元件描述本实施例的存储器内运算方法的详细步骤。

80.在步骤s1002中,处理器34创建具有多个层的神经网络且将具有如 上述实施例中所示出的量化格式的权重设定至这些层。

81.在步骤s1004中,处理器34通过将语音信号变换成数字数据且将经 过变换的数字数据输入至存储器32的输入线ili而将噪声或干净语音信号 输入至神经网络。

82.在步骤s1006中,处理器34通过进行神经网络的正向传播来增强语 音信号。将输入至存储器32的输入线ili的经过变换的数字数据乘以编程 至存储器32的单元(由电阻r

ij

表示)的权重,且输出由存储器32的感 测放大器sa感测到的总电流且将其变换成增强语音信号。

83.在步骤s1008中,处理器34通过进行神经网络的反向传播来微调神 经网络。在一些实施例中,处理器34基于增强语音信号与参考干净语音 信号之间的比较来调整编程至存储器32的单元中的权重。

84.在步骤s1010中,处理器34判定通过使用上文所示出的方程式(1) 计算出的商y是否大于或等于阈值。

85.响应于商y大于或等于阈值,在步骤s1012中,处理器34使用通过 上文所示出的方程式(2)所计算出的可能性,来重塑编程至存储器32的 单元中的权重。

86.回应于商y未大于或等于阈值或权重的重塑完成,在步骤s1014中, 处理器34将判定微调是否完成。响应于判定微调尚未完成,处理器返回 至步骤s1004,而持续输入语音信号以训练神经网络。另一方面,响应于 判定微调完成,处理器继续进行步骤s1016以结束训练。

87.在一些实施例中,处理器34可根据当前进行的迭代次数来判定微调 是否完成,且在迭代次数达到预定数目时判定微调完成。在一些实施例中, 处理器34可根据基于输出的增强语音信号与参考干净语音信号之间的差 所计算出的准确度,来判定微调是否完成,且在所计算出的准确度达到预 定阈值时,判定微调完成。

88.在一些实施例中,处理器34可响应于满足一些条件而提前重塑。在 一些实施例中,处理器34可根据整合的输出与输入信号的参考信号之间 的差来计算准确度,且响应于所计算出的准确度大于第一阈值而提前重 塑。在一些实施例中,处理器34可计算多个权重的二进制数据中的位「1」 与位「0」的比,且回应于所计算出的比大于第二阈值而提前重塑。

89.经由上文所描述的方法,可在对模型准确度的影响有限的情况下减小 重叠变化误差的几率。

90.综上所述,根据本发明的实施例,提出一种存储器内运算方法以权衡 神经网络或实施忆阻器的其他应用的效能、准确度以及数据形式。因此, 可缩减神经网络的模型大小或应用程序的计算,以使神经网络或这些应用 更可实作在边缘装置或其他资源有限的硬件上。

91.至此,已经结合附图对本公开实施例进行了详细描述。

92.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行 了进一步详

细说明,所应理解的是,以上所述仅为本发明的具体实施例而 已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修 改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。