存储装置和用于管理存储装置中的电源的方法

1.本技术要求于2020年4月14日提交的题为“用于支持存储装置上的多个连接器的系统、方法和设备(systems,methods and apparatus for supporting multiple connectors on storage devices)”的第63/010,041号美国临时专利申请以及于2020年7月10日提交的第16/926,636号美国专利申请的优先权和权益,所述美国专利申请的公开通过引用包含于此。

技术领域

2.本公开总体涉及存储装置,并且更具体地涉及用于支持存储装置上的多个连接器的系统、方法和设备。

背景技术:

3.存储装置可通过连接器连接到主机系统。连接器可包括电源管理引脚,电源管理引脚可使存储装置响应于施加到电源管理引脚的电源管理信号来配置电源。

4.在本背景技术部分中公开的以上信息仅用于增强对发明的背景技术的理解,因此它可包含不构成现有技术的信息。

技术实现要素:

5.一种存储装置可包括:连接器,包括电源管理引脚;检测器电路,被配置为检测在电源管理引脚上接收的电源管理信号的转变;以及电源管理电路,能够至少部分地基于检测器电路检测到电源管理信号的转变来配置至存储装置的至少一部分的电源。连接器还可包括双端口启用引脚,并且电源管理电路可被配置为至少部分地基于双端口启用引脚的状态而被禁用。存储装置还可包括非易失性存储器,并且电源管理电路可被配置为至少部分地基于非易失性存储器的状态(例如,通过固件)而被禁用或启用。检测器电路可被配置为至少部分地基于非易失性存储器的状态来锁存电源管理信号。电源管理引脚可包括电源禁用引脚,并且电源管理电路可能够基于检测器电路检测到电源管理信号的转变来禁用至存储装置的至少一部分的电源。

6.一种存储装置可包括:连接器,包括电源管理引脚;非易失性存储器;以及电源管理电路,被配置为:基于确定非易失性存储器的第一状态,在第一电源管理模式下操作。在第一电源管理模式下,电源管理电路可至少部分地基于在电源管理引脚上接收到的电源管理信号来配置至存储装置的至少一部分的电源。存储装置还可包括:检测器电路,被配置为检测在电源管理引脚上接收到的电源管理信号的转变,并且电源管理电路可至少部分地基于检测器电路检测到电源管理信号的转变来禁用至存储装置的至少一部分的电源。连接器还可包括双端口启用引脚,并且电源管理电路被配置为至少部分地基于双端口启用引脚的状态来禁用至存储装置的至少一部分的电源。存储装置可在第一电源管理模式下被配置为u.3存储装置。电源管理引脚可包括电源禁用引脚。电源管理电路可被配置为:基于确定非易失性存储器的第二状态,在第二电源管理模式下操作。在第二电源管理模式下,电源管理

电路可禁用至存储装置的至少一部分的电源。存储装置可在第二电源管理模式下被配置为u.2存储装置。

7.一种方法可包括:通过连接器将存储装置连接到主机;检测在存储装置处通过连接器从主机接收的电源管理信号的转变;以及至少部分地基于检测到电源管理信号的转变来配置至存储装置的至少一部分的电源。配置至存储装置的至少一部分的电源的步骤可包括:禁用至存储装置的至少一部分的电源。可至少部分地基于非易失性存储器的状态来配置至存储装置的至少一部分的电源。所述方法还可包括:基于复位信号来锁存电源管理信号。可至少部分地基于在存储装置处通过连接器从主机接收的双端口启用信号的状态来配置至存储装置的至少一部分的电源。所述方法还可包括:基于复位信号来锁存双端口启用信号。

附图说明

8.附图不一定按比例绘制,并且在整个附图中,为了说明的目的,类似结构或功能的元件通常由相同的参考标号表示。附图仅意在便于描述在此描述的各种实施例。附图没有描述在此公开的教导的每个方面,并且不限制权利要求的范围。为了防止附图变得模糊,可能未示出所有的组件、连接等,并且可能不是所有的组件都具有参考标号。然而,可从附图中容易地清楚组件配置的模式。附图与说明书一起示出了本公开的示例实施例,并且与描述一起用于解释本公开的原理。

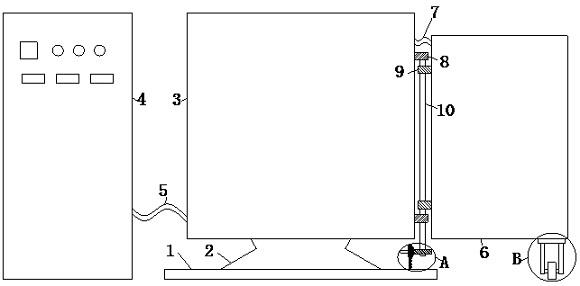

9.图1示出了根据本公开的具有检测器电路的存储装置的示例实施例。

10.图2示出了根据本公开的具有可配置的电源管理的存储装置的示例实施例。

11.图3示出了根据本公开的具有转变检测和可配置的电源管理的存储装置的示例实施例的真值表。

12.图4示出了根据本公开的存储装置的电源禁用信号的检测器电路的示例实施例。

13.图5示出了根据本公开的存储装置的电源禁用信号的检测器电路的另一示例实施例。

14.图6示出了根据本公开的可用于例如生成双端口启用有效信号的采样电路的实施例。

15.图7示出了根据本公开的用于生成双端口启用有效信号的方法的示例实施例的时序图。

16.图8示出了根据本公开的用于对电源禁用信号进行采样的方法时序的示例实施例的时序图。

17.图9示出了根据本公开的用于管理存储装置中的电源的方法的实施例。

具体实施方式

18.在一些实施例中,存储装置可响应于检测到通过连接器从主机接收的电源管理信号的转变而对装置内的电源进行管理。在一些实施例中,检测电源管理信号的转变可使得存储装置能够与具有不同引脚定义的不同主机连接器兼容,否则存储装置可能与具有不同引脚定义的不同主机连接器是不兼容的。例如,第一主机连接器可具有被定义为低(即,低电平)有效信号的电源禁用引脚。第二主机连接器可使用相同的(或机械兼容的)连接器,但

是将相同的电源禁用引脚定义为高(即,高电平)有效信号。这可能导致被设计用于第二主机连接器的存储装置在被插入第一主机连接器时不正确地表现(例如,进入电源禁用状态)。

19.然而,在第一主机连接器的一些实施方式中,电源禁用引脚可总是被拉到高状态(例如,它可不具有任何转变),而在第二主机连接器的一些实施方式中,电源禁用信号是高有效并且可具有从低状态到高状态的转变。因此,通过检测电源禁用信号的转变,存储装置可对第二主机连接器上的有效的电源禁用事件和第一主机连接器上的不存在电源禁用的事件进行区分。

20.在一些实施例中,存储装置的电源管理特征可响应于非易失性存储器的状态来配置。例如,存储装置可具有电源管理电路,该电源管理电路可响应于非易失性存储器中的配置位的状态来启用或禁用至存储装置的至少一部分的电源。在一些实施例中,这样的可配置的电源管理特征可使得单个存储装置能够被编程或配置,以例如与不同类型的主机连接器一起使用。

21.本公开中描述的特征可具有独立的实用性并可被单独实现,并且不是每个实施例都可利用每个特征。此外,特征也可以以各种组合来实现,所述各种组合中一些组合可以以协同的方式放大各个原理的益处。

22.示出根据本公开的一些可能的实施方式细节的系统、处理、方法等的一些示例实施例在下面进行描述。提供这些示例是为了说明本公开的原理,但是原理不限于这些实施例、实施方式细节等。

23.图1示出了根据本公开的具有检测器电路的存储装置的示例实施例。图1中示出的存储装置100可包括连接器102、检测器电路104、电源管理电路106、存储装置控制器108和存储介质110。连接器102可包括电源管理引脚112。

24.连接器102可利用可用于将存储装置连接到主机的任何类型的标准或非标准连接器来实现。一些示例可包括在sff

‑

8639规范中描述的连接器(诸如,被称为u.2和/或u.3(sff

‑

ta

‑

1001规范)连接器的连接器)、可扩展连接器(诸如,在sff

‑

ta

‑

1002规范中描述的连接器)、m.2连接器、可与任何存储互连一起使用的任何连接器(诸如,与串行高级技术附件(sata)、小型计算机系统接口(scsi)和/或串行连接scsi(sas)等一起使用的连接器)和/或具有任何机械和/或电气配置和/或任何配置的引脚的任何其他连接器。

25.检测器电路104可用如上所述的可检测在电源管理引脚112上接收的电源管理信号的转变的任何模拟和/或数字硬件、软件和/或它们的任何组合来实现。如下面更详细地描述的,例如,在连接器可被实现为u.3连接器的一些实施例中,检测器电路104可检测连接器的引脚p3上的pwrdis信号的低到高转变,以识别有效的电源禁用事件。

26.电源管理电路106可用可例如启用和/或禁用或减小至存储装置100的所有部分或任何部分的电源的任何模拟和/或数字硬件、软件和/或它们的任何组合来实现。例如,电源管理电路106可包括各种电源分配和/或调节电路,以通过连接器102的各种附加引脚从主机接收电源并将电源分配到整个存储装置100中。

27.存储介质110可用磁性、固态、光学和/或任何其他类型的数据存储技术或它们的组合来实现。因此,存储装置100可被实现为硬盘驱动器(hdd)、固态驱动器(ssd)、光盘驱动器(odd)和/或任何其他类型的存储装置。

28.存储装置控制器108可用可控制存储装置100的存储和其他功能的任何硬件、软件和/或它们的任何组合来实现。例如,在可使用闪存(诸如,与非(nand)存储器)作为存储介质110的一些实施例中,存储装置控制器108可包括闪存转换层(ftl)。

29.存储装置100可包括图1中未示出的附加组件和/或子组件和/或附加组件与子组件之间的互连。例如,一些实施例可包括一个或多个通信接口(例如,网络接口(诸如,以太网、光纤信道、无限带宽(infiniband)等)、存储或其他互连和/或协议(诸如,外围组件接口快速(pcie)、sas、sata、非易失性存储器快速(nvme)、通过网络的非易失性存储器快速(nvme over fabric,nvme

‑

of))等,以将存储装置控制器和/或其他组件接口连接到连接器102的各种引脚。作为另一示例,一些实施例可包括一个或多个计算组件(诸如,现场可编程门阵列(fpga)、嵌入式图形处理器(gpu)等)。

30.尽管在图1中一些组件可被示出为单独的组件,但是组件中的一些或全部可集成到其他组件中和/或分布在其他组件之间。

31.图2示出了根据本公开的具有可配置的电源管理的存储装置的示例实施例。图2中示出的存储装置114可包括与图1中示出的实施例中的组件类似的一些组件(诸如,具有电源管理引脚112的连接器102、电源管理电路106、存储装置控制器108和存储介质110)。然而,图2中示出的存储装置114还可包括非易失性存储器(nvm)116,非易失性存储器(nvm)116可用于配置和/或重新配置存储装置114的任何电源管理特征。例如,在一些实施例中,nvm 116可用于控制电源管理电路106,以启用或禁用至存储装置的所有部分或一个或多个部分的电源。

32.nvm 116可用可保存存储装置114的任何电源管理特征的模式或配置的任何技术来实现。一些示例可包括一个或多个位的只读存储器(rom)、可编程只读存储器(prom)、电池支持的随机存取存储器(ram)和/或闪存等。一些附加示例可包括一个或多个熔丝(fuse)、切割迹线(cut trace)、跳线(jumper)、拨码开关(dipswitch)、接头(header)、插入电路板或从电路板移除的导线等。

33.在一些实施例中,根据实施方式细节,基于非易失性存储器配置电源管理特征可使得存储装置能够沿着供应链(例如,通过制造商、分销商、用户等)在任何地方被配置和/或重新配置。例如,如果nvm用一个或多个位的电可重新编程存储器(诸如,闪存)来实现,则制造商、分销商、用户等可通过经由任何技术(诸如,以固件更新实用程序为例)访问闪存来对存储装置的电源管理配置进行重新编程。此外,具有可配置的电源管理的存储装置可通过使制造商能够制造单个设计的更多个装置并将它们编程为不同类型的装置来改善规模的经济性。

34.图3示出了根据本公开的具有信号转变检测和可配置的电源管理的存储装置的示例实施例的真值表。可在可被配置为使得u.3存储装置能够与具有u.2连接器的主机一起被使用的存储装置的情况下描述关于图3示出的实施例,但是发明原理不限于这些示例细节。

35.在一些实施例中,u.2主机连接器可被配置为与sata快速(sata express)规范一起使用,sata快速规范可将连接器的引脚p3定义为低有效时钟请求信号(clkreq#)。当被认定(低)时,clkreq#信号可使插入连接器的存储装置进入电源禁用状态。在一些实施例中,u.2主机连接器的引脚p3可被主机永久地拉到高逻辑电平,以防止插入到u.2主机连接器中的u.2存储装置进入电源禁用状态。在一些实施例中,对于可能不基于sata(例如,基于sas

或nvme)的主机,u.2主机连接器的引脚p3可被拉到高逻辑电平,以使默认地禁用电源禁用特征。

36.在一些实施例中,u.3主机连接器可配置有被定义为有高有效电源禁用信号(pwrdis)的连接器引脚p3。因此,如果u.3存储装置被插入到u.2主机连接器中,则u.3存储装置可能通过响应于连接器的引脚p3上的高逻辑电平而进入电源禁用状态而不正确地操作。因此,可使用单独的u.2存储装置和u.3存储装置来提供与u.2主机连接器和u.3主机连接器的正确操作。在一些实施例中,根据实施方式细节,这可增加制造商、分销商、用户等可能需要制造、库存等的装置类型的数量。

37.此外,在一些实施例中,存储装置的双端口特征还可能使电源管理特征的实现复杂化。例如,在一些实施例中,当存储装置被配置用于双端口操作时,电源禁用或其他电源管理特征可被禁用。例如,因为双端口操作可以是高可用性配置的一部分,所以电源管理可被禁用,在一些实施方式中,高可用性配置可能与电源禁用状态不一致。因此,具有存储装置的u.2和/或u.3版本中的每个的双端口启用版本的存储装置可进一步增加制造商、分销商、用户等可能需要制造、库存等的装置类型的数量。

38.在一些实施例中,根据实施方式细节,根据本公开的具有信号转变检测和可配置的电源管理的存储装置可使得单个存储装置能够在u.2主机连接器和u.3主机连接器两者中正确地操作,同时还利用同一装置实现单端口配置和双端口配置。

39.例如,为了实施图3中示出的特征,如图1中示出的实施例中所示,存储装置的实施例可实现检测器电路以检测u.3连接器的引脚p3上的pwrdis信号的转变。这样的实施例还可基于如图2中所示的实施例中示出的nvm单元的编程状态来启用或禁用电源管理电路。

40.再次参照图3,存储装置的实施例可根据nvm单元的编程状态响应于引脚p3和引脚e25的状态,如标记为“操作”的列中所示地进行操作。具体地,nvm单元可被编程至第一状态,以将存储装置配置为u.2存储装置。可选择地,nvm单元可被编程至第二状态,以将存储装置配置为u.3存储装置。引脚e25可被定义为用于u.2和u.3装置和主机连接器两者的低有效双端口启用信号(dualporten#)。当存储装置被配置为u.2装置时,引脚p3可被定义为低有效时钟请求信号(clkreq#),并且当存储装置被配置为u.3装置时,引脚p3可被定义为高有效电源禁用信号(pwrdis)。

41.参照图3的第二行,其中,引脚p3(pwrdis/clkreq#)和e25(dualporten#)两者都为低,存储装置可在电源管理被禁用的情况下在双端口模式下操作,而不管该装置被nvm单元配置为u.2装置还是u.3装置。在可能不基于sata(例如,基于sas和/或nvme)的一些实施例中,例如,因为nvm单元的状态可能不适用,所以可忽略nvm单元的状态。在一些实施方式中,可在pcie复位信号(perst#)的低到高转变期间对引脚p3进行采样。

42.参照图3的第三行,其中,引脚p3(pwrdis/clkreq#)为低并且e25(dualporten#)为高,存储装置可在电源管理被禁用的情况下在单端口模式下操作,而不管该装置被nvm单元配置为u.2装置还是u.3装置。

43.参照图3的第四行,其中,引脚p3(pwrdis/clkreq#)为高并且e25(dualporten#)为低,存储装置可在电源管理被禁用的情况下在双端口模式下操作,而不管该装置被nvm单元配置为u.2装置还是u.3装置。

44.参照图3的第五行,其中,引脚p3(pwrdis/clkreq#)和e25(dualporten#)二者为

高,存储装置可在单端口模式下操作,而不管该装置被nvm单元配置为u.2装置还是u.3装置。如果装置被配置为u.2装置,则电源管理可被禁用。然而,如果装置被配置为u.3装置,则电源管理可被启用,并且装置可响应于检测到pwrdis信号的低到高转变而进入电源禁用状态。

45.因此,在一些实施例中,根据实施方式细节,如图3中所示进行操作的存储装置可在插入u.3主机连接器时实现作为u.3存储装置的正确操作(例如,响应于pwrdis信号适当地实现电源管理),同时在插入u.2主机连接器时仍然保持可操作状态(不进入电源禁用状态)。

46.图4示出了根据本公开的存储装置的电源禁用信号的检测器电路的示例实施例。图4中示出的电路120可包括用于接收电源禁用输入信号(pwrdis)的输入端子122,电源禁用输入信号(pwrdis)可由包括电阻器r1、r2和电容器c1的滤波器电路滤波。例如,可从连接器上的电源管理引脚(例如,u.3连接器上的引脚p3)接收pwrdis信号。滤波后的输入信号vd_in可通过复杂可编程逻辑器件(cpld)124并且作为vd_out被施加到3输入与门126的一个输入。与门的输出可被施加到d触发器128的g输入,d触发器128可通过d端提供输出电源启用信号(chip_en)。d触发器128的s端接地。电源管理启用/gpio信号(电源管理启用)可被施加到3输入与门126的第二输入,并且双端口启用有效信号(dualporten_valid)可被施加到3输入与门126的第三输入。

47.在一些实施例中,输入端子122、滤波器电路、cpld 124和d触发器128可以是存储装置中的现有电路的一部分(例如,输入端子122、滤波器电路、cpld 124和d触发器128可作为图1中示出的存储装置控制器108的一部分)。因此,图4中示出的检测器电路120可获取现有信号vd_out,并且在vd_out由触发器128锁存之前用电源管理启用信号和双端口启用信号使其具备资格(qualify)。

48.chip_en信号可禁用至存储装置的所有部分或一些部分的电源。例如,chip_en信号可作为栅极信号被施加到电源管理电路,电源管理电路可通过连接器的引脚从主机接收电源并在整个存储装置中分配电源。

49.可例如由存储装置中的固件基于读取nvm中的寄存器中的配置位的状态来生成电源管理启用信号。因此,例如,如图3中所示,在一些实施例中,电源管理启用信号可使得电路120能够用于将存储装置配置为u.2装置或u.3装置。

50.可例如通过直接或通过反相器读取连接器上的双端口启用引脚(例如,u.3连接器上的引脚e25)的状态来生成dualporten_valid信号。可选择地,如下面更详细地描述的,可例如通过响应于复位信号而锁存连接器上的双端口启用引脚的状态来生成dualporten_valid信号。

51.因此,在一些实施例中,dualporten_valid信号可向电源管理电路提供单端口指示,该单端口指示可用于仅在存储装置处于单端口配置时才使引脚p3具备资格。例如,如图3中所示,在双端口配置中,可忽略引脚p3。如关于图3所描述的,在一些实施例中,电源禁用特征可仅用于单端口配置。对于双端口配置,例如,因为电源禁用可能与高可用性操作不一致,所以电源禁用可能不被支持。因此,在一些实施例中,当存储装置在单端口配置下操作时,与门126可仅使pwrdis信号能够由触发器128锁存。

52.图5示出了根据本公开的存储装置的电源禁用信号的检测器电路的另一示例实施

例。图5中示出的电路130可包括与图4中示出的实施例中的组件类似的一些组件。然而,在图5中示出的实施例中,与门132可被实现为2输入与门,并且电源管理启用信号反而可通过电阻器r3施加到cpld 136中的d触发器134的d输入。vd_out可从d触发器134的q端输出。在此实施例中,pwrdis信号可作为时钟输入施加到触发器134。因此,可在pwrdis信号的低到高转变时锁存电源管理启用信号的状态,这可使电路130能够检测pwrdis信号的低到高转变,pwrdis信号的低到高转变可用于进入电源禁用状态,但由电源管理启用信号的状态限定。因此,与u.2主机连接器上的恒定高逻辑电平相反,当在u.3存储装置中实现时,电路130可使得存储装置能够正确地确定存储装置连接到u.3主机连接器,并且因此确定pwrdis引脚信号上的高逻辑电平指示有效的电源禁用事件。

53.在一些实施例中,根据实施方式细节,检测器电路120和/或130中的任一个可被实现为例如可附接到存储装置的现有电路板的加密狗或附加板。因此,在一些实施例中,可在对制造和/或修改操作的影响相对低的情况下,将现有的存储装置转换为提供电源管理重新配置和/或正确的电源禁用和/或双端口操作。此外,在一些实施例中,根据实施方式细节,检测器电路120和/或130中的任一个可被集成到新设计中,而几乎没有或没有成本、开发时间等的增加。

54.图6示出了根据本公开的可用于例如生成双端口启用有效信号的采样电路的实施例。图6中示出的电路140可包括用于例如从连接器的引脚接收低有效pcie复位信号perst#的输入端子142。在由包括电阻器r4、r5和电容器c2的滤波器电路滤波之后,perst#信号可被施加到cpld 146中的d触发器144的时钟输入。例如,来自连接器上的双端口启用引脚(例如,u.2或u.3连接器上的引脚e25)的双端口启用信号(dualporten#)可作为d输入通过电阻器r6施加到触发器144。因此,可通过响应于perst#信号的低到高转变而锁存dualporten#信号来生成低有效dualporten#_valid信号。可通过反相器148提供互补的dualporten_valid信号。

55.图7示出了根据本公开的用于生成双端口启用有效信号的方法的示例实施例的时序图。图7中示出的方法可例如在上电(power

‑

up)时与图6中示出的采样电路一起使用。参照图7,在时间t1之前,一个或多个电源轨可以是稳定的,并且dualporten#信号可以是无效的。响应于低有效pcie复位信号perst#的激活,可在时间t2锁存dualporten#信号的状态。可例如基于dualporten#信号的保持时间、一个或多个电源轨可在指定的容差内之后的最小时间等来指定时间t1与t2之间的时间段t1。

56.在一些实施例中,可响应于复位信号(诸如,pcie复位信号perst#)来锁存电源管理信号(例如,电源禁用信号(诸如,pwrdis))。在一些实施例中,可使用与如图6中所示的用于双端口启用有效信号的电路140类似的采样电路来锁存电源管理信号。在一些实施例中,可至少部分地基于非易失性存储器的状态来锁存电源管理信号。

57.图8示出了根据本发明的用于对电源禁用信号进行采样的方法的示例实施例的时序图。该方法可开始于高有效电源禁用信号pwrdis处于低逻辑电平并且pcie复位信号perst#处于不确定状态。pwrdis信号可在时间t1被驱动至高有效状态并在时间段tpwrdis内保持在高有效状态,直到pwrdis信号可被去激活至低状态的时间t2。perst#信号可在pwrdis在时间t2被去激活之前的某个时间点被驱动至低有效状态。然后,perst#信号可在时间t3被去激活,这可在pwrdis信号在时间t2被去激活之后的保持时间tdisrst之后发生。

58.图6至图8中示出的实施例对于例如提供定义的和/或确定的行为、和/或为了符合可与可扩展连接器(诸如,在sff

‑

ta

‑

1002规范中描述的使用如例如在stt

‑

ta

‑

1009规范中定义的信号的可扩展连接器)一起使用的存储装置的实施例的规范可以是有益的。

59.图9示出了根据本公开的用于管理存储装置中的电源的方法的实施例。该方法可开始于在操作150通过经由连接器将存储装置连接到主机。在操作152,该方法可检测在存储装置处通过连接器从主机接收的电源管理信号的转变。在操作154,该方法可至少部分地基于检测到电源管理信号的转变来配置至存储装置的至少一部分的电源。

60.针对图9中示出的实施例以及在此描述的任何其他实施例描述的操作和/或组件是示例操作和/或组件。在一些实施例中,可省略一些操作和/或组件,和/或可包括其他操作和/或组件。此外,在一些实施例中,可改变操作和/或组件的时间顺序和/或空间顺序。

61.已经在各种实施方式细节的上下文中描述了上面公开的实施例,但是本公开的原理不限于这些具体细节或任何其他具体细节。例如,一些功能已经被描述为由特定组件实现,但是在其他实施例中,所述功能可分布在位于不同位置中并且具有各种用户界面的不同系统与组件之间。特定实施例已经被描述为具有特定的处理、步骤等,但是这些术语也包含其中特定的处理、步骤等可用多个处理、步骤等实现的实施例,或者其中多个处理、步骤等可被集成到单个处理、步骤等的实施例。对组件或元件的引用可仅表示组件或元件的一部分。例如,对集成电路的引用可表示集成电路的全部或仅一部分,并且对块的引用可表示整个块或一个或多个子块。除非从上下文中另外地清楚,否则在本公开和权利要求中使用诸如“第一”和“第二”的术语可仅用于区分它们所修饰的事物,并且可不指示任何空间顺序或时间顺序。在一些实施例中,“基于”可表示“至少部分地基于”。在一些实施例中,“禁用”可表示“至少部分地禁用”。对第一事物的引用可不暗示存在第二事物。

62.可组合上述各种细节和实施例以产生根据本专利公开的发明原理的附加实施例。由于在不脱离发明构思的情况下,可在布置和细节上修改本专利公开的发明原理,因此这些改变和修改被认为落入权利要求的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。