1.本发明是有关于一种处理器电路,且特别是有关于一种多核心处理器电路。

背景技术:

2.由于电子技术的进步,通过使用多核处理器可以实现更高的计算复杂性。为了降低晶片的成本,多核心设计中通常需要共享存储器架构。常规的多核心存储器共享设计需要仲裁器中的额外成本,尤其是程序存储器和数据存储器。于是,为共享程序存储器和用于多核心设计的数据存储器提出了一种新的架构,以通过使用分时共享方法,不存在存储器仲裁器的开销。

技术实现要素:

3.本发明提供一种多核心处理器电路,可省略存储器仲裁器的开销。

4.本发明的多核心处理器电路,包括多个处理器核心、程序存储器(program memory)、第一汇流排(first bus)、数据存储器(data memory)及第二汇流排(second bus)。程序存储器用以储存至少一程序指令。第一汇流排耦接于这些处理器核心与程序存储器之间。数据存储器用以储存至少一程序数据。第二汇流排耦接于多个处理器核心与数据存储器之间。其中,这些处理器核心逐个被使能以存取程序存储器及数据存储器,且其余的处理器核心被关闭。

5.基于上述,本发明实施例的多核心处理器电路,其中多个处理器核心不会同时运行,因此这些处理器核心与程序存储器或数据存储器的存取永远不会发生冲突。因此,不需要额外的仲裁程序设计来协调程序存储器和数据存储器。

6.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

附图说明

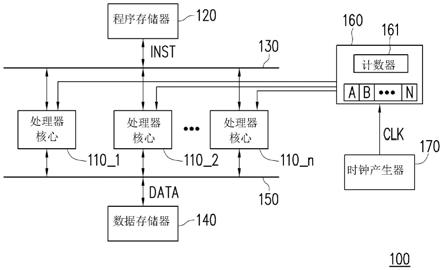

7.图1为依据本发明一实施例的多核心处理器电路的示意图。

8.图2为依据本发明一实施例的多核心处理器电路的时序示意图。

9.符号说明

10.100:多核心处理器电路;

11.110_1~110_n:处理器核心;

12.120:程序存储器;

13.130:第一汇流排;

14.140:数据存储器;

15.150:第二汇流排;

16.160:控制电路;

17.161:计数器;

18.170:时钟产生器;

19.a~n:暂存器;

20.clk:操作时钟;

21.data:程序数据;

22.inst:程序指令;

23.pm、dm:操作循环;

24.ta、tb:使能期间。

具体实施方式

25.图1为依据本发明一实施例的多核心处理器电路的示意图。请参照图1,在本实施例中,多核心处理器电路100包括多个处理器核心110_1~110_n、程序存储器120、第一汇流排130、数据存储器140、第二汇流排150、控制电路160及时钟产生器170,其中程序存储器120用以储存至少一程序指令inst,并且数据存储器140用以储存至少一程序数据data。其中,n为二以上的正整数。

26.第一汇流排130,耦接于这些处理器核心110_1~110_n与程序存储器120之间,并且第二汇流排150,耦接于这些处理器核心110_1~110_n与数据存储器140之间。控制电路160耦接处理器核心110_1~110_n,以逐个使能这些处理器核心110_1~110_n,并且关闭其余的处理器核心110_1~110_n。接着,当处理器核心110_1~110_n的其中之一被使能后,被使能的处理器核心110_1~110_n可以正常运作以存取程序存储器120及数据存储器140。其中,使能的处理器核心110_1~110_n可通过第一汇流排130存取程序存储器120及/或通过第二汇流排150存取数据存储器140。

27.进一步来说,时钟产生器170用以产生操作时钟clk至控制电路160,并且控制电路160仅将操作时钟clk提供至被使能的处理器核心110_1~110_n,而其余的处理器核心110_1~110_n不会接收到操作时钟clk。在使能的处理器核心110_1~110_n的使能期间(亦即所分配的操作期间)结束后,控制电路160会将操作时钟clk提供至下一个被使能的处理器核心110_1~110_n。

28.在本发明实施例中,控制电路160包括计数器161及多个暂存器a~n,其中暂存器a~n个别与这些处理器核心110_1~110_n对应,用以决定处理器核心110_1~110_n个别的使能期间。换言之,暂存器a~n中所储存的值决定处理器核心110_1~110_n个别的使能期间。并且,处理器核心110_1~110_n个别的使能期间ta、tb决定于各个处理器核心110_1~110_n的性质,亦即相同性质的处理器核心110_1~110_n可具有相同时间长度的使能期间,并且不同性质的处理器核心110_1~110_n可具有不同时间长度的使能期间。此外,具有简单处理任务的处理器核心110_1~110_n可具有较短时间的使能期间,并且具有复杂处理任务的处理器核心110_1~110_n可具有较长时间的使能期间。亦即,处理器核心110_1~110_n的使能期间可取决于任务复杂性和每个处理器核心110_1~110_n的计算能力。

29.计数器161用以计数这些处理器核心110_1~110_n的使能期间。进一步来说,计数器161依据操作时钟clk进行计数,在控制电路160改变操作时钟clk的提供至的处理器核心110_1~110_n时重置,且接着依据操作时钟clk进行计数,并且在计数器161的值达到对应的暂存器a~n中所储存的值时,将操作时钟clk提供至下一处理器核心110_1~110_n。

30.图2为依据本发明一实施例的多核心处理器电路的时序示意图。请参照图1及图2,在本实施例中,是以两个处理器核心110_1及110_2为例,并且处理器核心110_1的使能期间为ta(对应暂存器a),处理器核心110_2的使能期间为tb(对应暂存器b)。在此,一个总体循环期间可以为ta tb。并且,假设处理器核心110_1具有简单的处理任务,因此具有较短时间的使能期间ta,并且假设处理器核心110_2具有复杂的处理任务,因此具有较长时间的使能期间tb。

31.在使能期间ta开始时,计数器161被重置,且接着进行计数。当计数器161的值等于暂存器a所储存的值时,代表使能期间ta到达结束时间点,此时控制电路160会将操作时钟clk提供至处理器核心110_2。在使能期间ta,处理器核心110_1依序执行读取程序存储器120的操作循环pm及读取数据存储器140的操作循环dm,其中操作循环pm及dm的数量为用以说明,本发明实施例不以此为限。

32.接着,在使能期间tb开始时,计数器161会再被重置,且接着进行计数。当计数器161的值等于暂存器b所储存的值时,代表使能期间tb到达结束时间点,此时控制电路160会将操作时钟clk再提供至处理器核心110_1。在使能期间tb,处理器核心110_2同样会依序执行读取程序存储器120的操作循环pm及读取数据存储器140的操作循环dm。

33.在以两个处理器核心110_1及110_2的实施例中,处理器核心110_1对应的暂存器a可以设置为1200,处理器核心110_2对应的暂存器b可以设置为1200,亦即处理器核心110_1及110_2的使能期间的比率可以为1:1。另一实施中,处理器核心110_1对应的暂存器a可以设置为2400,处理器核心110_2对应的暂存器b可以设置为2400,亦即处理器核心110_1及110_2的使能期间的比率仍可以为1:1。在本发明实施例中,取决于任务的复杂性和每个处理器核心的计算能力,即使处理器核心的使能期间的比率相同,也可以设置得更灵活。

34.综上所述,本发明实施例的多核心处理器电路,其中多个处理器核心不会同时运行,因此这些处理器核心与程序存储器或数据存储器的存取永远不会发生冲突。因此,不需要额外的仲裁程序设计来协调程序存储器和数据存储器。通过设定暂存器内所储存的值,多核心处理器电路于时间共享上的另一个优点是时间共享的灵活性。

35.虽然本发明已以实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中相关技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与润饰,故本发明的保护范围当视前述的权利要求书范围所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。