1.本实用新型涉及安防设备扩展领域,特别是多接口、输入输出可配置韦根通信扩展板。

背景技术:

2.现有技术中,门禁控制器的输入接口数量通常是确定不变的,增加设备输入接口,则需要修改控制器硬件。随着应用的增加,门禁控制系统上接入的设备会越来越多,如人脸识别设备,二维码识别设备等,门禁控制器的输入接口数量限制会无法满足添加更多设备的需求。

3.随着技术的发展,现有的门禁设备产品中,设备的通信接口已不再是单一的韦根接口,越来越多的设备偏向于使用可交互双向通讯、传输速率高的接口,如rs485串行总线接口、rs232串行接口等,而不同类型接口的设备之间无法直接连接通讯,限制了门禁系统的扩展性、兼容性和灵活性。

4.实际应用中,安全等级较高的场合会存在双重验证的访问控制方式,例如指纹 rfid卡、人脸 rfid卡等,需对两种验证设备输出的韦根数据进行比较,数据相同时才会通过验证。现有的大多数门禁控制器的韦根接口之间是相互独立的,无法实现上述功能。

技术实现要素:

5.为了解决上述现有技术中存在的问题,本实用新型的目的是提供一种多接口、输入输出可配置韦根通信扩展板。它实现了门禁控制器接口的灵活扩展,大大提高了门禁控制器的扩展性和兼容性,能够在现有系统的基础上尽可能小的改动,快速扩展更多的设备。

6.为了达到上述发明目的,本实用新型的技术方案以如下方式实现:

7.多接口、输入输出可配置韦根通信扩展板,它由韦根输入/输出接口单元一、韦根输入/输出接口单元二、韦根输入接口单元一、韦根输入接口单元二、韦根输出接口单元、串行总线rs485接口单元、串行总线rs232接口单元、电源接口单元及微处理器单元组成。其结构特点是;

8.所述韦根输入/输出接口单元一和韦根输入/输出接口单元均由连接端子、输入缓冲电路、输出缓冲电路和切换开关电路组成。所述韦根输入接口单元一、韦根输入接口单元二和韦根输出接口单元均由连接端子和输出缓冲电路组成。所述串行总线rs485接口单元由连接器和rs485转换电路组成。所述串行总线rs232接口单元由连接器和rs232转换电路组成。所述电源接口单元由连接器、 5v电压调整器、和3.3v电压调整器组成,输入电源经过电压调整器转换为 5v和 3.3v电压后为扩展板上各部分电路工作提供电源。所述微处理器单元由处理器芯片、晶振电路和复位电路组成,对各接口单元输入的数据进行处理并根据需要将处理结果进行输出。所述韦根输入/输出接口单元一、韦根输入/输出接口单元二、韦根输入接口单元一、韦根输入接口单元二、韦根输出接口单元、串行总线rs485接口单元、串行总线rs232接口单元和电源接口单元分别与微处理器单元进行连接。

9.所述韦根输入/输出接口单元一和韦根输入/输出接口单元二配置为韦根输入接口接收外部设备传输过来的韦根数据,接收到的韦根数据经过韦根输出接口单元、串行总线rs485接口单元或者串行总线rs232接口单元中的任意一个接口单元输出。韦根输入/输出接口单元一和韦根输入/输出接口单元二或者配置为韦根输出接口,将收到的韦根数据进行输出。

10.所述韦根输入接口单元一和韦根输入接口单元二作为韦根输入接口接收外部设备传输来的韦根数据,接收到的韦根数据经过韦根输出接口单元、串行总线rs485接口单元或者串行总线rs232接口单元中的任意一个接口单元输出。

11.所述韦根输出接口单元作为韦根输出接口,将从韦根输入/输出接口单元一、韦根输入/输出接口单元二、及韦根输入接口单元一、韦根输入接口单元二、串行总线rs485接口单元和串行总线rs232接口单元输入的韦根数据进行输出。

12.在上述韦根扩展板中,所述韦根输入/输出接口单元一和韦根输入/输出接口单元二配置为韦根输入时,以及韦根输入接口单元一和韦根输入接口单元二四个接口单元中的任意两个接口单元配置加入比较组功能,在5s内比较组内的两个接口单元输入的韦根数据相同时,将接收到的韦根数据通过所配置的输出接口单元进行输出。

13.在上述韦根扩展板中,所述微处理器单元通过串行总线rs485接口单元或串行总线rs232接口单元实现处理器程序的远程或者本地在线升级。

14.在上述韦根扩展板中,所述韦根输入/输出接口单元一和韦根输入/输出接口单元二通过配置工作模式进行输入或者输出的切换。

15.本实用新型由于采用了上述结构,韦根输入信号线也可以当做韦根输出信号线使用,同时本实用新型的韦根信号还可以和485/232信号进行相互转换。同现有技术相比,本实用新型实现了门禁控制器接口的灵活扩展,大大提高了门禁控制器的扩展性和兼容性,使用起来特别方便,而且能够在现有门禁系统的基础上尽可能小的改动,快速扩展更多的设备。

16.下面结合附图和具体实施方式对本实用新型做进一步说明。

附图说明

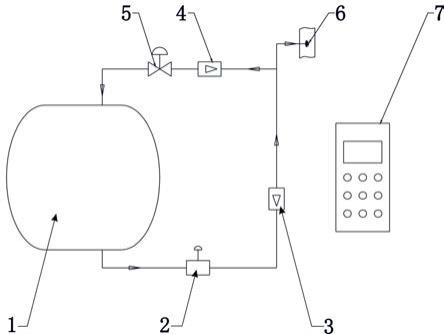

17.图1为本实用新型的电路连接示意图;

18.图2为本实用新型实施例中韦根输入/输出接口单元一和韦根输入/输出接口单元二的电路示意图;

19.图3为本实用新型实施例中韦根输入接口单元一和韦根输入接口单元二的电路示意图;

20.图4为本实用新型实施例中韦根输出接口单元的电路示意图;

21.图5为本实用新型实施例中串行总线rs485接口单元的电路示意图;

22.图6为本实用新型实施例中串行总线rs232接口单元的电路示意图;

23.图7为本实用新型实施例中电源接口单元的电路示意图;

24.图8为本实用新型实施例中微处理器单元的电路示意图。

具体实施方式

25.参看图1,本实用新型多接口、输入输出可配置韦根通信扩展板,它由韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、韦根输入接口单元一3、韦根输入接口单元二4、韦根输出接口单元5、串行总线rs485接口单元6、串行总线rs232接口单元7、电源接口单元8及微处理器单元9组成。

26.参看图2,韦根输入/输出接口单元一1和韦根输入/输出接口单元二2均由连接端子、输入缓冲电路、输出缓冲电路和切换开关电路组成。韦根输入/输出接口单元一1和韦根输入/输出接口单元二2共用一个6pin连接端子,各由d0、d1和gnd三根数据线组成,其中d0、d1均有对应的输入缓冲电路及输出缓冲电路和大功率tvs防护器件,连接端子的一端连接到输入缓冲电路的输入端及输出缓冲电路的输出端。

27.上述输入缓冲电路由差动比较器、异或门及外围器件组成,输入阻抗高,所需驱动电流小。当d0或者d1上输入的电平高于 2.5v时,对应的差动比较器输出高电平,表示输出逻辑“1”,当d0或者d1上输入的电平低于 2.5v时,对应的差动比较器输出低电平,表示输出逻辑“0”。两个差动比较器的输出连接到异或门的输入端,并进行异或运算,异或门的输出和d0对应差动比较器的输出作为输出缓冲电路的输出端。输入缓冲电路的输入端与连接端子及输出缓冲电路的输出端连接,输出端与切换开关电路的常闭端连接。输入缓冲电路能够很好对输入信号进行滤波、波形矫正及提高接口的电平兼容性。

28.上述输出缓冲电路由npn三极管及外围电路组成,输出阻抗小,带负载能力强;d0、d1分别连接到三极管的集电极。当d0或d1对应npn三极管基极有高电平输入时,三极管导通,d0或者d1输出低电平。当d0或者d1对应npn三极管基极有低电平输入时,三极管截止,d0或者d1输出高电平。输出缓冲电路输入端与切换开关电路的常开端连接,输出端与连接端子及输入缓冲电路的输入端连接。

29.上述切换开关电路由4通道单刀双掷spdt模拟开关芯片组成。通道1及通道2为同一控制组,公共端及控制端连接到所述的微处理器单元9,常闭端连接到韦根输入/输出接口单元一1的d0、d1对应输入缓冲电路,常开端连接到韦根输入/输出接口单元一1的d0、d1对应输出缓冲电路,用于切换韦根输入/输出接口单元一1对应的输入缓冲电路或输出缓冲电路。通道3及通道4为同一控制组,公共端及控制端连接到所述的微处理器单元9,常闭端连接到韦根输入/输出接口单元二2的d0、d1对应输入缓冲电路,常开端连接到韦根输入/输出接口单元二2的d0、d1对应输出缓冲电路,用于切换韦根输入/输出接口单元二2对应的输入缓冲电路或输出缓冲电路。

30.韦根输入/输出接口单元一1、韦根输入/输出接口单元二2既可作为韦根输入接口接收外部设备传输过来的韦根信号,自动兼容wg26/wg34/wg66/wg82韦根协议,接收到的韦根数据可经过所述的韦根输出接口单元5、串行总线rs485接口单元6或串行总线rs232接口单元7中的任意一个接口单元输出给其他设备。也可作为韦根输出接口输出韦根数据到其他设备,可配置输出wg26/wg34/wg66/wg82韦根协议格式数据。可对韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、及韦根输入接口单元一3、韦根输入接口单元二4的数据、及串行总线rs485接口单元6、串行总线rs232接口单元7输入的韦根数据进行输出。输入/输出可通过配置工作模式进行切换实现韦根接口扩展及输入输出接口数量的灵活配置。

31.参看3,韦根输入接口单元一3和韦根输入接口单元二4由连接端子和输出缓冲电路组成。韦根输入接口单元一3和韦根输入接口单元二4共用一个6pin连接端子,各由d0、d1和gnd三根数据线组成,其中d0、d1均有对应的输入缓冲电路及大功率tvs防护器件,连接端子的一端连接到输入缓冲电路的输入端。

32.上述输入缓冲电路由差动比较器、异或门及外围器件组成,输入阻抗高,所需驱动电流小。当d0或者d1上输入的电平高于 2.5v时,对应的差动比较器输出高电平,表示输出逻辑“1”,当d0或者d1上输入的电平低于 2.5v时,对应的差动比较器输出低电平,表示输出逻辑“0”。两个差动比较器的输出连接到异或门的输入端,并进行异或运算,异或门的输出和d0对应差动比较器的输出作为输出缓冲电路的输出端。输入缓冲电路能够很好对输入信号进行滤波、波形矫正及提高接口的电平兼容性,输入缓冲电路的输出连接到微处理器单元9。

33.韦根输入接口单元一3和韦根输入接口单元二4仅作为韦根输入接口接收外部设备传输过来的韦根数据,自动兼容wg26/wg34/wg66/wg82韦根协议,接收到的韦根数据可经过所述的韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、韦根输出接口单元5、串行总线rs485接口单元6或串行总线rs232接口单元7中的任意一个接口单元输出给其他设备,可实现灵活的接口扩展组合。

34.参看图4,韦根输出接口单元5由连接端子和输出缓冲电路组成, 与微处理器单元9进行连接。韦根输出接口单元5与电源接口单元8共用一个6pin连接端子,韦根输出接口单元5由d0、d1和gnd三根数据线组成,其中d0、d1均有对应的输出缓冲电路及大功率tvs防护器件,连接端子的一端连接到输出缓冲电路的输出端。

35.上述输出缓冲电路由npn三极管及外围器件组成,输出阻抗小,带负载能力强;d0、d1分别连接到三极管的集电极。当d0或d1对应npn三极管基极有高电平输入时,三极管导通,d0或者d1输出低电平;当d0或者d1对应npn三极管基极有低电平输入时,三极管截止,d0或者d1输出高电平。上述输出缓冲电路输入端与微处理器单元9连接,输出端与连接端子连接。

36.韦根输出接口单元5仅作为韦根输出接口输出韦根信号到其他设备,可配置输出wg26/wg34/wg66/wg82韦根协议格式数据,可对韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、及韦根输入接口单元一3、韦根输入接口单元二4的数据、及串行总线rs485接口单元6、串行总线rs232接口单元7输入的韦根数据进行输出,实现韦根接口的扩展。

37.所述的韦根输入/输出接口单元一1、韦根输入/输出接口单元二2配置为韦根输入时,以及所述的或韦根输入接口单元一3、韦根输入接口单元二4中的任意两个接口单元可配置加入比较组功能,在5s内比较组内的两个接口单元输入的韦根数据相同时,才将接收到的韦根数据通过所配置的输出接口单元进行输出。

38.参看图5,串行总线rs485接口单元6由连接端子、rs485转换电路组成,与微处理器单元9进行连接。串行总线rs485接口单元6与串行总线rs232接口单元7共用一个6pin连接端子,串行总线rs485接口单元6由a 、b

‑

、gnd三根数据线组成。

39.上述rs485转换电路由光耦隔离电路及rs485收发电路组成,光耦隔离电路由三个光耦器件及外围器件组成,实现微处理器单元9与rs485收发电路之间的电信号的隔离及电压转换的功能。rs485收发电路由专用的rs485收发芯片及外围器件组成,实现将光耦隔离

电路传输过来的电平信号转换为rs

‑

485协议标准的差分电平信号。

40.串行总线rs485接口单元6为半双工串行通讯接口,可与其他具备rs485标准接口的设备进行双向通讯,实现韦根接口到rs485接口扩展,通讯速率最高支持115200bps。

41.参看图6,串行总线rs232接口单元7由连接端子、rs232转换电路组成,与微处理器单元9进行连接。串行总线rs232接口单元7由tx、rx、gnd三根数据线组成。

42.上述rs232转换电路由专用的rs232收发芯片及外围器件组成,实现将微处理器单元9传输过来的电平信号转换为rs

‑

232协议标准的正负电平信号。

43.串行总线rs232接口单元7为全双工串行通讯接口,可与其他具备rs232标准接口的设备进行双向通讯,实现韦根接口到rs232接口的扩展,通讯速率最高支持115200bps。

44.串行总线rs485接口单元6和串行总线rs232接口单元7可通过上位机软件或特定格式的指令对本实用新型进行模式配置、查询及软件升级。同时,可将韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、及韦根输入接口单元一3、韦根输入接口单元二4输入的韦根数据通过上述接口单元进行输出。上述接口输入的韦根数据可通过韦根输出接口单元5进行输出,从而实现韦根接口的灵活扩展。

45.参看图7,所述电源接口单元8由连接器、 5v电压调整器、 3.3v电压调整器组成。电源接口单元8与韦根输出接口单元5共用一个6pin连接端子,电源接口单元8包括 12v、 5v、gnd三根电源线。

46.电源接口单元8为韦根扩展板板上各部分电路工作提供电源。当 12v电压接入时,经过 5v电压调整器转换为 5v电压后为 5v电压的工作系统进行供电。同时, 5v电压再经过 3.3v电压调整器转换 3.3v电压后为 3.3v电压工作的系统进行供电。当 5v电压接入时,直接为 5v电压的工作系统进行供电, 5v电压调整器不工作。同时, 5v电压再经过低压差线性调整器转换 3.3v电压后,为 3.3v电压工作的系统进行供电。

47.参看图8,微处理器单元9由处理器芯片、晶振电路、复位电路组成。

48.处理器芯片为cortex

‑

m3架构的arm高性能芯片,是整个韦根扩展板的数据处理中心。晶振电路由8m晶振及其外围器件组成,负责给处理器芯片提供运行时钟。复位电路为rc电路组成,为处理芯片提供上电复位电平。

49.微处理器单元9根据设置的模式,负责对韦根输入数据、rs485输入数据、rs232输入数据进行运算处理,并根据需要将处理结果进行输出。微处理器单元9通过串行总线rs485接口单元6或串行总线rs232接口单元7可以实现处理器程序的远程或本地升级。

50.本实用新型的创新点在于:

51.1、韦根输入信号线可以当韦根输出信号使用。现有技术中的韦根电路是把外接输入的韦根信号修整波形,然后传输给处理器处理获得结果。

52.本实用新型韦根扩展板的不同在于把韦根的输入电路和输出电路整合在了一起。韦根输入/输出接口单元一1、韦根输入/输出接口单元二2中连接端子上的输出cn1端口中的wg2_cd0/wg2_cd1,wg1_cd0/wg1_cd1四根信号线既可以当输入,又可以当输出信号线使用,如图2所示。当电路配置为输入模式的时候,首先mcu会控制管脚wg2_sel/wg1_sel来让com端连接到nc端,断开与no端的连接。然后信号从cn1端子输入,到达韦根缓冲整形电路。然后通过一个异或电路输出一个中断信号到nc2,这时nc2和com2导通,所以触发mcu通过nc1来读取韦根的输入信号。相反当韦根信号输出时,mcu通过控制wg2_sel/wg1_sel来让

com端连接到no端,断开与nc端的连接。然后韦根信号通过com端传到no端,no端的w2_od0/w2_od1是通过三极管和电阻连接到韦根信号的输入,从而实现一个信号端完成韦根信号的输入输出功能。

53.2、本实用新型中韦根信号和485/232可以相互转换。参看图5,mcu通过txd3/rxd3/rs485_ctrl(485芯片控制信号)来和485芯片通信工作。中间经过了光耦隔离,减少外部环境对核心电路的影响。光耦还有个作用就是把3.3v信号转换成5v信号,有电平转换器的功能。 cn6是485和232的接口端子。参看图6,左边是232和485的通信指示灯电路,只要txd1/rxd1上有低电平的信号经过,那么tx1/rx1两个发光二极管就会随着信号频率闪烁。u6是232转换芯片,主要是把mcu的串口信号txd1/rxd1转换成 232信号(rs232tx/rs232rx)。

54.上述的485/232/韦根信号都是可以通过mcu来相互转换的。比如485端子上输入了一个刷卡信号,经过485模块进入mcu,然后经过软件格式转换就可以从韦根端口输出韦根格式的刷卡信号。232同理。

55.本实用新型韦根扩展板使用时,韦根输入/输出接口单元一1配置为

‘

输入’模式时,对应的输入缓冲电路使能,输出缓冲电路禁止,即切换开关常闭端与公共端连通。当韦根数据传输进来时,经过输入缓冲电路及切换开关电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过韦根输出接口单元5和其他韦根输出接口单元进行输出,实现韦根输入接口扩展。

56.本实用新型中韦根输入/输出接口单元一1配置为

‘

转发到rs485’模式时,对应的输入缓冲电路使能,输出缓冲电路禁止,即切换开关常闭端与公共端连通。当韦根数据传输进来时,经过输入缓冲电路及切换开关电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过串行总线rs485接口单元6按预定的格式进行输出,实现韦根输入接口扩展。

57.本实用新型中韦根输入/输出接口单元一1配置为

‘

转发到rs232’模式时,对应的输入缓冲电路使能,输出缓冲电路禁止,即切换开关常闭端与公共端连通。当韦根数据传输进来时,经过输入缓冲电路及切换开关电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过串行总线rs232接口单元7按预定的格式进行输出,实现韦根输入接口扩展。

58.本实用新型中韦根输入/输出接口单元一1配置为

‘

输出’模式时,对应的输出缓冲电路使能,输入缓冲电路禁止,即切换开关常开端与公共端连通。当配置为

‘

输入’模式的韦根接口单元接收到韦根数据时,或当串行总线rs485接口单元6及串行总线rs232接口单元7接收到卡号数据时,微处理器单元9会将所接受到的韦根数据或卡号数据从此接口单元输出,实现韦根输出接口扩展。

59.本实用新型中韦根输入/输出接口单元二2配置为

‘

输入’模式时,对应的输入缓冲电路使能,输出缓冲电路禁止,即切换开关常闭端与公共端连通。当韦根数据传输进来时,经过输入缓冲电路及切换开关电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过韦根输出接口单元5和其他韦根输出接口单元进行输出,实现韦根输入接口扩展。

60.本实用新型中韦根输入/输出接口单元二2配置为

‘

转发到rs485’模式时,对应的输入缓冲电路使能,输出缓冲电路禁止,即切换开关常闭端与公共端连通。当韦根数据传输

进来时,经过输入缓冲电路及切换开关电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过串行总线rs485接口单元6按预定的格式进行输出,实现韦根输入接口扩展。

61.本实用新型中韦根输入/输出接口单元二2配置为

‘

转发到rs232’模式时,对应的输入缓冲电路使能,输出缓冲电路禁止,即切换开关常闭端与公共端连通。当韦根数据传输进来时,经过输入缓冲电路及切换开关电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过串行总线rs232接口单元7按预定的格式进行输出实现韦根输入接口扩展。

62.本实用新型中韦根输入/输出接口单元二2配置为

‘

输出’模式时,对应的输出缓冲电路使能,输入缓冲电路禁止,即切换开关常开端与公共端连通。当配置为

‘

输入’模式的韦根接口单元接收到韦根数据时,或当串行总线rs485接口单元6及串行总线rs232接口单元7接收到韦根数据时,微处理器单元9会将所接受到的韦根数据从此接口单元输出,实现韦根输出接口扩展。

63.本实用新型中韦根输入接口单元一3配置为

‘

输入’模式时,当韦根数据传输进来时,经过输入缓冲电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过韦根输出接口单元5和其他韦根输出接口单元进行输出,实现韦根输入接口扩展。

64.本实用新型中韦根输入接口单元一3配置为

‘

转发到rs485’模式时,当韦根数据传输进来时,经过输入缓冲电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过串行总线rs485接口单元6按预定的格式进行输出,实现韦根输入接口扩展。

65.本实用新型中韦根输入接口单元一3配置为

‘

转发到rs232’模式时,当韦根数据传输进来时,经过输入缓冲电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过串行总线rs232接口单元7按预定的格式进行输出,实现韦根输入接口扩展。

66.本实用新型中韦根输入接口单元二4配置为

‘

输入’模式时,当韦根数据传输进来时,经过输入缓冲电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过韦根输出接口单元5和其他韦根输出接口单元进行输出,实现韦根输入接口扩展。

67.本实用新型中韦根输入接口单元二4配置为

‘

转发到rs485’模式时,当韦根数据传输进来时,经过输入缓冲电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过串行总线rs485接口单元6按预定的格式进行输出,实现韦根输入接口扩展。

68.本实用新型中韦根输入接口单元二4配置为

‘

转发到rs232’模式时,当韦根数据传输进来时,经过输入缓冲电路后输入到微处理器单元9,微处理器单元9会将所接收到的韦根数据通过串行总线rs232接口单元7按预定的格式进行输出,实现韦根输入接口扩展。

69.本实用新型中韦根输出接口单元5可配置韦根输出数据格式为wg26/wg34/wg66/wg82四种韦根数据格式中的任意一种。微处理器单元9根据配置的格式,将来自韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、及韦根输入接口单元一3、韦根输入接口单元二4的数据、及串行总线rs485接口单元6、串行总线rs232接口单元7的韦根数据进行输出,实现韦根输出接口扩展。

70.本实用新型中的串行总线rs485接口单元6可配置波特率为9600bps/19200pbs/38400bps/57600bps/115200bps五种波特率中的任意一种,微处理器单元9根据配置的波特率按约定的数据格式与其他设备进行通讯。

71.当微处理器单元9通过所述的串行总线rs485接口单元6接收到符合参数设置格式的数据时,微处理器单元9会根据所接收到的参数对韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、韦根输入接口单元一3、韦根输入接口单元二4、韦根输出接口单元5、串行总线rs485接口单元6、串行总线rs232接口单元7进行参数设置,进而实现接口单元功能的在线灵活配置。

72.当微处理器单元9通过所述的串行总线rs485接口单元6接收到符合参数查询格式的数据时,微处理器单元9会将韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、韦根输入接口单元一3、韦根输入接口单元二4、韦根输出接口单元5、串行总线rs485接口单元6、串行总线rs232接口单元7共七个接口单元的参数数据通过串行总线rs485接口单元6进行回复输出,进而实现接口单元各项参数的获取。

73.当微处理器单元9通过所述的串行总线rs485接口单元6接收到符合iap升级格式的数据时,微处理器单元9会进入程序升级模式并开始接收升级数据包,数据包接收完成后开始升级,进而实现本实用新型程序的在线远程升级或本地升级。

74.当微处理器单元9通过所述的串行总线rs485接口单元6接收到符合韦根协议格式的数据时,微处理器单元9会将所接受到的数据通过韦根输出接口单元5进行输出,从而实现串行总线rs485接口到韦根接口的扩展。

75.本实用新型中串行总线rs232接口单元7可配置波特率为9600bps/19200pbs/38400bps/57600bps/115200bps五种波特率中的任意一种,微处理器单元9根据配置的波特率按约定的数据格式与其他设备进行通讯。

76.当微处理器单元9通过所述的串行总线rs232接口单元7接收到符合参数设置格式的数据时,微处理器单元9会根据所接收到的参数对韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、韦根输入接口单元一3、韦根输入接口单元二4、韦根输出接口单元5、串行总线rs485接口单元6、串行总线rs232接口单元7进行参数设置,进而实现接口单元功能的在线灵活配置。

77.当微处理器单元9通过所述的串行总线rs232接口单元7接收到符合参数查询格式的数据时,微处理器单元9会将韦根输入/输出接口单元一1、韦根输入/输出接口单元二2、韦根输入接口单元一3、韦根输入接口单元二4、韦根输出接口单元5、串行总线rs485接口单元6、串行总线rs232接口单元7共七个接口单元的参数数据通过串行总线rs485接口单元6进行回复输出,进而实现接口单元各项参数的获取。

78.当微处理器单元9通过所述的串行总线rs232接口单元7接收到符合iap升级格式的数据时,微处理器单元9会进入程序升级模式并开始接收升级数据包,数据包接收完成后开始升级,进而实现本实用新型程序的在线远程升级或本地升级。

79.当微处理器单元9通过所述的串行总线rs232接口单元7接收到韦根数据时,微处理器单元9会将所接受到的数据通过韦根输出接口单元5进行转发输出,从而实现串行总线rs232接口到韦根接口的扩展。

80.以上所述仅为本实用新型实施例的较佳实践,并不用以限制本实用新型技术,凡在本实用新型的精神和原则之内,进行的各种改动、同等替换、变型等,均应包含在本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。