1.本实用新型属于电子技术和磁耦合隔离领域,具体涉及一种应用于磁耦合隔离的双触发器解码电路。

背景技术:

2.电子产品的安全性和稳定性是电源技术在设计需要考虑的重要性能指标。考虑到电子产品工作条件和环境的不确定性,常常会在诸如高压条件下、特高压等极端工作条件和潮湿、高温等恶劣工作环境下使用,例如在工业应用中,igbt与其驱动电路是典型的高压工作电路与低压逻辑控制电路,由于存在极大的压差,因此需要引入隔离来保证控制电路的安全。

3.多年来,工业、医疗和其他隔离系统的设计人员实现安全隔离的手段有限,唯一合理的选择是光耦合器。其优点是信号单向传输、输入端和输出端完全实现了电气隔离,输出信号对输入端无影响,抗干扰能力强,工作稳定,无触点,使用寿命长,传输效率高。但随着工业的发展,光耦也因体积大、功耗高、传输速度慢等因素,制约着光耦在更高的场合中应用。

4.于是,具有体积小、应用方便、可靠性高、寿命长、功耗低等诸多优点的磁耦合器突出重围,成为现阶段各个行业隔离应用的新贵。一般的磁耦合隔离电路只适合于传输高频信号,对于低频或直流信号则无能为力。为了实现磁耦合隔离电路传输低频信号的功能,用一串窄脉冲代表数字信号的状态改变,以窄脉冲的磁隔离传输代替低频数字信号的磁隔离传输,以上电复位电路确定磁隔离传输电路的初始状态,在确定的初始状态和信号状态变化脉冲的共同作用下,在磁隔离电路的输出端完整恢复需要传输的数字信号,从而实现低频或直流信号的磁耦隔离传输。

技术实现要素:

5.本实用新型提供的一种应用于磁耦合隔离的双触发器解码电路实现了将编码输出信号与单稳态电路dm处理后ff信号重新相与,不仅实现了解码的作用,同时也保证了信号传输的安全性与准确性。

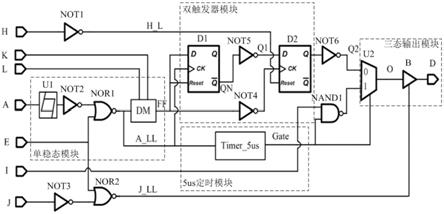

6.为了达到上述发明目的,本实用新型采用的技术方案为:一种应用于磁耦合隔离的双触发器解码电路,包括单稳态模块、双触发器模块、5us定时模块和三态输出模块;

7.所述单稳态模块分别与双触发器模块、5us定时模块和三态输出模块连接,所述三态输出模块分别与双触发器模块和5us定时模块连接。

8.进一步地,所述单稳态模块包括施密特整形器u1、非门not1、二输入或非门nor1和单稳态电路dm;

9.所述施密特整形器u1的输入端作为a端,其输出端通过非门not1与二输入或非门nor1的第一输入端连接;所述二输入或非门nor1的第二输入端作为e端,其与二输入或非门nor2的第一输入端连接;所述二输入或非门nor1的输出端分别与5us定时模块的输入端、单

稳态电路dm的输入端和双触发器模块中触发器d1的ck引脚连接;所述单稳态电路dm上设置有偏置电压端,所述偏置电压端包括l端和k端;所述二输入或非门nor2的第二输入端与非门not3的输出端连接,所述非门not3的输入端作为j端。

10.进一步地,所述双触发器模块包括触发器d1和触发器d2;所述触发器d1的d引脚分别与其reset引脚、单稳态电路dm的输出端和非门not4的输入端连接,所述触发器d1的端通过非门not5与触发器d2的d引脚连接;所述触发器d2的ck引脚与非门not4的输入端连接,所述触发器d2的reset引脚与非门not1的输出端连接,所述非门not1的输入端作为h端;所述触发器d2的q引脚与非门not6的输入端连接。

11.进一步地,所述5us定时模块包括5us定时器timer_5us,所述5us定时器timer_5us的输入端与二输入或非门nor1的输出端连接,所述5us定时器timer_5us的输出端分别与三态输出模块中二选一数据选择器u2的信号控制端和二输入与非门nand1的第一输入端连接,所述二输入与非门nand1的第二输入端作为i引脚。

12.进一步地,所述三态输出模块包括二选一数据选择器u2和三态缓冲器b;

13.所述二选一数据选择器u2的第一输入端与非门not6的输出端连接,所述二选一数据选择器u2的第二输入端与二输入与非门nand1的输出端连接,所述二选一数据选择器u2的输出端与三态缓冲器b的输入端连接,所述三态缓冲器b的信号控制端与二输入或非门nor2的输出端连接,所述三态缓冲器b的输出端作为d端。

14.进一步地,所述a端为编码脉冲信号接收端,所述d端为解码输出端,所述j端为输出三态控制端,所述h端为触发器上电清零端,所述i端为芯片故障或者上电时输出的状态端,所述e端为单稳态模块的解码使能端。

15.本实用新型的有益效果为:

16.(1)本实用新型将编码输出信号与单稳态电路dm处理后ff信号重新相与,不仅实现了解码的作用,同时也保证了信号传输的安全性与准确性。

17.(2)本实用新型结构简单,成本较低,同时拥有较低的功耗,可广泛应用于磁耦合隔离器的解码。

18.(3)本实用新型采用的双触发器为边沿d触发器,由于只在时钟上升沿接收输入信号,极大程度上提高了解码电路的可靠性和抗干扰能力,且杜绝了空翻现象的发生。

附图说明

19.图1为本实用新型提出的一种应用于磁耦合隔离的双触发器解码电路图。

具体实施方式

20.下面对本实用新型的具体实施方式进行描述,以便于本技术领域的技术人员理解本实用新型,但应该清楚,本实用新型不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本实用新型的精神和范围内,这些变化是显而易见的,一切利用本实用新型构思的发明创造均在保护之列。

21.下面结合附图详细说明本实用新型的实施例。

22.如图1所示,一种应用于磁耦合隔离的双触发器解码电路,包括单稳态模块、双触发器模块、5us定时模块和三态输出模块;

23.所述单稳态模块分别与双触发器模块、5us定时模块和三态输出模块连接,所述三态输出模块分别与双触发器模块和5us定时模块连接。

24.所述单稳态模块包括施密特整形器u1、非门not1、二输入或非门nor1和单稳态电路dm;

25.所述施密特整形器u1的输入端作为a端,其输出端通过非门not1与二输入或非门nor1的第一输入端连接;所述二输入或非门nor1的第二输入端作为e端,其与二输入或非门nor2的第一输入端连接;所述二输入或非门nor1的输出端分别与5us定时模块的输入端、单稳态电路dm的输入端和双触发器模块中触发器d1的ck引脚连接;所述单稳态电路dm上设置有偏置电压端,所述偏置电压端包括l端和k端;所述二输入或非门nor2的第二输入端与非门not3的输出端连接,所述非门not3的输入端作为j端。

26.所述双触发器模块包括触发器d1和触发器d2;所述触发器d1的d引脚分别与其reset引脚、单稳态电路dm的输出端和非门not4的输入端连接,所述触发器d1的端通过非门not5与触发器d2的d引脚连接;所述触发器d2的ck引脚与非门not4的输入端连接,所述触发器d2的reset引脚与非门not1的输出端连接,所述非门not1的输入端作为h端;所述触发器d2的q引脚与非门not6的输入端连接。

27.所述5us定时模块包括5us定时器timer_5us,所述5us定时器timer_5us的输入端与二输入或非门nor1的输出端连接,所述5us定时器timer_5us的输出端分别与三态输出模块中二选一数据选择器u2的信号控制端和二输入与非门nand1的第一输入端连接,所述二输入与非门nand1的第二输入端作为i引脚。

28.所述三态输出模块包括二选一数据选择器u2和三态缓冲器b;

29.所述二选一数据选择器u2的第一输入端与非门not6的输出端连接,所述二选一数据选择器u2的第二输入端与二输入与非门nand1的输出端连接,所述二选一数据选择器u2的输出端与三态缓冲器b的输入端连接,所述三态缓冲器b的信号控制端与二输入或非门nor2的输出端连接,所述三态缓冲器b的输出端作为d端。

30.所述a端为编码脉冲信号接收端,所述d端为解码输出端,所述j端为输出三态控制端,所述h端为触发器上电清零端,所述i端为芯片故障或者上电时输出的状态端,所述e端为单稳态模块的解码使能端。

31.在本实施例中,a为编码脉冲信号接收端;d为解码输出;l和k为偏置电压,从基准镜像电流;j为输出三态控制端,芯片故障或者上电时,输出被锁定为三态;h为触发器上电清零端;i端设置在芯片故障或者上电时输出的状态,i为高电平,输出在锁定状态下为低电平,否则为高电平;e为解码部分的使能端,即当e为高电平

‘1’

时,其后接的两个或非门会被强制输出0,输入信号a将不能传输到芯片内部,此时芯片不工作处于待机状态,当e为低电平

‘0’

时有效。

32.通道解码部分可以分为:不可重复触发的单稳态电路dm、双触发器模块、5us定时模块以及三态输出模块buffer。

33.其中,不可重复触发的单稳态电路(dm)通过处理经施密特整形来的解码脉冲,产生一个固定宽度的控制信号ff,ff信号电平时间大约为8ns,在这个时间内的编码脉冲最多只有前面三个有效。两个相邻信号的跳变沿被编码之后的脉冲之间最小的间隔将超过8ns,配合这个原理,正常情况下很难在一个ff信号高电平期间接收到超过三个脉冲,从而保证

信号解码的正确性。如果三个以上的信号被接收到,可以肯定的是干扰信号,后面的将被忽略。

34.解码功能由双触发器模块完成,模块中的触发器采用时钟ck上升沿触发,复位rst在低电平时清除触发器,输出置位为

‘0’

。dm产生的控制脉冲ff信号作为触发器d1的数据d端和复位端rst,反相后作为后级触发器d2的时钟ck,后级触发器d2的数据d端是前级触发器d1的qn反相。解码功能利用了门电路的延迟,后级触发器d2的输出q即为解码信号。

35.考虑到电路发生故障,在解码部分还加入一个5us定时电路:timer_5us,该模块检测输入端a是否有收到编码脉冲,超过5us时间内没有收到脉冲,则认为发送电路故障,timer_5us模块将发出一个控制信号gate锁定输出,在锁定状态下输出电平可以通过i端口进行修调。

36.本技术设计隔离器作为数据传输应用会用到总线上,总线挂载有很多设备,如果设备输出与数据写入方向一致,那么当读出数据时,该设备的输出不能影响到当前总线的数据状态,故当总线没有选择该外设时需要其处于高阻态。数据总线与外设数据口之间使用三态缓冲器,所以在输出端也加入一个三态缓冲器buffer,即可以提供大的驱动能力,也能提供高阻态。

37.下面对双触发器部分进行详细说明。

38.a_ll为编码脉冲a信号经过施密特整形后的信号,不算延迟时间则a_ll和a信号相同,即左边的dff1的ck信号即为a信号。ff信号是dm产生的输出,首先为左边d1的输入和rst信号,并且反相后作为右边d2的ck信号。h_l端为置位端,由h信号反相后驱动,当h信号为高电平时,h_l为低电平,直接将q1置位为“0”,则o输出为低电平,以下研究h为低电平时的情况。

39.由以上可知,a_ll信号的输入为双脉冲加一脉冲的三脉冲形式,而ff端输入为固定宽度的两个脉冲信号,且ff信号的第一个脉冲上升沿落后于a_ll的第一个脉冲上升沿,这个延迟由dm模块内部逻辑电路产生。触发器是在时钟ck上升沿锁存数据,则a_ll信号作为ck信号,a_ll信号第一个脉冲的上升沿来的时候,ff信号还没有发生翻转,则d1的输出不变,qn仍旧保持为高电平;当a_ll信号的第二个脉冲的上升沿来的时候,ff信号已经发生反转,则qn发生翻转变化,输出为低电平,但由于触发器本身内部的延迟的作用,使qn的翻转比a_ll第二个上升沿要落后一个dff1内部的延迟时间。当触发器d1的rst信号即ff信号发生1到0的变化时,qn直接被置位为

‘1’

。再看ck的第三个脉冲,同理,因为ff比a_ll信号要落后,当a_ll的第三个信号来的时候,f还未发生变化,则qn输出没有发生翻转,一直为高电平。

40.再看右侧的触发器d2,通过上面的分析我们已经知道,ff作为d1的复位信号所以d1输出qn的上升沿和ff的下跳沿是完全对应的,但是qn信号滞后于ff信号,这个延迟由于触发器的门电路引起。同时ff信号经过反相器后作为右边d2的时钟ck,qn同样经过一个相同的反相器被作为d2的数据d输入端。所以当ck上升沿到来时,右侧触发器d2锁存入的信号为ck上跳的前一刻d端信号的状态。上面的分析可知,a_ll信号滞后于ff信号,所以左侧触发器被a_ll的第一个脉冲锁入低电平,在a_ll信号的第二个脉冲处被锁入高电平,被ff信号被复位。这样左侧触发器d1只有在a_ll信号第二个脉冲的时候才能输出高电平。右侧触发器d2只有在a_ll信号为两个脉冲,的时候才能被置位为高电平,一个脉冲的时候输出为

低电平。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。