1.本发明整体涉及电子器件,并且更具体地讲,涉及半导体、半导体结构以及形成半导体器件的方法。

背景技术:

2.过去,使用各种方法和结构来形成放大器电路。在一些配置中,放大器的输出信号具有远大于公共返回电压的值的低值,诸如例如大于接地值。这可能导致接收输出信号的负载电路的不正确操作。另外,输出信号的高值通常具有与输入电压的值类似的值。一些应用具有在不同电压下操作的负载。因此,不同的电压可导致负载的不正确操作。

3.因此,希望具有一种器件,该器件具有高值的输出信号,该高值为与输入信号的高值不同的值,和/或具有接近电压返回值的低值。

技术实现要素:

4.本技术的一个方面涉及一种输出电路,所述输出电路包括:电压跟随器晶体管,所述电压跟随器晶体管被配置为接收第一信号,所述第一信号表示从第一电压源形成的输入电压,所述电压跟随器晶体管被配置为从小于所述第一电压源的第二供电电压形成输出电压,并且将输出处的输出电流供应给负载;增益晶体管,所述增益晶体管被配置为响应于所述输出电压的增大而从所述输出吸收电流,所述增益晶体管具有控制电极;和参考电路,所述参考电路耦接到所述增益晶体管的所述控制电极并被配置为响应于所述输出电压的所述增大而增大供应给所述增益晶体管的所述控制电极的第一电压,所述参考电路具有传导参考电流的参考晶体管。

5.本技术的另一方面涉及一种形成转换器电路的方法,所述方法包括:耦接电压跟随器晶体管以从第一电路接收控制信号,所述第一电路在第一操作电压下操作,所述电压跟随器晶体管被配置为由小于所述第一操作电压的第二操作电压形成输出电压,其中所述输出电压表示所述控制信号并且是在输出处形成的,并且其中所述电压跟随器晶体管在所述第二操作电压下供应输出电流;以及将参考电路配置为控制输出晶体管以响应于所述输出电压的减小而从所述输出吸收电流。

6.本技术的又一方面涉及一种形成半导体器件的方法,所述方法包括:将所述半导体器件的放大器电路配置为在第一操作电压下操作并且形成以所述第一操作电压为参考的第一信号;将所述半导体器件的输出晶体管配置为在小于所述第一操作电压的第二操作电压下操作,所述输出晶体管被配置为由所述第二操作电压形成输出电压并且还形成通过所述输出晶体管的输出电流,其中所述输出电压是在输出处形成的并且表示所述第一信号;以及将参考电路配置为形成与所述输出电流基本上成比例的参考电流,所述参考电路被配置为控制第一晶体管以响应于所述参考电流的变化而从所述输出吸收电流。

附图说明

7.图1示意性地示出了根据本发明的各放大器电路的各部分的实施方案的三个示例;

8.图2示意性地示出了放大器电路的一部分的实施方案的示例,该放大器电路可以是根据本发明的图1的电路中的任一个的另选实施方案;

9.图3示意性地示出了转换器电路或输出电路的一部分的实施方案的示例,该转换器电路或输出电路可以是根据本发明的图1至图2的电路中的任何一个的另选实施方案;

10.图4示意性地示出了电路的一部分的实施方案,该电路可以是根据本发明的图3的电路的另选实施方案;

11.图5示意性地示出了电路的一部分的实施方案,该电路可以是根据本发明的图3或图4的电路的另选实施方案;并且

12.图6示出了根据本发明的包括图1至图4中至少一个的电路中的一些电路的半导体器件的放大平面图。

13.为使图示清晰且简明,图中的组件未必按比例绘制,一些组件可能为了进行示意性的说明而被夸大,而且除非另外规定,否则不同图中的相同参考标号指示相同的组件。此外,为使描述简单,可省略公知步骤和组件的描述和细节。如本文所用,载流组件或载流电极意指器件的载送通过器件的电流的组件,诸如mos晶体管的源极或漏极或者双极型晶体管的发射极或集电极或者二极管的阴极或阳极,而控制组件或控制电极意指器件的控制通过器件的电流的组件,诸如mos晶体管的栅极或者双极型晶体管的基极。另外,一个载流组件可载送沿一个方向通过器件的电流,诸如载送进入器件的电流,而第二载流组件可载送沿相反方向通过器件的电流,诸如载送离开器件的电流。尽管器件在本文中可以被描述为某些n沟道或p沟道器件或者某些n型或p型掺杂区,但本领域的普通技术人员将理解,根据本发明的互补器件也是可以的。本领域的普通技术人员理解,导电类型是指通过其发生传导的机制,诸如通过孔或电子传导,因此,导电类型不是指掺杂浓度而是指掺杂类型,诸如p型或n型。本领域的技术人员应当理解,本文所用的与电路操作相关的术语“在

…

期间”、“在

…

同时”和“当

…

时”并不确切地意指称某个动作在引发动作后立即发生,而是指在初始动作所引发的反应之间可能存在一些较小但合理的延迟,诸如各种传播延迟。另外,术语“在

…

同时”意指某个动作至少在引发动作持续过程中的一段时间内发生。词语“大概”或“基本上”的使用意指组件的值具有预期接近陈述值或位置的参数。然而,如本领域所熟知,始终存在妨碍值或位置确切地为陈述值或位置的微小差异。本领域公认的是,高达至少百分之十(10%)(并且对于包括半导体掺杂浓度的一些组件,高达百分之二十(20%))的偏差是与确切如所述的理想目标相差的合理偏差。在关于信号状态使用时,术语“生效”意指信号的有效状态,而术语“失效”意指信号的无效状态。信号的实际电压值或逻辑状态(诸如“1”或“0”)取决于使用的是正逻辑还是负逻辑。因此,如果使用的是正逻辑,则高电压或高逻辑可生效,如果使用的是负逻辑,则低电压或低逻辑可生效;而如果使用的是正逻辑,则低电压或低状态可失效,如果使用的是负逻辑,则高电压或高逻辑可失效。在本文中,使用正逻辑约定,但本领域的技术人员理解,也可以使用负逻辑约定。权利要求书和/或具体实施方式中的术语“第一”、“第二”、“第三”等(如用在组件名称的一部分中)用于区分在类似组件之间,并且不一定描述时间上、空间上、等级上或任何其他方式的顺序。应当理解,如此

使用的术语在适当情况下可互换,并且本文所述的实施方案能够以除本文所述或举例说明外的其他顺序来操作。提到“一个实施方案”,意味着结合该实施方案描述的特定的特征、结构或特性包括在本发明的至少一个实施方案中。因此,在本说明书通篇内的不同位置出现的短语“在一个实施方案中”,不一定都指同一个实施方案,但在某些情况下,有可能指同一个实施方案。此外,如本领域的普通技术人员所清楚的,在一个或多个实施方案中,具体特征、结构或特性可以任何合适的方式结合。

14.下文将适当举例说明并描述的实施方案可缺少本文未具体公开的任何组件,并且/或者可在缺少本文未具体公开的任何组件的情况下实施。

具体实施方式

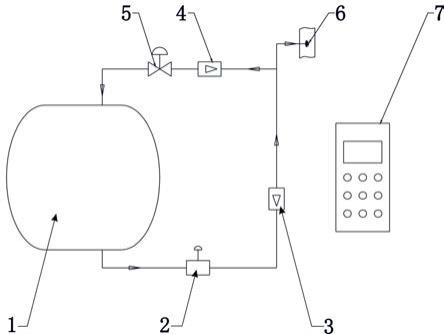

15.图1示意性地示出了包括转换器电路的各放大器电路的各部分的实施方案的三个示例,该转换器电路形成来自与放大器电路的其余部分不同的电源的输出信号。电路13示意性地示出了差分放大器的一部分的实施方案的示例,该差分放大器在输出28和29之间形成差分输出信号。电路13包括放大器电路14,该放大器电路放大差分输入信号并在第一操作电压(v1)19下操作。电路13还包括转换器电路22,该转换器电路在输入20上的第二操作电压(v2)下操作,并且在返回21上形成在电压v2和电路13的公共返回电压之间参考的差分输出信号。在一个实施方案中,第二操作电压小于第一操作电压。电路22包括两个单端输出电路或转换器电路24和25。电路24和25中的每一者接收来自放大器14的输出并形成在电压v2下操作的输出信号。电路24和25中的每一者向负载电路或负载31提供输出电压和输出电流27。

16.电路10示意性地示出了形成单端输出信号的差分放大器电路的一部分的实施方案的示例。电路10包括形成单端输出信号的放大器电路14。电路10还包括电路22的转换器电路24或另选地电路25。

17.电路12示意性地示出了差分放大器电路的一部分的实施方案的示例,该差分放大器电路接收差分输入信号并形成差分输出信号。电路12的输入可由两个不同的单端差分放大器11形成,每个单端差分放大器具有提供给差分放大器14的单端输出。放大器14包括电路22。电路10、12或13中的任一个可包括如图2所示的反馈回路或电路23。

18.图2示意性地示出了放大器电路26的一部分的实施方案的示例,该放大器电路可具有可以是电路10、12或13中的任一个的另选实施方案的实施方案。电路26具有差分输入放大器30,该差分输入放大器在不同输入之间接收输入信号并且在输出16和17之间提供差分输出。放大器30可以是图1的放大器14或11中的任一个的另选实施方案。电路26包括输出电路22。在一个实施方案中,放大器30可以是单端放大器。例如,反相输入可连接到基本上恒定的参考电压,如虚线所示。

19.本领域的技术人员应当理解,电路26可包括反馈回路,诸如例如电路23,使得电路26可为具有特定增益的运算放大器的一部分。

20.图3示意性地示出了转换器电路或输出电路33的一部分的实施方案的示例,该转换器电路或输出电路可具有可以是电路24或25(图1)或电路22的任一个的部分中的任一者或两者的另选实施方案的实施方案。电路33可以是一个输出电路,该输出电路可连接到差分放大器的输出以响应于在输入18上接收的输入电压(v

n

)而形成输出电压(v

o

)。例如,电路

33可为图1的电路24或25中的一者。电路33接收用于操作电路33的部分的第一操作电压(v1)。电路33还接收用于形成输出电压v

o

的第二操作电压(v2)。在一个实施方案中,电路33可被配置为使输出电压(v

o

)形成为具有不大于(或另选地小于)电压v2(因此小于输入19上的电压v1)的最大值。电路33的一个实施方案包括转换器电路,该转换器电路在输入20上的电压v2下操作,并且将输出电压(v

o

)形成为表示输入电压(v

n

),但处于比输入电压更低的电压。电路33还向负载诸如负载31供应输出电流27。在一个实施方案中,负载31可在输入20上的第二操作电压(v2)下操作,但在其他实施方案中可在其他电压下操作。例如,在大于第二操作电压(v2)但小于第一操作电压(v1)的电压下操作。

21.电路33包括形成电压v

o

的输出晶体管、增益电路和在输入19上接收的v1下操作的参考电路35。在一个实施方案中,输出晶体管可以是晶体管48,该晶体管被配置为电压跟随器以由v2形成电压v

o

。参考电路35的实施方案可被配置为形成表示通过晶体管48的电流51的参考电流46。一个实施方案可包括:电路33可被配置为控制增益电路以响应于参考电流或另选地响应于参考电流的变化而从输出28或者另选地从负载31吸收电流。在一个实施方案中,增益电路可响应于电压v

o

的增大值而从负载31吸收电流。一个实施方案可包括增益电路可为增益晶体管49。

22.电路35可具有可包括参考晶体管47、形成电流38的电流源37、晶体管44和形成电流53的第二电流源52的实施方案。如将在下文中进一步所见,电路33还可包括任选的响应电路58和任选的补偿电容器55。

23.源37和52被形成为使得在没有负载附接到输出28的情况下,相应电流38和53的值为:

24.i38=i46 i53,这使得i45=i53

25.其中:

26.i38=电流38的值,

27.i46=电流46的值,

28.i45=电流45的值,并且

29.i53=电流53的值。

30.假设电路33正在操作并且接收输入18上的输入电压(v

n

)以通过输出28向负载31供应v

o

和电流27。晶体管47接收v

n

或表示v

n

的信号,并且形成参考电流46以流过晶体管47。晶体管48还接收v

n

或表示v

n

的信号,并且形成流过晶体管48到达输出28的电流51作为电流27。在优选的实施方案中,晶体管48的有效区域被形成为通过值k与晶体管47的有效区域成比例,使得晶体管48的区域基本上为晶体管47的区域的k倍。因此,电流51通过值k与电流46成比例,例如为电流46的k倍。因此,电流46基本上是电流51的镜像。来自电流源37的电流38被划分,使得电流38的一部分作为电流46流过晶体管47,并且电流38的不同部分作为电流45流过晶体管44。电流45流到电流源52并影响晶体管49的栅极电压,因此影响v

gs

。随着电流45的值减小,供应给晶体管49的栅极的电压也减小,并且随着电流45增大,晶体管49的栅极电压也增大。当晶体管48正在供应电流27时,晶体管47正在传导电流46,其与电流27成比例,并且晶体管49正在传导电流50通过晶体管49,其将基本上等于电流46。

31.一个实施方案可以包括晶体管48以电压跟随器配置进行配置,因此,电压v

o

基本上由晶体管48的v

gs

偏移v

n

。由于晶体管48在v2下操作,所以v

o

的最大值不大于v2,v2小于v1,

因此小于v

n

的最大值。使用nmos晶体管作为晶体管48有利于形成v

o

以跟随v

n

。

32.如果v

n

相对于v

o

减小,或者另选地v

o

相对于v

n

增大,则晶体管47和48的v

gs

将减小,从而导致电流46和27减小。减小电流46会增大电流45,这也将增大晶体管49的v

gs

,使得电流50变得大于电流46。因此,除了电流46之外,晶体管49还将从负载31吸收电流。因此,电流27的至少一部分将流入电路33中,或者另选地流过晶体管49。如果v

n

相对于v

o

增大,或者另选地v

o

相对于v

n

减小,则晶体管47和48的v

gs

将增大,并且导致电流46和27增大。增大电流46会减小电流45,这使晶体管49的v

gs

减小,从而减小电流50。我省去了你在此所用的那些公式,因为我认为我们已经将这在正文中的几个地方进行解释了。如有必要,我们始终可以增添其他解释。

33.使用nmos晶体管作为晶体管49有利于电路33将v

o

的最低值形成为非常接近返回21上的返回电压。

34.电路33的实施方案可包括电路58。在一些情况下,电流27(因此电流46)的值可增大,使得电流45的值变得远小于电流53。在没有可选电路58的情况下,电流45可能足够小,使得晶体管49可停止传导。任选的电路58可被配置为在防止晶体管49在截止模式下操作的值处帮助形成晶体管49的v

gs

。如果晶体管49要截止,则晶体管49将花费有限的时间从截止恢复并开始传导电流50。因此,电路58可将晶体管49的栅极电压形成为基本上防止在截止模式下操作的值。在一个实施方案中,电路58可在不小于晶体管49的v

gs

阈值的值处形成晶体管49的v

gs

。v

gs

阈值是沟道开始形成并且晶体管49可以开始传导少量电流的值。

35.任选的电路58包括电流源36、晶体管60、晶体管61和以电流镜配置与晶体管60连接的晶体管62。晶体管62还设置施加到晶体管49的栅极的电压。施加到晶体管49的v

gs

电压可表示为:

36.vgs49=vgs61 vgs60

‑

vgs62

37.其中:

38.vgs49=施加到晶体管49的v

gs

,

39.vgs61=晶体管61的v

gs

,

40.vgs60=晶体管60的v

gs

,并且

41.vgs62=晶体管62的v

gs

。

42.晶体管61以二极管配置连接,该二极管配置使得晶体管60引导电流59通过晶体管60。晶体管60和62的电流镜配置形成电流63以流到电流源52,使得一些电流流入源52中。这保持晶体管49的v

gs

基本上不小于晶体管49的阈值v

gs

值。

43.电路33的实施方案还可包括连接在晶体管49的栅极和漏极之间的任选的频率补偿电容器55。将电容器55连接在栅极和漏极之间允许使用较小值的电容器来形成等效电容器,该等效电容器具有通过由晶体管49提供的增益而增大的值。

44.为了有助于为电路33提供上文所述的功能,源37的第一端子共同连接到输入19和源40的第一端子。源40的第二端子共同连接到输入20和晶体管48的漏极。晶体管48的源极共同连接到输出28、晶体管47的源极和晶体管49的漏极。晶体管49的源极共同连接到返回21和源52的第一端子。源52的第二端子共同连接到晶体管49的栅极和晶体管44的漏极。晶体管44的源极共同连接到源37的第二端子和晶体管47的漏极。晶体管47的栅极共同连接到晶体管48的栅极并接收输入电压(v

n

)。晶体管44的栅极连接到偏移电压电路43的第一端

子,该偏移电压电路具有连接到输入19的第二端子。

45.为了另外有助于为电路33提供上文所述的功能,任选的电路58可包括电流源36,该电流源具有连接到输入19的第一端子。电流源36的第二端子通常连接到晶体管60的漏极、晶体管60的栅极、晶体管62的栅极和晶体管62的漏极。晶体管62的源极连接到晶体管49的栅极。晶体管60的源极共同连接到晶体管61的漏极和晶体管61的栅极。晶体管61的源极连接到晶体管49的源极。任选的电容器55可具有连接到晶体管49的漏极的第一端子以及连接到晶体管49的栅极的第二端子。

46.图4示意性地示出了电路64的一部分的实施方案,该电路可具有可以是电路33(图3)的另选实施方案的实施方案。电路64基本上类似于电路33,不同的是参考电路包括插入晶体管48和输入20之间以及晶体管47和源极37之间的精度电路65。电路65可用于改善电流46和51之间的匹配。

47.在一个实施方案中,晶体管47和48的有效区域可被形成为具有长的宽度和非常小的长度,以便形成晶体管48的低输出电阻。然而,晶体管47和48的有效区域之间的比率或k关系受晶体管47和48的漏极电压的影响。晶体管66和67的电流镜连接有助于将晶体管47的漏极电压形成为与晶体管48的漏极电压基本上相同。形成这种关系有助于将有效区域之间的关系k形成为较少依赖于漏极电压,从而成为更精确的关系。

48.为了有助于为电路64提供上文所述的功能,晶体管67的漏极可共同连接到源40的第二端子、晶体管67的栅极以及晶体管66的栅极。晶体管67的源极可共同连接到输入20和晶体管48的漏极。晶体管66的源极可以连接到晶体管47的漏极,并且晶体管66的漏极可以连接到晶体管44的源极。

49.图5示意性地示出了电路70的一部分的实施方案,该电路可具有可以是电路64(图4)的另选实施方案的实施方案。电路70基本上类似于电路64,不同的是参考电路包括为电路65(图4)的另选实施方案的精度电路71。电路71包括晶体管72和电压偏移电路73。在电流46增大到接近电流38的值的情况下,晶体管72有助于供应电流以有助于形成电流46。在一个实施方案中,晶体管72有助于将晶体管66的漏极电压保持为约为晶体管72的栅极电压减去晶体管72的vgs的值。一个实施方案可以包括:如果电流46大于电流38,则晶体管66的漏极电压是v1

‑

v73

‑

vgs72(其中v73是由电路73提供的电压,并且vgs72是晶体管73的栅极

‑

源极电压)。在电流46小于电流38的情况下,晶体管72有助于将晶体管66的漏极保持在大于晶体管72的栅极加上晶体管72的阈值电压的值。一个实施方案可包括如果电流46小于电流38,则晶体管72截止(例如,晶体管44的栅极电压减去晶体管44的vgs大于晶体管72的栅极电压减去晶体管72的vgs)。在一个实施方案中,可选择由电路23和38提供的偏置电压以有助于提供这种状况。因此,晶体管72有助于为电路70提供改善的响应时间。

50.图6示出了形成在半导体管芯81上的半导体器件或集成电路80的实施方案的一部分的放大平面图。在一个实施方案中,电路10、12、13、26、31、33或34中的任何一者都可在管芯81上形成。管芯81也可包括为了简化附图而未在图5中示出的其他电路。

51.从上述所有内容可知,本领域技术人员应当理解输出电路可包括:

52.电压跟随器晶体管,诸如例如晶体管48,该电压跟随器晶体管被配置为接收表示由第一电压源(诸如例如19)形成的输入电压(诸如例如电压16)的第一信号,该电压跟随器晶体管被配置为由小于第一电压源的第二供电电压(诸如例如电压20)形成输出电压(诸如

例如电压vo),并且将输出(诸如例如输出28)处的输出电流(诸如例如电流27)供应给负载(诸如例如负载31);

53.增益晶体管,诸如例如晶体管49,该增益晶体管被配置为响应于该输出电压的增大而从该输出吸收电流,该增益晶体管具有控制电极;和

54.参考电路,诸如例如电路35,该参考电路耦接到该增益晶体管的该控制电极并且被配置为响应于该输出电压的增大而增大供应给该增益晶体管的该控制电极的第一电压,该参考电路具有传导参考电流(诸如例如电流46)的参考晶体管。

55.一个实施方案可包括参考电路可被配置为响应于输出电压的减小而减小第一电压。

56.在一个实施方案中,该电压跟随器晶体管可具有被耦接以接收该第二供电电压的漏极、被耦接以作为该输出电流的来源的源极、以及栅极。

57.该输出电路可具有一个实施方案,其中该参考晶体管可具有控制电极,该控制电极被耦接以接收该第一信号并且传导参考电流,其中该参考电流响应于该输出电压的变化而变化。

58.一个实施方案可包括参考电路可响应于参考电流的变化而改变供应给增益晶体管的控制电极的第一电压。

59.在一个实施方案中,电压跟随器晶体管的栅极通常耦接到参考晶体管的栅极并接收输入电压。

60.一个实施方案可包括电压跟随器晶体管可具有耦接到增益晶体管的源极并且被耦接以供应输出电压的源极。

61.在一个实施方案中,参考电路可形成第一电流,诸如例如电流38,该参考晶体管被配置为传导第一电流的第一部分作为参考电流;并且

62.该参考电路包括第一晶体管,诸如例如晶体管44,该第一晶体管传导该参考电流的第二部分(诸如例如部分45)作为第二电流(诸如例如电流45),并且与该第二电流的变化成比例地改变供应给该增益晶体管的该控制电极的第一电压。

63.一个实施方案可包括参考电路可具有耦接到增益晶体管的控制电极的第一电流源,诸如例如52,其中第一电流源传导第二电流。

64.在一个实施方案中,参考电路可包括第二电流源,诸如例如源37,该第二电流源具有被耦接以接收第一电压电源的第一端子和被耦接以供应第一电流的第二端子。

65.另一个实施方案还可包括响应电路(诸如例如电路58)可被配置为将第一电压限制为基本上不小于增益晶体管的栅极阈值电压的值。

66.在一个实施方案中,响应电路(诸如例如电路58)可具有第一晶体管(诸如例如晶体管61),其中源极耦接到增益晶体管的源极,第一晶体管具有耦接到第一晶体管的漏极和第二晶体管(诸如例如晶体管60)的源极的栅极,第二晶体管具有通常耦接到第二晶体管的漏极并且耦接到第三晶体管的栅极并且耦接到第三晶体管的漏极的栅极,第三晶体管具有耦接到增益晶体管的栅极的源极。

67.一个实施方案可包括精度电路,诸如例如电路65,该精度电路被配置为将该电压跟随器晶体管的漏极电压限制为基本上该参考电路的参考晶体管的漏极电压。

68.在一个实施方案中,精度电路可包括第一精度晶体管,诸如例如晶体管67,该第一

精度晶体管具有通常耦接到该电压跟随器晶体管的漏极并且接收该第二供电电压的源极,该第一精度晶体管具有耦接到该第一精度晶体管的漏极的栅极,该精度电路包括第二精度晶体管,诸如例如66,该第二精度晶体管具有耦接到该第一精度晶体管的栅极的栅极、耦接到该参考晶体管的漏极的源极以及被耦接以传导该参考电流的漏极。

69.本领域的技术人员也将理解,一种形成转换器电路的方法可包括:

70.耦接电压跟随器晶体管以从第一电路接收控制信号,该第一电路在第一操作电压下操作,该电压跟随器晶体管被配置为由小于该第一操作电压的第二操作电压形成输出电压,其中该输出电压表示该控制信号并且在输出处形成,并且其中该电压跟随器晶体管在该第二操作电压下供应输出电流;以及

71.将参考电路配置为控制输出晶体管(诸如例如晶体管49)以响应于输出电压的减小而在输出处吸收电流(诸如例如电流50)。

72.该方法可具有一个实施方案,该实施方案可包括形成电压跟随器晶体管以响应于输出电压的减小而减小输出电流的值。

73.一个实施方案还可包括将参考电路配置为形成与输出电流基本上成比例的参考电流,并且根据参考电流来控制输出晶体管。

74.本领域的技术人员将理解,一种形成半导体器件的方法的实施方案可包括:

75.将该半导体器件的放大器电路配置为在第一操作电压下操作并且形成以该第一操作电压为参考的第一信号;

76.将该半导体器件的输出晶体管配置为在小于该第一操作电压的第二操作电压下操作,该输出晶体管被配置为由该第二操作电压形成输出电压并且还形成通过该输出晶体管的输出电流,其中该输出电压在输出处形成并且表示该第一信号;以及

77.将参考电路配置为形成与该输出电流基本上成比例的参考电流,该参考电路被配置为控制第一晶体管(诸如例如49)以响应于该参考电流的变化而从该输出吸收电流。

78.该方法可具有一个实施方案,该方案可包括配置该参考电路包括耦接参考晶体管以形成该参考电流,其中该参考晶体管的栅极连接到该输出晶体管的栅极,其中该参考电流的变化改变该第一晶体管的栅极电压。

79.一个实施方案可包括将参考电路配置为控制第一晶体管以响应于该输出电压的增大而从该输出吸收电流。

80.鉴于上述全部内容,很明显公开了一种新颖的器件和方法。在一个实施方案的其他特征中,包括nmos电压跟随器输出晶体管,该nmos电压跟随器输出晶体管接收在第一电压源下操作的输入电压并且形成在较低电压源下操作的输出电压。电压跟随器配置有利于使用nmos晶体管而不是pmos晶体管。电压跟随器配置还有利于将输出电压的最大值限制为小于较低电压源。将参考电路配置为形成响应于负载电流的变化而变化的电流有利于控制增益晶体管以从输出吸收电流从而控制输出电压。参考电路的控制回路具有快速响应,这有利于快速响应输出电压或输入电压的变化。使用nmos晶体管作为增益晶体管有利于输出电压具有接近公共返回电压值的较低值。

81.使用任选的响应电路有助于具有快速响应时间。基本上保持增益晶体管不处于截止模式有助于提供快速响应时间。

82.虽然通过特定优选的实施方案和示例性实施方案描述了本说明书的主题,但本说

明书的前述附图和描述仅仅描绘了主题的实施方案的典型和非限制性示例,因此并不将前述附图和描述视为限制其范围,对本领域技术人员而言,许多备选方案和变型都将是显而易见的。

83.如下文的诸项权利要求所反映,本发明的各方面具有的特征可少于前文公开的单个实施方案的所有特征。所以,下文表述的诸项权利要求特此明确地并入附图说明中,并且每项权利要求本身都代表本发明的独立实施方案。此外,尽管本文描述的一些实施方案包含其他实施方案中包含的一些特征,却未包含其中包含的其他特征,但本领域技术人员应当理解,不同实施方案的特征的组合意在属于本发明的范围,而且意在形成不同的实施方案。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。