1.本实用新型涉及复位电路技术领域,尤其是一种低压低功耗上电复位电路。

背景技术:

2.上电复位信号是芯片内部时序电路能否正常工作的重要信号,复位信号的可靠性是芯片内部时序电路正常工作的关键。

3.传统的上电复位电路是通过检测电源电压大小的方式实现上电复位,在电源电压上升到某个设定的阈值时被上电复位电路检测到,从而输出上电复位信号。这种上电复位电路通过多个nmos管连接来实现下拉迟滞功能,即当电源电压上升到使一个nmos管导通时,其他的nmos管所组成的电流镜结构才能开始导通,从而对导线上的电压进行下拉,此时,输出复位信号信号por。在这种上电复位电路的实现方式中,电源电压最少要大于2个nmos管的vgs电压才可行,因此在电源电压降低时,若第一个工作的nmos管工作在线性区时,则会降低电路的可靠性。

4.为此,有必要提出一种低压低功耗上电复位电路来解决上述问题。

技术实现要素:

5.为了解决上述问题,本实用新型提出一种低压低功耗上电复位电路来解决上述问题。

6.本实用新型通过以下技术方案实现的:

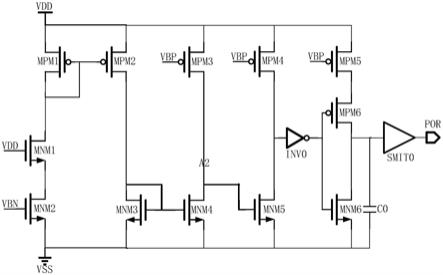

7.本实用新型提出一种低压低功耗上电复位电路,包括复位信号产生电路和整形电路,所述复位信号产生电路与所述整形电路电连接,所述复位信号产生电路包括下拉迟滞电路、pmos管mpm3、pmos管mpm4、nmos管mnm5,所述pmos管mpm3的栅极和偏置电压vbp相连,所述pmos管mpm3的漏极和所述下拉迟滞电路中的nmos管mnm4的漏极相连,所述pmos管mpm3的源极和电源电压vdd相连,所述pmos管mpm4的栅极和偏置电压vbp相连,所述pmos管mpm4的漏极和所述nmos管mnm5的漏极相连,所述pmos管mpm4的源极和电源电压vdd相连,所述nmos管mnm5的栅极和所述下拉迟滞电路中的nmos管mnm4的漏极相连,所述nmos管mnm5的漏极和所述pmos管mpm4的漏极相连,所述nmos管mnm5的源极接地。

8.进一步的,所述下拉迟滞电路包括pmos管mpm1、pmos管mpm2、nmos管mnm1、nmos管mnm2、nmos管mnm3、nmos管mnm4;

9.所述pmos管mpm1的栅极分别和所述pmos管mpm2的栅极、所述pmos管mpm1的漏极连接,所述pmos管mpm1的漏极分别和所述nmos管mnm1的漏极、所述pmos管mpm1的栅极连接,所述pmos管mpm1的源极和电源电压vdd相连;

10.所述pmos管mpm2的栅极分别和所述pmos管mpm1的栅极、所述pmos管mpm1的漏极相连,所述pmos管mpm2的漏极分别和所述nmos管mnm3的栅极、所述nmos管mnm3的漏极相连,所述pmos管mpm2的源极和电源电压vdd相连;

11.所述nmos管mnm1的栅极和电源电压vdd相连,所述nmos管mnm1的漏极分别和所述

pmos管mpm2的栅极、所述pmos管mpm1的栅极、所述pmos管mpm1的漏极相连,所述nmos管mnm1的源极和所述nmos管mnm2的漏极相连;

12.所述nmos管mnm2的栅极和偏置电压vbn相连,所述nmos管mnm2的漏极和所述nmos管mnm1的源极相连,所述nmos管mnm2的源极和电源地vss相连,

13.所述nmos管mnm3的栅极分别和所述pmos管mpm2的漏极、所述nmos管mnm3的漏极、所述nmos管mnm4的栅极相连,所述nmos管mnm3的源极和电源地vss相连;

14.所述nmos管mnm4的栅极分别和所述pmos管mpm2的漏极、所述nmos管mnm3的漏极、所述nmos管mnm3的栅极相连,所述nmos管mnm4的漏极分别和所述pmos管mpm3的漏极、所述nmos管mnm5的栅极相连,所述nmos管mnm4的源极和地vss相连。

15.进一步的,所述整形电路包括pmos管mpm5、pmos管mpm6、nmos管mnm6、电容c0、反相器inv0、正向施密特触发器smit0;

16.所述pmos管mpm5的栅极和偏置电压vbp相连,所述pmos管mpm5的漏极和所述pmos管mpm6的源极相连,所述pmos管mpm5的源极和电源vdd相连;

17.所述pmos管mpm6的栅极分别和反相器inv0的输出、所述nmos管mnm6的栅极相连,所述pmos管mpm6的漏极分别和所述nmos管mnm6的漏极、所述电容c0的上极板、所述正向施密特触发器smit0的输入端相连,所述pmos管mpm6的源极和所述pmos管mpm5的漏极相连;

18.所述nmos管mnm6的栅极分别和所述反相器inv0的输出、所述pmos管mpm6的栅极相连,所述nmos管mnm6的漏极分别和所述pmos管mpm6的漏极、所述电容c0的上极板、所述正向施密特触发器smit0的输入端相连,所述nmos管mnm6的源极接地vss;

19.所述电容c0的上极板分别和所述pmos管mpm6的漏极、所述nmos管mnm6的漏极、所述正向施密特触发器smit0的输入端相连,所述电容c0的下极板接地vss。

20.本实用新型的有益效果:

21.本实用新型提出一种低压低功耗上电复位电路,包括复位信号产生电路和整形电路,复位信号产生电路与整形电路电连接,复位信号产生电路包括下拉迟滞电路、pmos管mpm3、pmos管mpm4、nmos管mnm5,pmos管mpm3的栅极和偏置电压vbp相连,pmos管mpm3的漏极和下拉迟滞电路中的nmos管mnm4的漏极相连,pmos管mpm3的源极和电源电压vdd相连,pmos管mpm4的栅极和偏置电压vbp相连,pmos管mpm4的漏极和nmos管mnm5的漏极相连,pmos管mpm4的源极和电源电压vdd相连,nmos管mnm5的栅极和下拉迟滞电路中的nmos管mnm4的漏极相连,nmos管mnm5的漏极和pmos管mpm4的漏极相连,nmos管mnm5的源极接地;本低压低功耗上电复位电路有效地提高了电源在低电源电压下的可靠性,复位信号的产生与电源电压vdd的上升速度无关,且在较低电源电压时,仍能正常产生复位信号,使芯片中的时序电路复位,提高了上电复位的可靠性,且能在低电源电压下应用。

附图说明

22.图1为本实用新型提出的低压低功耗上电复位电路实施例1的电路图;

23.图2为本实用新型提出的低压低功耗上电复位电路实施例2的电路图;

24.图3为本实用新型提出的低压低功耗上电复位电路的正向施密特电路的电路图;

25.图4为本实用新型提出的低压低功耗上电复位电路在不同上电速度下的仿真结果示意图。

具体实施方式

26.为了更加清楚、完整的说明本实用新型的技术方案,下面结合附图对本实用新型作进一步说明。

27.实施例1

28.请参考图1、图3和图4,本实用新型提出一种低压低功耗上电复位电路,包括复位信号产生电路和整形电路,复位信号产生电路与整形电路电连接,复位信号产生电路包括下拉迟滞电路、pmos管mpm3、pmos管mpm4、nmos管mnm5,pmos管mpm3的栅极和偏置电压vbp相连,pmos管mpm3的漏极和下拉迟滞电路中的nmos管mnm4的漏极相连,pmos管mpm3的源极和电源电压vdd相连,pmos管mpm4的栅极和偏置电压vbp相连,pmos管mpm4的漏极和nmos管mnm5的漏极相连,pmos管mpm4的源极和电源电压vdd相连,nmos管mnm5的栅极和下拉迟滞电路中的nmos管mnm4的漏极相连,nmos管mnm5的漏极和pmos管mpm4的漏极相连,nmos管mnm5的源极接地。

29.进一步的,下拉迟滞电路包括pmos管mpm1、pmos管mpm2、nmos管mnm1、nmos管mnm2、nmos管mnm3、nmos管mnm4;

30.pmos管mpm1的栅极分别和pmos管mpm2的栅极、pmos管mpm1的漏极连接,pmos管mpm1的漏极分别和nmos管mnm1的漏极、pmos管mpm1的栅极连接,pmos管mpm1的源极和电源电压vdd相连;

31.pmos管mpm2的栅极分别和pmos管mpm1的栅极、pmos管mpm1的漏极相连,pmos管mpm2的漏极分别和nmos管mnm3的栅极、nmos管mnm3的漏极相连,pmos管mpm2的源极和电源电压vdd相连;

32.nmos管mnm1的栅极和电源电压vdd相连,nmos管mnm1的漏极分别和pmos管mpm2的栅极、pmos管mpm1的栅极、pmos管mpm1的漏极相连,nmos管mnm1的源极和nmos管mnm2的漏极相连;

33.nmos管mnm2的栅极和偏置电压vbn相连,nmos管mnm2的漏极和nmos管mnm1的源极相连,nmos管mnm2的源极和电源地vss相连,

34.nmos管mnm3的栅极分别和pmos管mpm2的漏极、nmos管mnm3的漏极、nmos管mnm4的栅极相连,nmos管mnm3的源极和电源地vss相连;

35.nmos管mnm4的栅极分别和pmos管mpm2的漏极、nmos管mnm3的漏极、nmos管mnm3的栅极相连,nmos管mnm4的漏极分别和pmos管mpm3的漏极、nmos管mnm5的栅极相连,nmos管mnm4的源极和地vss相连。

36.进一步的,整形电路包括pmos管mpm5、pmos管mpm6、nmos管mnm6、电容c0、反相器inv0、正向施密特触发器smit0;

37.pmos管mpm5的栅极和偏置电压vbp相连,pmos管mpm5的漏极和pmos管mpm6的源极相连,pmos管mpm5的源极和电源vdd相连;

38.pmos管mpm6的栅极分别和反相器inv0的输出、nmos管mnm6的栅极相连,pmos管mpm6的漏极分别和nmos管mnm6的漏极、电容c0的上极板、正向施密特触发器smit0的输入端相连,pmos管mpm6的源极和pmos管mpm5的漏极相连;

39.nmos管mnm6的栅极分别和反相器inv0的输出、pmos管mpm6的栅极相连,nmos管mnm6的漏极分别和pmos管mpm6的漏极、电容c0的上极板、正向施密特触发器smit0的输入端

相连,nmos管mnm6的源极接地vss;

40.电容c0的上极板分别和pmos管mpm6的漏极、nmos管mnm6的漏极、正向施密特触发器smit0的输入端相连,电容c0的下极板接地vss。

41.在本实施方式中:

42.vbn和vbp分别为内部基准提供的固定偏置电压。pmos管mpm1和pmos管mpm2组成一组电流镜结构,nmos管mnm3和nmos管mnm4组成一组电流镜结构,这两组电流镜结构提供pmos管mpm3和nmos管mnm4支路上的下拉电流。

43.当vdd<vds4时,即电源电压vdd小于nmos管mnm4的vds时,电路处于不工作状态,输出信号por为低电平,复位芯片。

44.当vds4<vdd<vds2 vth1时,即电源电压vdd大于nmos管mnm4的vds,小于nmos管mnm2的源漏电压和nmos管mnm1的阈值电压之和时,mnm1管断开,因此下拉迟滞电路中无电流,即pmos管mpm3和nmos管mnm4支路上的下拉电流为0,同时,内部基准电路开始工作,即pmos管mpm3和nmos管mnm4支路上的上拉电流开始增加,此时a2跟随电源电压vdd升高,输出信号por为低电平,复位芯片。

45.当vds2 vth1<vdd<vds4 vgs3时,即电源电压vdd大于nmos管mnm2的源漏电压和nmos管mnm1的阈值电压之和,小于nmos管mnm4的源漏电压和pmos管mpm3的栅源电压之和时,下拉迟滞电路开始工作,nmos管mnm4中的电流开始增加,pmos管mpm3中的电流继续增大,因而在pmos管mpm3和nmos管mnm4支路上上拉电流大于下拉电流,此时a2继续跟随电源电压升高,输出信号por为低电平,复位芯片。

46.当vds4 vgs3<vdd<vds1 vds2 vgs1时,即电源电压vdd大于nmos管mnm4的源漏电压和pmos管mpm3的栅源电压之和,小于nmos管mnm1的源漏电压vds1,nmos管mnm2的源漏电压vds2和pmos管mpm1的栅源电压vgs1之和时,因为pmos管mpm3达到饱和区,所以流过pmos管mpm3的电流保持恒定,同时,nmos管mnm4中的电流继续增加。在pmos管mpm3和nmos管mnm4支路中,上拉电流保持恒定,下拉电流继续增加,当下拉电流大于上拉电流时,a2从此时的电源电压降为0,此时输出信号por变为高电平,结束复位,芯片中的时序电路开始工作。

47.当vdd>vds1 vds2 vgs1时,即电源电压vdd大于nmos管mnm1的源漏电压vds1,nmos管mnm2的源漏电压vds2和pmos管mpm1的栅源电压vgs1之和时,确保nmos管mnm4中复制的电流大小是pmos管mpm3的2倍,提高复位信号的可靠性。

48.其中,pmos管mpm5的作用是使对电容c0的充电电流恒定,电容c0可使输出信号por的释放点滞后,提高电路的可靠性,防止输出信号por在电源电压vdd较低时释放。

49.其中,为了保证在电源电压上升的前段时间内,a2跟随电源电压上升,要通过调整相应的mos管尺寸,确保pmos管mpm1和pmos管mpm2工作在饱和区时所需的栅源电压vgs1要大于pmos管mpm3的栅源电压vgs3。

50.其中,为了实现翻转电平的固定,在本实施例中,通过正向施密特触发器smit0实现此功能,图3示出了正向施密特触发器的电路结构示意图,如图3所示,其中包括4个pmos管和4个nmos管以及一个反相器inv。

51.图4为实际仿真波形图,其中电源电压上电时间40us,在第37us处por信号释放,实现了上电复位功能。

52.实施例2

53.请参考图2、图3和图4,本实用新型提出一种低压低功耗上电复位电路,包括复位信号产生电路和整形电路,复位信号产生电路与整形电路电连接,复位信号产生电路包括下拉迟滞电路、pmos管mpm3、pmos管mpm4、nmos管mnm5,pmos管mpm3的栅极和偏置电压vbp相连,pmos管mpm3的漏极和下拉迟滞电路中的nmos管mnm4的漏极相连,pmos管mpm3的源极和电源电压vdd相连,pmos管mpm4的栅极和偏置电压vbp相连,pmos管mpm4的漏极和nmos管mnm5的漏极相连,pmos管mpm4的源极和电源电压vdd相连,nmos管mnm5的栅极和下拉迟滞电路中的nmos管mnm4的漏极相连,nmos管mnm5的漏极和pmos管mpm4的漏极相连,nmos管mnm5的源极接地。

54.进一步的,下拉迟滞电路包括pmos管mpm1、pmos管mpm2、nmos管mnm1、nmos管mnm2、nmos管mnm3、nmos管mnm4;

55.pmos管mpm1的栅极分别和pmos管mpm2的栅极、pmos管mpm1的漏极连接,pmos管mpm1的漏极分别和nmos管mnm1的漏极、pmos管mpm1的栅极连接,pmos管mpm1的源极和电源电压vdd相连;

56.pmos管mpm2的栅极分别和pmos管mpm1的栅极、pmos管mpm1的漏极相连,pmos管mpm2的漏极分别和nmos管mnm3的栅极、nmos管mnm3的漏极相连,pmos管mpm2的源极和电源电压vdd相连;

57.nmos管mnm1的栅极和电源电压vdd相连,nmos管mnm1的漏极分别和pmos管mpm2的栅极、pmos管mpm1的栅极、pmos管mpm1的漏极相连,nmos管mnm1的源极和nmos管mnm2的漏极相连;

58.nmos管mnm2的栅极和偏置电压vbn相连,nmos管mnm2的漏极和nmos管mnm1的源极相连,nmos管mnm2的源极和电源地vss相连,

59.nmos管mnm3的栅极分别和pmos管mpm2的漏极、nmos管mnm3的漏极、nmos管mnm4的栅极相连,nmos管mnm3的源极和电源地vss相连;

60.nmos管mnm4的栅极分别和pmos管mpm2的漏极、nmos管mnm3的漏极、nmos管mnm3的栅极相连,nmos管mnm4的漏极分别和pmos管mpm3的漏极、nmos管mnm5的栅极相连,nmos管mnm4的源极和地vss相连。

61.进一步的,整形电路包括pmos管mpm5、pmos管mpm6、nmos管mnm6、反相器inv0、正向施密特触发器smit0;

62.pmos管mpm5的栅极和偏置电压vbp相连,pmos管mpm5的漏极和pmos管mpm6的源极相连,pmos管mpm5的源极和电源vdd相连;

63.pmos管mpm6的栅极分别和反相器inv0的输出、nmos管mnm6的栅极相连,pmos管mpm6的漏极分别和nmos管mnm6的漏极、电容c0的上极板、正向施密特触发器smit0的输入端相连,pmos管mpm6的源极和pmos管mpm5的漏极相连;

64.nmos管mnm6的栅极分别和反相器inv0的输出、pmos管mpm6的栅极相连,nmos管mnm6的漏极分别和pmos管mpm6的漏极、电容c0的上极板、正向施密特触发器smit0的输入端相连,nmos管mnm6的源极接地vss。

65.在本实施方式中:

66.整体的电路去掉了电容c0,增加了一个pmos管mpm7和一个反相器inv1。

67.在考虑复位信号por释放过程中的干扰时,在实施例1中,如果电源出现噪声或者

其他因素引起的干扰,则可能影响复位信号por的正常释放,因此引入pmos管mpm7和反相器inv1,当复位信号por从0升高到电源电压vdd时,inv1的输出从电源电压vdd降低到0,pmos管mpm7导通,使pmos管mpm5短路,pmos管mpm5,pmos管mpm6和nmos管mnm6组成的支路上拉能力增强,smit1的输入被迅速上拉,加快por从0升高到电源电压vdd的过程。这个正反馈环路可加强复位信号por释放过程中的抗干扰能力,提高电路可靠性。

68.在考虑增加a2跟随电源电压的时间时,可将下拉迟滞电路中的nmos管mnm2工作在亚阈值区,减少nmos管mnm2的源漏电压vds2,从而在电源电压固定时,可以得到更大的栅源电压vgs1,即vgs3

‑

vgs1增大,a2跟随电源电压的时间更久,所以复位信号por保持复位状态的时间更久,电路可靠性提高。

69.图4为实际仿真波形图,其中电源电压上电时间40us,在第37us处por信号释放,实现了上电复位功能。

70.当然,本实用新型还可有其它多种实施方式,基于本实施方式,本领域的普通技术人员在没有做出任何创造性劳动的前提下所获得其他实施方式,都属于本实用新型所保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。