1.本实用新型属于功率解耦电路控制技术领域,尤其涉及一种基于交流侧并联功率解耦电路的控制器。

背景技术:

2.微逆变器因其多发电量、易扩展、低成本、热插拔和模块化设计的优点,逐渐成为未来分布式光伏逆变器的趋势。然而,在分布式发电系统中,光伏组件由于mppt控制产生恒定的输入功率,而传输到电网的功率却含有两倍工频的功率脉动,两者的瞬时值不一致。故传统微逆变器均使用电解电容器实现逆变器的瞬时输入输出功率的平衡。如此,相对5

‑

10万小时寿命的半导体器件和无源元件来说,电解电容器寿命小于1万小时,成为限制微逆变器稳定性和使用寿命的关键。为了延长微逆变器系统的整体寿命,设计了由电力电子元件组成的交流侧功率去耦电路,平衡电路中的脉动能量,降低系统中的电容容量,使用长寿命的薄膜电容器替换电解电容器。对于功率解耦电路的控制,从核心控制器的角度来看,目前常用的控制器有dsp和fpga两种。

3.dsp是一种独特的微处理器,有自己的完整指令系统,是以数字信号来处理大量信息的器件。一个数字信号处理器在一块不大的芯片内包括有运算单元、控制单元、各种寄存器以及一定数量的存储单元等等,在其外围还可以扩展连接若干存储器,并可以与一定数量的外部设备互相通信,有软、硬件的全面功能,本身就是一个微型计算机。由于它运算能力很强,速度很快,体积很小,而且采用软件编程具有高度的灵活性,因此为从事各种复杂的应用提供了一条有效途径。

4.fpga是在pal、gal、pld等可编程器件的基础上进一步发展的产物,其内部由各种基本逻辑门构成,是专用集成电路(asic)中集成度最高的一种。fpga内部包括可配置逻辑模块clb(configurable logic block)、输出输入模块iob(input output block)和内部连线(interconnect)三个部分。用户可对fpga内部的逻辑模块和i/o模块重新配置,以实现用户的逻辑。它还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改。可以毫不夸张的讲,fpga能完成任何数字器件的功能,上至高性能cpu,下至简单的74电路,都可以用fpga来实现。使用fpga来开发数字电路,可以大大缩短设计时间,减少pcb面积,提高系统的可靠性。

5.两种控制器性能都比较优异,都能单独应用于功率解耦电路中,但dsp采用串行指令流的工作方式限制了其采样速率,fpga虽然在高采样率场合能较好工作,但处理复杂的多算法任务时的灵活性还是不如dsp。在采用功率解耦电路的微逆变器中,升压和逆变电路部分通常需要实现电压环闭环控制、最大功率跟踪控制和并网控制等功能,且该部分电路的开关管通常工作在较低的工作频率,此时通常用dsp实现该部分功能。但在功率解耦电路中的功率解耦部分,开关管通常开关时间比较短暂,且要求较高的可靠性保证开关管的工作时序,否则将影响功率解耦电路的解耦效果。同时考虑到微逆变器对于系统体积的要求,应用高频开关技术是减小体积的有效途径,故目前不少学者采用将驱动算法以电路逻辑方

式固化的现场可编程门阵列(fpga),以此构成fpga与dsp相结合构成双cpu结构的控制器。根据光伏微逆变器使用场合和使用条件的要求,如果采用双cpu结构,将大大增加微逆变器的成本。

技术实现要素:

6.本实用新型的目的是提供一种基于交流侧并联功率解耦电路的控制器,针对光伏并网发电系统中交流侧解耦电路控制存在的问题,在系统控制中同时使用dsp数字控制和74系列芯片模拟控制,在能实现较低硬件成本的基础上又能更好的实现对微逆变器和解耦电路的控制。

7.本实用新型提供了一种基于交流侧并联功率解耦电路的控制器,包括设于逆变器交流侧的功率解耦电路,以及与所述逆变器连接的dsp数字控制器;

8.所述dsp数字控制器通过模拟控制系统与所述功率解耦电路连接,用于通过模拟控制满足功率解耦电路开关管的工作时间要求;

9.所述功率解耦电路包括电压检测模块、电流比较模块、驱动信号产生模块及多次闭锁模块;所述电压检测模块及电流比较模块与所述驱动信号产生模块连接,所述多次闭锁模块与所述电压检测模块连接;

10.所述电压检测模块用于检测逆变器输出电压;

11.所述电流比较模块用于将电感电流实际值与给定值比较,并传递给所述驱动信号产生模块;

12.所述驱动信号产生模块用于接收电压检测模块和电流比较模块的两路信号,并将信号传递给开关器件,并触发开关器件;

13.所述多次闭锁模块用于接收功率解耦电路工作周期信号及驱动信号产生模块产生的开关信号,执行闭锁或开放驱动信号产生模块动作。

14.进一步地,所述模拟控制系统包括由74l系列芯片构成的高速驱动电路。

15.借由上述方案,通过基于交流侧并联功率解耦电路的控制器,同时使用dsp数字控制和74l系列芯片模拟控制,在实现较低硬件成本,保证各开关时序的高速性及可靠性的基础上,更好的实现了对微逆变器和解耦电路的控制。

16.上述说明仅是本实用新型技术方案的概述,为了能够更清楚了解本实用新型的技术手段,并可依照说明书的内容予以实施,以下以本实用新型的较佳实施例详细说明如后。

附图说明

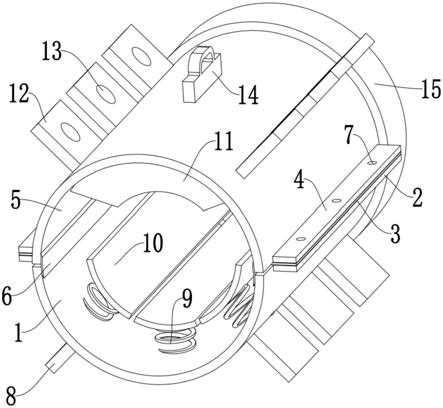

17.图1是本实用新型系统控制结构图;

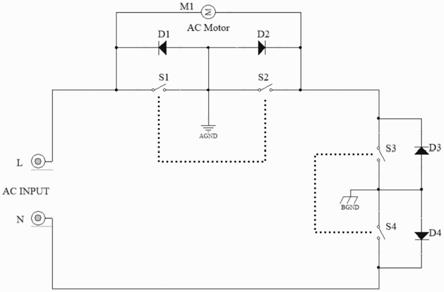

18.图2是本实用新型功率解耦电路控制工作流程图;

19.图3是本实用新型功率解耦电路的结构框图;

20.图4是本实用新型多次闭锁电路工作过程示意图;

21.图5是本实用新型电压检测电路原理图;

22.图6是本实用新型电流比较电路原理图;

23.图7是本实用新型驱动信号产生电路原理图;

24.图8是本实用新型多次闭锁电路原理图;

25.图9是本实用新型一实施例中各阶段开关触发脉冲信号与解耦电路工作信号示意图;

26.图10是本实用新型一实施例中解耦电路工作信号与输出电压上升沿信号示意图;

27.图11是本实用新型一实施例中多次闭锁后开关驱动信号示意图。

具体实施方式

28.下面结合附图和实施例,对本实用新型的具体实施方式作进一步详细描述。以下实施例用于说明本实用新型,但不用来限制本实用新型的范围。

29.本实施例以两级式逆变器加交流侧功率解耦电路为基础,功率解耦电路采用模拟控制来满足解耦电路开关管较短的工作时间,提高控制的准确性。两级式逆变器部分采用dsp数字控制器,来实现电路中直流升压部分的pi控制以及mppt功能,逆变部分采用滞环控制,其参考信号是在dsp中完成计算然后通过dac变换得到的。对于逻辑驱动模拟控制电路的解耦电感电流参考信号i

lx.ref

,频率为50hz,也由dsp计算得到,图1为整个系统控制结构图,其中i

pv

,u

pv

分别为光伏组件输出电流跟电压,u

dc

,u

ref

分别为中间母线电压以及中间母线参考电压,i

g

,u

g

,i

ref

分别为逆变器并网电流、逆变器并网电压、逆变器并网电流参考值。

30.目前boost和逆变器的dsp数字控制系统比较成熟,本实施例主要说明采用功率解耦电路模拟控制方案实现的设计,模拟控制系统均由74l系列芯片构成。

31.功率解耦电路控制流程图如图2所示,逆变器输出电压u

out

上升沿作为一个重要的导通标志当被开关驱动电路检测到的时候,导通stage1功率解耦电路开关器件,此时检测解耦电感电流i

l

信号,判断其是否到达峰值电流参考值,当满足条件,关断stage1功率解耦电路开关器件,同时导通stage2功率解耦电路开关器件。

32.参图3所示,根据功率解耦电路控制工作流程,功率解耦电路的控制组成由电压检测模块(电路),电流比较模块(电路),驱动信号产生模块(电路),多次闭锁模块(电路)组成。

33.(1)电压检测电路:逆变器输出电压u

g

上升沿作为一个重要的信号,当检测到这个信号时候,驱动信号产生电路会收到由电压检测电流传递来得的信号,同时还要确保电路工作周期内只输出一次触发脉冲信号。

34.(2)电流比较电路:将电感电流实际值与给定值比较,并传递给驱动信号产生电路。

35.(3)驱动信号产生电路:接收电压检测电路和电流比较电路两路信号,并传递给开关,实现触发开关器件。

36.(4)多次闭锁电路:该模块一方面接收功率解耦电路工作周期信号,另一方面接收驱动信号产生电路产生的开关信号。当多次闭锁电路接收到一次开关信号后,闭锁驱动信号产生电路,在接收到下一个周期的功率解耦电路的工作周期信号后,开放驱动信号产生电路。其工作过程如图4所示:

37.根据驱动电路各模块的工作要求,同时考虑要对各模块不同类型的输入信号进行处理,本实施例采用以74系列ttl芯片为主设计了一个交流侧功率解耦的高速驱动电路,其中74ls系列芯片的典型传输延时为18ns,可满足电路高速工作的需求。

38.参图5至8所示,下面对功率解耦电路的各电路(模块)进行详细说明。

39.电压检测电路

40.逆变器输出交流方波电压信号和多次闭锁信号都是电压检测电路的输入信号。sn74ls123的作用是检测方波电压信号的上升沿然后输出一脉冲信号。由b端输入待检测信号,为了保证每个周期只有一个脉冲信号被输出,上升沿触发脉冲与多次闭锁信号求与。输出脉冲的宽度是由电阻r1和电容c1来控制的,图5为电路的具体设计原理图。

41.电流比较电路

42.该部分电路原理图如图6所示,加入反相器dm74als04bn可以使得sn74ls123只对电感电流下降阶段的过零点进行检测,v

in

为经过霍尔传感器转化成电压的电感电流,参考峰值整定值为vref.h,参考过零整定值为vref.l。

43.驱动信号产生电路

44.本实施例采用两个下降沿jk触发器74f113pc将信号检测电路和电流比较电路产生的脉冲信号转化为驱动脉冲,jp为电路保护信号输入jk触发器的j端来对电路进行保护,图7为电路的具体设计原理图。

45.多次闭锁电路

46.为了降低成本本文采用jk触发器74f113pc产生所需要的闭锁信号,该过程原理图如图8所示。

47.为验证控制方案的合理性,进行了模拟控制的实验,图9中信号检测电路产生脉宽800ns的触发脉冲,来开通关断stage1和stage2中的开关,在图9中stage1的开关脉冲在一个工作周期内只导通一次stage2的开关脉冲在一个解耦电路工作周期内也只导通一次,而且两者时序为stage2开关触发脉冲信号导通在stage1开关触发脉冲信号关断之后,开关时序合理正确。

48.图10最上方波形为解耦电路工作周期信号,工作周期时间为50μs,其中有45μs是在高电平时间,说明功率解耦电路在高电平时间内可以工作。通过对比没有经过多次闭锁电路的和经过多次闭锁电路的逆变器上升沿信号ug,可以看出闭锁电路设计合理有效保证了解耦电路在一个工作周期内各个阶段开关只导通一次。

49.图11中stage1和stage2的开关触发信号工作时间短暂都在10us以下经过多次闭锁电路后信号仍旧完整,时序仍旧合理。

50.以上所述仅是本实用新型的优选实施方式,并不用于限制本实用新型,应当指出,对于本技术领域的普通技术人员来说,在不脱离本实用新型技术原理的前提下,还可以做出若干改进和变型,这些改进和变型也应视为本实用新型的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。