a/d转换设备及a/d转换方法

技术领域

1.本发明涉及一种将模拟的音信号转换为数字的音信号的a/d转换设备及a/d转换方法。

背景技术:

2.在浮点型a/d转换设备,在adc(analog digital converter)的前级设置可变增益放大器,进行可变增益放大器的增益的切换控制,使得针对adc的输入电平不高于上限、或不低于下限。

3.在专利文献1所述的浮点型a/d转换设备,根据由adc输出的数字样本而进行可变增益放大器的增益切换。另外,在专利文献2所记载的浮点型a/d转换设备,根据输入至adc的模拟信号而进行可变增益放大器的增益切换。

4.专利文献1:美国专利第9008334号

5.专利文献2:日本特开2017-175215号公报

技术实现要素:

6.专利文献1所记载的浮点型a/d转换设备基于adc的输出而进行增益切换,因此,存在如下问题,即,在需要进行增益切换的adc的输入电平产生了变化的情况下,由于adc的延迟而可变增益放大器的增益切换延迟。

7.另外,专利文献2所记载的浮点型a/d转换设备需要:模拟电路,其为了进行使可变增益放大器的增益降低的控制而将模拟信号的电平与第1电平进行比较;模拟比较器,其为了进行该增益升高的控制而将该电平与第2电平进行比较;以及模拟电路,其产生第1电平及第2电平,因此该浮点型a/d转换设备存在电路结构复杂且大规模的问题。

8.另外,专利文献2所记载的浮点型a/d转换设备在从采样并保持模拟信号至adc对模拟信号进行a/d转换为止的期间,根据该模拟信号的电压而确定可变增益放大器的增益。因此,如果所采样并保持的模拟信号的绝对值小(接近零电平)则立即提高增益,因此存在如下问题,即,提高增益的增益切换频发,因增益切换导致的音的劣化频发。

9.本发明就是鉴于如上所述的情况而提出的,其目的在于,提供一种a/d转换设备,该a/d转换设备不会导致模拟电路的大规模化而能够使可变增益放大器的增益讯速地追随模拟信号的电平变化,并且能够防止增益切换的频发。

10.本发明提供一种a/d转换设备,其包含:放大器,其以与状态相应的增益对第1模拟信号进行模拟放大,作为第2模拟信号而输出;转换器,其将所述第2模拟信号转换为数字信号,作为第1数字信号而输出;递减电路,其检测所述第2模拟信号超过由第1电平规定的范围,使所述状态转移至增益低1级的状态;以及递增电路,其检测所述第1数字信号在规定期间持续地进入由与所述第1电平相比绝对值小的第2电平规定的范围,使所述状态转移至增益高1级的状态。

附图说明

11.图1是表示本发明的作为第1实施方式的a/d转换设备的结构的框图。

12.图2是对该a/d转换设备的增益表进行说明的图。

13.图3是表示包含该a/d转换设备的音处理装置的结构的框图。

14.图4是表示该音处理装置的流程图。

15.图5是表示该音处理装置的流程图。

16.图6是表示该音处理装置的流程图。

17.图7是表示本发明的第2实施方式的动作的流程图。

具体实施方式

18.以下,参照附图对本发明的实施方式进行说明。

19.<第1实施方式>

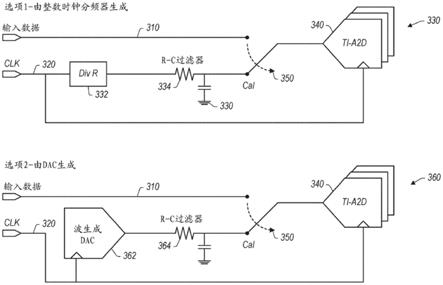

20.图1是表示本发明的作为第1实施方式的a/d转换设备1的结构的框图。该设备1具有放大器11、adc 12、模拟比较器13及14、fpga(field programmable gate array)20。该设备1作为音信号而接收模拟信号i_a(第1模拟信号),转换为数字信号o_d并输出至进行该数字信号o_d的信号处理的信号处理设备(例如,图3的信号处理部)。

21.放大器11是将对a/d转换设备1输入的模拟信号i_a以与当前的状态gs相应的增益进行放大,输出该放大后的模拟信号m_a(第2模拟信号)的可变增益放大器。这里,状态gs表示由fpga 20指示的放大器11的增益的阶段,在本实施方式,状态gs越高,增益越高。

22.adc 12是将模拟信号m_a转换为数字信号m_d(第1数字信号)的转换器。

23.向模拟比较器13及14分别赋予第1电平vref2及vref3。这里,vref2及vref3是用于判断是否提高放大器11的增益的参考电平,vref2是正侧的参考电平,vref3在负侧是参考电平。如果信号m_a的电压高于vref2,则模拟比较器13输出h电平作为信号cs2,除此以外输出l电平作为信号cs2。另外,如果信号m_a的电压低于vref3,则模拟比较器14输出h电平作为信号cs3,除此以外输出l电平作为信号cs3。

24.fpga 20如图1所示,被编程为作为数字比较器21及22、递增判定部23、递减判定部24、状态计数器25、增益存储器26及复原电路27起作用。

25.状态计数器25是存储当前的状态gs,根据递增指示而使状态gs升高1,根据递减指示而立即使状态gs下降1的递增递减计数器。使增益升高的动作可以相对于递增指示而稍微延迟。存储于该状态计数器25的状态gs被供给至上述的放大器11,用于增益的控制。

26.对数字比较器21及22分别赋予第2电平vref1及vref4。这里,vref1及vref4是表示用于判断是否使放大器11的增益下降的参考电平的数字值。如果将模拟信号m_a和将其转换后的数字信号m_d视作相同的电平,则在电平vref1及vref4和上述的电平vref2及vref3之间存在vref2>vref1>0>vref4>vref3的关系。即,如果以绝对值进行比较,则第2电平小于第1电平。

27.如果信号m_d的值低于vref1,则数字比较器21输出h电平作为信号cs1,除此以外输出l电平作为信号cs1。另外,如果信号m_d高于vref4,则数字比较器22输出h电平作为信号cs4,除此以外输出l电平作为信号cs4。

28.递增判定部23在信号cs1及cs4这两者在规定期间持续地维持了h电平时,即,在信

号m_d的电平在规定期间持续地维持了vref1及vref4间的电平时,向状态计数器25发送递增指示,使状态gs升高1。

29.数字比较器21及22和递增判定部23构成对第1数字信号m_d的值在规定期间持续地进入第2电平vref4至vref1的范围进行检测,使状态计数器25将其状态gs向增益提高1级的状态转移的递增电路。即,递增电路在接收到的音信号的正和负的峰值分别持续地未达到由当前的状态gs规定的正和负的参考值(正:vref1/ag(gs)、负:vref4/ag(gs))时,将放大器11的增益ag切换为高1阶段的增益。但是,状态计数器25的状态gs的最大值为7,无法向比其更大的状态递增。

30.递减判定部24在信号cs2或cs3的任意者成为h电平时,将递减指示发送至状态计数器25,使状态gs下降1。该递减判定部24和上述的模拟比较器13及14构成对第2模拟信号m_a的电压超过第1电平vref3至vref2的范围进行检测,使状态计数器25将其状态gs向增益降低1级的状态转移的递减电路。递减判定部24是根据模拟比较器13及14的输出使状态gs立即变化的低延迟的数字电路。即,递减电路在接收到的音信号的正和负的峰值的任意者从以当前的状态gs规定的正和负的参考值(正:vref2/ag(gs)、负:vref3/ag(gs))的范围偏离的瞬间,将放大器11的增益ag切换至低1阶段的增益。但是,状态计数器25的状态gs的最小值为0,无法向比其更小的状态递减。

31.增益存储器26是将与存储于状态计数器25的当前的状态gs对应的增益值dg(gs)在与adc 12的信号延迟相当的时间、延迟的定时向复原电路27供给的存储器。复原电路27将数字信号m_d以增益dg(gs)进行放大,作为信号o_d(第2数字信号)而输出。

32.对于由状态gs指定的各状态的放大器11的增益,原本存在由于电阻等模拟元件的波动引起的波动。在本实施方式,对增益存储器26采取了用于对因放大器11的增益设计值和实际的增益之间的误差而在信号o_d产生的增益误差进行校正的对策。

33.这里,设为在与状态相应的放大器11的增益的设计值g和实际的放大器11的模拟增益之间产生误差δg,模拟增益成为g δg。在该情况下,在复原电路27,如果不考虑误差,以增益1/g对信号m_d进行数字放大,则总的增益o_d/i_a成为(g δg)/g。误差δg针对每个放大器、每个状态而不同,其符号也有时为正有时为负。因此,在每次切换状态时,总增益发生变化,并且在切换的时间点产生信号o_d以阶梯状变形的噪声。因此,在本实施方式,在制造a/d转换设备1时,制作商对各状态gs的放大器11的模拟增益ag(gs)进行测定,基于该模拟增益而对各状态gs的增益dg(gs)进行计算,将包含上述多个状态gs的增益dg(gs)的增益表写入至增益存储器26。

34.图2是对增益表进行说明的图。如图2所示,在增益表存储有根据所测定的模拟增益ag(gs)计算出的复原电路27的各状态gs的增益dg(gs)=bg-ag(gs)。这里,bg为作为基本的基础增益,也可以以使得在后级的信号处理中状况良好的方式由制作商任意地决定。在图2,记载有模拟增益ag(gs)大约为60db等,这是因为,如上所述放大器11的模拟增益存在波动。

35.在图2所示的例子,增益ag(gs)以10db为增量,但这不过是设计的一个例子。增益ag(gs)也可以以其他增量幅度进行设计,还可以将增量幅度在中途改变。

36.另外,在图2所示的例子,状态gs越大,则增益ag(gs)越大,相反也可以是状态gs越大,则增益ag(gs)越小。在该情况下,在图1,递增指示和递减指示相反。

37.另外,也可以根据来自用户的指示或设定而对状态gs的变化范围进行限制(在图2的例子,gs=0至gs=5的范围)。例如,如果在已知不需要高的增益的信号(线路电平的信号)输入至a/d转换设备1的情况下,对状态gs的变化范围设定上限,则减少不必要的增益切换。该限制的详细内容将与图6相关联地后述。

38.在放大器11的增益切换时,除了由放大器11的模拟增益的误差引起的噪声以外,还产生过渡性的噪声。因此,在本实施方式,增益存储器26在状态gs被切换时,将表示其切换定时的信号gc发送至复原电路27。解调电路27以增益dg(gs)对信号m_d进行放大,并且进行以与信号gc相应的定时将在该放大后的信号m_d'所包含的其过渡性的噪声降低的运算。复原电路27将在信号m_d显现出因增益切换引起的过渡性的噪声的期间、更具体而言从信号gc的输出定时起规定时间以内的期间内的、放大后的信号m_d'的样本置换为插补样本,得到设备1所输出的信号o_d。插补样本是基于该期间的前后的信号m_d'而计算的。如上所述,能够降低因放大器11的增益切换而在该信号o_d产生的过渡性的噪声。该噪声降低不限于该置换法,也可以通过与过渡噪声的特征相应的噪声降低滤波器进行。例如,也可以根据该期间以前的样本对信号m_d'的一系列的样本中、包含过渡性的噪声的期间的该噪声的样本进行预测而将该预测出的噪声去除。

39.接着,对本实施方式的动作及效果进行说明。在本实施方式,与用于要求高速性的放大器11的增益递减判定的第1电平的比较是使用a/d转换前的第2模拟信号m_a而进行的。如果音信号超过由第1电平规定的范围,则能够高速地判定增益递减,防止在adc 12产生音信号的削波(clip)。

40.另一方面,与用于不要求高速性的放大器11的增益递增判定的第2电平的比较是通过使用a/d转换后的信号m_d的数字比较而进行的。该数字比较是使用已有的fpga等数字处理电路的一小部分而实现的。另一方面,能够削减在a/d转换设备1设置的模拟比较器及产生第2电平的模拟电路,因此作为整体而能够实现低成本化、低耗电化。

41.另外,在本实施方式,在检测到音信号(信号m_d)在规定期间持续地进入第2电平的范围时,使状态gs转移至增益高1级的状态。即使音信号(信号m_d)在短期变小,也不使放大器11的增益递增,能够防止增益切换频发。

42.另外,根据本实施方式,由增益存储器26对与多个状态的放大器11的增益的测量值相应的多个增益dg(gs)进行存储。另外,复原电路27以增益存储器26的与当前的状态gs相应的增益dg(gs)对信号m_d进行放大,作为信号o_d而输出。因此,即使在a/d转换设备1对状态进行切换,设备1整体的音信号的增益(即,信号o_d/信号i_a)不发生变化。

43.另外,在本实施方式,复原电路27将以增益dg(gs)放大后的信号m_d的一系列的样本的过渡性的噪声降低,因此即使放大器11的增益被切换,所输出的信号o_d也几乎不包含过渡性的噪声。

44.<应用例>

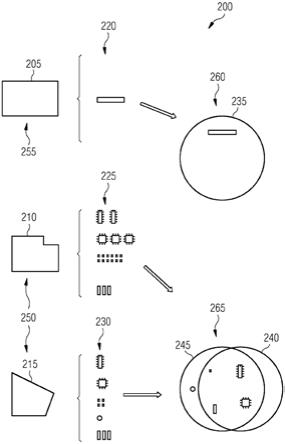

45.图3是表示包含与上述相同的a/d转换设备的音处理装置100的结构例的框图。该音处理装置100例如是数字混频器、信号处理引擎、音频装置、电子乐器、效果器、pc、智能机、平板终端等。接收模拟的音信号并转换为数字信号而进行处理的所有装置都能作为音处理装置100。

46.如图3所示,音处理装置100包含控制部110、ui(user interface)部120、存储部

130、a/d转换设备140、信号处理部150、dac(digital analog converter)160、以及将上述各要素相互连接的总线170。

47.控制部110是对音处理装置100整体进行控制的控制电路,例如由1个至多个cpu构成。ui部120具有如下部分等:操作部,其根据用户的操作而将其操作信息供给至控制部110;以及显示部,其在视觉上将来自控制部110的信息提供给用户。存储部130对由控制部110执行的程序、或由控制部110使用的控制信息等进行存储。a/d转换设备140是与图1的设备1相同的电路,将模拟的音信号i_a转换为数字的音信号o_d。信号处理部150针对从a/d转换设备140输出的音信号o_d,实施从控制部110指示的信号处理,将处理后的音信号输出至dac 160。dac 160将从信号处理部150输出的数字的音信号转换为模拟的音信号,输出至音处理装置100的外部的功率扬声器等放音装置。

48.该应用例的a/d转换设备140具有对参考电平vref1至vref4的值进行存储的4个寄存器r1至r4、和对状态gs的变化范围的上限值进行存储的寄存器ul(分别未图示)。寄存器r1及r4的设定值被作为vref1及vref4而供给至图1的数字比较器21及22。寄存器r2及r3的设定值通过未图示的d/a转换器而转换为模拟电压vref2及vref3,并供给至模拟比较器13及14。寄存器ul的设定值对在设备1中状态gs发生变化的范围进行限制。

49.图4~图6是表示在本应用例由控制部110执行的程序的处理内容的流程图。如果接通音处理装置100的电源,则控制部110将图4的流程图所示的主流程从存储部130读出而执行。

50.首先,控制部110执行初始设定(s101)。在该初始设定,控制部110将作为图2的fpga 20起作用的程序从存储部130读出,写入至a/d转换设备140的fpga。

51.接着,控制部110进行在音处理装置100发生的各种事件的检测(s102)、事件的有无的判断(s103)。

52.在s103没有任何事件的情况下,控制部110反复进行事件的检测(s102)及事件的有无的判断(s103)。

53.另一方面,在s103中存在任意事件的情况下,控制部110执行与该检测出的事件对应的事件处理(s104),之后,反复进行事件的检测(s102)及事件的有无的判断(s103)。

54.图5是在检测出由用户进行了对vref1至vref4中的任1个的参考电平的值进行变更的操作这一主旨的操作事件的情况下在s104执行的事件处理的流程图。在该事件处理,将寄存器r1至r4中的与所指定的参考电平对应的寄存器设定为与其操作相应的值。由此,图1的vref1至vref4中的与所设定的寄存器对应的参考电平被变更为与该设定后的值相应的电平。

55.图6是在检测出由用户进行了对状态gs的变化范围进行设定的操作这一主旨的操作事件的情况下在s104执行的事件处理的流程图。在该事件处理,将通过ui部120的操作而由用户指定的状态的变化范围的上限(图2的例子中为5)设定于a/d转换设备140的寄存器ul。在设定了寄存器ul的情况下,寄存器ul所示的上限值成为状态计数器25的状态gs的最大值。如果当前的状态gs达到ul所示的上限值,则即使进一步接收到递增指示,状态计数器25也不使状态gs递增。

56.<第2实施方式>

57.在第1实施方式的a/d转换设备,由fpga 20承担递增电路的作用,但递增电路不要

求高速性,因此在第2实施方式,使图3的控制部110承担该作用。

58.第2实施方式的a/d转换设备的结构基本上与图2相同,但fpga 20不具有递增电路(比较器21及22和递增判定部23)。另外,控制部110将图7所示的程序从存储部130读出而执行,由此承担递增电路的作用。另外,该a/d转换设备能够省略寄存器r1、r4、ul,具有寄存器r2及r3、用于将信号m_d的最大值和最小值交付给控制部110的寄存器rmax及rmin、和用于从控制部110接收递增信号的寄存器s。

59.图7是在检测出定期地发生的计时器的中断事件的情况下在s104执行的中断处理的流程图。在该中断处理,控制部110首先从a/d转换设备140的寄存器rmax和rmin取得在上次的中断处理至此次的中断处理为止的期间产生的信号m_d的max值和min值(s401)。

60.接着,控制部110判断参考电平vref1是否大于max值(s402),在该判断结果为“no”的情况下结束事件处理流程。在s402的判断结果为“yes”的情况下,控制部110判断min值是否大于参考电平vref4,在该判断结果为“no”的情况下结束事件处理流程。在s403的判断结果为“yes”的情况下,控制部110判断s402及s403的判断结果在规定期间是否持续地成为“yes”,在该判断结果为“no”的情况下,结束事件处理流程。对于持续期间,例如可以设置测量用计数器,作为测量用计数器的计数值而进行测量。更具体而言构成为,在上次的中断处理和此次的中断处理,在s403的判断都为“yes”时使该计数器递增,在上次为“no”而此次为“yes”时将该计数器重置为1。在该情况下,持续期间作为测量用计数器的计数值而进行测量。因此,在该计数值达到规定值时,能够判定为在规定期间持续。

61.s404的判断结果为“yes”的情况下,即,在信号m_d在规定期间维持了电平vref4及vref1间的电平的情况下,控制部110将递增指示写入至寄存器s(s405),结束事件处理流程。根据向寄存器s的递增指示,a/d转换设备的状态计数器25将状态gs变更为增益高1级的状态。但是,在从s401的读出max值和min值起至s405的递增指示为止的期间存在由递减电路发出的递减指示的情况下,状态计数器25忽略该递增指示,不对状态gs进行变更。

62.如上所示,在本实施方式,通过由控制部110执行程序而实现上述第1实施方式的数字比较器21及22和递增判定部23的功能。

63.在本实施方式,也得到与上述第1实施方式相同的效果。另外,在本实施方式,控制部110进行递增判定,因此存在如下优点,即,容易动态地对递增判定的参考电平、规定时间等条件进行变更。

64.以上,对本发明的第1及第2实施方式进行了说明,但本发明也可以有其他实施方式。例如,如下所述。

65.(1)也可以将4个参考电平中的vref2和vref3设为绝对值相同而极性相反的电平。同样地,也可以将vref1和vref4设为绝对值相同而极性相反的电平。如上所述,也可以将4个寄存器r1至r4减少为2个寄存器(例如,r1、r2)。

66.(2)在上述第1实施方式,进行了通过信号m_a的与第1电平的比较而使增益降低1个状态的控制,但也可以取代信号m_a而将对信号m_a全波整流后的信号与第1电平进行比较。另外,在上述第1实施方式,进行了通过信号m_d和第2电平的比较而使增益升高1个状态的控制,但也可以取代信号m_d而将对信号m_d全波整流后的信号与第2电平进行比较。在这些情况下,能够将用于前者的比较的模拟比较器、用于后者的比较的数字比较器的个数减半,但模拟比较器的负侧的响应时间长于正侧。

67.标号的说明

68.1、140

……

a/d转换设备,11

……

放大器,12

……

adc,13、14

……

模拟比较器,20

……

fpga,21、22

……

数字比较器,23

……

递增判定部,24

……

递减判定部,25

……

状态计数器,26

……

增益存储器,27

……

复原电路,100

……

音处理装置,110

……

控制部,120

……

ui部,130

……

存储部,140

……

a/d转换设备,150

……

信号处理部,160

……

dac,170

……

总线。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。