1.示例涉及用于校准时间交错模数转换器的装置、设备、方法和计算机程序。

背景技术:

2.ti

‑

adc(时间交错模数转换器)采用并联操作的若干低速子adc,以便实现所需的总采样率。因此,与使用单个adc时相比,每个子adc能够以更低的速度操作。ti

‑

adc可遭遇定时偏差(也称为定时失配),例如,各个子adc的时钟相位中的随机延迟。这可导致严重的性能劣化。

附图说明

3.以下将仅以举例的方式并参考附图来描述装备和/或方法的一些示例,其中

4.图1示出了根据本公开的各个方面的为4切片式(4x)ti

‑

adc生成的示例性测试信号;

5.图2示出了根据本公开的各个方面的在时间偏差校准之前和之后的4x

‑

ti adc的测量;

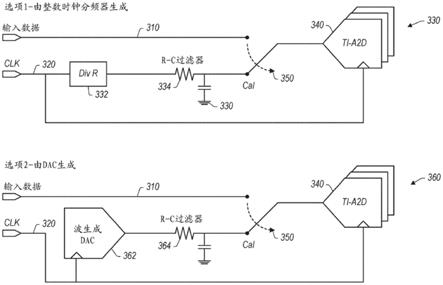

6.图3示出了根据本公开的各个方面的用于生成测试信号的信号生成电路的两个示例性具体实施;

7.图4示出了根据本公开的各个方面的布置成矩阵形式的20个样本的示例;

8.图5示出了测试信号值的估计的示例,其中对矩阵的列执行求平均值;

9.图6示出了根据本公开的各个方面的误差矩阵计算的示例;并且

10.图7示出了根据本公开的各个方面的斜率计算的示例。

具体实施方式

11.现在将参考附图更充分地描述各种示例,在附图中示出了一些示例。在附图中,为了清楚起见,线、层和/或区域的厚度可被放大。

12.因此,虽然另外的示例能够进行各种修改和另选形式,但是其一些特定示例在附图中示出并且随后将被详细描述。然而,该具体实施方式不将另外的示例限制于所描述的特定形式。另外的示例可涵盖落入本公开的范围内的所有修改、等同形式和另选形式。相同或相似的数量是指整个附图说明中相似或类似的元件,这些元件可在彼此比较时以相同或修改的形式实现,同时提供相同或类似的功能。

13.应当理解,当元件被称为“连接”或“耦接”到另一个元件时,元件可直接连接或耦接或经由一个或多个居间元件连接或耦接。如果使用“或”对两个元件a和b进行组合,则在没有另外明确或隐含地限定的情况下应当理解为公开了所有可能的组合,即仅a、仅b以及a和b。针对相同组合的另选词是“a和b中的至少一者”或“a和/或b”。加以必要的变更同样适用于多于两个元件的组合。

14.本文中所使用的术语仅仅是为了描述特定示例并非旨在对另外的示例进行限制。

每当使用单数形式诸如“一个”、“一种”和“该”并且仅使用没有被明确或隐含地限定为强制性的单个元件时,另外的示例也可使用多个元件来实现相同的功能。同样,当随后将功能描述为使用多个元件来实现时,另外的示例可使用单个元件或处理实体来实现相同的功能。还应当理解,术语“包括”在使用时是指定存在所陈述的特征、整数、步骤、操作、过程、动作、元件和/或部件,但是并不排除存在或添加一个或多个其他特征、整数、步骤、操作、过程、动作、元件、部件和/或其任何分组。

15.除非另有限定,否则所有术语(包括技术和科学术语)在本文中均以其在示例所属领域中的普通含义来使用。

16.示例提供了用于校准包括多个时间交错模数转换器电路的时间交错模数转换器的装置。该装置包括信号生成电路,该信号生成电路被配置为生成用于多个时间交错模数转换器电路的周期性校准信号。该周期性校准信号的周期是模数转换器的时钟信号的时钟周期的倍数。该装置包括处理电路,该处理电路被配置为获得模数转换器的输出信号,该输出信号基于由多个时间交错模数转换器电路对周期性校准信号进行的时间交错采样。该处理电路被配置为比较源自多个时间交错模数转换器电路中的不同模数转换器电路的周期性校准信号的一个或多个预定义部分(例如,多个预定义部分)的采样值。该处理电路被配置为基于对采样值的比较来确定多个时间交错模数转换器电路的偏差。

17.在至少一些示例中,该倍数不等于多个时间交错模数转换器电路中的时间交错模数转换器电路的数量。例如,周期性校准信号可具有等于r个时钟周期的周期,其中多个时间交错模数转换器电路包括ns个时间交错模数转换器电路。r和ns可以是互质数。这可使得每个时间交错模数转换器电路能够对周期性校准信号的每个预定义部分进行采样。

18.在至少一些示例中,处理电路被配置为确定周期性校准信号的一个或多个预定义部分中的每个预定义部分的平均采样值。该多个时间交错模数转换器电路的偏差可基于周期性校准信号的一个或多个预定义部分的采样值与周期性校准信号的一个或多个预定义部分中的每个预定义部分的平均采样值的偏差。这可确定周期性校准信号的平均型式。因此,处理电路可甚至在不了解周期性校准信号的确切形状的情况下工作。

19.在各种示例中,输出信号包括多个区段。该多个区段可各自包括采样值,该采样值基于该一个或多个预定义部分中的预定义部分与该多个时间交错模数转换器电路中的模数转换器电路的组合。例如,该多个区段可包括该一个或多个预定义部分与该多个时间交错模数转换器电路的所有组合的采样值。这可确保每个adc转换器电路已对每个预定义部分进行采样,从而能够计算平均信号。

20.每个区段可具有模数转换器的时钟信号的一个时钟周期的长度。这可有利于对采样的周期性校准信号进行处理。

21.在一些示例中,该信号生成电路被配置为将白噪声添加到周期性校准信号。该多个区段可包括该一个或多个预定义部分与该多个时间交错模数转换器电路的所有组合的多个采样值。a2d量化可限制区分类似振幅的能力,因此,其可限制偏差估计的分辨率。这可通过将热噪声

‑

白噪声添加到信号并对多次出现的每个样本求平均值来克服。

22.在各种示例中,信号生成电路包括低通滤波器电路,该低通滤波器电路被配置为对周期性校准信号进行低通滤波。至少一些示例示出了利用缺乏快速振幅变化的周期性校准信号来改善性能。

23.例如,信号生成电路可包括时钟分频器电路。该周期性校准信号可基于模数转换器的时钟信号的整数分频型式。时钟分频器是仅需要很少硬件修改的信号生成电路的具体实施。另选地,信号生成电路可包括数模转换电路,该数模转换电路被配置为基于模数转换器的时钟信号或基于模数转换器的时钟信号所基于的另一时钟信号来生成周期性校准信号。

24.在至少一些示例中,处理电路被配置为估计周期性校准信号的斜率。该处理电路可被配置为基于周期性校准信号的估计斜率来确定多个时间交错模数转换器电路的偏差。基于该斜率,可计算偏差,如图7a至图7c所示。

25.在实施方案中,处理电路可使用一个或多个处理单元、一个或多个处理设备、可与相应适配的软件一起操作的任何处理装置,诸如处理器、计算机或可编程硬件部件来实现。换句话讲,处理电路的所述功能也能够在软件中实现,该软件随后在一个或多个可编程硬件部件上执行。此类硬件部件可包括通用处理器、数字信号处理器(dsp)、微控制器等。

26.示例还提供了时间交错模数转换器,该时间交错模数转换器包括多个时间交错模数转换器电路和根据前述权利要求之一所述的用于校准该时间交错模数转换器的装置。该时间交错模数转换器还可包括用于在输入信号和周期性校准信号之间切换的切换电路。该切换电路可将输入信号或周期性校准信号提供给多个时间交错模数转换器电路。

27.示例还提供了用于校准包括多个时间交错模数转换装置的时间交错模数转换器的设备。该设备的部件被限定为部件装置,这些部件装置对应于上文所述装置的相应结构部件。该设备包括用于为多个时间交错模数转换器电路生成周期性校准信号的装置。该周期性校准信号的周期是模数转换器的时钟信号的时钟周期的倍数。该设备包括用于处理的装置,该用于处理的装置被配置用于获得模数转换器的输出信号。该输出信号基于由多个时间交错模数转换器电路对周期性校准信号进行的时间交错采样。用于处理的装置被配置用于比较源自多个时间交错模数转换装置中的不同模数转换装置的周期性校准信号的一个或多个预定义部分的采样值。用于处理的装置被配置为基于对采样值的比较来确定多个时间交错模数转换装置的偏差。

28.示例还提供了时间交错模数转换器,该时间交错模数转换器包括多个时间交错模数转换器电路和根据前述权利要求之一所述的用于校准所述时间交错模数转换器的设备。时间交错模数转换器还可包括用于在输入信号和周期性校准信号之间切换的装置,该用于切换的装置将输入信号或周期性校准信号提供给多个时间交错模数转换器电路。

29.示例还提供了用于校准包括多个时间交错模数转换器电路的时间交错模数转换器的对应方法。该方法包括为多个时间交错模数转换器电路生成周期性校准信号,该周期性校准信号的周期是模数转换器的时钟信号的时钟周期的倍数。该方法包括获得模数转换器的输出信号。输出信号基于由多个时间交错模数转换器电路对周期性校准信号进行的时间交错采样。该方法包括比较源自多个时间交错模数转换器电路中的不同模数转换器电路的周期性校准信号的一个或多个预定义部分的采样值。该方法包括基于对采样值的比较来确定多个时间交错模数转换器电路的偏差。

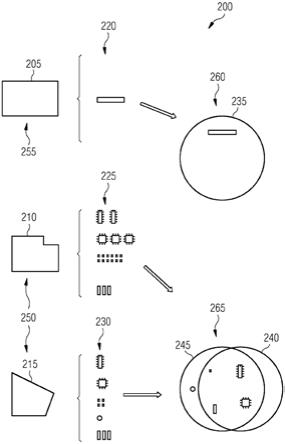

30.示例还提供了包括程序代码的机器可读存储介质,该程序代码在被执行时,使得机器执行所述方法。示例还提供了计算机程序,该计算机程序具有程序代码,该程序代码用于当计算机程序在计算机、处理器或可编程硬件部件上执行时执行所述方法。示例还提供

了包括机器可读指令的机器可读存储装置,所述机器可读指令在被执行时,如在本专利申请的上下文中介绍的来实现方法或实现装置。

31.本公开的示例提供了交错a2d(模数转换器)的简单时间偏差校正。

32.如今,许多应用需要高速高带宽的精确模数转换器(a2d)。实现此转换器的常见方式是使多个低速转换器进行时间交错(ti

‑

adc,时间交错模数转换器)。这可在每个特定adc动态范围的功率方面提供改进,然而不同转换器之间的失配可降低ti

‑

adc性能,因此校准可用于中到高分辨率adc,或用于高采样率adc。

33.在转换中引起误差的主要失配可以是dc(直流)偏移、增益和定时偏差。dc偏移和增益可易于通过简单且直接的校准来克服。定时偏差可能需要更多关注。切片之间的定时偏差可在输入bw(带宽)增加时限制adc性能。不同切片之间的时间偏差失配(这是固有的损害)可以是固定的,因为它们在输入bw增加时限制adc性能并且更难校准。

34.在未校准的情况下,该失配可在切片之间达到最多 /

‑

30ps,这可显著降低adc性能。示例提供了用于时间交错校准的(简单的)数字低功率、低面积且易于实现的方法。偏差可由自主逻辑部件测量和校准,该自主逻辑部件可能不需要生成准确信号如正弦波,或者甚至不需要了解用于校准的信号。

35.在一些系统中,可通过基于非常庞大的统计数据和相关性的在线校准、用于比较的附加a2d(以不同的采样率)、或通过实施单个跟踪/保持(t/h)/实施单个采样/保持(s/h)来消除时间偏差误差来提供此类校准。

36.此类方法可能需要以下中的至少一种:

37.‑

在线校准

‑

具有大量数字实现、较长收敛时间和额外功率消耗的复杂(校准)算法

38.‑

附加a2d

‑

模拟侧上的附加硬件(例如,用于校准的附加转换器)、高频时钟上的更多负载、信号驱动器上的负载

39.‑

常见的t/h

‑

用单个跟踪/保持以高频率对高bw信号进行采样消耗了较高的功率,并且在许多情况下,这不是有效的或甚至可行的解决方案。

40.‑

用于在线算法的较长收敛时间和额外功率消耗

41.‑

模拟设计挑战(例如,常见的s/h、t/h)

42.示例提供了用于校准切片之间的偏差失配的离线算法。为了避免需要了解确切的测试信号,可使用周期信号(例如,周期性校准信号),并且可比较切片之间的值,而不表征校准信号。换句话讲,示例提供了校准不同adc切片之间的偏差失配的自主离线算法。为了避免需要生成或了解确切的测试信号,可使用从采样时钟(例如,信号生成电路)生成的周期信号,并且可(例如,使用处理电路)比较所有切片的采样值。示例可能不需要表征校准信号,或不需要以准确的方式生成校准信号。

43.图1的图示出了对从采样时钟生成的周期信号进行采样的4个切片(1、2、3和4)(采样信号是输入时钟除以5)。图1示出了为4切片式adc生成的测试信号的示例(输入时钟除以r=5)。图1的附图标记110示出了采样信号(例如,周期性校准信号)的周期长度,在这种情况下,该周期长度是adc的时钟信号的5个时钟周期长,因为它基于输入时钟除以5。附图标记120示出了由四个切片采样的周期的长度,其不同于采样信号的周期110。附图标记130示出了采样信号,并且附图标记140示出了adc的时钟信号。在该示例中,存在由每个切片采样的五个不同的输入信号值(圆形、梯形、五边形、正方形和星形)。通过使用每个切片对相同

出现的测试信号的(例如,周期性校准信号的一个或多个预定义部分)进行采样,能够计算不同切片之间的系统时间误差。

44.该算法在8b 4x

‑

ti adc中以2.5gsps(千兆样本每秒)的采样率实施和测量。校准之前和之后的adc信号与时间偏差杂散在图2中示出。图2示出了时间偏差校准之前和之后的4x

‑

ti adc的测量。图2的图表的x轴示出了以mhz为单位的输入信号频率,y轴示出了以db为单位的信号与ti杂散。附图标记210示出了校准之后(校准后)的硅测量的曲线图,而附图标记220示出了校准之前(校准前)的硅测量的曲线图。

45.示例可使得能够在不运行长时间或复杂校准的情况下在大bw信号(5g,wigig)上使用高速率高性能的交错a2d。示例可实现时间偏差计算,而无需附加的硬件来生成准确的测试信号。时间偏差误差计算可以是简单、快速的,并且可能不需要大量逻辑。校准精度可能不受限制,并且可通过增加样本数来改善。在任何情况下,与其他方法相比,获得高精度所需的周期数可能较低。

46.在包括时间交错adc的adc中,可使用整数时钟分频器或dac和简单lpf滤波器(低通滤波器)。时钟分频器或dac可由采样时钟馈电,因此它们可易于在其他块之间被区分。

47.此外,如果监测adc的供电电压或电流,则可识别频率元素,该频率元素是采样时钟的互质分频。时间偏差校准可以是自主的和离线的,而不需要特定的硬件。

48.在至少一些示例中,算法可分解成三个操作:

49.1.生成测试信号(例如,周期性校准信号)

50.2.对多个周期进行采样和求平均值(例如,可获得和比较源自多个时间交错模数转换器电路中的不同模数转换器电路的周期性校准信号的一个或多个预定义部分的采样值)

51.3.计算偏差估计(例如,通过基于对采样值的比较来确定多个时间交错模数转换器电路的偏差)

52.生成精确的模拟测试信号是一项困难的任务。至少一些示例可使用未知的测试信号,这可有利于测试信号的生成。在一些示例中,可能存在来自该信号的仅两个要求:它应当是平滑且周期性的信号,这两者均可易于在硬件中实现。例如,信号可由以下两个操作中的一者生成(例如,由信号生成电路生成):

53.1.通过整数分频器对采样时钟进行分频并通过简单r

‑

c滤波器对其进行滤波

54.2.使用相同的采样时钟用dac生成波并使该波通过rc滤波器

55.也可以使用其他操作。

56.图3示出了用于生成测试信号的信号生成电路的两个示例性具体实施330和360。图3中330示出了选项1,其中信号生成电路330的整数时钟分频器332与r

‑

c

‑

lpf 334结合使用以基于时钟信号320生成测试信号。在校准期间,测试信号可经由逻辑或硬件切换电路350提供至ti

‑

a2d 340(其基于同一时钟信号310)。当不执行校准时,可将输入数据310提供给ti

‑

a2d 340(经由逻辑或硬件切换电路350)。另选地,可使用图3的选项2的信号生成电路360。图3中360示出了选项2,其中信号生成电路360的波生成dac(数模转换器)362与r

‑

c

‑

lpf 336结合使用,以基于时钟信号320生成测试信号。选项2的其他部件可类似于选项1来实现。如果使用选项1,则除了简单的整数分频器和r

‑

c之外,可能不需要附加的硬件。

57.例如,对于给定数量的切片ns(例如,8),测试信号可为周期性的,其中周期为r与

ns互质(例如,7、5、11)。该信号可能不是恒定的,因为其斜率是振幅和时间偏差之间的关联(如果仅可观察到振幅)。一种选项是生成具有较大std的信号(不饱和的)。在偏差计算中执行的动作之一可涉及从样本估计斜率,对于该动作,信号可能最好不具有非常大/快速的变化。换句话讲,测试信号可为低通的。生成此类周期信号的一些简单方式可以是将采样时钟除以r并使其通过lpf,或者使用具有周期性代码斜坡的较小dac(使用与adc相同的时钟),并且使其通过lpf。

58.至少一些示例可包括采样和求平均值(例如,获得输出信号并对输出信号进行采样,并且比较源自多个时间交错模数转换器电路中的不同模数转换器电路的周期性校准信号的一个或多个预定义部分的采样值)。由于ns和r是互质数,因此采样信号可以是周期性的,其中周期为ns

·

r。可在r个不同点处对信号进行采样,这些点中的每个点可由所有ns个切片进行采样。确切的采样时间取决于每个采样切片的时间偏差。图1示出了4x时间交错adc(ns=4)的测试信号,其中r=5(即,输入采样时钟除以5)。

59.a2d量化可限制区分类似振幅的能力,因此,其可限制偏差估计的分辨率。这可通过向信号添加热噪声

‑

白噪声并对多次出现的每个ns

·

r样本求平均值来克服。

60.至少一些示例可包括偏差估计(例如,偏差的确定)。一旦已获得ns

·

r平均样本,就可以更容易地将它们重新成形为矩阵(m

ns

×

r

)以用于数学表示。其中每个行表示一个切片,并且每个列表示测试信号中的点。图4示出了布置成矩阵形式的20个样本(r

×

ns=5

×

4)的示例。附图标记410至440分别表示由切片1、2、3和4(ns)采样的样本,而附图标记450至490表示由切片采样的点1至5(r)。

61.首先,对原始信号(v[r])的估计可通过对来自所有n

s

个切片的r点中的每一个求平均值来计算:

[0062][0063]

在图5和图6中并且在图7的矩阵700中,估计值用撇号表示。在图5和图6中,估计值由(估计值510的)附图标记515、516、517、518和519表示。图1示出了通过对矩阵的列执行求平均值来估计值的测试信号的示例。

[0064]

其次,可通过减去估计的原始测试信号来计算矩阵中的每个点的振幅误差(e[n,r]):

[0065]

e[n,r]=m[n,r]

‑

v[r]

[0066]

图6示出了误差矩阵计算e[n,r]的示例。附图标记610至640表示切片1至4的相应误差值。

[0067]

时间偏差误差可与振幅误差成比例。它们之间的比率可为信号的斜率(导数)。简单的导数估计为:

[0068][0069]

图7示出了斜率计算y’[n]的示例。图7示出了计算矩阵700、斜率702和图表704,该图表示出了电压误差720(振幅)与时间偏差710之间的比率。

[0070]

在之前使用的术语中,其可以是:

[0071][0072]

需注意,由于信号周期性,可在索引上使用调制操作。

[0073]

现在进行估计。在一些示例中,模型为:

[0074]

e[n,r]=d[r]

·

θ[n] ε[n,r]

[0075]

e[n]=d

·

θ[n] ε[n]

[0076]

最小二乘(ls)解为:

[0077][0078]

除了可能引入复杂性的除法部分之外,此类计算可易于在硬件中实现。由于分母不是[n]的函数,因此其计算中(或除法中)的任何误差可导致所有偏差估计中的共同增益误差。当使用迭代估计和校正时,此类误差可能不是问题(因为误差与残余偏差成比例)。当使用模拟校正时,可能已经需要迭代方法(因为它不需要对校正dac进行校准)。

[0079]

实施例1涉及用于校准包括多个时间交错模数转换器电路的时间交错模数转换器的装置。所述装置包括信号生成电路,所述信号生成电路被配置为为多个时间交错模数转换器电路生成周期性校准信号,所述周期性校准信号的周期是模数转换器的时钟信号的时钟周期的倍数。所述装置包括处理电路,所述处理电路被配置为:获得所述模数转换器的输出信号,所述输出信号基于由所述多个时间交错模数转换器电路对所述周期性校准信号进行的时间交错采样;比较源自所述多个时间交错模数转换器电路中的不同模数转换器电路的所述周期性校准信号的一个或多个预定义部分的采样值;以及基于对所述采样值的所述比较来确定所述多个时间交错模数转换器电路的偏差。

[0080]

在实施例2中,实施例1或本文所述的任何实施例的主题还可包括:所述倍数不等于多个时间交错模数转换器电路中的时间交错模数转换器电路的数量。

[0081]

在实施例3中,实施例1至2中的一者或本文所述的任何实施例的主题还可包括:所述周期性校准信号具有等于r个时钟周期的周期,其中所述多个时间交错模数转换器电路包括ns个时间交错模数转换器电路,其中r和ns是互质数。

[0082]

在实施例4中,实施例1至3中的一者或本文所述的任何实施例的主题还可包括:所述处理电路被配置为确定周期性校准信号的一个或多个预定义部分中的每个预定义部分的平均采样值,所述多个时间交错模数转换器电路的所述偏差基于所述周期性校准信号的所述一个或多个预定义部分的所述采样值与所述周期性校准信号的所述一个或多个预定义部分中的每个预定义部分的所述平均采样值的偏差。

[0083]

在实施例5中,实施例1至4中的一者或本文所述的任何实施例的主题还可包括:所述输出信号包括多个区段,所述多个区段各自包括采样值,所述采样值基于所述一个或多个预定义部分中的预定义部分与所述多个时间交错模数转换器电路中的模数转换器电路的组合。

[0084]

在实施例6中,实施例5或本文所述的任何实施例的主题还可包括:每个区段具有模数转换器的时钟信号的一个时钟周期的长度。

[0085]

在实施例7中,实施例5至6中的一者或本文所述的任何实施例的主题还可包括:所述多个区段包括所述一个或多个预定义部分与所述多个时间交错模数转换器电路的所有

组合的采样值。

[0086]

在实施例8中,实施例7或本文所述的任何实施例的主题还可包括:所述信号生成电路被配置为将白噪声添加到周期性校准信号,其中所述多个区段包括所述一个或多个预定义部分与所述多个时间交错模数转换器电路的所有组合的多个采样值。

[0087]

在实施例9中,实施例1至8中的一者或本文所述的任何实施例的主题还可包括:所述信号生成电路包括低通滤波器电路,所述低通滤波器电路被配置为对周期性校准信号进行低通滤波。

[0088]

在实施例10中,实施例1至9中的一者或本文所述的任何实施例的主题还可包括:所述信号生成电路包括时钟分频器电路,其中所述周期性校准信号基于模数转换器的时钟信号的整数分频型式。

[0089]

在实施例11中,实施例1至9中的一者或本文所述的任何实施例的主题还可包括:所述信号生成电路包括数模转换电路,所述数模转换电路被配置为基于所述模数转换器的所述时钟信号或基于所述模数转换器的所述时钟信号所基于的另一时钟信号来生成所述周期性校准信号。

[0090]

在实施例12中,实施例1至11中的一者或本文所述的任何实施例的主题还可包括:所述处理电路被配置为估计周期性校准信号的斜率,其中所述处理电路被配置为基于所述周期性校准信号的所估计的斜率来确定所述多个时间交错模数转换器电路的所述偏差。

[0091]

实施例13涉及时间交错模数转换器,所述时间交错模数转换器包括多个时间交错模数转换器电路和根据前述实施例中的一者所述的用于校准所述时间交错模数转换器的装置。

[0092]

在实施例14中,实施例13或本文所述的任何实施例的主题还可包括:所述时间交错模数转换器包括用于在输入信号与周期性校准信号之间切换的切换电路,所述切换电路向所述多个时间交错模数转换器电路提供所述输入信号或所述周期性校准信号。

[0093]

实施例15涉及用于校准包括多个时间交错模数转换装置的时间交错模数转换器的设备。所述设备包括用于为多个时间交错模数转换器电路生成周期性校准信号的装置,所述周期性校准信号的周期是模数转换器的时钟信号的时钟周期的倍数。所述设备包括用于处理的装置,所述装置被配置用于:获得所述模数转换器的输出信号,所述输出信号基于由所述多个时间交错模数转换器电路对所述周期性校准信号进行的时间交错采样;比较源自所述多个时间交错模数转换装置中的不同模数转换装置的所述周期性校准信号的一个或多个预定义部分的采样值;以及基于对所述采样值的所述比较来确定所述多个时间交错模数转换装置的偏差。

[0094]

实施例16涉及时间交错模数转换器,所述时间交错模数转换器包括多个时间交错模数转换器电路和根据实施例15所述的用于校准所述时间交错模数转换器的设备。

[0095]

实施例17涉及一种用于校准包括多个时间交错模数转换器电路的时间交错模数转换器的方法。所述方法包括为多个时间交错模数转换器电路生成周期性校准信号,所述周期性校准信号的周期是模数转换器的时钟信号的时钟周期的倍数。所述方法包括获得模数转换器的输出信号,所述输出信号基于由多个时间交错模数转换器电路对周期性校准信号进行的时间交错采样。所述方法包括比较源自多个时间交错模数转换器电路中的不同模数转换器电路的周期性校准信号的一个或多个预定义部分的采样值。所述方法包括基于对

采样值的比较来确定多个时间交错模数转换器电路的偏差。

[0096]

实施例19涉及一种机器可读存储介质,所述机器可读存储介质包括程序代码,所述程序代码在被执行时,使得机器执行根据权利要求17所述的方法。

[0097]

实施例19涉及一种计算机程序,所述计算机程序具有程序代码,所述程序代码用于当所述计算机程序在计算机、处理器或可编程硬件部件上执行时执行根据实施例17所述的方法。

[0098]

实施例20涉及一种机器可读存储装置,该机器可读存储装置包括机器可读指令,这些机器可读指令在被执行时,如任何未决权利要求或实施例所要求保护的来实现方法或实现装置。

[0099]

结合一个或多个先前详述的示例和附图所提及和描述的方面和特征也可与其他示例中的一个或多个组合,以便替换其他示例的相似特征或为了另外将该特征引入到其他示例中。

[0100]

当计算机程序在计算机或处理器上执行时,示例还可以是或涉及具有用于执行上述方法中的一个或多个的程序代码的计算机程序。可通过编程的计算机或处理器来执行各种上述方法的步骤、操作或过程。这些示例还可涵盖程序存储设备诸如数字数据存储介质,这些程序存储设备是机器可读、处理器可读或计算机可读的,并且对指令的机器可执行程序、处理器可执行程序或计算机可执行程序进行编码。这些指令执行或致使执行上述方法中的一些或全部动作。程序存储设备可包括或可以是例如数字存储器、磁性存储介质诸如磁盘和磁带、硬盘驱动器或光学可读数字数据存储介质。另外的示例还可涵盖被编程用于执行上述方法或(现场)可编程逻辑阵列((f)pla)或(现场)可编程门阵列((f)pga)的动作的计算机、处理器或控制单元,所述计算机、处理器或控制单元被编程用于执行上述方法的动作。

[0101]

说明书和附图仅示出本公开的原理。此外,本文所列举的所有示例原则上旨在明确地仅用于示例性目的,以帮助读者理解本公开的原理以及由一个或多个发明人为推进本领域所贡献的概念。本文中列举本公开的原理、方面和示例的所有陈述以及它们的具体示例均旨在包括它们的等同形式。

[0102]

表示为执行特定功能的“用于...的装置”的功能框可指被配置为执行特定功能的电路。因此,“用于...的装置”可被实现为“被配置为或适用于...的装置”,诸如被配置为或适用于相应任务的设备或电路。

[0103]

在图中示出的各种元件的功能包括标记为“装置”、“用于提供信号的装置”、“用于生成信号的装置”等的任何功能框,这些功能框可以专用硬件的形式实现,诸如“信号提供器”、“信号处理单元”、“处理器”、“控制器”等,以及能够与适当的软件相关联地执行软件的硬件。当由处理器提供时,这些功能可由单个专用处理器、单个共享处理器或多个单独处理器提供,可共享其中一些或全部。然而,术语“处理器”或“控制器”远不限于唯一能够执行软件的硬件,但是可包括数字信号处理器(dsp)硬件、网络处理器、专用集成电路(asic)、现场可编程门阵列(fpga)、用于存储软件的只读存储器(rom)、随机存取存储器(ram)和非易失性存储器。还可包括常规和/或定制的其他硬件。

[0104]

框图可例如示出实现本公开的原理的高电平电路图。类似地,流程图、流程图表,状态转变图、伪代码等可表示各种过程、操作或步骤,这些过程、操作或步骤可例如基本上

表示在计算机可读介质中,并且因此由计算机或处理器执行,无论是否明确地示出了此类计算机或处理器。可由具有用于执行这些方法的每个相应动作的装置的设备来实现本说明书或权利要求中所公开的方法。

[0105]

应当理解,本说明书或权利要求中所公开的多种动作、过程、操作、步骤或功能的公开内容可不理解为是在特定顺序内,除非例如因为技术原因另外明确或隐含地说明。因此,多种动作或功能的公开内容将不会把这些动作或功能局限于特定顺序,除非此类动作或功能因为技术原因而不可互换。此外,在一些示例中,单个动作、功能、过程、操作或步骤可分别包括或可分为多个子动作、子功能、子过程、子操作或子步骤。除非明确排除,否则此类子动作可被包括在内并且为该单个动作的公开内容的一部分。

[0106]

此外,据此将以下权利要求并入具体实施方式中,其中每项权利要求可独立地作为单独的示例。虽然每项权利要求可独立地作为单独的示例,但应当指出的是,尽管可在权利要求中提及从属权利要求与一个或多个其他权利要求的特定组合,但其他示例也可包括从属权利要求与每个其他从属或独立权利要求的主题的组合。除非说明不旨在使用特定组合,否则本文明确提出此类组合。此外,还旨在同时将权利要求的特征包括在任何其他独立权利要求中,即使该权利要求没有直接依赖于独立权利要求。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。