1.本发明涉及兼容于cmos集成电路设计与制造技术领域,具体为一种适用于高集成低功耗cmos集成电路设计和制造技术的双掺杂源漏单晶体管同或门及制造方法。

背景技术:

2.基于现有的cmos场效应晶体管技术,在集成工艺确定的前提下,为实现特定功能,在设计中所采用的晶体管数量越多,实现该功能所需要占用的芯片面积也相应越大。目前基于现有技术的同或门门通常需要利用由4个或以上互补型金属氧化物半导体场效应晶体管所组成的异或门通过连接由2个晶体管所组成的反相器,通过对异或门逻辑取非来实现,因此至少需要6个及以上晶体管,利用更少的晶体管实现同或门逻辑有助于进一步简化集成电路基本门电路的单元结构,在相同集成工艺技术和相同芯片面积上实现更多的同或门以提升集成度。

技术实现要素:

3.本发明的目的在于提供了一种双掺杂源漏单晶体管同或门及制造方法,使集成电路实现用最少数量的晶体管数量,即单个晶体管来实现同或门逻辑功能。

4.为实现上述目的,本发明提供如下技术方案:双掺杂源漏单晶体管同或门,包含soi晶圆的硅衬底,soi晶圆的硅衬底上方为soi晶圆的衬底绝缘层,soi晶圆的衬底绝缘层为绝缘材料层,soi晶圆的衬底绝缘层的上方为半导体薄膜区、可互换n型源漏区a、可互换p型源漏区a、可互换n型源漏区b、可互换p型源漏区b、绝缘介质层、栅电极绝缘层、栅电极a和栅电极b;半导体薄膜区为半导体材料,半导体薄膜区的上表面和前后侧表面的左右两侧与栅电极绝缘层相互接触;半导体薄膜区的上表面和前后侧表面的中央部分与绝缘介质层相互接触;

5.可互换n型源漏区a和可互换p型源漏区a分别为掺有n型杂质和p型杂质的半导体区域;可互换n型源漏区a和可互换p型源漏区a同时位于半导体薄膜区的左侧,并与半导体薄膜区相互接触;

6.可互换n型源漏区a的前侧表面和可互换p型源漏区a的后侧表面与绝缘介质层相互接触;可互换n型源漏区a的后侧表面和可互换p型源漏区a的前侧表面与防耗尽隔离层a相互接触;防耗尽隔离层a为绝缘介质材料;

7.可互换n型源漏区a和可互换p型源漏区a的上表面的左侧与可互换源漏电极a相互接触,可互换n型源漏区a和可互换p型源漏区a的上表面的右侧与绝缘介质层相互接触;

8.可互换n型源漏区b和可互换p型源漏区b分别为掺有n型杂质和p型杂质的半导体区域;可互换n型源漏区b和可互换p型源漏区b同时位于半导体薄膜区的右侧,并与半导体薄膜区相互接触;

9.可互换n型源漏区b的前侧表面和可互换p型源漏区b的后侧表面与绝缘介质层相互接触;可互换n型源漏区b的后侧表面和可互换p型源漏区b的前侧表面与防耗尽隔离层b

相互接触;防耗尽隔离层b为绝缘介质材料;

10.可互换n型源漏区b和可互换p型源漏区b的前后两侧表面与绝缘介质层相互接触,可互换n型源漏区b和可互换p型源漏区b的上表面的右侧与可互换源漏电极b相互接触,可互换n型源漏区b和可互换p型源漏区b的上表面的左侧与绝缘介质层相互接触;

11.绝缘介质层为绝缘介质材料;栅电极绝缘层为绝缘介质材料,栅电极绝缘层的左侧部分的上表面和前后侧表面与栅电极a相互接触;栅电极绝缘层的右侧部分的上表面和前后侧表面与栅电极b相互接触;栅电极a和栅电极b为金属、合金、多晶硅或金属硅化物;栅电极a与栅电极绝缘层的左侧部分的上表面以及前后侧表面相互接触,栅电极a通过栅电极绝缘层与半导体薄膜区彼此相互绝缘隔离,栅电极a通过绝缘介质层与可互换源漏电极a和可互换源漏电极b彼此绝缘隔离;栅电极b与栅电极绝缘层的右侧部分的上表面以及前后侧表面相互接触,栅电极b通过栅电极绝缘层与半导体薄膜区彼此相互绝缘隔离,栅电极b通过绝缘介质层与可互换源漏电极a和可互换源漏电极b彼此绝缘隔离;栅电极a与栅电极b通过绝缘介质层彼此绝缘隔离;可互换源漏电极a为金属、合金或金属硅化物,可互换源漏电极a的下表面与可互换n型源漏区a和可互换p型源漏区a的上表面的左侧相互接触并形成欧姆类型的反阻挡层接触;可互换源漏电极b为金属、合金或金属硅化物,可互换源漏电极b的下表面与可互换n型源漏区b和可互换p型源漏区b的上表面的右侧相互接触并形成欧姆类型的反阻挡层接触。

12.与现有技术相比,本发明的有益效果是:

13.1.所实现的同或门结构简单

14.本发明所述的双掺杂源漏单晶体管同或门及制造方法,该电路仅需一个具有双掺杂源漏结构的晶体管即可实现同或门逻辑,因此极大地简化了同或门电路结构的复杂度,易于集成电路集成度的提升。

15.2.可实现双向同或门逻辑传输功能:

16.本发明所述的双掺杂源漏单晶体管同或门及制造方法,具有左右对称的结构特征,可互换源漏电极a和可互换源漏电极b可彼此互换,即可互换源漏电极a和可互换源漏电极b之中的任意一端与电源电压输入端连接,另一端与同或门输出端连接均可输出同或门。

附图说明

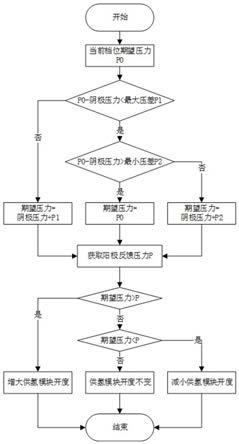

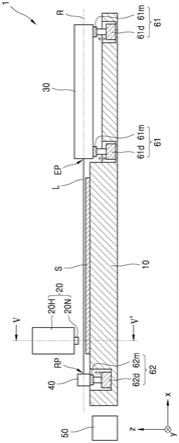

17.图1为本发明双掺杂源漏单晶体管同或门的俯视图;

18.图2为本发明双掺杂源漏单晶体管同或门的沿图1虚线a的剖面图;

19.图3为本发明双掺杂源漏单晶体管同或门的沿图1虚线b的剖面图;

20.图4为本发明双掺杂源漏单晶体管同或门的沿图1虚线c的剖面图;

21.图5为本发明双掺杂源漏单晶体管同或门的沿图1虚线d的剖面图;

22.图6为本发明双掺杂源漏单晶体管同或门的电路连接图。

23.图7为步骤一的俯视图;

24.图8为步骤一的沿虚线a的剖面图;

25.图9为步骤一的沿虚线b的剖面图;

26.图10为步骤二的俯视图;

27.图11为步骤二的沿虚线a的剖面图;

28.图12为步骤二的沿虚线b的剖面图;

29.图13为步骤二的沿虚线c的剖面图;

30.图14为步骤二的沿虚线d的剖面图;

31.图15为步骤三的俯视图;

32.图16为步骤三的沿虚线a的剖面图;

33.图17为步骤三的沿虚线b的剖面图;

34.图18为步骤三的沿虚线c的剖面图;

35.图19为步骤三的沿虚线d的剖面图;

36.图20为步骤三的沿虚线e的剖面图;

37.图21为步骤四的俯视图;

38.图22为步骤四的沿虚线a的剖面图;

39.图23为步骤五的俯视图;

40.图24为步骤五的沿虚线a的剖面图;

41.图25为步骤五的沿虚线b的剖面图;

42.图26为步骤五的沿虚线c的剖面图;

43.图27为步骤五的沿虚线d的剖面图;

44.图28为步骤五的沿虚线e的剖面图;

45.图29为步骤六的俯视图;

46.图30为步骤六的的沿虚线a的剖面图;

47.图31为步骤六的的沿虚线b的剖面图;

48.图32为步骤六的的沿虚线c的剖面图;

49.图33为步骤六的的沿虚线d的剖面图;

50.图34为步骤七的俯视图;

51.图35为步骤七的沿虚线a的剖面图;

52.图36为步骤七的沿虚线b的剖面图;

53.图37为步骤七的沿虚线c的剖面图;

54.图38为步骤八的的俯视图;

55.图39为步骤八的沿虚线a的剖面图;

56.图40为步骤八的沿虚线b的剖面图;

57.图41为步骤八的沿虚线c的剖面图;

58.图42为步骤八的沿虚线d的剖面图;

59.图43为步骤九的的俯视图;

60.图44为步骤九的沿虚线a的剖面图;

61.图45为步骤九的沿虚线b的剖面图;

62.图46为步骤九的沿虚线c的剖面图;

63.图47为步骤九的沿虚线d的剖面图;

64.图48为步骤九的沿虚线e的剖面图;

65.图49为步骤九的沿虚线e的剖面图;

66.图50为步骤九的沿虚线e的剖面图;

67.1、soi晶圆的硅衬底;2、soi晶圆的衬底绝缘层;3、半导体薄膜区;4、可互换n型源漏区a;5、可互换p型源漏区a;6、可互换n型源漏区b;7、可互换p型源漏区b;8、绝缘介质层;9、栅电极绝缘层;10、栅电极a;11、栅电极b;12、可互换源漏电极a;13、可互换源漏电极b;14、防耗尽隔离层a;15、防耗尽隔离层b;16、信号输入端a;17、和信号输入端b;18、电源电压输入端;19、同或门输出端。

具体实施方式

68.请参阅图1

‑

5,本发明提供一种技术方案:双掺杂源漏单晶体管同或门,包含soi晶圆的硅衬底1,其特征在于:soi晶圆的硅衬底1上方为soi晶圆的衬底绝缘层2,soi晶圆的衬底绝缘层2为绝缘材料层,soi晶圆的衬底绝缘层2的上方为半导体薄膜区3、可互换n型源漏区a4、可互换p型源漏区a5、可互换n型源漏区b6、可互换p型源漏区b7、绝缘介质层8、栅电极绝缘层9、栅电极a10和栅电极b11;半导体薄膜区3为半导体材料,半导体薄膜区3的上表面和前后侧表面的左右两侧与栅电极绝缘层9相互接触;半导体薄膜区3的上表面和前后侧表面的中央部分与绝缘介质层8相互接触;可互换n型源漏区a4和可互换p型源漏区a5分别为掺有n型杂质和p型杂质的半导体区域;可互换n型源漏区a4和可互换p型源漏区a5同时位于半导体薄膜区3的左侧,并与半导体薄膜区3相互接触;可互换n型源漏区a4的前侧表面和可互换p型源漏区a5的后侧表面与绝缘介质层8相互接触;可互换n型源漏区a4的后侧表面和可互换p型源漏区a5的前侧表面与防耗尽隔离层a14相互接触;防耗尽隔离层a14为绝缘介质材料;可互换n型源漏区a4和可互换p型源漏区a5的上表面的左侧与可互换源漏电极a12相互接触,可互换n型源漏区a4和可互换p型源漏区a5的上表面的右侧与绝缘介质层8相互接触;可互换n型源漏区b6和可互换p型源漏区b7分别为掺有n型杂质和p型杂质的半导体区域;可互换n型源漏区b6和可互换p型源漏区b7同时位于半导体薄膜区3的右侧,并与半导体薄膜区3相互接触;可互换n型源漏区b6的前侧表面和可互换p型源漏区b7的后侧表面与绝缘介质层8相互接触;可互换n型源漏区b6的后侧表面和可互换p型源漏区b7的前侧表面与防耗尽隔离层b15相互接触;防耗尽隔离层b15为绝缘介质材料;可互换n型源漏区b6和可互换p型源漏区b7的上表面的右侧与可互换源漏电极b13相互接触,可互换n型源漏区b6和可互换p型源漏区b7的上表面的左侧与绝缘介质层8相互接触;绝缘介质层8为绝缘介质材料;栅电极绝缘层9为绝缘介质材料,栅电极绝缘层9的左侧部分的上表面和前后侧表面与栅电极a10相互接触;栅电极绝缘层9的右侧部分的上表面和前后侧表面与栅电极b11相互接触;栅电极a10和栅电极b11为金属、合金、多晶硅或金属硅化物;栅电极a10与栅电极绝缘层9的左侧部分的上表面以及前后侧表面相互接触,栅电极a10通过栅电极绝缘层9与半导体薄膜区3彼此相互绝缘隔离,栅电极a10通过绝缘介质层8与可互换源漏电极a12和可互换源漏电极b13彼此绝缘隔离;栅电极b11与栅电极绝缘层9的右侧部分的上表面以及前后侧表面相互接触,栅电极b11通过栅电极绝缘层9与半导体薄膜区3彼此相互绝缘隔离,栅电极b11通过绝缘介质层8与可互换源漏电极a12和可互换源漏电极b13彼此绝缘隔离;栅电极a10与栅电极b11通过绝缘介质层8彼此绝缘隔离;可互换源漏电极a12为金属、合金或金属硅化物,可互换源漏电极a12的下表面与可互换n型源漏区a4和可互换p型源漏区a5的上表面的左侧相互接触并形成欧姆类型的反阻挡层接触;可互换源漏电极b13为金属、合金或金属硅化物,可互换源漏电极b13的下表面与可互换n型源漏区b6和可互换p型源漏区b7的上表面的

右侧相互接触并形成欧姆类型的反阻挡层接触。

69.如图6所示,本发明还提供一种双掺杂源漏单晶体管同或门的使用方法,栅电极a10与同或门的两个信号输入端,即信号输入端a16和信号输入端b17中的一端相互连接,同时栅电极b11与同或门的两个信号输入端,即与信号输入端a16和信号输入端b17中与栅电极a10连接之外的另一端相互连接;可互换源漏电极a12与电源电压输入端18和同或门输出端19中的一端相互连接,同时可互换源漏电极b13与电源电压输入端18和同或门输出端19中与可互换源漏电极a12连接之外的另一端相互连接。

70.当信号输入端a16和信号输入端b17同时输入高电平,栅电极a10和栅电极b11同时处于高电位,且当可互换源漏电极a12和可互换源漏电极b13分别与电源电压输入端18和同或门输出端19中的其中一端相互连接时,半导体薄膜区3在栅电极a10和栅电极b11的共同作用下,通过电场效应在内部所形成电子沟道,使电子可以从可互换源漏电极a12和可互换源漏电极b13之中处于电势较低的一端,流至可互换n型源漏区a4和可互换n型源漏区b6之中同样处于电势较低的一端,并经过半导体薄膜区3内部形成电子沟道流向可互换n型源漏区a4和可互换n型源漏区b6之中处于电势较高的一端,再从可互换源漏电极a12和可互换源漏电极b13之中处于电势较高的一端流出,双掺杂源漏单晶体管同或门此时处于低阻状态,对同或门输出端19输出高电平;当信号输入端a16和信号输入端b17同时输入低电平,栅电极a10和栅电极b11同时处于低电位,且当可互换源漏电极a12和可互换源漏电极b13分别与电源电压输入端18和同或门输出端19中的其中一端相互连接时,半导体薄膜区3在栅电极a10和栅电极b11的共同作用下,通过电场效应在内部形成空穴沟道,使空穴可以从可互换源漏电极a12和可互换源漏电极b13之中处于电势较高的一端,流至可互换p型源漏区a5和可互换p型源漏区b7之中同样处于电势较高的一端,并经过半导体薄膜区3内部所形成空穴沟道流向可互换p型源漏区a5和可互换n型源漏区b6之中处于电势较低的一端,再从可互换源漏电极a12和可互换源漏电极b13之中处于电势较低的一端流出,双掺杂源漏单晶体管同或门此时处于低阻状态,对同或门输出端19输出高电平;当信号输入端a16和信号输入端b17其中一个输入高电平,另一个输入低电平,且当可互换源漏电极a12和可互换源漏电极b13分别与电源电压输入端18和同或门输出端19中的其中一端相互连接时,栅电极a10和栅电极b11其中一个处于高电平,另一个处于低电平,栅电极a10和栅电极b11之中处于高电平的一个可以通过电场效应阻挡“空穴”从可互换源漏电极a12和可互换源漏电极b13之中处于电势较高的一端流向电势较低的一端,栅电极a10和栅电极b11之中处于低电平的一个可以通过电场效应阻挡“电子”从可互换源漏电极a12和可互换源漏电极b13之中处于电势较低的一端流向电势较低的一端,双掺杂源漏单晶体管同或门此时处于高阻状态,对同或门输出端19输出低电平。

71.该电路仅需一个具有双掺杂源漏结构的晶体管即可实现同或门逻辑,结构左右对称,可互换源漏电极a12和可互换源漏电极b13可彼此互换,即可互换源漏电极a12和可互换源漏电极b13之中的任意一端与电源电压输入端18连接,另一端与同或门输出端19连接均可输出同或门。

72.本发明还提供一种双掺杂源漏单晶体管同或门的制造方法,不仅限于此方法,其可在soi晶圆硅衬底上实现的一种具体制造步骤如下:

73.步骤一:请参阅图7

‑

9,提供一个soi晶圆,最下方为soi晶圆的硅衬底1,硅衬底的

上面是soi晶圆的衬底绝缘层2,soi晶圆的衬底绝缘层2的上表面为半导体薄膜,通过光刻、刻蚀和淀积工艺,初步形成半导体薄膜3;

74.步骤二:请参阅图10

‑

14,通过离子注入工艺,分别初步形成可互换n型源漏区a4、可互换p型源漏区a5、可互换n型源漏区b6、可互换p型源漏区b7;

75.步骤三:请参阅图15

‑

20,通过刻蚀工艺,刻蚀掉步骤二所生成的可互换n型源漏区a4、可互换p型源漏区a5之间的部分区域,刻蚀掉步骤二所生成的可互换n型源漏区b6、可互换p型源漏区b7之间的部分区域,进一步形成可互换n型源漏区a4、可互换p型源漏区a5、可互换n型源漏区b6、可互换p型源漏区b7,并为防耗尽隔离层a14和防耗尽隔离层b15预留空间,再通过淀积工艺,在步骤二基础之上淀积绝缘介质层,再通过平坦化处理至露出半导体薄膜3,形成防耗尽隔离层a14和防耗尽隔离层b15,初步形成绝缘介质层8,再通过刻蚀工艺刻蚀掉半导体薄膜3前后表面左右两侧部分的绝缘介质层至露出soi晶圆的衬底绝缘层2,进一步形成绝缘介质层8;

76.步骤四:请参阅图21

‑

22,通过淀积工艺,在步骤三基础之上淀积栅电极绝缘层,再通过平坦化处理至露出半导体薄膜3,初步形成栅电极绝缘层9;

77.步骤五:请参阅图23

‑

28,通过淀积工艺,在步骤四基础之上淀积绝缘介质层,进行平坦化处理后,再通过光刻、刻蚀工艺对左右两侧中间部分进行刻蚀至露出步骤四所形成的栅电极绝缘层9和栅电极绝缘层9的上下两侧部分之间的半导体薄膜3的上表面;

78.步骤六:请参阅图29

‑

33,通过淀积工艺,在步骤五基础之上淀积栅电极绝缘层,再通过平坦化处理至露出绝缘介质层8的上表面,再通过光刻、刻蚀工艺去掉栅电极绝缘层9的左右两侧部分的上下两侧部分至露出衬底绝缘层2,再通过淀积工艺淀积金属、合金、多晶硅或金属硅化物,再通过平坦化处理至露出栅电极绝缘层9,初步形成栅电极a10和栅电极b11;

79.步骤七:请参阅图34

‑

37,通过淀积工艺,在步骤六基础之上淀积栅电极绝缘层,进行平坦化处理后,再通过光刻、刻蚀工艺对左右两侧中间部分进行刻蚀至露出步骤六所形成的栅电极绝缘层9、栅电极a10和栅电极b11的上表面;

80.步骤八:请参阅图38

‑

42,通过淀积工艺,在步骤七基础之上淀积金属、合金、多晶硅或金属硅化物,再通过平坦化处理至露出绝缘介质层8的上表面,进一步形成栅电极a10和栅电极b11;

81.步骤九:请参阅图43

‑

50,通过刻蚀工艺,在步骤八基础之上刻蚀掉部分绝缘介质层8至露出可互换n型源漏区a4和可互换p型源漏区a5左侧的上表面,及可互换n型源漏区b6和可互换p型源漏区b7右侧的上表面;

82.步骤十:请参阅图1

‑

5,通过淀积工艺,在步骤九基础之上淀积金属、合金、多晶硅或金属硅化物,再通过平坦化处理至露出绝缘介质层8的上表面,形成可互换源漏电极a12和可互换源漏电极b13。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。