1.本发明涉及半导体技术领域,具体是陶瓷基板。

背景技术:

2.陶瓷基板具有热导率高、耐热性好、热膨胀系数低、机械强度高、绝缘性好、耐腐蚀、抗辐射等特点,在电子器件封装中得到广泛应用,根据制备原理和工艺的不同,目前主流产品可以分为厚膜印刷陶瓷基板(thick printing ceramic substrate,tpc)、直接键合铜陶瓷基板(direct bonded copper ceramic substrate,dbc)、活性金属焊接陶瓷基板(active metal brazing ceramic substrate,amb)等。小型化的高压大功率模块是半导体器件重要发展方向之一,在半导体器件设计中,随着尺寸减小,芯片功率密度急剧增加,对模块散热封装可靠性提出了新的要求。

3.现有的陶瓷基板的制备方法往往是单纯的将金属层与瓷片的复合,瓷片固定在金属层上,这种结构大大的限制了后期封装件的厚度,且不易于保证对芯片的相对固定效果。而且,芯片的散热区域仅为正面金属层向外传动,对于芯片的散热效果不佳。

技术实现要素:

4.针对现有技术存在的问题,本发明提供一种嵌埋式陶瓷基板的制备方法,以解决以上至少一个技术问题。

5.为了达到上述目的,本发明提供了一种嵌埋式陶瓷基板的制备方法,其特征在于,包括如下步骤:

6.步骤一,正面金属层以及背面金属层预处理;

7.所述正面金属层包括至少两层金属片,至少两层金属片包括靠近瓷片的第一金属片,至少两层金属片中除了第一金属片的其余的金属片开设有至少一个上下贯穿的贯穿孔;

8.步骤二,将正面金属层、瓷片以及背面金属层从上至下依次堆叠后进行真空烧结。

9.所述贯穿孔用于内嵌芯片。

10.本专利通过在正面金属层上开设有贯穿孔,便于实现了对芯片的限位固定效果。相应的减薄了后期封装件的厚度。此外,可以实现芯片的热量从周向向外以及向下区域的金属层散热,大大的提高的散热范围。

11.进一步优选的,所述第一金属片上通过精雕机开设有盲孔。

12.进一步优选的,所述盲孔的深度为第一金属片深度的2/3。

13.进一步优选地,所述贯穿孔的横截面为正方形、长方形、圆形、五边形、六边形中的一种或几种。

14.进一步优选地,所述正面金属层包括从下至上依次设置的第一金属片、第二金属片以及第三金属片;

15.所述第一金属片的厚度为0.2mm

‑

0.4mm,所述第二金属片的厚度为0.2mm

‑

0.3mm,

所述第三金属片的厚度为0.2mm

‑

0.3mm,所述背面金属层的厚度为0.5mm

‑

1.0mm。

16.进一步优选地,所述正面金属层为铜层或铝层。

17.进一步优选地,所述背面金属层为铜层或铝层。

18.进一步优选的,步骤一中,正面金属层的所有金属片从上至下堆叠后扩散焊接相连,步骤二中,正面金属层、瓷片以及背面金属层真空钎焊相连。

19.所述瓷片与所述正面金属层以及背面金属层之间涂覆有钎料。

20.或者,步骤二中,正面金属层的所有金属片、瓷片以及背面金属层从上至下依次堆叠后真空钎焊;

21.所述瓷片与所述第一金属片以及背面金属层之间涂覆有钎料。

22.进一步优选地,所述正面金属层包括从下至上依次设置的第一金属片、第二金属片以及第三金属片;

23.所述第二金属片以及所述第三金属片上均开设有所述贯穿孔,且所述第二金属片以及所述第三金属片上的贯穿孔相互导通;

24.所述第二金属片的贯穿孔的面积要小于第三金属片的贯穿孔的面积。

25.便于实现芯片的限位。

26.一种嵌埋式陶瓷基板的制备方法,其特征在于,包括如下步骤:

27.步骤一,正面金属层以及背面金属层预处理;

28.所述正面金属层包括至少两层金属片,至少两层金属片包括靠近瓷片的第一金属片,至少两层金属片中除了第一金属片的其余的金属片开设有至少一个上下贯穿的贯穿孔;

29.步骤二,第一金属片、瓷片以及背面金属层从上至下依次堆叠后真空钎焊烧结;

30.步骤三,对第一金属片进行蚀刻,制成图案,使得所述第一金属片上设有内凹的内凹部,且所述第一金属片上还开设有上下贯穿的回形槽,所述回形槽位于所述内凹部的外围,所述回形槽用于将内凹部呈孤岛状设置在第一金属片;

31.步骤四,将步骤三制成的金属基板的上方依次堆叠正面金属层的其余金属片后,真空扩散焊接;

32.所述贯穿孔与所述内凹部上下导通。

33.通过优化制备方法,为了避免内凹部的结构从第一金属片上脱离、移位,本专利采用两步烧结,第一金属片的图案制备方式为先烧结,后制备,第一次烧结将第一金属片、瓷片与背面金属层真空钎焊在一起,然后在第一金属片上金属层蚀刻制成图案,将金属基板再与第二金属片、第三金属片真空扩散焊接在一起。

34.步骤二中,真空钎焊烧结的温度控制在700℃

‑

940℃,真空度小于0.01pa,烧结时间60min

‑

540min。

35.步骤四中,真空扩散焊接的工艺参数:扩散焊烧结温度为500℃

‑

900℃,真空度小于0.1pa,烧结时间10min

‑

540min。

36.进一步优选的,所述内凹部的深度为第一金属片深度的2/3。

37.进一步优选地,所述贯穿孔的横截面为正方形、长方形、圆形、五边形、六边形中的一种或几种。

38.进一步优选地,所述第一金属片的厚度为0.2mm

‑

0.4mm,所述第二金属片的厚度为

0.2mm

‑

0.3mm,所述第三金属片的厚度为0.2mm

‑

0.3mm,所述背面金属层的厚度为0.5mm

‑

1.0mm。

39.进一步优选地,所述正面金属层为铜层或铝层。

40.进一步优选地,所述背面金属层为铜层或铝层。

41.有益效果是:1)能够降低封装模块的厚度,从而降低芯片的封装密度;2)嵌埋式覆铜基板能够为芯片提供更好的散热性,并提供芯片定位槽,可防止芯片焊接时位置偏移。

附图说明

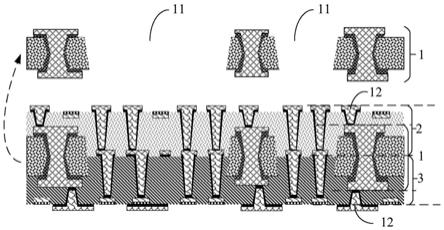

42.图1为本发明具体实施例1的流程图;

43.图2为本发明具体实施例1的结构一的立体结构示意图;

44.图3为本发明具体实施例1的结构一的正面金属层的爆炸分解图;

45.图4为本发明具体实施例1的结构二的立体结构示意图;

46.图5为本发明具体实施例1的结构二的第一金属片的结构示意图;

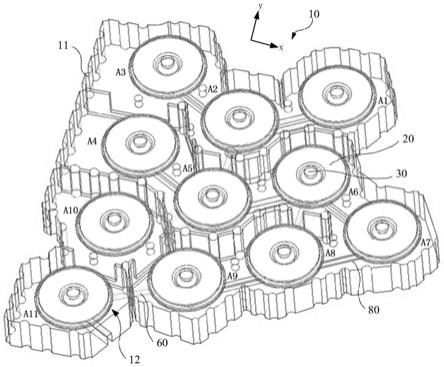

47.图6为本发明具体实施例2的产物的立体结构示意图;

48.图7为本发明具体实施例2的产物的第一金属片的结构示意图。

49.其中:1为正面金属层,11为第一金属片,111为芯片定位槽,112为回路凹槽,113为内凹部,12为第二金属片,121为第二金属片贯通区、13为第三金属片,131为第三金属片贯通区,2为瓷片,3为背面金属层。

具体实施方式

50.下面结合附图对本发明做进一步的说明。

51.参见图1,具体实施例1,一种嵌埋式陶瓷基板的制备方法,包括如下步骤:

52.步骤一,正面金属层以及背面金属层预处理;

53.正面金属层包括至少两层金属片,至少两层金属片包括靠近瓷片的第一金属片,至少两层金属片中除了第一金属片的其余的金属片开设有至少一个上下贯穿的贯穿孔;

54.步骤二,将正面金属层、瓷片以及背面金属层从上至下依次堆叠后进行真空烧结。

55.贯穿孔用于内嵌芯片。

56.本专利通过在正面金属层上开设有贯穿孔,便于实现了对芯片的限位固定效果。相应的减薄了后期封装件的厚度。此外,可以实现芯片的热量从周向向外以及向下区域的金属层散热,大大的提高的散热范围。

57.预处理包括清洗烘干预处理。

58.第一金属片上通过精雕机开设有盲孔。盲孔的深度为第一金属片深度的2/3。贯穿孔的横截面为正方形、长方形、圆形、五边形、六边形中的一种或几种。

59.第一金属片的厚度为0.2mm

‑

0.4mm,第二金属片的厚度为0.2mm

‑

0.3mm,第三金属片的厚度为0.2mm

‑

0.3mm,背面金属层的厚度为0.5mm

‑

1.0mm。

60.正面金属层为铜层或铝层。

61.背面金属层为铜层或铝层。

62.正面金属层包括从下至上依次设置的第一金属片、第二金属片以及第三金属片;第二金属片以及第三金属片上均开设有贯穿孔,且第二金属片以及第三金属片上的贯穿孔

相互导通;第二金属片的贯穿孔的面积要小于第三金属片的贯穿孔的面积。便于实现芯片的限位。

63.针对于正面金属层、背面金属层与瓷片的真空烧结方式,可以有如下几种:

64.方式一:步骤二,将正面金属层、瓷片以及背面金属层从上至下依次堆叠后进行真空钎焊;

65.所述瓷片与所述第一金属片以及背面金属层之间涂覆有钎料。

66.真空钎焊的温度控制在700℃

‑

940℃,真空度小于0.01pa,烧结时间60min

‑

540min。

67.方式二:步骤一中,正面金属层的所有金属片从上至下堆叠后扩散焊接相连;

68.步骤一中,扩散焊接的工艺参数:扩散焊烧结温度为500℃

‑

900℃,真空度小于0.1pa,烧结时间10min

‑

540min。

69.步骤二中,正面金属层、瓷片以及背面金属层真空钎焊相连;

70.所述瓷片与所述第一金属片以及背面金属层之间涂覆有钎料。

71.真空烧结的温度控制在700℃

‑

940℃,真空度小于0.01pa,烧结时间60min

‑

540min。

72.制成的产物,可以是如下两种:

73.参见图2以及图3,结构一:第一金属片不开盲孔:

74.金属层设有三个金属片,分别为从下至上依次设置的第一金属片11、第二金属片12以及第三金属片13;第二金属片12以及第三金属片13上均开设有至少一个贯穿孔,且第二金属片12上的贯穿孔(也就是第二金属片贯穿区121)以及第三金属片13上的贯穿孔(也就是第三金属片贯穿区131)相互导通;第二金属片12的贯穿孔(也就是第二金属片贯穿区121)的面积要小于第三金属片13的贯穿孔(也就是第三金属片贯穿区131)的面积。优选为,第二金属片贯通区121面积相对于第三金属片贯通区131为等比例缩小。便于实现芯片的限位。

75.参见图4以及图5,结构二:第一金属片开盲孔(芯片定位槽111):

76.金属层设有三个金属片,分别为从下至上依次设置的第一金属片11、第二金属片12以及第三金属片13。第一金属片11上开设有芯片定位槽111,芯片定位槽111是非贯通盲槽。芯片定位槽111的深度为第一金属片11深度的2/3。

77.第二金属片以及第三金属片上的贯穿孔采用激光雕刻而成。

78.具体实施例2,一种嵌埋式陶瓷基板的制备方法,包括如下步骤:

79.步骤一,正面金属层以及背面金属层预处理;

80.正面金属层包括至少两层金属片,至少两层金属片包括靠近瓷片的第一金属片,

81.步骤二,第一金属片、瓷片以及背面金属层从上至下依次堆叠后真空钎焊烧结;

82.步骤三,对第一金属片进行蚀刻,制成图案,使得第一金属片上设有内凹的内凹部,且第一金属片上还开设有回形槽,回形槽位于内凹部的外围,且回形槽的深度大于内凹部的深度,且小于第一金属片的厚度;

83.步骤四,将步骤三制成的金属基板的上方依次堆叠正面金属层的其余金属片后,真空扩散焊接;贯穿孔与内凹部上下导通。

84.通过优化制备方法,为了避免内凹部的结构从第一金属片上脱离、移位,本专利采

用两步烧结,第一金属片的图案制备方式为先烧结,后制备,第一次烧结将第一金属片、瓷片与背面金属层真空钎焊在一起,然后在第一金属片上金属层蚀刻制成图案,将金属基板再与第二金属片、第三金属片真空扩散焊接在一起。

85.步骤二中,真空钎焊烧结的温度控制在700℃

‑

940℃,真空度小于0.01pa,烧结时间60min

‑

540min。

86.步骤四中,真空扩散焊接的工艺参数:扩散焊烧结温度为500℃

‑

900℃,真空度小于0.1pa,烧结时间10min

‑

540min。

87.内凹部的深度为第一金属片深度的2/3。

88.贯穿孔的横截面为正方形、长方形、圆形、五边形、六边形中的一种或几种。第一金属片的厚度为0.2mm

‑

0.4mm,第二金属片的厚度为0.2mm

‑

0.3mm,第三金属片的厚度为0.2mm

‑

0.3mm,背面金属层的厚度为0.5mm

‑

1.0mm。正面金属层为铜层或铝层。背面金属层为铜层或铝层。

89.具体的产物的结构,参见图6至图7,正面金属层包括从下至上依次设置的第一金属片11、第二金属片12以及第三金属片13。

90.第一金属片11上设有内凹的内凹部113(也就是孤岛状图形区),且第一金属片11上还开设有上下贯穿的回形槽112,回形槽112位于所述内凹部的外围,所述回形槽用于将内凹部呈孤岛状设置在第一金属片。

91.第二金属片以及第三金属片上的贯穿孔采用激光雕刻而成。

92.有益效果是:1)能够降低封装模块的厚度,从而降低芯片的封装密度;2)嵌埋式覆铜基板能够为芯片提供更好的散热性,并提供芯片定位槽,可防止芯片焊接时位置偏移。

93.以上仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。