1.本发明涉及一种cmp用浆料组合物及使用其的研磨方法。

背景技术:

2.近来,随着半导体元件的集成度程度增加,半导体晶圆(wafer)上形成的结构物之间的高低段差增加,当段差增加时,在后续的光刻(lithography)工艺中,因焦深(dof,depth of focusing)问题而发生难以准确印刷(printing)掩模图案的困难。

3.据此,近来为了平坦化晶圆表面而广泛使用将化学去除加工和机械去除加工合为一个加工工艺的化学机械研磨(chemical

‑

mechanical polishing,以下称为cmp)工艺。通常,cmp工艺将具有段差的晶圆表面紧贴于研磨垫(polishing pad)上后,将作为包含研磨材料和化学物质的研磨液的浆料(slurry)注入到晶圆与研磨垫之间,以使晶圆的表面平坦化。即,简单而言,可以说cmp工艺是在半导体晶圆平坦地刮除特定膜质的作业,在这种cmp工艺中,研磨(polishing)后研磨表面的均一度非常重要。用于cmp工艺的结构包括:安装晶圆的头部、与头部沿相同方向旋转的垫、及在它们之间包含纳米尺寸的研磨粒子等的浆料;其中,晶圆通过表面张力或真空而安装于头部。在cmp工艺中,通过垫和浆料研磨晶圆,附着有垫的研磨台进行单纯的旋转运动,且头部同时进行旋转运动与摇动运动,并对晶圆以一定压力向研磨台方向施压。由于头部的自身荷重和被施加的加压力,晶圆表面和垫接触,且作为加工液的浆料在该接触面之间的微细缝隙,即垫的孔隙部分之间流动。通过浆料内部的研磨粒子和垫的表面突起实现机械去除作用,并通过浆料内的化学成分实现化学去除作用。此外,由于从晶圆的形成器件的突出部分的顶部形成与研磨粒子或表面突起的接触,且压力集中到该突出部分,因此相比其他部分具有相对高的表面去除速度,且随着加工的进行,在整个面积突出部分被均匀地去除。

4.通常,在低ph下,氮化硅膜具有正(positive)ζ电位(zeta potential),相反地,氧化硅膜具有负(negative)ζ电位。根据静电引力理论,为了实现对氧化硅膜的高研磨率,使用具有正(positive)ζ电位作为相反电位的研磨材料,以提高其与具有负(negative)ζ电位的氧化硅膜的吸附力。此外,由于研磨剂硅溶胶中存在在制造过程中产生或成为污染的金属杂质,因此在研磨过程中刮伤(scratch)缺陷有所增加。去除了这些金属杂质的高纯度研磨材料能够显著地降低刮伤的发生率。

5.cmp工艺可以分为在工艺进行过程中仅研磨同一物质以去除指定厚度的类型、及在遇到其他不同种类物质时确定研磨终点(polishing end point)的类型。在工艺中,当不应该被研磨的层的研磨率比需要研磨的物质的研磨率小很多时,可以通过少许的过度研磨来自然地决定研磨终点(pep)。如上所述的两种物质的研磨比称为选择比。上述cmp工艺中使用的浆料需要在能够引起化学反应的气氛的溶液中混合具有选择比的研磨材料。换句话说,在制造3d nand闪存(nand flash)半导体中,在栅极间隙多晶硅(gate gap poly)工艺中,如上所述,需要优先研磨氧化硅膜并在暴露氮化硅膜的同时停止研磨的研磨比不同的,即选择比不同的两种物质的浆料。此外,需要开发一种无金属层损伤并通过减少微细刮伤

来提高元件的电性能的最佳cmp用浆料组合物。

6.另一方面,cmp的被研磨面暴露多晶硅膜(polysilicon film)、单晶硅膜、氧化硅膜、氮化硅膜等多种材料。以往,使用以上材料中的一种作为目标的cmp用浆料组合物,以cmp去除其目标材料。但是,当与其他材料的研磨速度比区别太大时,则目标材料可能被过度研磨而导致凹陷或侵蚀等缺陷。此外,由于每种目标材料选择适合各个目标材料的cmp用浆料组合物,并必须通过cmp去除,因此存在生产力降低的问题。

7.据此,进来伴随着半导体器件的结构多样化,要求同时研磨多晶硅膜、氧化硅膜及氮化硅膜三种膜质。为了同时研磨这三种膜质,需要开发一种能够脱离需选择各个研磨对象适合对象的浆料以供给浆料的工艺,而由cmp用浆料组合物自身调节膜质的选择比以进行研磨的技术。

技术实现要素:

8.要解决的问题

9.本发明在于提供一种cmp用浆料组合物,所述组合物能够自由地调节对氧化硅膜、氮化硅膜及多晶硅膜的研磨选择比以进行研磨而能够有效地应用于需要选择性去除氧化硅膜、氮化硅膜及多晶硅膜的半导体制造工艺中。此外,本发明还在于提供一种研磨浆料及使用其的绝缘膜的平坦化方法,所述研磨浆料作为用于去除氧化硅膜段差的研磨材料能够使用高纯度的正(positive)ζ电位(zeta potential)的硅溶胶,且在去除段差时能够最小化刮伤(scratch)缺陷。

10.解决问题的方案

11.为了达到上述的目的,提供一种cmp用浆料组合物,其特征在于,包括:研磨材料,所述研磨材料由硅溶胶组成;添加剂,所述添加剂选自由聚乙二醇、杂环化合物所组成的组中的一种以上;及溶剂,以便能够提高氧化硅膜的研磨性能且最小化刮伤缺陷且能够调节对氧化硅膜、氮化硅膜及多晶硅膜的选择比以进行研磨。

12.在本发明的一优选实施例中,所述硅溶胶的ζ电位(zeta potential)为 10至 70mv。

13.在本发明的一优选实施例中,所述金属(li、b、mg、k、ca、ti、v、cr、mn、fe、co、ni、cu、zn、zr、mo、ag、cd、sn、ta、w、pt、na、al)含量为100ppb以下。将粒子大小为10至120nm作为特征。

14.在本发明的一优选实施例中,其特征在于,所述杂环化合物具有两个以上的氮原子,且选自由1,2,4h

‑

三唑、5

‑

甲基苯并三唑、四唑、咪唑、1,2

‑

二甲基咪唑及哌嗪所组成的组中的一种以上。

15.在本发明的一优选实施例中,其特征在于,所述添加剂由对于多晶硅膜能够调节选择比的聚乙二醇及对于氮化硅膜能够调节选择比的杂环化合物组成。

16.在本发明的一优选实施例中,其特征在于,所述cmp用浆料组合物,相对于组合物的总重量,包括:由硅溶胶组成的0.2至10重量%的研磨材料;选自由聚乙二醇及杂环化合物所组成的组中的一种以上的0.001至7重量%的添加剂;及余量的溶剂。

17.在本发明的一优选实施例中,其特征在于,所述添加剂中的聚乙二醇、杂环化合物的比例为0~5.0:0~5.0。

18.在本发明的一优选实施例中,其特征在于,所述cmp用浆料组合物的ph为3至5。

19.在本发明的一优选实施例中,其特征在于,所述cmp用浆料组合物的氧化硅膜的研磨率为并同时对由选自氧化硅膜、氮化硅膜及多晶硅膜中的两种以上所形成的被研磨膜进行研磨。

20.在本发明的一优选实施例中,其特征在于,在所述研磨中,氧化硅膜、氮化硅膜及多晶硅膜的研磨选择比为1~50:1:1~10。

21.在本发明的一优选实施例中,其特征在于,所述cmp用浆料组合物是在研磨材料中包含添加剂而作为单一浆料使用。

22.在本发明的另一实施例中,提供一种使用cmp用浆料组合物的研磨方法,其特征在于,包括使用所述cmp浆料组合物研磨半导体晶圆的步骤。

23.在本发明的一优选实施例中,其特征在于,在所述研磨方法中,分别注入研磨材料和添加剂,并通过调节研磨材料和添加剂的含量来调节氧化硅膜、氮化硅膜及多晶硅膜的选择比以进行研磨。

24.在本发明的一优选实施例中,通过调节所述硅溶胶的含量来调节氧化硅膜的研磨率,通过调节所述聚乙二醇含量来调节多晶硅膜的选择比以进行研磨。

25.此外,其特征在于,通过调节杂环化合物的含量来调节氮化硅膜的选择比以进行研磨。

26.在本发明的一优选实施例中,其特征在于,在所述添加剂中,聚乙二醇、杂环化合物的比例为0~5.0:0~5.0。

27.发明的效果

28.根据本发明的cmp用浆料组合物,通过提高氧化硅膜的研磨性能且最小化刮伤(scratch)缺陷来提高工艺可靠度和生产力。此外,相对于氮化硅膜和多晶硅膜能够以高研磨选择比研磨氧化硅膜,从而能够有效地应用于需要选择性地去除氧化硅膜的半导体制造工艺中。此外,由于如上所述的cmp用浆料组合物无需选择各个研磨对象适合对象膜质的各种浆料,因此能够助于提高生产效率。

29.最佳实施方式

30.以下,详细说明本发明。

31.在没有其他定义的前提下,本说明书中所使用的所有技术用语和科学用语具有与本发明所属技术领域中普通技术人员通常理解的含义相同的含义。一般情况下,本说明书中使用的命名法是本技术领域已经公知并通常使用的命名法。

32.在整个本技术说明书中,当某部分“包含”某构成要素时,在没有特别相反记载的情况下并不除外其他构成要素,而是意味着还可以包含其他构成要素。

33.通常,cmp(化学机械研磨,chemical

‑

mechanical polishing,以下称为cmp)工艺中所谓浆料(slurry)是指包含研磨材料(abrasive)和添加剂(additive)的浆料,此外,作为单一化的产品的仅研磨材料也称为浆料。由于本发明是通过改变研磨材料和添加剂的流量以改变对被研磨膜质的选择比的技术,因此区分为研磨材料和添加剂。但是根据情况,可以在研磨材料中包含添加剂以制备成单一浆料组合物。

34.在本发明中,「去除率(removal rate)」是指在cmp工艺中晶圆的膜质被刮除的程度,即膜质的去除速度。

35.在本发明中,「选择比(selectivity ratio)」是指在相同的研磨条件下,对彼此不同物质的不同去除率。

36.以下,详细说明本发明的cmp用浆料组合物及使用其的研磨方法。

37.使用于通常的cmp用浆料组合物的硅溶胶的ζ电位(zeta potential)具有负(negative)的值,且在低ph下氧化硅膜也具有相同的负表面电位。据此,由于研磨材料与氧化硅膜之间的静电斥力而研磨率低,因此去除初期段差大的氧化硅膜有局限。所述硅溶胶的ζ电位为 10至 70mv的在从适当地保持去除率(removal rate)的方面是优选的,且电位值 30mv至 50mv是更加优选的。如果ζ电位值不足 10mv,则对膜质的去除率(removal rate)减小而所需的工艺进行时间长,如果ζ电位值超过70mv,则由于过度(over)去除率而脆弱于刮伤(scratch),因此是不优选的。

38.通常,硅溶胶在制造过程所产生的金属杂质为10~600ppm,这在cmp工艺中增加了致命的刮伤(scratch)缺陷率。为了减少刮伤(scratch),所述硅溶胶中金属(li、b、mg、k、ca、ti、v、cr、mn、fe、co、ni、cu、zn、zr、mo、ag、cd、sn、ta、w、pt、na、al)含量优选为100ppb以下,更加优选为50ppb以下。

39.通常情况下,在低ph下,氮化硅膜的研磨效果最好,但在本发明中,可以通过降低对氮化硅膜的选择比来最小化去除率,并可以根据器件的结构特性,调节与氮化硅膜相比的对氧化硅膜和多晶硅膜的选择比,从而自由地调高或调低去除率以进行研磨。

40.如上所述,作为调节对氧化硅膜、氮化硅膜及多晶硅膜的选择比的主要因素,取决于作为cmp用浆料组合物的组合物质的“添加剂及研磨材料的含量调节”,可以通过调节添加剂及研磨剂的含量应用符合各自的cmp工艺的最佳选择比来研磨半导体晶圆。

41.据此,现有的半导体工艺中使用的浆料根据各研磨对象具有需在中途更换浆料的麻烦,但本发明要开发的浆料针对各种器件及多种工艺使用一种浆料,可以通过调节添加剂及研磨材料的含量来调节对氧化硅膜、氮化硅膜及多晶硅膜的选择比以进行研磨,因此可以连续地进行研磨去除,而无需根据研磨对象在中途更换浆料。

42.根据本发明的一实施例,可以提供一种cmp用浆料组合物,其特征在于,包括:研磨材料,所述研磨材料由硅溶胶组成;添加剂,所述添加剂选自由聚乙二醇、杂环化合物所组成的组中的一种以上;及溶剂,以便能够调节对氧化硅膜、氮化硅膜及多晶硅膜的选择比以进行研磨。

43.所述硅溶胶是指具有纳米粒子大小的二氧化硅粒子不产生沉降而稳定地分散于溶剂中的胶体溶液。所述硅溶胶的粒子大小为10至120nm的在适当地保持刮伤(scratch)及去除率(removal rate)的方面是优选的,粒子大小为30至80nm时是更加优选的。如果硅溶胶的粒子大小不足10nm的情况下,则对膜质的去除率(removal rate)减小而所需的工艺进行时间长,如果其粒子大小超过120nm,则脆弱于刮伤(scratch),因此是不优选的。

44.在根据本发明一实施例的cmp用浆料组合物中,所述添加剂可以由对于多晶硅膜能够调节选择比的聚乙二醇及对于氮化硅膜能够调节选择比的杂环化合物组成。即,当调高作为添加剂的聚乙二醇的含量时,可以用非离子界面活性剂根据粉状乳化剂的特性而大幅减小对多晶硅膜的研磨速度;当调高作为添加剂的杂环化合物的含量时,可以与抑制沉降和凝集的特性一起减少对氮化硅膜的研磨速度。

45.此时,所述杂环化合物为两个以上的氮原子的化合物,且选自由1,2,4h

‑

三唑、5

‑

甲基苯并三唑、四唑、咪唑、1,2

‑

二甲基咪唑及哌嗪所组成的组中的一种以上。

46.在根据本发明一实施例的cmp用浆料组合物中,所述溶剂用作调节组合物的浓度以调节膜质的去除率,可以稀释于添加剂使用,溶剂可以使用去离子水、水等,但优选使用去离子水。

47.所述cmp用浆料组合物,相对于组合物的总重量,包括:由硅溶胶组成的0.2至10重量%的研磨材料;选自由聚乙二醇及杂环化合物所组成的组中的一种以上的0.001至7重量%的添加剂;及余量的溶剂。

48.由所述硅溶胶组成的研磨材料,即硅溶胶,相对于组合物的总重量,优选包括0.2至10重量%。如果将硅溶胶以不足0.2重量%来使用,则由于固体(solid)含量不足而导致去除率(removal rate)减小,如果超过10重量%来使用,则由于含量过多导致发生凝集现象,因此是不优选的。

49.选自由所述聚乙二醇、杂环化合物所组成的组中的一种以上的添加剂,相对于组合物的总重量,优选包括0.001至7重量%。如果将添加剂以不足0.001重量%来使用,则由于添加剂的含量低而几乎没有添加剂的作用,如果超过7重量%来使用,则由于过量地含有添加剂导致一同添加的其他种类的添加剂无法正常发挥其功能,因此是不优选的。

50.此时,就添加剂是聚乙二醇、杂环化合物的比例为0~5.0:0~5.0而言,满足氧化硅膜、氮化硅膜及多晶硅膜的研磨选择比为1~50:1:1~10,从而可以通过调节与氮化硅膜相比的对氧化硅膜和多晶硅膜的选择比来自由地调高或调低去除率以进行研磨,因此是优选的。

51.在组合物的稳定性方面,根据本发明的一实施例的cmp用浆料组合物的ph为3至5是优选的。如果ph范围不足3,则去除率(removal rate)不稳定,如果ph范围超过5,则由于胶体粒子的凝集现象及去除率(removal rate)不稳定,因此是不优选的。为了调节至上述ph范围,可以单独或混合使用的碱性物质有koh、nh4oh、naoh、tmah、tbah、hno3等,可以单独或混合使用的酸性物质有硝酸、硫酸、盐酸等无机酸。由于ph与氧化硅膜、氮化硅膜及多晶硅膜的研磨速度密切相关,因此需要对其进行精密调节。

52.如上所述,本发明提供的cmp用浆料组合物,可以通过调节添加剂及硅溶胶的含量来同时研磨由氧化硅膜、氮化硅膜及多晶硅膜中选择的两种以上所形成的被研磨膜。此时,所述cmp用浆料组合物可以是氧化硅膜、氮化硅膜及多晶硅膜的研磨选择比为1~50:1:1~10的组合物。此外,氧化硅膜的去除率(研磨速度)可以为多晶硅膜的去除率(研磨速度)可以为氮化硅膜的去除率(研磨速度)可以为这些在暴露氮化硅膜的半导体工艺中,能够以高研磨选择比来研磨氧化硅膜和多晶硅膜,因此能够有效地应用于需要选择性地去除氧化硅膜及多晶硅膜的半导体工艺中。

53.此外,本发明提供的cmp用浆料组合物,虽然能够通过调节对氧化硅膜、氮化硅膜及多晶硅膜的选择比以进行研磨,但是根据情况,也能够研磨一些其他的膜质。例如,就本发明的cmp用浆料组合物而言,在沟槽(trench)结构形态的情况下,能够有效地使用于研磨块状(bulk)膜质。不仅如此,通常,管通道(pipe channel)区域使用牺牲膜质来形成结构,在打算通过cmp工艺形成结构时,为了最小化由管通道的凹陷(dishing)或过度研磨(over cmp)引起的沟槽变化,需要使用具有各种特性的浆料。在这种情况下,可以应用能够调节膜

质选择比的本发明的cm p用浆料组合物。

54.所述cmp用浆料组合物,能够通过将添加剂添加到研磨材料中而作为单一浆料使用。

55.根据本发明的另一实施例,提供一种使用cmp用浆料组合物的研磨方法,其特征在于,包括使用所述cmp用浆料组合物来研磨半导体晶圆的步骤。所述研磨方法可以是分别注入研磨材料和添加剂,并通过调节添加剂和研磨材料的含量来调节氧化硅膜、氮化硅膜及多晶硅膜的选择比而进行研磨。

56.使用所述cmp用浆料组合物的研磨方法的一个示例如下。首先,向研磨平台上的研磨垫供应cmp用浆料组合物,使其与被研磨表面接触,并通过被研磨表面与研磨垫的相对运动进行研磨。作为研磨装置,可以使用具有维持半导体基板的支座和贴有研磨垫的研磨平台的普通研磨装置。作为研磨垫,可以使用普通的无纺布、发泡聚氨酯、多孔氟树脂等。在研磨过程中,通过各研磨材料及添加剂的管道用泵等向研磨垫连续地供应cmp用浆料组合物。对于该供应量没有限制,但优选保持研磨垫的表面始终被研磨材料覆盖的状态。此时,所述添加剂可以通过调节聚乙二醇的含量来调节多晶硅膜的选择比而进行研磨,也可以通过调节杂环化合物的含量来调节氮化硅膜的选择比而进行研磨。此时,在所述添加剂中,聚乙二醇、杂环化合物的比例可以为0~5.0:0~5.0。优选地,在研磨完成之后,使用流水充分洗涤半导体基板后,使用旋转干燥器、灯式干燥机等去除附着在半导体基板上的水滴后进行干燥。作为被处理物,可以例举为具有由选自多晶硅膜、氮化硅膜及氧化硅膜中的两种以上形成的被研磨表面的半导体基板。

57.根据本发明的cmp用浆料组合物能够以高选择比来研磨氧化硅膜、氮化硅膜及多晶硅膜,因此能够有效地应用于具有由多晶硅膜、氮化硅膜及氧化硅膜的三种膜所形成的被研磨表面的半导体制造工艺中。如上所述的cmp用浆料组合物无需针对各个研磨对象选择适合对象的浆料,因此能够助于提高生产效率。

58.以下说明本发明的优选实施例及比较例。但下述实施例仅是本发明的优选实施例,本发明的范围并不限于下述实施例。

具体实施方式

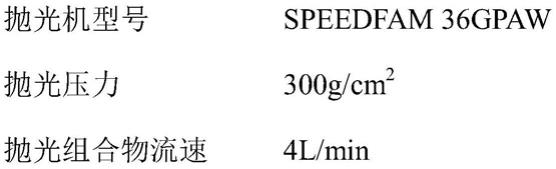

59.实施例1~6

60.按照表1记载的组成成分、组成比例、ζ电位值及ph制备浆料组合物,首先,准备作为研磨材料的硅溶胶,在含有聚乙二醇、作为杂环化合物的5

‑

甲基苯并三唑的添加剂中混合作为溶剂的余量去离子水,分别调节所述研磨材料的ζ电位值和含量,制备了提高氧化硅膜的研磨性能并能够调节与氮化硅膜的选择比的cmp用浆料组合物。在所制备的cmp用浆料组合物中添加作为ph调节剂的koh、hno3以将ph调节为3.5。

61.比较例1及比较例2

62.按照表1记载的组成成分、组成比例、ζ电位值及ph来制备了浆料组合物,除了将ζ电位值调节为负(negative)值之外,与实施例1至6相同地制备。

63.[表1]

[0064][0065]

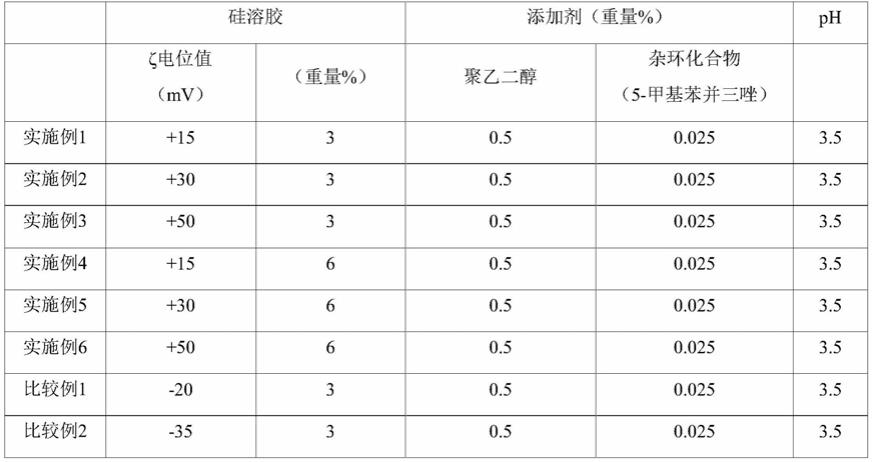

特性测定(根据cmp浆料组合物的研磨速度评价)

[0066]

使用按照上述实施例1至6及比较例1至2所制备的cmp浆料组合物评价氧化硅膜、氮化硅膜的研磨速度。

[0067]

此时,研磨设备使用cts公司的cmp设备。

[0068]

将使用cmp浆料组合物测定氧化硅膜、氮化硅膜的研磨速度的结果示于以下表2。

[0069]

[表2]

[0070][0071][0072]

比较实施例1至6和比较例,如上表2所示,确认到当作为研磨材料的硅溶胶的ζ电位(zeta potential)为正(positive)值时,对氮化硅膜的氧化硅膜的研磨选择比增加。

[0073]

但是,当ζ电位(zeta potential)为负(negative)值时,相反地,确认到对氧化硅膜的氮化硅膜的研磨选择比增加。

[0074]

在相当于ζ电位(zeta potential)为正(positive)值的情况的

‘

实施例1至3’中,

确认到随着将ζ电位值增加为15、30、50,氮化硅膜的去除率减小、氧化硅膜的去除率增加而选择比增加。这些结果,也在相当于ζ电位(zeta potential)为正(positive)值的情况的

‘

实施例4至6’中,确认到随着将ζ电位值增加为15、30、50,氮化硅膜的去除率减小、氧化硅膜的去除率增加而选择比增加。

[0075]

另一方面,在相当于相同的ζ电位值下增加研磨材料含量的情况的

‘

实施例1及4’中,确认到将研磨材料含量从3增加至6时,氧化硅膜的去除率增加而选择比增加。这些结果,也在相当于将研磨材料的含量增加的情况的

‘

实施例2及5’及

‘

实施例3及6’中,确认到将研磨材料含量从3增加至6时,氧化硅膜的去除率增加而选择比增加。

[0076]

从结果来看,在增加硅溶胶的ζ电位(zeta potential)的正值或增加研磨材料含量的本发明的组合物的情况下,能够通过增加氧化硅膜的研磨速度而将初期段差大的氧化硅膜以高研磨速度进行研磨。

[0077]

此外,相对于氮化硅膜以高研磨选择比研磨氧化规模,从而确认到可以提供能够有效地应用于需要选择性地去除氧化硅膜的半导体制造工艺,例如栅极间隙多晶硅(gate gap poly)工艺中的cmp用浆料组合物。

[0078]

实施例7

[0079]

准备去除了金属杂质的高纯度硅溶胶,并以与实施例2相同的方法制备cmp用浆料组合物。

[0080]

比较例3

[0081]

除了使用实施例7中没有去除金属杂质的普通硅溶胶之外,以与实施例7相同的方法制备cmp用浆料组合物。

[0082]

所制备的cmp用浆料组合物中含有的金属杂质含量、组成成分、组成比例、ζ电位值如以下表3所示。

[0083]

[表3]

[0084][0085]

特性测定(根据cmp浆料组合物的研磨速度评价)

[0086]

上述表3示出了使用按照实施例7和比较例3制备的cmp浆料组合物研磨氧化硅膜后,利用ait

‑

xp测定的刮伤数。

[0087]

与比较例3相比,可知使用实施例7的浆料组合物进行研磨时刮伤数显著减少。

[0088]

从结果来看,使用已去除金属杂质的硅溶胶的本发明的组合物,能够最小化氧化硅膜的刮伤缺陷,从而提高工艺的可靠度和生产力。

[0089]

实施例8至12

[0090]

按照表4记载的组成成分、组成比例、ζ电位值及ph制备浆料组合物,首先,准备作

为研磨材料的硅溶胶,在含有聚乙二醇、作为杂环化合物的5

‑

甲基苯并三唑的添加剂中混合作为溶剂的余量去离子水,分别调节所述研磨材料的ζ电位值和含量,制备了提高氧化硅膜的研磨性能并能够调节与氮化硅膜的选择比的cmp用浆料组合物。在所制备的cmp用浆料组合物中添加作为ph调节剂的koh、hno3而将ph调节为3.5。

[0091]

比较例4至5

[0092]

除了比较例4不使用聚乙二醇及比较例5不使用作为杂环化合物的5

‑

甲基苯并三唑的点之外,以与实施例8至12相同地制备比较例4至5。此时,以相同的硅溶胶的种类和含量制备cmp用浆料组合物。

[0093]

所制备的cmp用浆料组合物中包含的浆料含量如以下表4所示。

[0094]

[表4]

[0095][0096]

特性测定(根据cmp浆料组合物的研磨速度评价)

[0097]

使用按照上述实施例8至12及比较例4至5所制备的cmp用浆料组合物评价氧化硅膜、氮化硅膜及多晶硅膜的研磨速度。

[0098]

此时,研磨设备使用cts公司的cmp设备。

[0099]

将使用cmp浆料组合物测定氧化硅膜、氮化硅膜及多晶硅膜的研磨速度的结果示于以下表5。

[0100]

[表5]

[0101][0102][0103]

比较实施例8至12和比较例4、5,如上表5所示,确认到实施例8至12中对氮化硅膜的氧化硅膜及多晶硅膜的研磨选择比增加。特别是,对氮化硅膜的氧化硅膜的研磨选择比均显著地增加为1:10以上。

[0104]

相比之下,在不使用调节多晶硅膜的去除率的聚乙二醇的比较例4的情况下,多晶硅膜的去除率比氧化硅膜的去除率高,因此在cmp工艺后可能存在留下多晶硅残留物(residue)的问题。

[0105]

如同比较例5,在不使用作为杂环化合物的5

‑

甲基苯并三唑的情况下,氮化硅膜的去除率上升,因此相对于氮化硅膜,氧化硅膜及多晶硅膜的选择比减少。

[0106]

如此地,在包含本发明的cmp用浆料组合物时,确认到相对于氮化硅膜以高研磨选择比研磨氧化硅膜及多晶硅膜而提供一种能够有效地应用于需要选择性地去除氧化硅膜及多晶硅膜的半导体工艺中的cmp用浆料组合物。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。