1.本发明涉及形成半导体装置的方法,特别是涉及形成具不同临界值电压的半导体装置的方法。

背景技术:

2.半导体集成电路(integrated circuit;ic)产业正面临迅速的成长。在ic进化的进程中,功能密度(意即,每芯片面积的内连线装置的数量)已大致上增加,而几何尺寸(意即,制程可形成的最小的布件(或线))缩小。此缩小制程,通过增加制程效率以及降低相关的成本,原则上提供一些优点。然而,此缩小制程亦伴随着更加复杂的包含这些ic的装置的设计以及制程,并且,为了使这些进展能够实现,装置制程需要类似的发展。

3.当ic装置的几何尺寸持续的缩小,以理想的形状形成特征就会变得越来越有挑战性。例如,在后置栅极(gate

‑

last)制程中,虚设栅极堆叠首先以占位区形成,使得在其后形成的金属栅极堆叠经历实质部分的制程,并且在其后移除并以功能金属栅极堆叠取代虚设栅极堆叠。为了取代虚设栅极堆叠,首先移除虚设栅极堆叠以形成栅极沟槽,并且在栅极沟槽中沉积多个层以形成功能金属栅极堆叠。在一些情况下,额外的偶极(dipole)层或是介电层可沉积在栅极介电层上以提供不同临界值电压的晶体管。由于缩小的几何亦缩小了栅极沟槽的尺寸,这些额外的偶极层以及介电层可能会缩小在功能金属栅极结构中满意地沉积多个层的制程窗口。在栅极沟槽不是笔直的状况下,制程窗口可能会进一步缩小。因此,虽然现有的后置栅极制程可满足其预期的目的,但是却不是对全方面都令人满意。

技术实现要素:

4.在一实施例中,本公开提供一种半导体装置,包含第一晶体管、第二晶体管、以及第三晶体管。第一晶体管包含第一主动区、第一栅极介电层,在第一主动区上,第一栅极介电层包含偶极层材料的第一浓度、以及第一栅极结构,设置在第一栅极介电层上。第二晶体管包含第二主动区、第二栅极介电层,在第二主动区上,第二栅极介电层包含偶极层材料的第二浓度、以及第二栅极结构,设置在第二栅极介电层上。第三晶体管包含第三主动区、第三栅极介电层,在第三主动区上,第三栅极介电层包含偶极层材料的第三浓度、以及第三栅极结构,设置在第三栅极介电层上。偶极层材料包含氧化镧、氧化铝、或氧化钇。第一浓度大于第二浓度,以及第二浓度大于第三浓度。

5.在另一实施例中,本公开提供一种半导体装置的制造方法,包含提供工件,工件包含第一装置区、第二装置区、以及第三装置区,在第一装置区形成第一栅极沟槽、在第二装置区形成第二栅极沟槽、以及在第三装置区形成第三栅极沟槽,沉积栅极介电层在第一栅极沟槽、第二栅极沟槽、以及第三栅极沟槽中,沉积第一偶极层在第一栅极沟槽、第二栅极沟槽、以及第三栅极沟槽中的栅极介电层上,选择性地移除第二栅极沟槽中的第一偶极层,沉积第二偶极层,第二偶极层在第一栅极沟槽中的第一偶极层、第二栅极沟槽中的栅极介电层、以及第三栅极沟槽中的第一偶极层上,选择性地移除第三栅极沟槽中的第一偶极层

以及第二偶极层,以及退火工件。

6.在另一实施例中,本公开提供一种半导体装置的制造方法包含提供工件,工件包含第一装置区、第二装置区、第三装置区、以及第四装置区,在第一装置区形成第一栅极沟槽、在第二装置区形成第二栅极沟槽、在第三装置区形成第三栅极沟槽、以及在第四装置区形成第四栅极沟槽,沉积一极介电层,栅极介电层在第一栅极沟槽、第二栅极沟槽、第三栅极沟槽、以及第四栅极沟槽中,沉积第一偶极层,第一偶极层在第一栅极沟槽、第二栅极沟槽、第三栅极沟槽、以及第四栅极沟槽中的栅极介电层上,选择性地移除第三栅极沟槽以及第四栅极沟槽中的第一偶极层,对工件进行第一退火制程,移除第一栅极沟槽以及第二栅极沟槽中的第一偶极层,在移除第一偶极层之后,沉积第二偶极层第一栅极沟槽、第二栅极沟槽、第三栅极沟槽、以及第四栅极沟槽上,选择性地移除第二栅极沟槽以及第四栅极沟槽中的第二偶极层,对工件进行第二退火制程,以及从工件移除第二偶极层。

附图说明

7.本公开的各项层面在以下的实施方式搭配附带的图示一同阅读会有最好的理解。需要强调的是,依据产业的标准惯例,许多特征并没有按比例描绘。事实上,为了讨论的清晰度,许多特征的尺寸可为任意的增加或缩减。

8.图1根据本公开的一些实施例描绘形成半导体装置的方法的流程图。

9.图2

‑

图15根据本公开的一些实施例,为图1的方法在各个制程操作当中的工件的局部剖面图。

10.图16根据本公开的一些实施例描绘形成半导体装置的另一方法的流程图。

11.图17

‑

图27、图28a、以及图28b根据本公开的一些实施例,为图16的诸多制程当中的工件的局部剖面图。

12.图29根据本公开的一些实施例,为8晶体管(8t)静态随机存取存储器(static random access memory;sram)单元的电路图。

13.图30根据本公开的一些实施例,为图29的8t sram单元的布局图。

14.图31根据本公开的一些实施例,为10晶体管(10t)sram单元的电路图。

15.图32根据本公开的一些实施例,为图31的10t sram单元的布局图。

16.其中,附图标记说明如下:

17.100、500:方法

18.102

‑

122、502

‑

526:方框

19.10:通道区

20.20:源极/漏极区

21.200:工件/半导体装置

22.202:基板

23.204、905、1005:主动区

24.205:虚设栅极介电层

25.207:虚设栅极电极

26.208:虚设栅极堆叠

27.210:栅极间隔物层

28.212:源极/漏极特征

29.214:接点蚀刻停止层

30.216:介电层

31.218:栅极沟槽

32.220:界面层

33.222:栅极介电层

34.224:第一偶极层

35.226、232、242:硬遮罩层

36.228、234、244:底部抗反射涂膜层

37.230、240:第二偶极层

38.236:功能金属栅极堆叠

39.300:退火制程

40.410、810:第一晶体管

41.420、820:第二晶体管

42.430、830:第三晶体管

43.600:第一退火制程

44.700:第二退火制程

45.840:第四晶体管

46.900:8

‑

晶体管sram单元

47.902、1002:第一通道栅极晶体管

48.904、1004:第二通道栅极晶体管

49.906、1006:第一上拉晶体管

50.908、1008:第二上拉晶体管

51.910、1010:第一下拉晶体管

52.912、1012:第二下拉晶体管

53.914:读取下拉晶体管

54.916:读取通道栅极晶体管

55.918:读取端

56.920、1026:虚拟接地

57.922、1028:保持晶体管

58.924、1030:电源栅极晶体管

59.903、1003:栅极结构

60.903

‑

1、1003

‑

1:第一栅极结构

61.903

‑

2、1003

‑

2:第二栅极结构

62.1000:10

‑

晶体管sram单元

63.1014:第一读取端

64.1016:第二读取端

65.1018:第一读取下拉晶体管

66.1020:第一读取通道栅极晶体管

67.1022:第二读取下拉晶体管

68.1024:第二读取通道栅极晶体管

69.1100、3100:第一装置区

70.1200、3200:第二装置区

71.1300、3300:第三装置区

72.2221、2231:第一栅极介电层

73.2222、2232:第二栅极介电层

74.2233:第三栅极介电层

75.3400:第四装置区

76.bl:位元线

77.blb:互补位元线

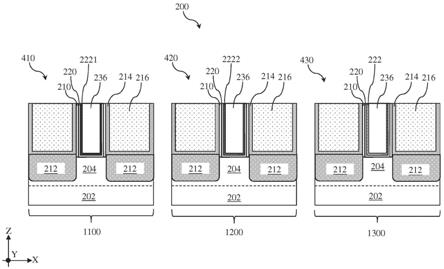

78.i:区域

79.q:第一数据存储节点

80.qb:第二数据存储节点

81.rbl:读取位元线

82.rblb:读取互补位元线

83.rwl:读取字元线

84.wl:字元线

具体实施方式

85.以下公开内容提供了用于实施所提供标的的不同特征的许多不同实施例或实例。以下描述了部件以及布置等的特定实例以简化本公开内容。当然,所述仅仅是实例,而并不旨在为限制性的。例如,在以下描述中在第二特征上方或之上形成第一特征可以包括第一特征和第二特征形成为直接接触的实施例,并且亦可以包括可以在第一特征与第二特征之间形成额外特征,使得第一特征和第二特征可以不直接接触的实施例。另外,本公开可以在各种实例中重复参考数字及/或字母。该重复是为了简单和清楚的目的,并且本身并不代表所论述的各种实施例及/或配置之间的关系。

86.除此之外,在本公开当中的一特征在另一特征之上、与之连接和/或耦合的形成可以包括其中特征形成为直接接触的实施方式,并且还可以包括其中可以插入额外的特征的形成实施方式,以使得特征可能不直接接触。另外,在空间上相对的用语,例如“下部”,“上部”,“上方”,“之上”,“下方”,“顶部”、“底部”等及其派生词(例如,“水平的”,“向下的”,“向上的”等)皆用以使本公开更容易地描述一个特征与另一特征之间的关系。空间相对术语意在除了涵盖装置在图式所描述的取向,亦涵盖在操作当中或使用当中的装置的不同取向。

87.更进一步,当一数字或一范围的数字是用“大约”、“近似”以及类似方式形容时,该字汇的目的是涵盖包括所述的数字的一定合理范围内的其他数字,例如在所述的数字的 /

‑

10%的范围之内或者对于所属领域的技术人员所能够理解的其他数值。举例来说,“大约5nm”这词汇涵盖从4.5纳米至5.5纳米的尺寸范围。

88.在现代晶体管中常见的金属栅极堆叠,可利用前置栅极(gate

‑

first)制程或者后置栅极(gate

‑

last)制程形成。在前者中,功能金属栅极堆叠在其他特征(例如源极/漏极特

征以及层间介电(interlayer dielectric)层)之前形成。在后者中,首先形成非功能虚设栅极堆叠为占位符(placeholder),以用于在其后形成的金属栅极堆叠,进行源极/漏极特征以及层间层(interlayer)的制程,并且接着移除虚设栅极堆叠并以功能金属栅极堆叠取代。为了取代虚设栅极堆叠,首先移除虚设栅极堆叠以形成栅极沟槽,接着在栅极沟槽沉积多个层以形成功能金属栅极堆叠。在一些情况下,一个或多个偶极(dipole)层可沉积在栅极介电层上以提供不同临界值电压的晶体管。基于氧原子密度的差异(differential),在偶极层以及下层氧化硅界面层之间的界面可能产生界面偶极。根据界面偶极的极性,界面偶极可能增加或降低所属的晶体管的临界值电压。虽然偶极层可用以调节临界值电压,但额外的偶极层可能会进一步缩小在功能金属栅极堆叠中满意地沉积多个层的制程窗口。在栅极沟槽不是笔直的案例中,制程窗口可进一步缩小。例如,在栅极沟槽沉积所有的多个层以形成功能金属栅极堆叠之前,层的两侧可结合并关闭沟槽的开口,以防止后续的层在栅极沟槽沉积。

89.为了减缓前面的问题,本公开提供形成半导体装置的方法。在本公开的一些实施例中,此方法包含在工件上的第一装置区、第二装置区、以及第三装置区中的栅极沟槽上沉积栅极介电层。接着在第一装置区、第二装置区、以及第三装置区中的栅极沟槽中的栅极介电层上沉积第一偶极层。在第二装置区中的栅极沟槽上的第一偶极层为选择性移除,而第一偶极层依旧包覆着第一装置区以及第三装置区中的栅极介电层。接着在第一装置区以及第三装置区中的栅极沟槽中第一偶极层上,以及第二装置区中的栅极介电层上沉积第二偶极层。接着移除第三装置区中的栅极介电层上的第一偶极层以及第二偶极层。接着将工件在大约500℃以及大约900℃之间的温度退火,使得第一偶极层以及第二偶极层的原料(ingredients)可热扩散至栅极介电层以更动临界值电压。接着从工件的栅极沟槽移除第一偶极层以及第二偶极层,在第一装置区、第二装置区、以及第三装置区中的栅极沟槽中形成实质上相同的栅极结构,以形成在第一装置区中的第一晶体管、在第二装置区中的第二晶体管、以及在第三装置区中的第三晶体管。第一装置区中的第一晶体管、第二装置区中的第二晶体管、以及第三装置区中的第三晶体管具不同的临界值电压。由于偶极层不包含在栅极沟槽,而仅作为扩散掺杂物的载体(vehicle),因此形成功能金属栅极堆叠的制程窗口并没有缩小。本公开亦提供了具四个装置区的实施例。

90.图1根据本公开的一些实施例描绘形成半导体装置的方法100的流程图。图2

‑

图15为图1的方法100在各个制程阶段当中的工件的局部剖面图。额外的操作可在方法100之前、之中、以及之后提供,并且所述的一些操作对于方法100的额外的实施例可被移动、取代、或移除。额外的特征可加在图2

‑

图15所示的接点结构,并且以下所述的一些特征在图2

‑

图15所示的内连线(interconnect)结构的其他实施例中可被取代、调整、或移除。

91.参考图1以及图2,方法100包含方框102,其中方框102接收工件200。在方法100完成后,工件200可经制程而成为半导体装置200。在这个意义上,工件200在合适的背景下亦可称为半导体装置200。半导体装置200可包含在为处理器、存储器、以及/或其他集成电路(ic)装置。在一些实施例中,半导体装置200为集成电路(ic)芯片的一部分、系统芯片(system on chip;soc)、或前述的一部分,并包含诸多被动电子装置以及主动微电子装置,如电阻、电容、电感、二极管、p型场效晶体管(pfets)、n型场效晶体管(nfets)、金属氧化物半导体场效晶体管(mosfets)、互补式金属氧化物半导体(cmos)、双极性接面晶体管

(bjts)、横向扩散金属氧化物半导体(laterally diffused mos;ldmos)晶体管、高压晶体管、高频晶体管、其他合适的布件、或前述的组合。晶体管可为平面晶体管或多栅极晶体管,如类鳍式fets(finfets)或栅极全环(gate

‑

all

‑

around;gaa)晶体管。

92.如图2所描绘,半导体装置200包含基板(晶圆)202。在所示的实施例中,基板202包含硅(silicon)。基板202替代性地或者额外地包含另一个元素半导体,如锗(germanium);化合物半导体,如碳化硅(silicon carbide)、砷化镓(gallium arsenide)、磷化镓(gallium phosphide)、磷化铟(indium phosphide)、砷化铟(indium arsenide)、以及/或锑化铟(indium antimonide);合金半导体,如锗化硅(silicon germanium;sige)、磷化砷镓(gaasp)、砷化铝铟(alinas)、砷化铝镓(algaas)、砷化镓铟(gainas)、磷化铟镓(gainp)、以及/或砷磷化镓铟(gainasp);或前述的组合。在一些实施例中,基板202包含一个或多个iii

‑

v组材料、一个或多个ii

‑

iv材料、或前述的组合。在一些实施例中,基板202为绝缘层上半导体(semiconductor

‑

on

‑

insulator)基板,如绝缘体上硅薄膜(silicon

‑

on

‑

insulator;soi)基板、绝缘层上锗化硅(silicon germanium

‑

on

‑

insulator;sgoi)基板、或绝缘体上锗薄膜(germanium

‑

on

‑

insulator;goi)基板。绝缘层上半导体基板可用分离植入氧气(separation by implanted oxygen;simox)、晶圆接合(wafer bonding)、以及/或其他合适的方法制成。根据半导体装置200的设计需求配置,基板202可包含诸多经掺杂的区域(未图示),如p型掺杂区、n型掺杂区、或前述的组合。n型掺杂区(例如,p型井)包含p型掺杂物,如硼(boron)、铟(indium)、其他p型掺杂物、或前述的组合。n型掺杂区(例如,n型井)包含n型掺杂物,如磷(phosphorus)、砷(arsenic)、其他n型掺杂物、或前述的组合。在一些实施例中,基板202包含由p型掺杂物以及n型掺杂物的组合形成的掺杂区。诸多掺杂区可直接在基板202之中或之上形成,例如,提供p井结构、n井结构、双井结构、凸起结构、或前述的组合。可执行离子布植制程、扩散制程、以及/或其他合适的掺杂制程以形成诸多掺杂区。

93.半导体装置200包含在基板202上的主动区204。主动区204可为鳍片形状的半导体特征,或纵向堆叠的纳米结构。如图2所示,主动区204在基板202上沿着x方向横向延伸并且沿着基板202的z方向纵向延伸。在一些实施例中,主动区204可为基板202的一部分(如基板202的材料层的一部分)。例如,硅的主动区204可能由硅的基板202所形成。或者,在一些实施例中,主动区204在材料层中定义,如在基板202上形成一个或多个半导体材料层。例如,主动区204可包含半导体层堆叠,该半导体层堆叠具沉积在基板202上的诸多半导体层(如异质结构(heterostructure))。半导体层可包含任何合适的材料,如硅(silicon)、锗(germanium)、锗化硅(silicon germanium)、其他合适的半导体材料、或前述的组合。半导体层可包含相同或不同的材料、蚀刻速率、构成的原子百分比、构成的重量百分比、厚度、以及/或根据半导体装置200的设计需求的配置。在一些实施例中,半导体层堆叠包含交替的半导体层,如第一材料所组成的多个半导体层以及第二材料所组成的多个半导体层。例如,半导体层堆叠交替硅(silicon)层以及锗化硅(silicon germanium)层(例如,从底层到顶层为锗化硅(sige)/硅(si)/锗化硅(sige)/硅(si)/锗化硅(sige)/硅(si))。在一些实施例中,半导体层堆叠包含相同材料的半导体层但具交替的构成原子百分比,如具第一原子百分比的组分的半导体层以及第二原子百分比的组分的半导体层。例如,半导体层堆叠包含锗化硅(silicon germanium)层,该锗化硅(silicon germanium)层具交替的硅(silicon)以及/或锗(germanium)原子百分比(例如,从底层到顶层为si

a

ge

b

/si

c

ge

d

/si

a

ge

b

/si

c

ge

d

/

glass)制程填充沟槽所形成。可执行化学机械研磨(chemical mechanical polishing;cmp)制程以移除过多的绝缘材料以及/或平坦化隔离特征的顶层表面。在一些实施例中,在形成主动区204(在一些实施例中,使得绝缘材料层填充主动区204以及相邻主动区之间的缝隙(沟槽))以及回蚀(etching back)绝缘材料层以形成隔离特征之后,沉积绝缘材料在基板202之上可形成sti特征。在一些实施例中,隔离特征包含填充沟槽的多层结构,如设置在衬垫介电(liner dielectric)层上的块状(bulk)介电层,其中块状介电层以及衬垫介电层包含根据设计需求的材料(例如,块状介电层,该块状介电层包含设置在包含热氧化物(thermal oxide)的衬垫介电层上的氮化硅(silicon nitride)。

96.在图2所描绘的实施例中,工件200包含在主动区204中的通道区10之上且环绕通道区10的虚设栅极堆叠208。各个虚设栅极堆叠208可包含虚设栅极介电层205以及虚设栅极电极207。在图2所代表的实施例中,虚设栅极堆叠208包含在主动区204上的虚设栅极介电层205以及在虚设栅极介电层205之上的虚设栅极电极207。在一些实施例中,虚设栅极介电层205可由氧化硅(silicon oxide)所形成,而虚设栅极电极207可由多晶硅(polysilicon)所形成。栅极间隔物层210可以任何合适的制程沿着虚设栅极堆叠208侧壁形成,且包含介电材料。栅极间隔物层210的介电材料可包含硅(silicon)、氧(oxygen)、碳(carbon)、氮(nitrogen)、其他合适的材料、或前述的组合(例如,氧化硅(silicon oxide)、氮化硅(silicon nitride)、氮氧化硅(silicon oxynitride)、或碳化硅(silicon carbide)。在一些实施例中,栅极间隔物层210可包含多层结构,如包含氮化硅(silicon nitride)的第一间隔物层以及包含氧化硅(silicon oxide)的第二间隔物层。在一些实施例中,栅极间隔物层210可包含不止一组与栅极堆叠相邻形成的间隔物,如密封间隔物(seal spacers)、偏移间隔物(offset spacers)、牺牲间隔物(sacrificial spacers)、虚设间隔物、以及/或主间隔物。值得注意的是,图2的剖面图描述沿着主动区204的顶层表面的x方向进行剖面。例如,当主动区204为鳍片形状主动区(或者为一个鳍片)时,图2中的虚设栅极堆叠208展示为设置在鳍片的顶层表面上。

97.工件200可进一步包含在与通道区10相邻的源极/漏极区20中形成的源极/漏极特征212。如图2所示,源极/漏极特征212与虚设栅极堆叠208相邻设置。在一些实施例中,源极/漏极特征212利用外延制程在主动区204的源极/漏极区20上形成。外延制程可实施化学气相沉积(cvd)沉积技术(例如,气相外延(vapor

‑

phase expitaxy;vpe)、超高真空化学气相沉积(ultra

‑

high vacuum cvd;uhv

‑

cvd)、低压化学气相沉积(lpcvd)、以及/或等离子体辅助化学气相沉积(pecvd))、分子束外延(molecular beam epitaxy)、其他合适的选择晶膜生长(seg)制程、或前述的组合。源极/漏极特征212可由n型掺杂物或p型掺杂物所掺杂。在一些实施例中,当晶体管配置为n型装置(例如,具n通道),源极/漏极特征212可为包含硅(silicon)的外延层或包含硅

‑

碳(silicon

‑

carbon)的外延层,所述外延层掺杂了磷(phosphorus)、其他n型掺杂物、或前述的组合(例如,形成硅:磷(si:p)外延层或硅:碳:磷(si:c:p)外延层)。在一些实施例中,当晶体管配置为p型装置(例如,具p通道),源极/漏极特征212可为包含硅以及锗(silicon

‑

and

‑

germanium)的外延层,所述外延层掺杂了硼(boron)、其他p型掺杂物、或前述的组合(例如,形成硅:锗:硼(si:ge:b)外延层)。在一些实施例中,执行退火制程以启动(activate)半导体装置200的源极/漏极特征212中的掺杂物。

98.工件200可包含接点蚀刻停止层(contact etch stop layer;cesl)214,沉积在源

极/漏极特征212上。在一些情况下,cesl 214亦可沉积在栅极间隔物层210的侧表面上。在一些实施例中,cesl 214亦可由氮化硅(silicon nitride)、氮氧化硅(silicon oxynitride)、或碳氮化硅(silicon carbonitride)所形成,且可利用原子层沉积(atomic layer deposition;ald)顺应性地形成。介电层216亦可称为层间介电(interlayer dielectric;ild)层216,沉积在cesl 214上。介电层216可利用可流动的化学气相沉积(flowable chemical vapor deposition;fcvd)制程形成。在一些实施例中,在使用fcvd制程之后,沉积的介电层216可由紫外光(uv)辐射的入射、退火、或两者皆有,进行固化(cured)。在一些实施例中,介电层216可包含介电材料,包含例如,氧化硅(silicon oxide)、正硅酸乙酯(teos)形成的氧化物、磷硅酸盐玻璃(psg)、硼磷硅酸盐玻璃(bpsg)、低介电系数(low

‑

k)介电材料、其他合适的介电材料、或前述的组合。低介电系数介电材料的范例包含(fsg)、(carbon)(silicon oxide)、black (加利福尼亚圣塔克拉拉的应用材料公司(applied materials of santa clara,california))、干凝胶(xerogel)、气凝胶(aerogel)、非晶碳氟化合物(amorphous fluorinated carbon)、聚对二甲苯(parylene)、苯并环丁烯(bcb)、silk(密西根密德兰的陶氏化学(dow chemical,midland,michigan))、聚酰亚胺(polyimide)、其他低介电系数介电材料、或前述的组合。

99.参考图1以及图3,方法100包含方框104,其中移除虚设栅极堆叠208以形成栅极沟槽218。在一些实施例中,可利用合适的干蚀刻制程以及湿蚀刻制程的组合移除虚设栅极堆叠208以形成栅极沟槽218。栅极沟槽218暴露主动区204的通道区10。虽然虚设栅极堆叠208以及栅极沟槽218描绘为具有沿着z方向的笔直侧壁,但在一些实施例中亦可为非笔直且可包含颈缩轮廓(necking profile)。缩颈轮廓可能会缩小在栅极沟槽218沉积多个薄层以形成功能金属栅极堆叠的制程窗口。

100.参考图1以及图4,方法100包含方框106,其中在栅极沟槽218中沉积界面层220。在一些实施例中,界面层220可由氧化硅(silicon oxide)所形成。

101.参考图1以及图5,方法100包含方框108,其中在界面层220上沉积栅极介电层222。栅极介电层222可包含具高介电系数的介电材料,例如高于氧化硅(silicon oxide)的介电系数(k≈3.9)。高介电系数(high

‑

k)介电材料的范例包含铪(hafnium)、锆(zirconium)、钽(tantalum)、钛(titanium)、氧(oxygen)、氮(nitrogen)、其他合适的构成物、或前述的组合。在一些实施例中,栅极介电层222可包含高介电系数介电材料,包含例如二氧化铪(hfo2)、氧化硅铪(hfsio)、氮氧化硅铪(hfsion)、氧化钽铪(hftao)、氧化钛铪(hftio)、氧化锆铪(hfzro)、二氧化锆(zro2)、二氧化钛(tio2)、五氧化二钽(ta2o5)、其他合适的高介电系数介电材料、或前述的组合。

102.如下面所将描述,工件200可包含具有不同临界值电压的晶体管的多个装置区域(如三个装置区域、四个装置区域、或更多装置区域),并且在图2

‑

图5所示的结构可横跨且在所述多个装置区域重复,但重复的结构已省略,而以图2

‑

图5所示的省略符号(

“…”

)作代表。对待不同装置区域有所不同的方法100的操作将会与图6

‑

图15在下面作描述。为了描述的简易性与清晰性,图6

‑

图14描绘不同装置区域中的区域“i”的局部剖面图。

103.参考图1以及图6,方法100包含方框110,其中沉积第一偶极层224在栅极介电层222上。在图6

‑

图15所描绘的一些实施例中,工件200包含三个装置区域

‑

第一装置区1100、第二装置区1200、以及第三装置区1300。如上面所描述,图6描绘第一装置区1100、第二装置

区1200、以及第三装置区1300中的区域“i”的局部剖面图。第一偶极层224沉积在第一装置区1100、第二装置区1200、以及第三装置区1300中的栅极沟槽中的栅极介电层222上。在一些实施例中,第一偶极层224可由氧化镧(lanthanum oxide)、氧化钇(yttrium oxide)、或氧化铝(aluminum oxide)形成,且可利用原子层沉积(atomic layer deposition;ald)进行沉积。在一些实施例中,形成第一偶极层224所使用的ald制程可包含大约2至大约10循环之间。在所述实施例中,第一偶极层224可具大约至大约的厚度之间。在一个实施例中,第一偶极层224可由氧化镧(lanthanum oxide)形成。

104.参考图1、图7、图8、以及图9,方法100包含方框112,其中从第二装置区1200选择性地移除第一偶极层224。在一些实施例中,可利用微影制程技术以及蚀刻技术以执行方框112的操作。范例制程在图7

‑

图9展示。首先参考图7。先在第一偶极层224上形成硬遮罩层226以及在硬遮罩层226上沉积底部抗反射涂膜(bottom antireflective coating;barc)层228。在一些情况下,硬遮罩层226可为单一层或多个层。当硬遮罩层226为单一薄层时,硬遮罩层226可包含氧化硅(silicon oxide)、氮化硅(silicon nitride)、或氮氧化硅(silicon oxynitride)。当硬遮罩层226为多个层时,硬遮罩层226可包含硅(silicon)薄层以及在硅(silicon)薄层上的氮化硅(silicon nitride)薄层。barc层228可包含氮氧化硅(silicon oxynitride)、聚合物、或合适的材料。为了图案化barc层228以及硬遮罩层226,光阻层可毯式地沉积在工件200上,包含在第一装置区1100、第二装置区1200、以及第三装置区1300中的barc层228上。光阻层可为单一薄层或多个层,如三层。光阻层接着暴露于穿透遮罩或者从遮罩反射的辐射、在后烘烤制程中进行烘烤、以及在显影液中进行显影,以形成图案化的光阻遮罩。barc层228以及硬遮罩层226接着利用图案化的光阻遮罩进形图案化以形成在第二装置区1200上方具开口的蚀刻遮罩。接着,于蚀刻制程中利用蚀刻遮罩选择性蚀刻掉在第二装置区1200中的栅极沟槽中的第一偶极层224,如图8所描绘。蚀刻制程可为干蚀刻制程、湿蚀刻制程、或合适的蚀刻制程。参考图9,在第一偶极层224从第二装置区1200中的栅极沟槽中选择性蚀刻掉之后,利用合适的蚀刻制程移除第一装置区1100以及第三装置区1300中的硬遮罩层226以及barc层228。

105.参考图1以及图10,方法100包含方框114,其中第二偶极层230沉积在工件200上。如图10所示,第二偶极层230沉积在第一装置区1100以及第三装置区1300中的栅极沟槽中的第一偶极层224上,以及沉积在第二装置区1200中的栅极沟槽中的栅极介电层222上。在一些实施例中,第二偶极层230以及第一偶极层224可具相同的成分。与第一偶极层224相似,第二偶极层230亦可由氧化镧(lanthanum oxide)、氧化钇(yttrium oxide)、或氧化铝(aluminum oxide)所形成,且可利用原子层沉积(atomic layer deposition;ald)作沉积。在一些实施例中,沉积第二偶极层230所使用的ald制程可包含大约2至大约10循环之间。在一些实施例中,第二偶极层230可具大约至大约的厚度之间。在一实施例中,第二偶极层230可由氧化镧(lanthanum oxide)所形成。

106.参考图1、图11、图12、以及图13,方法100包含方框116,其中从第三装置区1300选择性地移除第二偶极层230。与方框112的操作相似,亦可利用微影制程技术以及蚀刻技术执行方框116的操作。例如,如图11所示,可在第二偶极层230上形成硬遮罩层232以及底部抗反射涂膜(barc)层234。由于硬遮罩层232可相似于硬遮罩层226以及barc层234可相似于

barc层228,硬遮罩层232以及barc层234的详细叙述为了简洁而省略。在此之后,可接着在barc层234上沉积阻剂层。接着阻剂层、barc层234、以及硬遮罩层232以相似于对应的方框112所描述的方式进行图案化而不在此重复。图案化的硬遮罩层232允许选择性移除第三装置区1300中的栅极沟槽中的第一偶极层224以及第二偶极层230,而暴露第三装置区1300中的栅极沟槽中的栅极介电层222。如图12所描绘,在此刻,第一装置区1100中的栅极沟槽包含以上所述的第一偶极层224以及第二偶极层230;第二装置区1200中的栅极沟槽包含以上所述的第二偶极层230;以及第三装置区1300中的栅极沟槽没有第一偶极层224以及第二偶极层230。换句话说,第一装置区1100中的栅极沟槽中的第一偶极层224以及第二偶极层230的总厚度(沿着z方向)大于第二装置区1200中的栅极沟槽中的第二偶极层230的总厚度,而第三装置区1300中的栅极沟槽没有任何偶极层。在从第三装置区1300中的栅极沟槽选择性移除第一偶极层224以及第二偶极层230之后,如图13所描绘,可接着从第一装置区1100以及第二装置区1200移除硬遮罩层232以及barc层234。

107.参考图1以及图13,方法100包含方框118,其中工件200在退火制程300进行退火。在方框118,利用退火制程300以热驱动第一偶极层224以及/或第二偶极层230中的元素至第一装置区1100以及第二装置区1200中的栅极沟槽中的栅极介电层222。第一偶极层224以及第二偶极层230作为扩散掺杂载体以带着元素直接接触栅极介电层222。退火制程300可为快速热退火(rapid thermal annealing;rta)制程、激光尖退火(laser spike annealing)制程、急骤退火(flash anneal)制程、或炉退火(furnace anneal)制程。在一些实施例中,退火制程300包含大约500℃至大约900℃之间的高退火温度,使得第一偶极层224以及/或第二偶极层230中的镧(lanthanum)、钇(yttrium)、或铝(aluminum)得以扩散至第一装置区1100以及第二装置区1200中的栅极沟槽中的栅极介电层222。由于第三装置区1300中的栅极沟槽没有任何偶极层,在方框118的退火制程300并不造成任何偶极层材料扩散至第三装置区1300中的栅极介电层222。在一些实施例中,退火制程300可持续大约5秒至大约20秒之间。

108.参考图1以及图14,方法100包含方框120,其中从工件200移除第一偶极层224以及第二偶极层230。在方框118热驱动第一偶极层224以及第二偶极层230中的元素至栅极介电层222之后,从第一装置区1100中的栅极沟槽移除第一偶极层224以及第二偶极层230,以及从第二装置区1200中的栅极沟槽移除第二偶极层230。方框120的操作可由干蚀刻制程、湿蚀刻制程、或合适的蚀刻制程所执行。如图14所示,在方框118的退火制程300造成第一装置区1100中的栅极沟槽中的第一栅极介电层2221以及第二装置区1200中的栅极沟槽中的第二栅极介电层2222。由于缺乏任何偶极层,第三装置区1300中的栅极沟槽中的栅极介电层222维持实质上不变。

109.也观察到较厚的偶极层有助于栅极介电层222中的偶极层材料(dipole layer material)的更高掺杂浓度。例如,当栅极介电层222由氧化铪(hafnium oxide)所形成以及第一偶极层224/第二偶极层230由氧化镧(lanthanum oxide)所形成,在方框118的操作可造成第一装置区1100中的栅极沟槽中的第一栅极介电层2221中的第一镧(lanthanum)浓度,以及第二装置区1200中的栅极沟槽中的第二栅极介电层2222中的第二镧(lanthanum)浓度。由于第三装置区1300中的栅极沟槽没有任何偶极层,第三装置区1300中的栅极沟槽中的栅极介电层222包含零浓度的第三镧(lanthanum)浓度。由于第一装置区1100中的栅极

沟槽包含第一偶极层224以及第二偶极层230两者,第一镧(lanthanum)浓度大于第二镧(lanthanum)浓度,并且大于零浓度的第三镧(lanthanum)浓度。各个第一、第二、以及第三镧(lanthanum)浓度可以镧(lanthanum)浓度(意即,第一偶极层224/第二偶极层230的[镧(lanthanum)]或[la])对铪(hafnium)浓度(意即栅极介电层222中的[铪(hafnium)]或[hf])的比例所代表。在上述的范例中,第一镧(lanthanum)浓度(意即,第一镧(lanthanum)对铪(hafnium)的比例)可为大约0.4([镧(la)]/[铪(hf)]),以及第二镧(lanthanum)浓度(意即,第二镧(lanthanum)对铪(hafnium)的比例)可为大约0.2([镧(la)]/[铪(hf)]),而第三镧(lanthanum)浓度(意即,第三镧(lanthanum)对铪(hafnium)的比例)为零。前面的描述大致上适用于其他偶极层材料,如钇(yttrium)以及铝(aluminum),以及其他栅极介电材料,如氧化硅铪(hfsio)、氮氧化硅铪(hfsion)、氧化钽铪(hftao)、氧化钛铪(hftio)、氧化锆铪(hfzro)、二氧化锆(zro2)、二氧化钛(tio2)、五氧化二钽(ta2o5),前提是不同偶极层材料可具不同扩散率以及不同偶极层材料在不同栅极介电层可具有不同固溶度(solid solubility)。

[0110]

参考图1以及图15,方法100包含方框122,其中执行进一步的制程以在第一装置区1100形成第一晶体管410、在第二装置区1200形成第二晶体管420、以及在第三装置区1300形成第三晶体管430。如图15所示,第一晶体管410包含第一栅极介电层2221,第二晶体管420包含第二栅极介电层2222,以及第三晶体管430包含栅极介电层222。各个第一晶体管410、第二晶体管420、以及第三晶体管430除了包含界面层220以及第一栅极介电层2221/第二栅极介电层2222/栅极介电层222之外还包含功能金属栅极堆叠236。由于第一晶体管410中的第一栅极介电层2221、第二晶体管420中的第二栅极介电层2222、以及第三晶体管430中的栅极介电层222仅为不同的成分而非不同的尺寸,因此所有不同装置区1100、1200、以及1300的功能金属栅极堆叠236为结构上以及尺寸上一致。

[0111]

功能金属栅极堆叠236可包含一个或多个功函数层以及金属填充层。n型装置以及p型装置可具不同功函数层。在一些实施例中,虽然n型装置区域以及p型装置区域可共享特定共同功函数层,但n型装置区域可包含不在p型装置区域的一个或多个功函数层。相似地,在另外的实施例中,p型装置区域可包含不在n型装置区域的一个或多个功函数层。p型功函数层包含任何合适的p型功函数材料,如氮化钛(tin)、氮化钽(tan)、氮化硅钽(tasn)、钌(ru)、钼(mo)、铝(al)、氮化钨(wn)、氮化碳钨(wcn)、二硅化锆(zrsi2)、二硅化钼(mosi2)、二硅化钽(tasi2)、二硅化镍(nisi2)、其他p型功函数材料、或前述的组合。n型功函数层包含任何合适的n型功函数材料,如钛(ti)、铝(al)、银(ag)、锰(mn)、锆(zr)、铝化钛(tial)、碳化铝钛(tialc)、碳硅化铝钛(tialsic)、碳化钽(tac)、氮化碳钽(tacn)、氮化硅钽(tasin)、铝化钽(taal)、碳化铝钽(taalc)、碳铝化硅钽(tasialc)、氮化铝钛(tialn)、其他n型功函数材料、或前述的组合。值得注意p型功函数层并不限于使用在p型装置区域,以及n型功函数层并不限于使用在n型装置区域。p型功函数层以及n型功函数层可适用于n型装置区域以及p型装置区域以达到理想的临界值电压。可在n型装置区域以及p型装置区域上沉积金属填充层,使得金属填充层填补不同装置区域中的栅极沟槽的任何剩余的部分。金属填充层可包含合适的导电材料,如铝(aluminum;al)、钨(tungsten;w)、钌(ruthenium;ru)、以及/或铜(copper;cu)。金属填充层可额外或全体包含其他金属、金属氮化物、其他合适的材料、或前述的组合。

[0112]

由于使用第一栅极介电层2221、第二栅极介电层2222、以及栅极介电层222所造成的不同界面偶极,第一装置区1100中的第一晶体管410、第二装置区1200中的第二晶体管420、以及第三装置区1300中的第三晶体管430具不同临界值电压。不同金属氧化物具有不同氧(oxygen)原子的面密度(areal density)。例如,氧化镧(lanthanum oxide)以及氧化钇(yttrium oxide)中的氧原子的面密度大于比氧化硅(silicon oxide)中的氧原子的面密度,而氧化铝(aluminum oxide)以及氧化铪(hafnium oxide)中的氧原子的面密度大于氧化硅中的氧原子的面密度。在这些金属氧化物中,氧化铝具最大的氧原子的面密度。在栅极介电层222本质上包含氧化铪(hafnium oxide),以及界面层220本质上包含氧化硅的实施例中,可形成朝栅极介电层222的界面偶极。当第一偶极层224以及第二偶极层230中的镧(lanthanum)或钇(yttrium)(具小于氧化硅的氧原子的面密度)允许扩散至栅极介电层222,可缩减或反转朝栅极介电层的界面偶极。当第一偶极层224以及第二偶极层230中的铝(aluminum)(具大于氧化硅的氧原子的面密度)允许扩散至栅极介电层222,可增加朝栅极介电层的界面偶极。

[0113]

在第一栅极介电层2221具第一镧(lanthanum)浓度(意即,第一镧对铪(hafnium)的比例)为大约0.4([镧(la)]/[铪(hf)])、第二栅极介电层2222具第二镧浓度(意即,第二镧对铪的比例)为大约0.2([镧(la)]/[铪(hf)])、以及栅极介电层222具零的第三镧浓度(意即,第三镧对铪的比例)为大约零([镧(la)]/[铪(hf)])的实施例中,第一晶体管410具第一临界值电压(vt1)、第二晶体管420具第二临界值电压(vt2)、以及第三晶体管430具第三临界值电压(vt3)。当第一晶体管410、第二晶体管420、以及第三晶体管430为n型晶体管,vt1可比vt3小大约150毫伏(mv),且vt2可比vt3小大约50毫伏(mv)。当第一晶体管410、第二晶体管420、以及第三晶体管430为p型晶体管,vt1可比vt3大大约150毫伏(mv),且vt1可比vt2大大约50毫伏(mv)。

[0114]

第一晶体管410、第二晶体管420、以及第三晶体管430可实施在静态随机存取存储器(static random access memory;sram)单元以改进sram单元的信号

‑

噪声容限(signal

‑

to

‑

noise margin;snm)以及写入容限(write margin;wm)。例如,第一晶体管410、第二晶体管420、以及第三晶体管430可实施在图29以及图30所示的8

‑

晶体管(eight

‑

transistor;8t)sram单元900,或图31以及图32所示的10

‑

晶体管(ten

‑

transistor;10t)sram单元1000。

[0115]

首先参考图29所示的8t sram单元900的电路图。其中wl为字元线、bl为位元线、blb为互补位元线、rwl为读取字元线、以及rbl为读取位元线。8t sram单元900包含形成第一反向器的第一上拉晶体管(pu1)906以及第一下拉晶体管(pd1)910、形成与第一反向器交叉耦合的第二反向器的第二上拉晶体管(pu2)908以及第二下拉晶体管(pd2)912、配置以写入由交叉耦合的第一反向器以及第二反向器所存储的数据的第一通道栅极晶体管(pg1)902以及第二通道栅极晶体管(pg2)904。8t sram单元900进一步包含读取下拉晶体管(read pull

‑

down;rpd)914以及读取通道栅极晶体管(read pass

‑

gate;rpg)916,读取下拉晶体管(rpd)914以及读取通道栅极晶体管(rpg)916形成读取端(read port;rp)918以存取由交叉耦合的第一反向器以及第二反向器所存储的数据。第一上拉晶体管(pu1)906、第一下拉晶体管(pd1)910、以及第一通道栅极晶体管(pg1)902的漏极电极电性连接在第一数据存储节点q。第二上拉晶体管(pu2)908、第二下拉晶体管(pd2)912、以及第二通道栅极晶体管(pg2)904的漏极电极电性连接在第二数据存储节点qb。第二上拉晶体管(pu2)908以及第二下拉

晶体管(pd2)912的栅极电极通过第一数据存储节点q电性连接至第一下拉晶体管(pd1)910、第一通道栅极晶体管(pg1)902、以及第一上拉晶体管(pu1)906的漏极电极,而第一上拉晶体管(pu1)906以及第一下拉晶体管(pd1)910的栅极电极通过第二数据存储节点qb电性连接至第二下拉晶体管(pd2)912、第二通道栅极晶体管(pg2)904、以及第二上拉晶体管(pu2)908的漏极电极。第一下拉晶体管(pd1)910、第二下拉晶体管(pd2)912、以及读取下拉晶体管(read pull

‑

down;rpd)914的源极电极连接至第一电源供应节点vss,而第一上拉晶体管(pu1)906以及第二上拉晶体管(pu2)908的源极电极连接至第二电源供应节点vdd。根据一实施例,第一电源供应节点vss电性连接至虚拟接地(virtual ground)920,而第二电源供应节点vdd电性连接至正电位,该正电位由sram的电源供应电路(未图示)供应。在一些实施例中,虚拟接地920包含保持晶体管(hold transistor)922以及电源栅极晶体管924。

[0116]

图29中的电路图可在图30所示的8t sram单元900的布局图中实施。在一些实施例中,各个第一通道栅极晶体管(pg1)902、第二通道栅极晶体管(pg2)904、第一下拉晶体管(pd1)910、第二下拉晶体管(pd2)912、读取下拉晶体管(read pull

‑

down;rpd)914、以及读取通道栅极晶体管(read pass

‑

gate;rpg)916包含设置在两主动区905上的栅极结构903。各个第一上拉晶体管(pu1)906以及第二上拉晶体管(pu2)908包含设置在单一主动区905上的栅极结构903(包含第一栅极结构903

‑

1以及第二栅极结构903

‑

2)。在主动区为鳍片形状的情况下,前者可称为双鳍片装置而后者可称为单鳍片装置。

[0117]

在一实施例中,电源栅极晶体管924可为第一晶体管410。由于第一晶体管410在第一晶体管410、第二晶体管420、以及第三晶体管430当中具最高临界值电压(第一临界值电压,vt1),第一晶体管410具最小漏电流且可缩减在电源栅极晶体管924的漏电。在相同的实施例中,读取端(read port;rp)918可由第三晶体管430所形成。由于第三晶体管430在第一晶体管410、第二晶体管420、以及第三晶体管430当中具最低临界值电压(第三临界值电压,vt3),第三晶体管430具最高切换速率且可增进8t sram单元900的读取速率。在相同的实施例中,具中位数的临界值电压位阶(第二临界值电压,vt2)的第二晶体管420可施加在各个第一通道栅极晶体管(pg1)902、第二通道栅极晶体管(pg2)904、第一下拉晶体管(pd1)910、以及第二下拉晶体管(pd2)912以得到平衡的信号

‑

噪声容限(snms)。由第一下拉晶体管(pd1)910、第二通道栅极晶体管(pg2)904、以及读取通道栅极晶体管(read pass

‑

gate;rpg)916共享第一栅极结构903

‑

1,所以两第二晶体管420(以pd1以及pg1实施)以及一第三晶体管430(以rpg实施)共享第一栅极结构903

‑

1。相似地,由于第一通道栅极晶体管(pg1)902、第二下拉晶体管(pd2)912、以及读取下拉晶体管(read pull

‑

down;rpd)914共享第二栅极结构903

‑

2,所以两第二晶体管420(以pd2以及pg2实施)以及一第三晶体管430(以rpd实施)共享第二栅极结构903

‑

2。如这里所使用的栅极结构被称为由多个晶体管共享,因为该栅极结构的功能金属栅极堆叠在所述晶体管上方延伸。参考图15。虽然第一晶体管410、第二晶体管420、以及第三晶体管430具不同的栅极介电层,但所述晶体管可具有共同功能金属栅极堆叠236。共同功能金属栅极堆叠236允许本公开的晶体管与不止一个晶体管共享。

[0118]

接着请参考图31所示的10t sram单元1000的电路图。其中wl为字元线、bl为位元线、blb为互补位元线、rwl为读取字元线、rbl为读取位元线、以及rblb为读取互补位元线。10t sram单元1000包含形成第一反向器的第一上拉晶体管(pu1)1006以及第一下拉晶体管

(pd1)1010、形成与第一反向器交叉耦合的第二反向器的第二上拉晶体管(pu2)1008以及第二下拉晶体管(pd2)1012、配置以写入由交叉耦合的第一反向器以及第二反向器所存储的数据的第一通道栅极晶体管(pg1)1002以及第二通道栅极晶体管(pg2)1004。10t sram单元1000进一步包含第一读取端(first read port;rp1)1014以及第二读取端(second read port;rp2)1016以存取由交叉耦合的第一反向器以及第二反向器所存储的数据。第一读取端1014包含第一读取下拉晶体管(first read pull

‑

down;rpd1)1018以及第一读取通道栅极晶体管(first read pass

‑

gate;rpg1)1020,而第二读取端1016包含第二读取下拉晶体管(second read pull

‑

down;rpd2)1022以及第二读取通道栅极晶体管(second read pass

‑

gate;rpg2)1024。第一上拉晶体管(pu1)1006、第一下拉晶体管(pd1)1010、以及第一通道栅极晶体管(pg1)1002的漏极电极电性连接在第一数据存储节点q。第二上拉晶体管(pu2)1008、第二下拉晶体管(pd2)1012、以及第二通道栅极晶体管(pg2)1004的漏极电极电性连接在第二数据存储节点qb。第二上拉晶体管(pu2)1008以及第二下拉晶体管(pd2)1012的栅极电极通过第一数据存储节点q电性连接至第一下拉晶体管(pd1)1010、第一通道栅极晶体管(pg1)1002、以及第一上拉晶体管(pu1)1006的漏极电极,而第一上拉晶体管(pu1)1006以及第一下拉晶体管(pd1)1010的栅极电极通过第二数据存储节点qb电性连接至第二下拉晶体管(pd2)1012、第二通道栅极晶体管(pg2)1004、以及第二上拉晶体管(pu2)1008的漏极电极。第一下拉晶体管(pd1)1010、第二下拉晶体管(pd2)1012、第一读取下拉晶体管(first read pull

‑

down;rpd1)1018以及第二读取下拉晶体管(second read pull

‑

down;rpd2)1022的源极电极连接至第一电源供应节点vss,而第一上拉晶体管(pu1)1006以及第二上拉晶体管(pu2)1008的源极电极连接至第二电源供应节点vdd。根据一实施例,第一电源供应节点vss电性连接至虚拟接地(virtual ground)1026,而第二电源供应节点vdd电性连接至正电位,该正电位由sram的电源供应电路(未图示)供应。在一些实施例中,虚拟接地1026包含保持晶体管(hold transistor)1028以及电源栅极晶体管1030。

[0119]

图31中的电路图可在图32所示的10t sram单元1000的布局图中实施。在一些实施例中,各个第一通道栅极晶体管(pg1)1002、第二通道栅极晶体管(pg2)1004、第一下拉晶体管(pd1)1010、第二下拉晶体管(pd2)1012、第一读取下拉晶体管(first read pull

‑

down;rpd1)1018、第一读取通道栅极晶体管(first read pass

‑

gate;rpg1)1020、第二读取下拉晶体管(second read pull

‑

down;rpd2)1022、以及第二读取通道栅极晶体管(second read pass

‑

gate;rpg2)1024包含设置在两主动区1005上的栅极结构1003。各个第一上拉晶体管(pu1)1006以及第二上拉晶体管(pu2)1008包含设置在单一主动区1005上的栅极结构1003(包含第一栅极结构1003

‑

1以及第二栅极结构1003

‑

2)。在主动区为鳍片形状的情况下,前者可称为双鳍片装置而后者可称为单鳍片装置。

[0120]

在一实施例中,电源栅极晶体管1030可为第一晶体管410。由于第一晶体管410在第一晶体管410、第二晶体管420、以及第三晶体管430当中具最高临界值电压(第一临界值电压,vt1),第一晶体管410具最小漏电流且可缩减在电源栅极晶体管1030的漏电。在相同的实施例中,第一读取端(first read port;rp1)1014以及第二读取端(second read port;rp2)1016可由第三晶体管430所形成。由于第三晶体管430在第一晶体管410、第二晶体管420、以及第三晶体管430当中具最低临界值电压(第三临界值电压,vt3),所以第三晶体管430具最高切换速率且可增进10t sram单元1000的读取速率。在相同的实施例中,具中

位数的临界值电压位阶(第二临界值电压,vt2)的第二晶体管420可施加在各个第一通道栅极晶体管(pg1)1002、第二通道栅极晶体管(pg2)1004、第一下拉晶体管(pd1)1010、以及第二下拉晶体管(pd2)1012以得到平衡的信号

‑

噪声容限(snms)。由于第一读取下拉晶体管(first read pull

‑

down;rpd1)1018、第一下拉晶体管(pd1)1010、第二通道栅极晶体管(pg2)1004、以及第二读取通道栅极晶体管(second read pass

‑

gate;rpg2)1024共享第一栅极结构1003

‑

1,所以两第二晶体管420(以pd1以及pg1实施)以及两第三晶体管430(以rpd1以及rpg2实施)共享第一栅极结构1003

‑

1。相似地,由于第一读取通道栅极晶体管(first read pass

‑

gate;rpg1)1020、第一通道栅极晶体管(pg1)1002、第二下拉晶体管(pd2)1012、以及第二读取下拉晶体管(second read pull

‑

down;rpd2)1022共享第二栅极结构1003

‑

2,所以两第二晶体管420(以pd2以及pg2实施)以及两第三晶体管430(以rpg1以及rpd2实施)共享第二栅极结构1003

‑

2。如上所述,栅极结构被称为与多个晶体管共享,因为该栅极结构的功能金属栅极堆叠在所述晶体管上方延伸。参考图28a以及图28b。虽然第一晶体管810、第二晶体管820、第三晶体管830、以及第四晶体管840具有不同的栅极介电层,但所述晶体管可具有共同功能金属栅极堆叠236。共同功能金属栅极堆叠236允许本公开的晶体管与不止一个晶体管共享。

[0121]

图16根据本公开的一些实施例描绘形成半导体装置的方法500的流程图。图2

‑

图5、图17

‑

图27、图28a、以及图28b为图16中的方法500的诸多制程当中的工件200的局部剖面图。额外的操作可在方法500之前、之中、或之后提供,而且可移动、取代、或移除描述的方法500的额外实施例的一些操作。可在图2

‑

图5、图17

‑

图27、图28a、以及图28b所描述的接点结构中加入额外的特征,且可移动、取代、或移除在图2

‑

图5、图17

‑

图27、图28a、以及图28b所展示的内连线(interconnect)结构的其他实施例中的一些以下描述的特征。

[0122]

参考图16以及图2,方法500包含方框502,其中方框502接收工件200。由于在方框502的操作与上述的方框102相似,在此的描述将不重复。除此之外,工件200的详细描述以及在工件200的诸多特征已在上面所描述而为了简洁亦在此移除。

[0123]

参考图16以及图3,方法500包含方框504,其中移除虚设栅极堆叠208以形成栅极沟槽218。由于在方框504的操作与上述的方框104相似,在此的描述将不重复。除此之外,虚设栅极堆叠208以及栅极沟槽218的详细描述已在上面所描述而为了简洁亦在此移除。

[0124]

参考图16以及图4,方法500包含方框506,其中在栅极沟槽218中沉积界面层220。由于在方框506的操作与上述的方框106相似,在此的描述将不重复。除此之外,界面层220的详细描述已在上面所描述而为了简洁亦在此移除。

[0125]

参考图16以及图5,方法500包含方框508,其中在界面层220上沉积栅极介电层222。由于在方框508的操作与上述的方框108相似,在此的描述将不重复。除此之外,栅极介电层222的详细描述已在上面所描述而为了简洁亦在此移除。

[0126]

如下面所将描述,工件200可包含具有不同临界值电压的晶体管的多个装置区域(如三个装置区域、四个装置区域、或更多装置区域),并且在图2

‑

图5所示的结构可横跨且在所述多个装置区域重复,但重复的结构已省略,而以图2

‑

图5所示的省略符号(

“…”

)作代表。对待不同装置区域有所不同的方法500的操作将会与图17

‑

图27、图28a、以及图28b在下面作描述。为了描述的简易性与清晰性,图17

‑

图27描绘不同装置区域中的区域“i”的局部剖面图。

[0127]

参考图16以及图6,方法500包含方框510,其中第一偶极层224沉积在栅极介电层222上。在图17

‑

图27、图28a、以及图28b所描绘的一些实施例中,工件200包含四个装置区域

‑

第一装置区3100、第二装置区3200、第三装置区3300、以及第四装置区3400。如上面所描述,图17描绘第一装置区1100、第二装置区1200、第三装置区1300、以及第四装置区3400中的区域“i”的局部剖面图。第一偶极层224沉积在第一装置区1100、第二装置区1200、第三装置区1300、以及第四装置区3400中的栅极沟槽中的栅极介电层222上。在一些实施例中,第一偶极层224可由氧化镧、氧化钇、或氧化铝形成,且可利用原子层沉积(ald)进行沉积。在一些实施例中,形成第一偶极层224所使用的ald制程可包含大约2至大约10循环之间。在所述实施例中,第一偶极层224可具大约至大约的厚度之间。在一个实施例中,第一偶极层224可由氧化镧形成。

[0128]

参考图16、图18、图19、以及图20,方法500包含方框512,其中从第三装置区3300以及第四装置区3400选择性地移除第一偶极层224。在一些实施例中,可利用微影制程技术以及蚀刻技术以执行方框512的操作。范例制程在图18

‑

图20展示。首先参考图18。先在第一偶极层224上形成硬遮罩层226以及在硬遮罩层226上沉积底部抗反射涂膜层228。在一些情况下,硬遮罩层226可为单一薄层或多个层。当硬遮罩层226为单一薄层时,硬遮罩层226可包含氧化硅、氮化硅、或氮氧化硅。当硬遮罩层226为多个层时,硬遮罩层226可包含硅薄层以及在硅薄层上的氮化硅薄层。barc层228可包含氮氧化硅、聚合物、或合适的材料。为了图案化barc层228以及硬遮罩层226,光阻层可毯式地沉积在工件200上,包含在第一装置区1100、第二装置区1200、以及第三装置区1300中的barc层228上。光阻层可为单一薄层或多个层,如三层。光阻层接着暴露于穿透遮罩或者从遮罩反射的辐射、在后烘烤制程中进行烘烤、以及在显影液中进行显影,以形成图案化的光阻遮罩。barc层228以及硬遮罩层226接着利用图案化的光阻遮罩进形图案化以形成在第三装置区3300以及第四装置区3400上方具开口的蚀刻遮罩。接着利用蚀刻遮罩于蚀刻制程中选择性蚀刻掉在第三装置区3300以及第四装置区3400中的栅极沟槽中的第一偶极层224,如图19所描绘。蚀刻制程可为干蚀刻制程、湿蚀刻制程、或合适的蚀刻制程。参考图20,在第一偶极层224从第三装置区3300以及第四装置区3400中的栅极沟槽中选择性蚀刻掉之后,第一装置区3100以及第二装置区3200中的硬遮罩层226以及barc层228利用合适的蚀刻制程移除。

[0129]

参考图16以及图21,方法500包含方框514,其中工件200在第一退火制程600进行退火。在方框514,利用第一退火制程600以热驱动第一偶极层224中的元素至第一装置区3100以及第二装置区3200中的栅极沟槽中的栅极介电层222。第一偶极层224作为扩散掺杂载体以带着元素直接接触第一装置区3100以及第二装置区3200中的栅极介电层222。第一退火制程600可为快速热退火制程、激光尖退火制程、急骤退火制程、或炉退火制程。在一些实施例中,第一退火制程600包含大约500℃至大约900℃之间的高退火温度,使得第一偶极层224中的镧、钇、或铝得以扩散至第一装置区3100以及第二装置区3200中的栅极沟槽中的栅极介电层222。由于第三装置区3300以及第四装置区3400中的栅极沟槽没有第一偶极层224,在方框514的第一退火制程600并不造成任何偶极层材料扩散至第三装置区3300以及第四装置区3400中的栅极介电层222。在一些实施例中,第一退火制程600可持续大约5秒至大约20秒之间。如图22所示,在方框514的第一退火制程600之后,第一偶极层224中的元素扩散至栅极介电层222以在第一装置区3100以及第二装置区3200中的栅极沟槽中形成第二

栅极介电层2232。

[0130]

参考图16以及图22,方法500包含方框516,其中从工件200选择性地移除第一偶极层224。在一些实施例中,在方框516可利用微影制程技术以及蚀刻技术以避免损害第三装置区3300以及第四装置区3400中的栅极介电层222。例如,可在工件200上沉积硬遮罩、底部抗反射涂膜层、以及光阻层。接着图案化硬遮罩、barc层、以及光阻层以形成蚀刻遮罩,该蚀刻遮罩暴露第一装置区3100以及第二装置区3200中的栅极沟槽中的第一偶极层224。接着利用蚀刻遮罩以干蚀刻制程、湿蚀刻制程、或合适的蚀刻制程对第一偶极层224进行蚀刻。接着移除由硬遮罩以及barc层所形成的蚀刻遮罩。在方框516的结尾,暴露第一装置区3100以及第二装置区3200中的栅极沟槽中的第二栅极介电层2232,以及暴露第三装置区3300以及第四装置区3400中的栅极沟槽中的栅极介电层222。

[0131]

参考图16以及图23,方法500包含方框518,其中在工件200上沉积第二偶极层240。如图23所示,第二偶极层240沉积在第一装置区3100以及第二装置区3200中的栅极沟槽中的第二栅极介电层2232上,以及沉积在第三装置区3300以及第四装置区3400中的栅极沟槽中的栅极介电层222上。在一些实施例中,第二偶极层240以及第一偶极层224可具相同的成分。与第一偶极层224相似,第二偶极层240亦可由氧化镧、氧化钇、或氧化铝所形成,且可利用原子层沉积(ald)作沉积。在一些实施例中,沉积第二偶极层240所使用的ald制程可包含大约2至大约5循环之间。在一些实施例中,第二偶极层240可具大约至大约的厚度之间。在一实施例中,第二偶极层240可由氧化镧所形成。与第2

‑

15图所描绘的实施例中的第二偶极层230不同之处在于,图17

‑

图27、图28a、以及图28b所描绘的实施例中的第二偶极层240较薄。具有大约至大约的厚度之间的第二偶极层240比具有大约至大约的厚度之间的第一偶极层224还薄。

[0132]

参考图16、图24、图25、以及图26,方法500包含方框520,其中从第二装置区3200以及第四装置区3400中的栅极沟槽选择性地移除第二偶极层240。与方法100中的方框112的操作相似,亦可利用微影制程技术以及蚀刻技术执行方框520的操作。例如,如图24所示,可在第二偶极层240上形成硬遮罩层242以及底部抗反射涂膜(barc)层244。由于硬遮罩层242可相似于硬遮罩层226,以及barc层244可相似于barc层228,硬遮罩层242以及barc层244的详细叙述为了简洁而省略。在此之后,可接着在barc层244上沉积光阻层。接着光阻层、barc层244、以及硬遮罩层242以相似于对应的方法100的方框112所描述的方式进行图案化而不在此重复。图案化的硬遮罩层242允许选择性移除第二装置区3200以及第四装置区3400中的栅极沟槽中的第二偶极层240,而暴露第二装置区3200中的第二栅极介电层2232以及第四装置区3400中的栅极介电层222。如图25所描绘,在此刻,第一装置区3100中的栅极沟槽包含以上所述的第二栅极介电层2232以及第二偶极层240;第二装置区3200中的栅极沟槽包含以上所述的第二栅极介电层2232;第三装置区3300中的栅极沟槽包含以上所述的第二偶极层240;以及第四装置区3400中的栅极沟槽没有被任何偶极层覆盖。在从第二装置区3200以及第四装置区3400中的栅极沟槽选择性移除第二偶极层240之后,如图26所描绘,可接着从第一装置区3100以及第三装置区3300移除硬遮罩层242以及barc层244。

[0133]

参考图16以及图26,方法500包含方框522,其中工件200在第二退火制程700进行退火。在方框522,利用第二退火制程700以热驱动第二偶极层240中的元素至第一装置区

3100中的栅极沟槽中的第二栅极介电层2232以及第三装置区3300中的栅极沟槽中的栅极介电层222。第二偶极层240作为扩散掺杂载体以带着元素直接接触第二栅极介电层2232以及栅极介电层222。第二退火制程700可为快速热退火制程、激光尖退火制程、急骤退火制程、或炉退火制程。在一些实施例中,第二退火制程700包含大约500℃至大约900℃之间的高退火温度,使得第二偶极层240中的镧、钇、或铝得以扩散至第一装置区3100的栅极沟槽中的第二栅极介电层2232以及第三装置区3300中的栅极沟槽中的栅极介电层222。由于第四装置区3400中的栅极沟槽没有任何偶极层,在方框522的退火制程700并不造成任何偶极层材料扩散至第四装置区3400中的栅极介电层222。在一些实施例中,第二退火制程700可持续大约5秒至大约20秒之间。

[0134]

参考图16以及图27,方法100包含方框524,其中从工件200移除第二偶极层240。方框524的操作可由干蚀刻制程、湿蚀刻制程、或合适的蚀刻制程所执行。接着,热驱动第二偶极层240中的元素至第一装置区3100中的第二栅极介电层2232以及第三装置区3300中的栅极介电层222。在方框524,从第一装置区3100以及第三装置区3300中的栅极沟槽移除第二偶极层240。由于在方框522的第二退火制程,第一栅极介电层2231在第一装置区3100中的栅极沟槽上形成,以及第三栅极介电层2233在第三装置区3300中的栅极沟槽上形成。总结而言,退火制程600驱入的第一偶极层224以及退火制程700驱入的第二偶极层240造成第一装置区3100中的第一栅极介电层2231;退火制程600驱入的第一偶极层224造成第二装置区3200中的第二栅极介电层2232;退火制程700驱入的第二偶极层240造成第三装置区3300中的第三栅极介电层2233,而第四装置区3400中的栅极介电层222没有任何偶极层的元素扩散。

[0135]

也观察到较厚的偶极层以及增进的退火制程有助于栅极介电层222中的偶极层材料的更高掺杂浓度。例如,当栅极介电层222由氧化铪所形成以及第一偶极层224/第二偶极层240由氧化镧所形成,在方框526的操作可造成第一装置区3100中的第一栅极介电层2231中的第一镧浓度,第二装置区3200中的第二栅极介电层2232中的第二镧浓度,第三装置区3300中的第三镧浓度,以及第四装置区3400中的第四镧浓度。第一镧浓度大于第二镧浓度,第二镧浓度大于第三镧浓度,以及第三镧浓度大于第四镧浓度。由于第四装置区3400中的栅极沟槽没有任何偶极层,第四镧浓度为零。各个第一、第二、第三、以及第四镧浓度可以镧浓度(意即,第一偶极层224/第二偶极层240的[镧]或[la])对铪浓度(意即栅极介电层222中的[铪]或[hf])的比例所代表。在上述的范例中,第一镧浓度(意即,第一镧对铪的比例)可为大约0.6([镧(la)]/[铪(hf)]),第二镧浓度(意即,第二镧对铪的比例)可为大约0.4([镧(la)]/[铪(hf)]),以及第三镧浓度(意即,第三镧对铪的比例)可为大约0.2([镧(la)]/[铪(hf)]),而第四镧浓度(意即,第四镧对铪的比例)为零。前面的描述大致上适用于其他偶极层材料,如钇以及铝,以及其他栅极介电材料,如氧化硅铪(hfsio)、氮氧化硅铪(hfsion)、氧化钽铪(hftao)、氧化钛铪(hftio)、氧化锆铪(hfzro)、二氧化锆(zro2)、二氧化钛(tio2)、五氧化二钽(ta2o5),前提是不同偶极层材料可具不同扩散率以及不同偶极层材料在不同栅极介电层可具不同固溶度(solid solubility)。

[0136]

参考图16、图28a以及图28b,方法500包含方框526,其中执行进一步的制程以在第一装置区3100形成第一晶体管810、在第二装置区3200形成第二晶体管820、在第三装置区3300形成第三晶体管830、以及在第四装置区3400形成第四晶体管840。如图28a以及图28b

所示,第一晶体管810包含第一栅极介电层2231,第二晶体管820包含第二栅极介电层2232,第三晶体管830包含第三栅极介电层2233,以及第四晶体管840包含栅极介电层222。各个第一晶体管810、第二晶体管820、第三晶体管830、以及第四晶体管840除了包含界面层220以及第一栅极介电层2231/第二栅极介电层2232/第三栅极介电层2233/栅极介电层222之外还包含功能金属栅极堆叠236。由于第一晶体管810中的第一栅极介电层2231、第二晶体管820中的第二栅极介电层2232、第三晶体管830中的第三栅极介电层2233、以及第四晶体管840中的栅极介电层222仅为不同的成分而非不同的尺寸,因此所有不同装置区3100、3200、3300、以及3400的功能金属栅极堆叠236为结构上以及尺寸上均匀。

[0137]

功能金属栅极堆叠236可包含一个或多个功函数层以及金属填充层。n型装置以及p型装置可具不同功函数层。在一些实施例中,虽然n型装置区域以及p型装置区域可共享特定共同功函数层,但n型装置区域可包含不在p型装置区域的一个或多个功函数层。相似地,在另外的实施例中,p型装置区域可包含不在n型装置区域的一个或多个功函数层。p型功函数层包含任何合适的p型功函数材料,如氮化钛(tin)、氮化钽(tan)、氮化硅钽(tasn)、钌(ru)、钼(mo)、铝(al)、氮化钨(wn)、氮化碳钨(wcn)、二硅化锆(zrsi2)、二硅化钼(mosi2)、二硅化钽(tasi2)、二硅化镍(nisi2)、其他p型功函数材料、或前述的组合。n型功函数层包含任何合适的n型功函数材料,如钛(ti)、铝(al)、银(ag)、锰(mn)、锆(zr)、铝化钛(tial)、碳化铝钛(tialc)、碳硅化铝钛(tialsic)、碳化钽(tac)、氮化碳钽(tacn)、氮化硅钽(tasin)、铝化钽(taal)、碳化铝钽(taalc)、碳铝化硅钽(tasialc)、氮化铝钛(tialn)、其他n型功函数材料、或前述的组合。值得注意p型功函数层并不限于使用在p型装置区域,以及n型功函数层并不限于使用在n型装置区域。p型功函数层以及n型功函数层可适用于n型装置区域以及p型装置区域以达到理想的临界值电压。可在n型装置区域以及p型装置区域上沉积金属填充层,使得金属填充层填补不同装置区域中的栅极沟槽的任何剩余的部分。金属填充层可包含合适的导电材料,如铝(aluminum;al)、钨(tungsten;w)、钌(ruthenium;ru)、以及/或铜(copper;cu)。金属填充层可额外或全体包含其他金属、金属氮化物、其他合适的材料、或前述的组合。

[0138]

由于使用第一栅极介电层2231、第二栅极介电层2232、第三栅极介电层2233、以及栅极介电层222所造成的不同界面偶极,第一装置区3100中的第一晶体管810、第二装置区3200中的第二晶体管820、第三装置区3300中的第三晶体管830、以及第四装置区3400中的第四晶体管840具有不同临界值电压。不同金属氧化物具不同氧原子的面密度。例如,氧化镧以及氧化钇中的氧原子的面密度大于氧化硅中的氧原子的面密度,而氧化铝以及氧化铪中的氧原子的面密度大于氧化硅中的氧原子的面密度。在这些金属氧化物中,氧化铝具有最大的氧原子的面密度。在栅极介电层222本质上包含氧化铪,以及界面层220本质上包含氧化硅的实施例中,可形成朝栅极介电层222的界面偶极。当第一偶极层224以及第二偶极层240中的镧或钇(具小于氧化硅的氧原子的面密度)允许扩散至栅极介电层222,可缩减或反转朝栅极介电层的界面偶极。当第一偶极层224以及第二偶极层240中的铝(具大于氧化硅的氧原子的面密度)允许扩散至栅极介电层222,可增加朝栅极介电层的界面偶极。

[0139]

在第一栅极介电层2231具第一镧(lanthanum)浓度(意即,第一镧对铪的比例)为大约0.6([镧(la)]/[铪(hf)])、第二栅极介电层2232具第二镧浓度(意即,第二镧对铪的比例)为大约0.4([镧(la)]/[铪(hf)])、第三栅极介电层2233具第三镧浓度(意即,第三镧对

铪的比例)为大约0.2([镧(la)]/[铪(hf)])、以及栅极介电层222具零的第四镧浓度(意即,第四镧对铪的比例)为大约零([镧(la)]/[铪(hf)])的实施例中,第一晶体管810具有第一临界值电压(vt1)、第二晶体管820具有第二临界值电压(vt2)、第三晶体管830具有第三临界值电压(vt3)、以及第四晶体管840具有第四临界值电压(vt4)。当第一晶体管810、第二晶体管820、第三晶体管830、以及第四晶体管840为n型晶体管,vt1可比vt4小大约250毫伏(mv),vt2可比vt4小大约150毫伏(mv),且vt3可比vt4小大约50毫伏(mv)。当第一晶体管810、第二晶体管820、第三晶体管830、以及第四晶体管840为p型晶体管,vt1可比vt4大大约250毫伏(mv),vt1可比vt3大大约150毫伏(mv),且vt1可比vt2大大约50毫伏(mv)。

[0140]

第一晶体管810、第二晶体管820、第三晶体管830、以及第四晶体管840可实施在静态随机存取存储器(static random access memory;sram)单元以改进sram单元的信号

‑

噪声容限(signal

‑

to

‑

noise margin;snm)以及写入容限(write margin;wm)。例如,第一晶体管810、第二晶体管820、第三晶体管830、以及第四晶体管840可实施在图29以及图30所示的8

‑

晶体管(eight

‑

transistor;8t)sram单元900中,或图31以及图32所示的10

‑

晶体管(ten

‑

transistor;10t)sram单元1000中。

[0141]

在一些实施例中,第一晶体管810、第二晶体管820、第三晶体管830、以及第四晶体管840可实施在图29以及图30所示的8t sram单元900中。在一范例中,具有第一临界值电压vt1的第一晶体管810可实施为第一通道栅极晶体管(pg1)902以及第二通道栅极晶体管(pg2)904;具有第二临界值电压vt2的第二晶体管820可实施为第一下拉晶体管(pd1)910以及第二下拉晶体管(pd2)912;具有第三临界值电压vt3的第三晶体管830可实施为读取通道栅极晶体管(read pass

‑

gate;rpg)916;以及具有第四临界值电压vt4的第四晶体管840可实施为读取下拉晶体管(read pull

‑

down;rpd)914。在前述范例中,由于第三晶体管830以及第四晶体管840相较于第一晶体管810以及第二晶体管820具有较低的临界值电压,读取端(read port;rp)918可具更快的读取速率。除此之外,由于具有较高的临界值电压的晶体管具较小的漏电流(意即,驱动电流;drive current),通过第一通道栅极晶体管(pg1)902以及第二通道栅极晶体管(pg2)904的漏电流小于通过第一下拉晶体管(pd1)910以及第二下拉晶体管(pd2)912的漏电流。此安排可允许8t sram单元900的beta(β)比值上升,而beta(β)比值上升相当于(translates into)增进的读取稳定度。

[0142]

在所述实施例中,由于第一下拉晶体管(pd1)910、第二通道栅极晶体管(pg2)904、以及读取通道栅极晶体管(read pass

‑

gate;rpg)916之间共享第一栅极结构903

‑

1,所以一个第一晶体管810(以pg2实施)、一个第二晶体管820(以pd1实施)、以及一个第三晶体管830(以rpg实施)之间共享第一栅极结构903

‑

1。相似地,由于第一通道栅极晶体管(pg1)902、第二下拉晶体管(pd2)912、以及读取下拉晶体管(read pull

‑

down;rpd)914之间共享第二栅极结构903

‑

2,所以一个第一晶体管810(以pg1实施)、一个第二晶体管820(以pd2实施)、以及一个第三晶体管830(以rpd实施)之间共享第二栅极结构903

‑

2。如上所述,由于栅极结构的功能金属堆叠在多个晶体管上延伸,栅极结构被称为由多个晶体管共享。参考图28a以及图28b。虽然第一晶体管810、第二晶体管820、第三晶体管830、以及第四晶体管840具有不同的栅极介电层,但前述的晶体管可具有共同功能金属栅极堆叠236。共同功能金属栅极堆叠236允许本公开的晶体管与不止一个晶体管之间共享。

[0143]

在其他的一些实施例中,第一晶体管810、第二晶体管820、第三晶体管830、以及第

四晶体管840可实施在图31以及图32所示的10t sram单元1000中。在一范例中,具有第一临界值电压vt1的第一晶体管810可实施为第一通道栅极晶体管(pg1)1002以及第二通道栅极晶体管(pg2)1004;具有第二临界值电压vt2的第二晶体管820可实施为第一下拉晶体管(pd1)1010以及第二下拉晶体管(pd2)1012;具有第三临界值电压vt3的第三晶体管830可实施为第一读取通道栅极晶体管(first read pass

‑

gate;rpg1)1020以及第二读取通道栅极晶体管(second read pass

‑

gate;rpg2)1024;以及具有第四临界值电压vt4的第四晶体管840可实施为第一读取下拉晶体管(first read pull

‑

down;rpd1)1018以及第二读取下拉晶体管(second read pull

‑

down;rpd2)1022。在前述范例中,由于第三晶体管830以及第四晶体管840相较于第一晶体管810以及第二晶体管820具有较低的临界值电压,第一读取端(first read port;rp1)1014以及第二读取端(second read port;rp2)1016可具更快的读取速率。除此之外,由于具有较高的临界值电压的晶体管具较小的漏电流(意即,驱动电流;drive current),通过第一通道栅极晶体管(pg1)1002以及第二通道栅极晶体管(pg2)1004的漏电流小于通过第一下拉晶体管(pd1)1010以及第二下拉晶体管(pd2)1012的漏电流。此安排可允许10t sram单元1000的beta(β)比值上升,而beta(β)比值上升相当于(translates into)增进的读取稳定度。

[0144]

在所述实施例中,由于第一读取下拉晶体管(first read pull

‑

down;rpd1)1018、第一下拉晶体管(pd1)1010、第二通道栅极晶体管(pg2)1004、以及第二读取通道栅极晶体管(second read pass

‑

gate;rpg2)1024之间共享第一栅极结构1003

‑

1,所以一个第一晶体管810(以pg2实施)、一个第二晶体管820(以pd1实施)、一个第三晶体管830(以rpg2实施)、以及一个第四晶体管840(以rpd1实施)之间共享第一栅极结构1003

‑

1。相似地,由于第一读取通道栅极晶体管(first read pass

‑

gate;rpg1)1020、第一通道栅极晶体管(pg1)1002、第二下拉晶体管(pd2)1012、以及第二读取下拉晶体管(second read pull

‑

down;rpd2)1022之间共享第二栅极结构1003

‑

2,所以一个第一晶体管810(以pg1实施)、一个第二晶体管820(以pd2实施)、一个第三晶体管830(以rpg1实施)、以及一个第四晶体管840(以rpd2实施)之间共享第二栅极结构1003

‑

2。如上所述,由于栅极结构的功能金属堆叠在多个晶体管上延伸,栅极结构被称为由多个晶体管共享。参考图28a以及图28b。随然第一晶体管810、第二晶体管820、第三晶体管830、以及第四晶体管840具有不同的栅极介电层,但前述的晶体管可具有共同功能金属栅极堆叠236。共同功能金属栅极堆叠236允许本公开的晶体管与不止一个晶体管之间共享。

[0145]

在本公开全文当中,对于具相似的成分的特征可使用相似的参考数字编号,前提是前述的多个装置区域以及特征对于不同的实施例可重新编号。例如,图6中的三个装置区域为第一装置区1100、第二装置区1200、以及第三装置区1300,而图17中的四个装置区域为第一装置区3100、第二装置区3200、第三装置区3300、以及第四装置区3400。相同的编号约定适用于栅极介电层(例如,图15中的222、2221、2222以及图28a以及图28b中的222、2231、2232、以及2233)、晶体管(例如,图15中的410、420、430以及图28a以及图28b中的810、820、830、以及840)。除此之外,虽然第一偶极层224可分别与方法100以及500相似,但方法100中的第二偶极层230以及方法500中的第二偶极层240可为不相似。因此,前述的第二偶极层以不同的参考数字编号表示。除此之外,界面层220、栅极介电层222(或第一、第二、或第三栅极介电层,如不同实施例中可能的情况)、以及功能金属栅极堆叠236在一些情况下可被称

为金属栅极结构或功能金属栅极结构。

[0146]

根据本公开的方法公开一种提供不同临界值电压的晶体管的机制,而该机制不影响形成栅极结构的制程窗口。在此选择性沉积一个或多个偶极层在栅极介电层且作为扩散掺杂物的载体以掺杂栅极介电层,而不是引入存留在栅极沟槽的额外的偶极层。根据偶极层的厚度、退火制程的持续时间、以及偶极层的材料,经掺杂的栅极介电层与界面层的界面可具有不同的界面偶极。在掺杂制程之后,从栅极沟槽移除所使用的偶极层。亦即,本公开的方法保留了利用偶极层的不同临界值电压的好处而没有相关了坏处。本公开提供了在具有三个装置区域的半导体装置中实现三个阶级的临界值电压的实施例,本公开亦提供了在具有四个装置区域的半导体装置中实现四个阶级的临界值电压的实施例。本公开中具有不同阶级的晶体管可施加于sram单元,如8t sram单元或10t sram单元,以增进sram单元的效能。在检阅本实施例后,在本领域具通常技艺的人员将意识到在更多装置有更高临界值电压是有可能的。

[0147]

在一实施例中,本公开提供一种半导体装置,包含第一晶体管、第二晶体管、以及第三晶体管。第一晶体管包含第一主动区、第一栅极介电层,在第一主动区上,第一栅极介电层包含偶极层材料的第一浓度、以及第一栅极结构,设置在第一栅极介电层上。第二晶体管包含第二主动区、第二栅极介电层,在第二主动区上,第二栅极介电层包含偶极层材料的第二浓度、以及第二栅极结构,设置在第二栅极介电层上。第三晶体管包含第三主动区、第三栅极介电层,在第三主动区上,第三栅极介电层包含偶极层材料的第三浓度、以及第三栅极结构,设置在第三栅极介电层上。偶极层材料包含氧化镧、氧化铝、或氧化钇。第一浓度大于第二浓度,以及第二浓度大于第三浓度。

[0148]

在一些实施例中,第一栅极结构、第二栅极结构、以及第三栅极结构实质上彼此相同。在一些实施例中,第三浓度为零。在一些实施例中,第一晶体管、第二晶体管、以及第三晶体管为n型晶体管。第一晶体管包含第一临界值电压、第二晶体管包含第二临界值电压、以及第三晶体管包含第三临界值电压。第一临界值电压小于第二临界值电压,以及第二临界值电压小于第三临界值电压。在一些实施例中,第一晶体管、第二晶体管、以及第三晶体管为p型晶体管。第一晶体管包含第一临界值电压、第二晶体管包含第二临界值电压、以及第三晶体管包含第三临界值电压。第一临界值电压大于第二临界值电压,以及第二临界值电压大于第三临界值电压。在一些实施例中,第一栅极介电层、第二栅极介电层、以及第三栅极介电层进一步包含氧化铪。

[0149]

在另一实施例中,本公开提供一种半导体装置的制造方法,包含提供工件,工件包含第一装置区、第二装置区、以及第三装置区,在第一装置区形成第一栅极沟槽、在第二装置区形成第二栅极沟槽、以及在第三装置区形成第三栅极沟槽,沉积栅极介电层在第一栅极沟槽、第二栅极沟槽、以及第三栅极沟槽中,沉积第一偶极层在第一栅极沟槽、第二栅极沟槽、以及第三栅极沟槽中的栅极介电层上,选择性地移除第二栅极沟槽中的第一偶极层,沉积第二偶极层,第二偶极层在第一栅极沟槽中的第一偶极层、第二栅极沟槽中的栅极介电层、以及第三栅极沟槽中的第一偶极层上,选择性地移除第三栅极沟槽中的第一偶极层以及第二偶极层,以及退火工件。

[0150]

在一些实施例中,半导体装置的制造方法进一步包含在退火工件之后,从工件移除第一偶极层以及第二偶极层。在一些实施例中,第一偶极层以及第二偶极层包含氧化镧、

氧化铝、或氧化钇。在一些实施例中,退火工件的操作包含在大约500℃以及大约900℃之间的温度。在一些实施例中,退火工件的操作包含在大约5秒至大约20秒之间的持续时间。在一些实施例中,第一偶极层的厚度以及第二偶极层的厚度为大约至大约之间。在一些实施例中,选择性地移除第二栅极沟槽中的第一偶极层的操作包含在工件上沉积硬遮罩层、在硬遮罩层上沉积底部抗反射涂膜层、图案化底部抗反射涂膜层以及硬遮罩层以暴露第二栅极沟槽、以及在硬遮罩层以及底部抗反射涂膜层覆盖第一栅极沟槽以及第三栅极沟槽的同时,移除第二栅极沟槽中的第一偶极层。在一些实施例中,第一偶极层包含第一厚度、第二偶极层包含第二厚度、以及第一厚度实质上与第二厚度相同。

[0151]

在另一实施例中,本公开提供一种半导体装置的制造方法包含提供工件,工件包含第一装置区、第二装置区、第三装置区、以及第四装置区,在第一装置区形成第一栅极沟槽、在第二装置区形成第二栅极沟槽、在第三装置区形成第三栅极沟槽、以及在第四装置区形成第四栅极沟槽,沉积一栅极介电层,栅极介电层在第一栅极沟槽、第二栅极沟槽、第三栅极沟槽、以及第四栅极沟槽中,沉积第一偶极层,第一偶极层在第一栅极沟槽、第二栅极沟槽、第三栅极沟槽、以及第四栅极沟槽中的栅极介电层上,选择性地移除第三栅极沟槽以及第四栅极沟槽中的第一偶极层,对工件进行第一退火制程,移除第一栅极沟槽以及第二栅极沟槽中的第一偶极层,在移除第一偶极层之后,沉积第二偶极层第一栅极沟槽、第二栅极沟槽、第三栅极沟槽、以及第四栅极沟槽上,选择性地移除第二栅极沟槽以及第四栅极沟槽中的第二偶极层,对工件进行第二退火制程,以及从工件移除第二偶极层。

[0152]

在一些实施例中,第一偶极层包含第一厚度、第二偶极层包含第二厚度、以及第一厚度大于第二厚度。在一些实施例中,第一厚度为大约至大约之间以及第二厚度为大约至大约之间。在一些实施例中,第一偶极层以及第二偶极层包含氧化镧、氧化铝、或氧化钇。在一些实施例中,第一退火制程以及第二退火制程包含在大约500℃以及大约900℃之间的温度。在一些实施例中,第一退火制程以及第二退火制程包含在大约5秒至大约20秒之间的持续时间。

[0153]

前述内容概述了几个实施例的特征使得本领域技术人员可更容易了解本公开的各面向。本领域技术人员应该理解,他们可以容易地将公开用作设计或修改其他制程和结构的基础,以实现与本文介绍的实施例相同的目的和/或实现相同的优点。本领域技术人员还应该认知到,等效的构造不脱离本公开的精神和范围,并且在不脱离本公开的精神和范围的情况下,它们可以进行各种改变,替换和变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。