1.本揭露是关于半导体元件及其制造方法。

背景技术:

2.随着集成电路尺寸的微缩,集成电路的布局被改变以减小集成电路所占据的总面积。可透过使用比先前的集成电路元件小的新结构的集成电路元件来实现布局面积的减小。亦可以透过减小集成电路层中电路元件之间的距离来实现布局面积的减小。

技术实现要素:

3.依据的部分实施例,提供一种半导体元件,包含:第一组半导体鳍片、第二组半导体鳍片、第一栅极结构、vdd线和vss线。第一组半导体鳍片沿第一方向延伸并以第一鳍片至鳍片间距配置。第二组半导体鳍片沿第一方向延伸并以第二鳍片至鳍片间距配置,第二组半导体鳍片与第一组半导体鳍片透过无鳍片区域分开,无鳍片区域大于第一鳍片至鳍片间距和第二鳍片至鳍片间距。第一栅极结构沿不同于第一方向的第二方向跨越第一组半导体鳍片、无鳍片区域和第二组半导体鳍片延伸。vdd线和vss线沿第一方向在第一栅极结构上延伸,其中第一组半导体鳍片和第二组半导体鳍片在上视图中位于vdd线和vss线之间,并且在上视图中vdd线与第一组半导体鳍片之间的重叠面积与vss线与第二组半导体鳍片之间的重叠面积不同。

附图说明

4.当结合附图阅读时,根据以下详细描述可以最好地理解的各方面。应理解,根据行业中的标准实践,各种特征未按比例绘制。实际上,为了清楚起见,各种特征的尺寸可以任意地增加或减小。

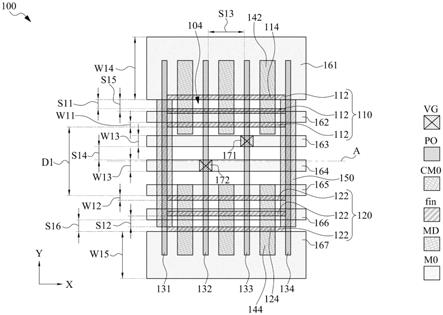

5.图1a是根据部分实施例的半导体元件的布局图;

6.图1b至图1d是根据部分实施例的使用图1a的布局制造的半导体元件的视图;

7.图2a是根据部分实施例的半导体元件的布局图;

8.图2b至图2c是根据部分实施例的使用图2a的布局制造的半导体元件的视图;

9.图3a是根据部分实施例的半导体元件的布局图;

10.图3b至图3c是根据部分实施例的使用图3a的布局制造的半导体元件的视图;

11.图4a是根据部分实施例的半导体元件的布局图;

12.图4b至图4c是根据部分实施例的使用图4a的布局制造的半导体元件的视图;

13.图5a是根据部分实施例的半导体元件的布局图;

14.图5b至图5c是根据部分实施例的使用图5a的布局制造的半导体元件的视图;

15.图6是根据部分实施例的用于设计半导体元件的布局的系统的示意图;

16.图7是根据部分实施例的半导体元件制造系统的框图。

17.【符号说明】

18.100:布局

19.100a:半导体元件

20.102a:基板

21.104:隔离结构布局图案

22.104a:隔离结构

23.106a:栅极间隔物

24.110:鳍片组布局图案

25.110a:鳍片组区域

26.112:鳍片布局图案

27.112a:鳍片

28.114:源极/漏极区域布局图案

29.114a:源极/漏极区域

30.120:鳍片组布局图案

31.120a:鳍片组

32.120b:鳍片组区域

33.122:鳍片布局图案

34.122a:鳍片

35.124:源极/漏极区域布局图案

36.124a:源极/漏极区域

37.131:栅极布局图案

38.131a:栅极结构

39.132:栅极布局图案

40.132a:栅极结构

41.133:栅极布局图案

42.133a:栅极结构

43.134:栅极布局图案

44.134a:栅极结构

45.142:源极/漏极接触布局图案

46.142a:源极/漏极接触

47.143a:源极/漏极接触

48.144:源极/漏极接触布局图案

49.144a:源极/漏极接触

50.150:切割布局图案

51.161:金属线布局图案

52.161a:金属线

53.162:金属线布局图案

54.162a:金属线

55.163:金属线布局图案

56.163a:金属线

57.164:金属线布局图案

58.164a:金属线

59.165:金属线布局图案

60.165a:金属线

61.166:金属线布局图案

62.166a:金属线

63.167:金属线布局图案

64.167a:金属线

65.171:栅极接触布局图案

66.171a:栅极接触

67.172:栅极接触布局图案

68.172a:栅极接触

69.173a:栅极接触

70.200:布局

71.200a:半导体元件

72.202a:基板

73.204:隔离结构布局图案

74.204a:隔离结构

75.210:鳍片组布局图案

76.210a:鳍片组

77.212:鳍片布局图案

78.212a:鳍片

79.214:源极/漏极区域布局图案

80.214a:源极/漏极区域

81.220:鳍片组布局图案

82.220a:鳍片组

83.220b:鳍片组

84.222:鳍片布局图案

85.222a:鳍片

86.224:源极/漏极区域布局图案

87.224a:源极/漏极区域

88.231:栅极布局图案

89.231a:栅极结构

90.232:栅极布局图案

91.232a:栅极结构

92.233:栅极布局图案

93.233a:栅极结构

94.234:栅极布局图案

95.234a:栅极结构

96.242:源极/漏极接触布局图案

97.242a:源极/漏极接触

98.244:源极/漏极接触布局图案

99.244a:源极/漏极接触

100.250:切割布局图案

101.261:金属线布局图案

102.261a:金属线

103.262:金属线布局图案

104.262a:金属线

105.263:金属线布局图案

106.263a:金属线

107.264:金属线布局图案

108.264a:金属线

109.265:金属线布局图案

110.265a:金属线

111.266:金属线布局图案

112.266a:金属线

113.267:金属线布局图案

114.267a:金属线

115.271:栅极接触布局图案

116.271a:栅极接触

117.272:栅极接触布局图案

118.272a:栅极接触

119.300:布局

120.300a:半导体元件

121.302a:基板

122.304:隔离结构布局图案

123.304a:隔离结构

124.310:鳍片组布局图案

125.310a:鳍片组区域

126.312:鳍片布局图案

127.312a:鳍片

128.314:源极/漏极区域布局图案

129.314a:源极/漏极区域

130.320:鳍片组布局图案

131.320a:鳍片组区域

132.322:鳍片布局图案

133.322a:鳍片

134.324:源极/漏极区域布局图案

135.324a:源极/漏极区域

136.331:栅极布局图案

137.331a:栅极结构

138.332:栅极布局图案

139.332a:栅极结构

140.333:栅极布局图案

141.333a:栅极结构

142.334:栅极布局图案

143.334a:栅极结构

144.335:栅极布局图案

145.335a:栅极结构

146.336:栅极布局图案

147.336a:栅极结构

148.337:栅极布局图案

149.337a:栅极结构

150.338:栅极布局图案

151.338a:栅极结构

152.342:源极/漏极接触布局图案

153.342a:源极/漏极接触

154.344:源极/漏极接触布局图案

155.344a:第二源极/漏极接触

156.361:金属线布局图案

157.361a:金属线

158.362:金属线布局图案

159.362a:金属线

160.363:金属线布局图案

161.363a:金属线

162.364:金属线布局图案

163.364a:金属线

164.365:金属线布局图案

165.365a:金属线

166.366:金属线布局图案

167.366a:金属线

168.367:金属线布局图案

169.367a:金属线

170.371:栅极接触布局图案

171.371a:栅极接触

172.372:栅极接触布局图案

173.372a:栅极接触

174.373:栅极接触布局图案

175.373a:栅极接触

176.374:栅极接触布局图案

177.374a:栅极接触

178.400:布局

179.400a:半导体元件

180.402a:基板

181.404:隔离结构布局图案

182.404a:隔离结构

183.410:鳍片组布局图案

184.410a:鳍片组区域

185.412:鳍片布局图案

186.412a:鳍片

187.414:源极/漏极区域布局图案

188.414a:源极/漏极区域

189.420:鳍片组布局图案

190.420a:鳍片组区域

191.422:鳍片布局图案

192.422a:鳍片

193.424:源极/漏极区域布局图案

194.424a:源极/漏极区域

195.431:栅极布局图案

196.431a:栅极结构

197.432:栅极布局图案

198.432a:栅极结构

199.433:栅极布局图案

200.433a:栅极结构

201.434:栅极布局图案

202.434a:栅极结构

203.440:鳍片组布局图案

204.440a:鳍片组

205.442:源极/漏极接触布局图案

206.442a:源极/漏极接触

207.444:源极/漏极接触布局图案

208.444a:源极/漏极接触

209.450:切割布局图案

210.461:金属线布局图案

211.461a:金属线

212.462:金属线布局图案

213.462a:金属线

214.463:金属线布局图案

215.463a:金属线

216.464:金属线布局图案

217.464a:金属线

218.465:金属线布局图案

219.465a:金属线

220.466:金属线布局图案

221.466a:金属线

222.467:金属线布局图案

223.467a:金属线

224.471:栅极接触布局图案

225.471a:栅极接触

226.472:栅极接触布局图案

227.472a:栅极接触

228.474a:栅极接触

229.481:源极/漏极导孔布局图案

230.481a:源极/漏极导孔

231.482:源极/漏极导孔布局图案

232.482a:源极/漏极导孔

233.483:源极/漏极导孔布局图案

234.483a:源极/漏极导孔

235.500:布局

236.500a:半导体元件

237.502a:基板

238.504:隔离结构布局图案

239.504a:隔离结构

240.510:鳍片组布局图案

241.510a:鳍片组区域

242.512:鳍片组布局图案

243.512a:鳍片

244.514:源极/漏极区域布局图案

245.514a:源极/漏极区域

246.520:鳍片组布局图案

247.520a:鳍片组区域

248.522:鳍片布局图案

249.522a:鳍片

250.524:源极/漏极区域布局图案

251.524a:源极/漏极区域

252.531:栅极布局图案

253.531a:栅极结构

254.532:栅极布局图案

255.532a:栅极结构

256.533:栅极布局图案

257.533a:栅极结构

258.534:栅极布局图案

259.534a:栅极结构

260.535a:栅极结构

261.542:源极/漏极接触布局图案

262.542a:源极/漏极接触

263.544:源极/漏极接触布局图案

264.544a:源极/漏极接触

265.550:切割布局图案

266.561:金属线布局图案

267.561a:金属线

268.562:金属线布局图案

269.562a:金属线

270.563:金属线布局图案

271.563a:金属线

272.564:金属线布局图案

273.564a:金属线

274.565:金属线布局图案

275.565a:金属线

276.566:金属线布局图案

277.566a:金属线

278.567:金属线布局图案

279.567a:金属线

280.571:栅极接触布局图案

281.571a:栅极接触

282.572:栅极接触布局图案

283.572a:栅极接触

284.581:源极/漏极导孔布局图案

285.581a:源极/漏极导孔

286.582:源极/漏极导孔布局图案

287.582a:源极/漏极导孔

288.583:源极/漏极导孔布局图案

289.583a:源极/漏极导孔

290.600:电子设计自动化系统

291.602:处理器

292.604:计算机可读储存媒体

293.606:指令集、指令

294.607:设计布局

295.608:总线

296.609:设计规则检查平台

297.610:输入/输出接口

298.612:网络接口

299.614:网络

300.616:界面

301.620:制造商

302.622:集成电路制造工具

303.630:遮罩室

304.632:遮罩制造工具

305.700:制造系统

306.720:设计厂

307.722:设计布局

308.730:光罩厂

309.732:数据准备

310.744:光罩制造

311.745:光罩

312.750:制造商

313.752:晶圆制造

314.753:半导体晶圆

315.760:半导体元件

316.a:对称轴

317.cm0:切割布局图案

318.c-c’:线

319.d-d’:线

320.d1:无鳍片区域

321.d1a:无鳍片区域

322.d2:无鳍片区域

323.d2a:无鳍片区域

324.fin:鳍片布局图案

325.m0:金属线布局图案

326.md:源极/漏极接触布局图案

327.net_1:网络

328.net_2:网络

329.po:多晶硅布局图案

330.r:凹陷区域

331.s11:鳍片至鳍片间距

332.s11a:鳍片至鳍片间距

333.s12:鳍片至鳍片间距

334.s12a:鳍片至鳍片间距

335.s13:栅极至栅极间距

336.s13a:栅极至栅极间距

337.s14:线至线间距

338.s14a:线至线间距

339.s15:线至线间距

340.s15a:线至线间距

341.s16:线至线间距

342.s16a:线至线间距

343.s21:鳍片至鳍片间距

344.s21a:鳍片至鳍片间距

345.s22:鳍片至鳍片间距

346.s22a:鳍片至鳍片间距

347.s23:栅极至栅极间距

348.s23a:栅极至栅极间距

349.s24:线至线间距

350.s24a:线至线间距

351.s25:线至线间距

352.s25a:线至线间距

353.s26:线至线间距

354.s26a:线至线间距

355.vg:栅极接触布局图案

356.w11:鳍片宽度

357.w12:鳍片宽度

358.w13:线宽

359.w13a:线宽

360.w14:线宽

361.w14a:线宽

362.w15:线宽

363.w15a:线宽

364.w21:鳍片宽度

365.w22:鳍片宽度

366.w23:线宽

367.w23a:线宽

368.w24:线宽

369.w24a:线宽

370.w25:线宽

371.w25a:线宽

372.x:方向

373.y:方向

具体实施方式

374.以下公开提供了用于实现所提供的主题的不同特征的许多不同的实施例或示例。以下描述元件和配置的特定示例以简化。当然,这些仅是示例,并不旨在进行限制。例如,在下面的描述中,在第二特征之上或上方形成第一特征可以包括其中第一特征和第二特征以直接接触形成的实施例,并且还可以包括在第一特征和第二特征之间形成附加特征,使得第一特征和第二特征可以不直接接触的实施例。另外,可以在各个示例中重复参考数字及/或文字。此重复是出于简单和清楚的目的,并且其本身并不指示所讨论的各种实施例及/或配置之间的关系。

375.更甚者,空间相对的词汇(例如,“低于”、“下方”、“之下”、“上方”、“之上”等相关词汇)于此用以简单描述如图所示的元件或特征与另一元件或特征的关系。在使用或操作时,除了图中所绘示的转向之外,这些空间相对的词汇涵盖装置的不同的转向。再者,这些装置可旋转(旋转90度或其他角度),且在此使用的空间相对的描述语可作对应的解读。

376.场效应晶体管(field effect transistor,fet)是集成电路的元件。场效应晶体管包括通道区域以及由通道区域间隔开的源极区域和漏极区域(统称为源极/漏极区域)。栅极在通道区域上方。透过向栅极施加电压,通道区域的电导率增加以允许电流从源极区域流到漏极区域。场效应晶体管利用导电的栅极接触电连接到栅极,以将栅极电压施加到场效应晶体管,并且源极/漏极接触电连接到源极/漏极区域以将电流传导到场效应晶体管或从场效应晶体管传导电流。栅极接触从位于栅极接触上方的下一层上的导线(在中可互换地称为“m0”线)接收栅极电压。一些集成电路包括多组半导体鳍片,且每组半导体鳍片可包括例如分享共同的源极/漏极接触并且被例如两个栅极结构跨越的三个鳍片。如果将落在这两个栅极结构上的两个栅极接触设计为电连接到不同的网络(nets),则可以利用鳍片组之间的两条m0线分别连接到两个栅极接触。然而,在相邻鳍片组之间放置两条m0线可能会减少其中一个鳍片组中的鳍片数,以便为m0线留出足够的空间。亦或是,如果两个栅极接触设计为使用同一条m0线电连接到不同的网络,则需要使用额外的微影和蚀刻步骤以将m0线分成用于不同网络的不同的部分。然而,额外的微影和蚀刻步骤将增加制造成本。

377.在的部分实施例中,在半导体元件的布局设计中移动m0线,使得m0线相对于相邻的鳍片组布局图案以不对称的方式配置,其中相邻的鳍片组布局图案中的每一个均包括多个鳍片(例如,三个鳍片)。m0线的不对称配置允许在相邻的鳍片组布局图案之间配置多条m0线(例如,两条m0线)而不会与鳍片组布局图案重叠。以此方式,m0线允许多个栅极接触(例如,两个栅极接触)电连接到不同的网络,而无须减少鳍片数量或额外的微影和蚀刻步骤(这将在下面更详细地描述)。

378.图1a是根据部分实施例的半导体元件的布局100的布局图。布局100可用于制造如图1b至图1d所示的半导体元件100a。

379.参照图1a,布局100包括第一鳍片组布局图案110和第二鳍片组布局图案120。第一鳍片组布局图案110和第二鳍片组布局图案120定义了半导体元件100a的相应的第一鳍片组区域110a和第二鳍片组区域120b(图1b至图1d)。第一鳍片组布局图案110和第二鳍片组布局图案120沿着布局100的第一方向(例如,x方向)延伸,并且沿着布局100的第二方向(例如,y方向)彼此间隔开。在部分实施例中,第二方向y垂直于第一方向x。

380.第一鳍片组布局图案110包括沿着x方向延伸并且沿着y方向彼此间隔开的三个第一鳍片布局图案112。每个第一鳍片布局图案112在y方向上与相邻的第一鳍片布局图案112间隔开第一鳍片至鳍片间距(fin-to-fin spacing)s11,并且每个第一鳍片布局图案112具有在y方向上测量的第一鳍片宽度w11。类似地,第二鳍片组布局图案120包括沿着x方向延伸并且沿着y方向彼此间隔开的三个第二鳍片布局图案122。每个第二鳍片布局图案122在y方向上与相邻的第二鳍片布局图案122间隔开第二鳍片至鳍片间距s12,并且每个第二鳍片布局图案122具有在y方向上测量的第二鳍片宽度w12。第一鳍片组布局图案110透过无鳍片区域d1在y方向上与第二鳍片组布局图案120分开,此无鳍片区域d1大于第一鳍片至鳍片间距s11和第二鳍片至鳍片间距s12。在部分实施例中,第一鳍片布局图案112的第一鳍片至鳍片间距s11与第二鳍片布局图案122的第二鳍片至鳍片间距s12相同。在部分实施例中,第一鳍片至鳍片间距s11不同于第二鳍片至鳍片间距s12。在部分实施例中,第一鳍片布局图案112的第一鳍片宽度w11与第二鳍片布局图案122的第二鳍片宽度w12相同。在一些其他实施例中,第一鳍片宽度w11与第二鳍片宽度w12不同。第一鳍片布局图案112和第二鳍片布局图案122定义了半导体元件100a的对应的第一鳍片112a和第二鳍片122a(图1b至图1d)。鳍片布局图案112和122在附图中标示为“fin”。

381.第一鳍片布局图案112中的每个均包括第一源极区域布局图案和第一漏极区域布局图案(统称为第一源极/漏极区域布局图案114),其定义了半导体元件100a的相应的第一源极/漏极区域114a(图1b至图1d)。类似地,第二鳍片布局图案122中的每个均包括第二源极区域布局图案和第二漏极区域布局图案(统称为第二源极/漏极区域布局图案124),其定义了半导体元件100a的相应的第二源极/漏极区域124a(图1b至图1d)。

382.鳍片布局图案112和122透过隔离结构布局图案104在同一布局层上彼此分离并与布局100的其他元件分离。隔离结构布局图案104定义了半导体元件100a的相应的隔离结构104a(图1b至图1d)。

383.布局100还包括在第一鳍片组布局图案110和120上方的多个栅极布局图案131、132、133和134。栅极布局图案131至134定义了半导体元件100a的对应的栅极结构131a、132a、133a和134a(图1b至图1d)。每个栅极布局图案131至134沿y方向延伸跨越鳍片组布局图案110和120。每个栅极布局图案131至134在x方向上与相邻的栅极布局图案131至134的一间隔开栅极至栅极间距s13。在所描绘的实施例中,栅极至栅极间距s13大于鳍片至鳍片间距s11和s12。栅极布局图案131至134和在栅极布局图案131至134的相对侧上的对应的源极/漏极区域布局图案114形成多个场效应晶体管。在部分实施例中,栅极布局图案131至134也被称为多晶硅(poly)布局图案,并且在附图中标示为“po”。

384.布局100包括覆盖在第一源极/漏极区域布局图案114上的多个第一源极/漏极接触布局图案142,以提供与第一源极/漏极区域布局图案114的电连接。此外,第一源极/漏极接触布局图案142沿着y方向延伸跨越三个第一鳍片布局图案112的第一源极/漏极区域布

局图案114,因此,三个第一鳍片布局图案112共享公共的源极/漏极接触布局图案142。类似地,布局100还包括覆盖第二源极/漏极区域布局图案124的多个第二源极/漏极接触布局图案144,以提供与第二源极/漏极区域布局图案124的电连接。此外,第二源极/漏极接触布局图案144沿着y方向延伸跨越在三个第二鳍片布局图案122的第二源极/漏极区域布局图案124,因此三个第二鳍片布局图案122共享公共的源极/漏极接触布局图案144。

385.源极/漏极接触布局图案142和144定义了半导体元件100a的对应的源极/漏极接触142a和144a(图1b至图1d)。源极/漏极接触布局图案142和144中的每一个均在第二方向y上延伸并且在对应的一对相邻的栅极布局图案131至134之间。源极/漏极接触布局图案142和144在附图中标示为“md”。

386.布局100还包括多个金属线布局图案161、162、163、164、165、166和167,其沿着x方向延伸并且沿着y方向彼此间隔开。金属线布局图案161至167定义了半导体元件100a的对应的金属线161a至167a(图1b至图1d)。金属线布局图案161至167在附图中标示为“m0”。

387.布局100的上边界处的金属线布局图案161是vdd线布局图案,布局100的下边界处的金属线布局图案167是vss线布局图案。金属线布局图案162至166配置在vdd线布局图案161和vss线布局图案167之间。每个金属线布局图案162至166在y方向与相邻的金属线布局图案162至166间隔开线至线间距(line-to-line spacing)s14,并且每个金属线布局图案162至166具有在y方向上量测的线宽w13。在部分实施例中,金属线布局图案162至166的线宽大于第一鳍片布局图案112和第二鳍片布局图案122的鳍片宽度w11和w12。

388.金属线布局图案162至166被移位,因此相对于鳍片组布局图案110和120以非对称的方式配置。更详细地,第一鳍片组布局图案110和第二鳍片组布局图案120对称于在x方向上延伸的对称轴a,但是金属线布局图案162至166对于鳍片组布局图案110和120的对称轴a不对称。金属线布局图案162至166的不对称配置允许金属线布局图案163和164配置在鳍片组布局图案110和120之间,而不与鳍片布局图案112和122中的任何一个重叠。

389.vdd线布局图案161在y方向上具有vdd线宽w14,并且vss线布局图案167在y方向上具有vss线宽w15。在图1a所描绘的实施例中,vdd线宽w14大于vss线宽w15,这将允许金属线布局图案162至166向第二鳍片组布局图案120偏移,同时保持vdd线布局图案161和相邻的金属线布局图案162之间的线至线间距s15与vss线布局图案167和相邻的金属线布局图案166之间的线至线间距s16相同。在实施例中,vdd线宽w14与vss线宽w15之比在大约101.5%至大约111.5%的范围内。如果vdd线宽w14与vss线宽w15之比过度地超过上限,则p型场效应晶体管的电流将过度地高于n型场效应晶体管。如果vdd线宽w14与vss线宽w15之比过度地低于下限,则金属线布局图案162至166的不对称配置可能不允许金属线布局图案163和164配置在鳍片组布局图案110和120之间而不与鳍片布局图案112和122中的任何一个重叠。

390.在部分实施例中,因为金属线布局图案162至166朝向第二鳍片组布局图案120偏移,所以更多的金属线布局图案与第二鳍片组布局图案120重叠,并且更少的金属线布局图案与第一鳍片组布局图案110重叠。作为示例而非限制,金属线布局图案162至166中的两个(例如,金属线布局图案165和166)与第二鳍片组布局图案120重叠,而金属线布局图案162至166中的一个(例如,金属线布局图案162)与第一鳍片组布局图案110重叠。此外,vdd线宽w14大于vss线宽w15,因此,vdd线布局图案161和源极/漏极接触布局图案142之间的重叠区

域大于vss线布局图案167和源极/漏极接触布局图案144之间的重叠区域。类似地,vdd线布局图案161和第一鳍片布局图案112之间的重叠区域大于vss线布局图案167和第二鳍片布局图案122之间的重叠区域。作为示例而非限制,vdd线布局图案161与第一鳍片布局图案112中的最上一个的整个部分重叠,并且vss线布局图案167仅与第二鳍片布局图案122中的最下一个的部分区域重叠。

391.线至线间距s14与线宽w13的两倍的总和小于第一鳍片组布局图案110和第二鳍片组布局图案120之间的无鳍片区域d1的宽度(即,第一鳍片布局图案112中的最下一个和第二鳍片布局图案122中的最上一个的距离)。这将允许金属线布局图案163和164不与第一鳍片组布局图案110和第二鳍片组布局图案120重叠。在部分实施例中,金属线布局图案162至166的线至线间距s14等同于vdd线布局图案161与相邻的金属线布局图案162之间的线至线间距s15,以及vss线布局图案167与相邻的金属线布局图案166之间的线至线间距s16。在部分实施例中,金属线布局图案162至166的线至线间距s14小于金属线布局图案162至166的线宽w13,这将允许金属线布局图案162至166的紧密配置。

392.布局100还包括覆盖在栅极布局图案133上的栅极接触布局图案171和覆盖在栅极布局图案132上的栅极接触布局图案172。栅极接触布局图案171和172定义了半导体元件100a的对应的栅极接触171a和172a(图1b至图1d)。栅极接触布局图案171与栅极布局图案133和金属线布局图案163的相交处重叠,从而提供了栅极布局图案133和金属线布局图案163之间的电连接。栅极接触布局图案172与栅极布局图案132和金属线布局图案164的相交处重叠,从而在栅极布局图案132和金属线布局图案164之间提供电连接。透过这种方式,栅极结构132a和133a电连接到不同的金属线164a和163a(图1b至图1d),其将允许栅极结构132a和133a电连接到不同的网络。每个网络是在共同形成电路的半导体元件的节点或端子之间的单独导电路径。例如,网络是超大型集成电路(very large scale integration,vlsi)的一个或多个微影级上的一个或多个金属化图案(例如,栅极接触以及在栅极接触上方的金属线和导孔)的单独的导电部分。在部分实施例中,在附图中使用标示“vg”代表栅极接触布局图案171和172。

393.布局100还包括两个切割布局图案150,其沿着y方向延伸跨越金属线布局图案162至166。切割布局图案150代表依据集成电路设计为了断开电连接而去除金属线布局图案162至166的切割部分或图案化区域。切割布局图案150沿y方向延伸,因此,切割布局图案150和栅极布局图案131至134彼此平行。此外,切割布局图案150可以在布局100的相对侧处与栅极布局图案131和134重叠。在部分实施例中,切割布局图案150用于指示m0线的切割部分并且在附图中标识为“cm0”。

394.图1b至图1d是根据部分实施例的使用布局100制造的半导体元件100a的视图,因此,如下面更详细描述的,半导体元件100a继承了布局100中那些图案的几何形状。图1b是半导体元件100a的上视图。图1c是沿图1b的半导体元件100a的线c-c’截取的剖面图。图1d是沿图1b的半导体元件100a的线d-d’截取的剖面图。半导体元件100a是用于帮助本揭露的说明的非限制性示例。

395.参照图1b至图1d,半导体元件100a包括基板102a,其中半导体元件100a的各种元件形成在基板102a上。基板102a包括但不限于块状硅基板、绝缘体上硅(silicon-on-insulator,soi)基板或硅锗基板。其他包括iii族、iv族和v族元素的半导体材料皆在的范

围内。

396.半导体元件100a还包括从基板102a向上延伸的第一鳍片组110a和第二鳍片组120a,以及沿着y方向延伸跨越鳍片组110a和120a的栅极结构131a、132a、133a和134a。第一鳍片组110a包括以第一鳍片至鳍片间距s11a配置的三个第一鳍片112a,而第二鳍片组120a包括以第二鳍片至鳍片间距s12a配置的三个第二鳍片122a。在部分实施例中,第一鳍片至鳍片间距s11a与布局100中的第一鳍片布局图案112的第一鳍片至鳍片间距s11相当,并且第二鳍片至鳍片间距s12a与布局100中的第二鳍片布局图案122的第二鳍片至鳍片间距s12相当。在部分实施例中,即使在布局100中已经将第一鳍片至鳍片间距s11和第二鳍片至鳍片间距s12设置为相同(如图1a所示),然而,由于用于制造鳍片112a和122a的微影和蚀刻技术的天性,第一鳍片至鳍片间距s11a可能与第二鳍片至鳍片间距s12a稍有不同。

397.第一鳍片112a和第二鳍片122a可以透过使用微影和蚀刻技术来对半导体基板102a进行图案化而形成,因此,所得的鳍片112a和122a也由半导体材料形成。因此,在中,这些鳍片可以被互换地称为半导体鳍片。例如,间距图像转移(spacer image transfer,sit)图案化技术可用于半导体鳍片。在此方法中,使用合适的微影和蚀刻制程在基板102a上形成牺牲层并对其进行图案化以形成心轴。使用自对准制程在心轴旁边形成间隔物。然后透过适当的选择性蚀刻制程去除牺牲层。接着,每个剩余的间隔物可以作为硬遮罩,以透过使用例如反应性离子蚀刻(reactive ion etching,rie)将沟槽蚀刻到基板102a中来图案化各个鳍片112a和122a。

398.鳍片112a和122a透过隔离结构104a彼此电隔离。在部分实施例中,隔离结构104a是浅沟槽隔离(shallow trench isolation,sti)结构,其包括填充有一种或多种介电材料的沟槽。在部分实施例中,浅沟槽隔离结构包括二氧化硅、氮化硅、氮氧化硅或任何其他合适的绝缘材料。

399.浅沟槽隔离结构104a可以透过沉积一种或多种介电材料(例如,氧化硅)以完全地填充鳍片112a和122a周围的沟槽,然后使介电材料的顶表面凹陷至鳍片112a和122a最上端之下而形成。浅沟槽隔离结构104a的介电材料的沉积可以使用高密度电浆化学气相沉积(high density plasma chemical vapor deposition,hdp-cvd)、低压化学气相沉积(low-pressure chemical vapor deposition,lpcvd)、次大气压化学气相沉积(sub-atmospheric chemical vapor deposition,sacvd)、可流动化学气相沉积(flowable chemical vapor deposition,fcvd)、自旋及/或类似物或其组合。在沉积之后,可以执行退火制程或固化制程。在一些情况下,浅沟槽隔离结构104a可以包括衬垫(例如,透过氧化硅表面而生长的热氧化物衬垫)。凹陷制程可以使用例如平坦化制程(例如,化学机械平坦化(chemical mechanical polish,cmp)),随后是选择性蚀刻制程(例如,湿式蚀刻或干式蚀刻或其组合),以使浅沟槽隔离结构104a中的介电材料的顶表面凹陷,以使得第一鳍片112a和第二鳍片122a的上部从周围的绝缘浅沟槽隔离结构104a中突出。在一些情况下,还可以透过平坦化制程来去除用于形成第一鳍片112a和第二鳍片122a的图案化的硬遮罩。

400.第一鳍片112a和第二鳍片122a各自包括多个源极/漏极区域114a和124a。源极/漏极区域114a和124a是位于相应的栅极结构131a至134a的相对侧上的掺杂的半导体区域。在部分实施例中,源极/漏极区域114a和124a包括p型掺杂剂(例如,硼),以用于形成p型场效应晶体管。在其他实施例中,源极/漏极区域114a和124a包括n型掺杂剂(例如,磷),以用于

dielectric)材料和高介电常数介电质材料的堆叠。在部分实施例中,界面介电材料包括二氧化硅。在栅极介电质上方形成栅极金属。示例性栅极金属包括例如,铜(cu)、铝(al)、钛(ti)、氮化钛(tin)、钽(ta)、氮化钽(tan)、碳化钽(tac)、钽氮化硅(tasin)、钨(w)、氮化钨(wn)或氮化钼(mon)。

404.半导体元件100a进一步包括第一源极/漏极接触142a和第二源极/漏极接触144a,其中每个第一源极/漏极接触142a均延伸跨越三个第一鳍片112a的第一源极/漏极区域114a,而每个第二源极/漏极接触144a均延伸跨越三个第二鳍片122a的第二源极/漏极区域124a。在部分实施例中,源极/漏极接触132a包括导电材料(例如,钴(co)、铜(cu)、钨(w)或其他合适的金属)。源极/漏极接触142a和144a的形成包括例如在形成高介电常数金属栅极结构131a至134a之后,在鳍片112a、122a上方的第一层间介电质(interlayer dielectric,ild)层(未示出)中蚀刻源极/漏极接触开口,在源极/漏极接触开口中沉积一种或多种导电材料,并执行化学机械平坦化制程以使一种或多种导电材料与栅极结构131a至134a齐平。

405.半导体元件100a还包括分别在对应的栅极结构133a和132a之上的栅极接触171a和172a。在部分实施例中,栅极接触171a和172a包括导电材料(例如,钴、铜、钨或其他合适的金属)。栅极接触171a和172a的形成包括例如在栅极结构131a至134a上方的第二层间介电质层(其在形成源极/漏极接触142a和144a之后沉积在第一层间介电质层上)中蚀刻栅极接触开口,在栅极接触开口中沉积一种或多种导电材料,并透过使用例如化学机械平坦化制程来平坦化一种或多种导电材料。

406.半导体元件100a进一步包括多条金属线161a、162a、163a、164a、165a、166a和167a,其位于栅极接触171a和172a上方的下一层中。金属线161a至167a沿着与y方向垂直的x方向延伸,其中栅极结构131a至134a以及源极/漏极接触142a和144a沿着此y方向延伸。图1b所示的最上面的金属线161a是vdd线,而图1b所示的最下面的金属线167a是vss线。vdd线161a电连接至vdd电压(例如,正电压),并且vss线167a电连接至vss电压(例如,接地或负电压)。金属线162a至166a配置在vdd线161a和vss线167a之间,并且可以连接到与vdd线161a和vss线167a不同的电压。

407.在部分实施例中,金属线161a至167a包括导电材料(例如,钴、铜、钨或其他合适的金属)。金属线161a至167a的形成包括例如在栅极接触171a和172a上方的第三层间介电质层(其形成在未绘示的第二层间介电质层上方)中蚀刻沟槽,沉积一个或多个导电材料于此沟槽中并执行化学机械平坦化制程以平坦化一种或多种导电材料。随后,使用布局100中的切割布局图案150来图案化金属线162a至166a。例如,首先在半导体元件100a上涂覆光阻,然后使用布局100中的切割布局图案150来图案化光阻,之后,透过使用图案化的光阻作为蚀刻遮罩的蚀刻制程来图案化金属线162a至166a。作为蚀刻过程的结果,金属线162至166a中的每一个被分成不连续的金属线(如图1b所示)。

408.每个金属线162a至166a在y方向上与相邻的金属线162a至166a间隔开线至线间距s14a,并且每个金属线162a至166a均具有在y方向上测量的线宽w13a。线至线间距s14a与布局100中的金属线布局图案162至166的线至线间距s14相当,并且线宽w13a与布局100中的金属线布局图案162至166的线宽w13相当。在部分实施例中,由于用于制造金属线162a至166a的微影和蚀刻技术的天性,线至线间距s14a可能彼此略有不同,并且线宽w13a也可以彼此稍有不同。

409.金属线162a至166a被移位并且因此相对于鳍片组110a和120a以不对称的方式配置。更详细地,第一鳍片组110a和第二鳍片组120a对于在x方向上延伸的对称轴a对称,但是金属线162a至166a对于鳍片组110a和120a的对称轴a不对称。金属线162a至166a的不对称配置允许金属线163a和164a配置在鳍片组110a和120a之间并且不与鳍片112a和122a重叠。

410.vdd线161a在y方向上具有vdd线宽w14a,而vss线167a在y方向上具有vss线宽w15a。vdd线宽w14a与布局100中的vdd线宽w14相当,并且vss线宽w15a与布局100中的vss线宽w15相当。在图1b所示的实施例中,vdd线宽w14a大于vss线宽w15a,这将允许金属线162a至166a向第二鳍片组120偏移,同时保持在vdd线161a和相邻的金属线162a之间的线至线间距s15a与在vss线167a和相邻的金属线166a之间的线至线间距s16a相当。在部分实施例中,由于用于制造金属线161a至167a的微影和蚀刻制程的天性,线至线间距s15a可能与线至线间距s16a稍微不同。在部分实施例中,vdd线宽w14a与vss线宽w15a之比在从大约101.5%到大约111.5%的范围内。如果vdd线宽w14a与vss线宽w15a之比过度地超过上限,则p型场效应晶体管的电流将过度地高于n型场效应晶体管的电流。如果vdd线宽w14a与vss线宽w15a之比过度地低于下限,则金属线的不对称配置可能不允许金属线163a和134a配置在鳍片组110和120之间而不重叠鳍片112a和122a中的任何一个。

411.线至线间距s14a和线宽w13a的两倍的总和小于第一鳍片组110a和第二鳍片组120a之间的无鳍片区域d1a的宽度(即,第一鳍片110a中的最下一个鳍片和第二鳍片120a中的最上一个鳍片之间的距离)。这将允许金属线163a和164a不与第一鳍片组110a和第二鳍片组120a重叠。

412.图2a是根据一些其他实施例的半导体元件的布局200的示意图。布局200可用于制造如图2b至图2c所示的半导体元件200a。布局200与布局100实质上相同,除了vss线宽大于vdd线宽之外(其将在下面更详细地描述)。在以下实施例中可以采用与图1a至图1d所描述的相同或相似的配置,并且可以省略其详细说明。

413.参考图2a,布局200包括第一鳍片组布局图案210和第二鳍片组布局图案220。第一鳍片组布局图案210和第二鳍片组布局图案220定义了半导体元件200a的相应的第一鳍片组210a和第二鳍片组220b(图2b至图2c)。第一鳍片组布局图案210包括沿着x方向延伸并且沿着y方向彼此间隔开的三个第一鳍片布局图案212。每个第一鳍片布局图案212在y方向上与相邻的第一鳍片布局图案212间隔开第一鳍片至鳍片间距s21,并且每个第一鳍片布局图案212具有在y方向上测量的第一鳍片宽度w21。类似地,第二鳍片组布局图案220包括沿着x方向延伸并且沿着y方向彼此间隔开的三个第二鳍片布局图案222。每个第二鳍片布局图案222在y方向上与相邻的第二鳍片布局图案222间隔开第二鳍片至鳍片间距s22,并且每个第二鳍片布局图案222具有在y方向上测量的第二鳍片宽度w22。第一鳍片组布局图案210在y方向上透过无鳍片区域d2与第二鳍片组布局图案220间隔开,此无鳍片区域d2宽度大于第一鳍片至鳍片间距s21和第二鳍片至鳍片间距s22。第一鳍片布局图案212的第一鳍片至鳍片间距s21可以与第二鳍片布局图案222的第二鳍片至鳍片间距s22相同或不同。第一鳍片布局图案212的第一鳍片宽度w21与第二鳍片布局图案222的第二鳍片宽度w22相同或不同。第一鳍片布局图案212和第二鳍片布局图案222定义了半导体元件200a的对应的第一鳍片212a和第二鳍片222a(图2b至图2c)。

414.每个第一鳍片布局图案212均包括第一源极/漏极区域布局图案214,其定义了半

导体元件200a的对应的第一源极/漏极区域214a(图2b至图2c)。类似地,每个第二鳍片布局图案222均包括第二源极/漏极区域布局图案224,其定义了半导体元件200a的对应的第二源极/漏极区域224a(图2b至图2c)。鳍片布局图案212和222透过隔离结构布局图案204彼此分离并与在同一布局层上的布局200的其他元件分离。隔离结构布局图案204定义了半导体元件200a的对应的隔离结构204a(图2b至图2c)。

415.布局200还包括沿着y方向延伸跨越鳍片组布局图案210和220的多个栅极布局图案231、232、233和234。栅极布局图案231至234定义半导体元件200a的相应的栅极结构231a、232a、233a和234a(图2b至图2c)。每个栅极布局图案231至234与相邻的栅极布局图案231至234在x方向上间隔开栅极至栅极间距s23。栅极至栅极间距s23大于鳍片至鳍片间距s21和s22。栅极布局图案231至234和在栅极布局图案231至234的相对侧上的对应的源极/漏极区域布局图案214和224形成多个场效应晶体管。

416.布局200包括多个第一源极/漏极接触布局图案242,其沿着y方向延伸跨越三个第一鳍片布局图案212的第一源极/漏极区域布局图案214,因此,三个第一鳍片布局图案212共享公共的源极/漏极接触布局图案242。类似地,布局200还包括多个第二源极/漏极接触布局图案244,其沿y方向延伸跨越三个第二鳍片布局图案222的第二源极/漏极区域布局图案224,因此,三个第二鳍片布局图案222共享公共的源极/漏极接触布局图案244。源极/漏极接触布局图案242和244定义了半导体元件200a的对应的源极/漏极接触242a和244a(图2b至图2c)。

417.布局200还包括多个金属线布局图案261、262、263、264、265、266和267,其沿着x方向延伸并且沿着y方向彼此间隔开。金属线布局图案261至267定义了半导体元件200a的对应的金属线261a至267a(图2b至图2c)。

418.在布局200的上边界处的金属线布局图案261是vdd线布局图案,并且在布局200的下边界处的金属线布局图案267是vss线布局图案。金属线布局图案262至266配置在vdd线布局图案261和vss线布局图案267之间。每个金属线布局图案262至266在y方向上与相邻的金属线布局图案262至266间隔开线至线间距s24,并且每个金属线布局图案262至266具有在y方向上测量的线宽w23。在部分实施例中,金属线布局图案262至266的线宽w23大于第一鳍片布局图案212和第二鳍片布局图案222的鳍片宽度w21和w22。

419.金属线布局图案262至266被移位并且因此相对于鳍片组布局图案210和220以不对称的方式配置。更详细地,第一鳍片组布局图案210和第二鳍片组布局图案220对于在x方向上延伸的对称轴a对称,而金属线布局图案262至266对于鳍片组布局图案210和220的对称轴a不对称。金属线布局图案262至266的不对称配置允许金属线布局图案264和265配置在鳍片组布局图案210和220之间,而不与鳍片布局图案212和222中的任何一个重叠。

420.vdd线布局图案261在y方向上具有vdd线宽w24,而vss线布局图案267在y方向上具有vss线宽w25。在图2a中所描绘的实施例中,vss线宽w25大于vdd线宽w24,这将允许金属线布局图案262至266朝着第一鳍片组布局图案210移动,同时保持在vdd线布局图案261与相邻的金属线布局图案262之间的线至线间距s25与在vss线布局图案267与相邻的金属线布局图案266之间的线至线间距s26相同。在部分实施例中,vss线宽w25与vdd线宽w24之比在大约101.5%至大约111.5%的范围内。如果vss线宽w25与vdd线宽w24之比过度地超过上限,则n型场效应晶体管的电流将过度地高于p型场效应晶体管。如果vss线宽w25与vdd线宽

w24之比过度地低于下限,则金属线布局图案262至266的不对称配置可能不允许金属线布局图案264和265配置在鳍片组布局图案210和220之间而不与鳍片布局图案212和222中的任何一个重叠。

421.在部分实施例中,因为vdd线宽w24小于vss线宽w25,所以vdd线布局图案261与源极/漏极接触布局图案242之间的重叠区域小于vss线布局图案267和源极/漏极接触布局图案244之间的重叠区域。类似地,vdd线布局图案261和第一鳍片布局图案212之间的重叠区域小于vss线布局图案267和第二鳍片布局图案222之间的重叠区域。作为示例而非限制,vss线布局图案267与第二鳍片布局图案222中的最下一个的全部重叠,并且vdd线布局图案261仅与第一鳍片布局图案212中的最上一个的一部分重叠。

422.线至线间距s24与线宽w23的两倍的和小于第一鳍片组布局图案210和第二鳍片组布局图案220之间的无鳍片区域d2的宽度(即,第一鳍片布局图案212中的最下一个和第二鳍片布局图案222中的最上一个之间的距离)。这将允许金属线布局图案264和165不与第一鳍片组布局图案210和第二鳍片组布局图案220重叠。在部分实施例中,金属线布局图案262至266的线至线间距s24等同于vdd线布局图案261与相邻的金属线布局图案262之间的线至线间距s25,并且等同于vss线布局图案267与相邻的金属线布局图案266之间的线至线间距s26。在部分实施例中,金属线布局图案262至266的线至线间距s24小于金属线布局图案262至266的线宽w23,这将允许金属线布局图案262至266的紧密配置。

423.布局200还包括分别覆盖在对应的栅极布局图案232和233上方的栅极接触布局图案271和272。栅极接触布局图案271和272定义了半导体元件200a的对应的栅极接触271a和272a(图2b至图2c)。栅极接触布局图案271与栅极布局图案232和金属线布局图案264的相交处重叠,从而提供了在栅极布局图案232和金属线布局图案264之间的电连接。栅极接触布局图案272与栅极布局图案233和金属线布局图案265的相交处重叠,从而在栅极布局图案233和金属线布局图案265之间提供电连接。如此,栅极结构232a和233a电连接到不同的金属线264a和265a(图2b至图2c),其将允许栅极结构232a和233a电连接到不同的网络。

424.布局200还包括两个切割布局图案250,其沿着y方向延伸跨越金属线布局图案262至266。切割布局图案250代表根据集成电路设计为了断开电连接而去除金属线布局图案262至266的切割部分或图案化区域。

425.图2b和图2c是根据部分实施例的使用布局200制造的半导体元件200a的视图,因此,半导体元件200a继承了布局200中的那些图案的几何形状(如下面更详细地描述的)。图2b是半导体元件200a的上视图。图2c是沿图2b中半导体元件200a的线c-c’截取的剖面图。半导体元件200a是用于帮助本揭露的说明的非限制性示例。

426.参考图2b和图2c,半导体元件200a包括基板202a,从基板202a向上延伸的第一鳍片组210a和第二鳍片组220a,以及沿y方向延伸跨越鳍片组210a和220a的栅极结构231a、232a、233a和234a。第一鳍片组210a包括以第一鳍片至鳍片间距s21a配置的三个第一鳍片212a,而第二鳍片组220a包括以第二鳍片至鳍片间距s22a配置的三个第二鳍片222a。在部分实施例中,第一鳍片至鳍片间距s21a与布局200中的第一鳍片布局图案212的第一鳍片至鳍片间距s21相当,并且第二鳍片至鳍片间距s22a与布局200中的第二鳍片布局图案222的第二鳍片至鳍片间距s22相当。在部分实施例中,由于用于制造鳍片212a和222a的微影和蚀刻技术的本质的因素,第一鳍片至鳍片间距s21a可能与第二鳍片至鳍片间距s22a稍微不

同。基板202a、鳍片212a、222a和栅极结构231a至234a的示例性材料和制造方法与图1b至图1d中所示的相似,因此为了简洁起见不再重复。

427.鳍片212a和222a透过隔离结构204a彼此电隔离。在部分实施例中,隔离结构204a是浅沟槽隔离结构,其包括填充有一种或多种介电材料的沟槽。浅沟槽隔离结构204a的示例性材料和制造方法与在图1b至图1d中所示的浅沟槽隔离结构104a的描述相似,因此为了简洁起见不再重复。

428.鳍片212a和222a包括多个源极/漏极区域214a和224a。源极/漏极区域214a和224a是位于相应栅极结构231a至234a的相对侧上的掺杂的半导体区域。在部分实施例中,源极/漏极区域214a和224a包括p型掺杂剂(例如,硼),以用于形成p型场效应晶体管。在其他实施例中,源极/漏极区域214a和224a包括n型掺杂剂(例如,磷),以用于形成n型场效应晶体管。源极/漏极区域214a和224a的示例性制造方法类似于在图1b至图1d中所示的源极/漏极区域114a和124a的描述,因此为了简洁起见不再重复。

429.栅极结构231a至234a沿着y方向延伸穿过第一鳍片212a和第二鳍片222a。栅极结构231a至234a以栅极至栅极间距s23a配置。栅极至栅极间距s23a大于鳍片至鳍片间距s21a和s22a。栅极至栅极间距s23a与布局200中栅极布局图案231至234的栅极至栅极间距s23相当。在部分实施例中,栅极结构231a至234a是高介电常数金属栅极结构,其可以使用后栅极制程流程形成(如先前关于图1b至图1d所示的栅极结构131a至134a所描述的)。因此,为了简洁起见,不再重复高介电常数金属栅极结构的示例性材料和制造方法。

430.半导体元件200a进一步包括第一源极/漏极接触242a和二源极/漏极接触244a,其中每个第一源极/漏极接触242a延伸跨越三个第一鳍片212a的第一源极/漏极区域214a,而每个第二源极/漏极接触244a延伸跨越三个第二鳍片222a的第二源极/漏极区域224a。半导体元件200a还分别在相应的栅极结构232a和233a上包括栅极接触271a和272a。源极/漏极接触242a、244a和栅极接触271a、272a的示例性材料和制造方法与在图1b至图1d中所示的源极/漏极接触142a、144a和栅极接触171a、172a的描述相似,因此为了简洁起见不再重复。

431.半导体元件200a进一步包括多个金属线261a、262a、263a、264a、265a、266a和267a,它们位于栅极接触271a和272a上方的下一层。金属线261a至267a沿着垂直于y方向的x方向延伸(其中栅极结构231a至234a以及源极/漏极接触242a和244a沿着此y方向延伸)。图2b所示的最上面的金属线261a是vdd线,而图2b所示的最下面的金属线267a是vss线。vdd线261a电连接至vdd电压(例如,正电压),并且vss线267a电连接至vss电压(例如,接地或负电压)。金属线262a至266a配置在vdd线261a和vss线267a之间,并且可以连接到与vdd线261a和vss线267a不同的电压。金属线261a至267a的示例性材料和制造方法与在图1b至图1d中所示的金属线161a至167a的描述相似,因此为了简洁起见不再重复。

432.每条金属线262a至266a在y方向上与相邻的金属线262a至266a隔开线至线间距s24a,并且每条金属线262a至266a具有在y方向上测量的线宽w23a。线至线间距s24a与布局200中的金属线布局图案262至266的线至线间距s24相当,线宽w23a与布局200中的金属线布局图案262至266的线宽w23相当。在部分实施例中,由于用于制造金属线262a至266a的微影和蚀刻技术的天性,线至线间距s24a可能略有不同,并且线宽w23a也可能略有不同。

433.金属线262a至266a被移位并且因此相对于鳍片组210a和220a以不对称的方式配置。更详细地,第一鳍片组210a和第二鳍片组220a与在x方向上延伸的对称轴a对称,而金属

线262a至266a与鳍片组210a和220a的对称轴a不对称。金属线262a至266a的不对称配置允许金属线264a和265a配置在鳍片组210a和220a之间而不与鳍片212a和222a重叠。

434.vdd线261a在y方向上具有vdd线宽w24a,而vss线267a在y方向上具有vss线宽w25a。vdd线宽w24a与布局200中的vdd线宽w24相当,并且vss线宽w25a与布局200中的vss线宽w25相当。在图2b所示的实施例中,vss线宽w25a大于vdd线宽w24a,这将允许金属线262a至266a向第一鳍片组210a移动,而保持在vdd线261a和相邻的金属线262a之间的线至线间距s25a与在vss线267a和相邻金属线266a之间的线至线间距s26a相当。在部分实施例中,由于用于制造金属线261a至267a的微影和蚀刻制程的天性,线至线间距s25a可以与线至线间距s26a稍有不同。在部分实施例中,vss线宽w25a与vdd线宽w24a之比在大约101.5%到大约111.5%的范围内。如果vss线宽w25a与vdd线宽w24a之比过度地超过上限,则n型场效应晶体管的电流将过度地高于p型场效应晶体管的电流。如果vss线宽w25a与vdd线宽w24a之比过度地低于下限,则配置在鳍片组210a和220a之间的金属线264a和265a的不对称配置可能会重叠鳍片212a和222a中的任何一个。

435.线至线间距s24a与线宽w23a的两倍的和小于第一鳍片组210a与第二鳍片组220a之间的无鳍片区域d2a的宽度(即,第一鳍片212a中的最下一个与第二鳍片222a中的最上一个之间的距离)。这将允许金属线264a和265a不与第一鳍片组110a和第二鳍片组120a重叠。

436.图3a是根据一些其他实施例的半导体元件的布局300的视图。布局300可用于制造如图3b至图3c所示的半导体元件300a。布局300绘示使用两条相邻的m0金属线形成不同的网络net_1和net_2。网络net_1和net_2是不同的网络,因此没有电连接。因此,网络net_1和net_2可以电连接到不同的电压。在以下实施例中可以采用如图1a至图1d所示的结构,并且可以省略其详细说明。

437.参照图3a,布局300包括第一鳍片组布局图案310和第二鳍片组布局图案320。第一鳍片组布局图案310和第二鳍片组布局图案320定义了半导体元件300a的相应的第一鳍片组区域310a和第二鳍片组区域320a(图3b至图3c)。第一鳍片组布局图案310包括沿着x方向延伸并且沿着y方向彼此间隔开的三个第一鳍片布局图案312,而第二鳍片组布局图案320包括沿着x方向延伸并且沿y方向彼此间隔开的三个第二鳍片布局图案322。

438.第一鳍片布局图案312中的每个均包括第一源极/漏极区域布局图案314,其定义半导体元件300a的对应的第一源极/漏极区域314a(图3b至图3c)。类似地,第二鳍片布局图案322中的每个均包括第二源极/漏极区域布局图案324,其定义了半导体元件300a的对应的第二源极/漏极区域324a(图3b至图3c)。鳍片布局图案312和322透过隔离结构布局图案304彼此间隔开并与在相同布局层上的布局300的其他元件分离。隔离结构布局图案304定义了半导体元件300a的相应的隔离结构304a(图3b至图3c)。

439.布局300还包括沿着y方向延伸跨越鳍片组布局图案310和320的多个栅极布局图案331、332、333、334、335、336、337和338。栅极布局图案331至338定义了半导体元件300a的对应的栅极结构331a、332a、333a、334a、335a、336a、337a和338a(图3b至图3c)。栅极布局图案331至338以及在栅极布局图案331至338的相对侧上的对应的源极/漏极区域布局图案314和324形成多个场效应晶体管。

440.布局300包括多个第一源极/漏极接触布局图案342,其沿y方向延伸跨越三个第一鳍片布局图案312的第一源极/漏极区域布局图案314,因此三个第一鳍片布局图案312共享

公共的源极/漏极接触布局图案342。类似地,布局300还包括多个第二源极/漏极接触布局图案344,其沿着y方向延伸跨越三个第二鳍片布局图案322的第二源极/漏极区域布局图案324,因此三个第二鳍片布局图案322共享公共的源极/漏极接触布局图案344。源极/漏极接触布局图案342和344定义了半导体元件300a的对应的源极/漏极接触342a和344a(图3b至图3c)。

441.布局300还包括多个金属线布局图案361、362、363、364、365、366和367,其沿着x方向延伸并且沿着y方向彼此间距隔开。金属线布局图案361至367定义了半导体元件300a的对应的金属线361a至367a(图3b至图3c)。在布局300的上边界处的金属线布局图案361是vdd线布局图案,而在布局300的下边界处的金属线布局图案367是vss线布局图案。金属线布局图案362至366配置在vdd线布局图案361和vss线布局图案367之间。

442.金属线布局图案361至367被移位并且因此相对于鳍片组布局图案310和320以不对称的方式配置。例如,vdd线布局图案361与一个第一鳍片布局图案312的整个部分重叠,然而vss线布局图案367仅与一个第二鳍片布局图案322的一部分(例如,此第二鳍片布局图案322的长侧)重叠。金属线布局图案361至367的不对称配置允许金属线布局图案363和364配置在鳍片组布局图案310和320之间,而不与鳍片布局图案312和322中的任何一个重叠。

443.布局300还包括分别覆盖在对应的栅极布局图案332、334、335和338上的栅极接触布局图案371、372、373和374。栅极接触布局图案371至374定义了半导体元件300a的对应的栅极接触371a、372a、373a和374a(图3b至图3c)。

444.栅极接触布局图案371与栅极布局图案332和金属线布局图案364的相交处重叠,从而在栅极布局图案332和金属线布局图案364之间提供电连接。栅极接触布局图案372与栅极布局图案334和金属线布局图案363的相交处重叠,从而在栅极布局图案334和金属线布局图案363之间提供电连接。栅极接触布局图案373与栅极布局图案335和金属线布局图案364的相交处重叠,从而在栅极布局图案335和金属线布局图案364之间提供电连接。栅极接触布局图案374与栅极布局图案338和金属线布局图案363的相交处重叠,从而在栅极布局图案338和金属线布局图案363之间提供电连接。金属线布局图案363和364彼此不电连接。以这种方式,可以透过使用金属线布局图案364将栅极布局图案332和335电连接到第一网络net_1,并且可以透过使用金属线布局图案363将栅极布局图案334和338电连接到不同于第一网络net_1的第二网net_2。因此,可以透过使用两条m0线来实现不同的网络net_1和net_2,这将节省绕线(routing)资源并提高绕线灵活性。

445.图3b和图3c是根据部分实施例使用布局300制造的半导体元件300a的视图,因此,半导体元件300a继承了布局300中那些图案的几何形状(如下面更详细地描述的)。图3b是半导体元件300a的上视图。图3c是图3b中半导体元件300a沿线c-c’截取的的剖面图。半导体元件300a是用于帮助本揭露的说明的非限制性示例。

446.参考图3b和图3c,半导体元件300a包括基板302a,从基板302a向上延伸的第一鳍片组310a和第二鳍片组320a,以及沿y方向延伸跨越鳍片组310a和320a的栅极结构331a、332a、333a、334a、335a、336a、337a和338a。第一鳍片组310a包括三个间隔开设置的第一鳍片312a,而第二鳍片组310a包括三个间隔开设置的第二鳍片322a。基板302a、鳍片312a、322a和栅极结构331a至334a的示例性材料和制造方法与图1b至图1d中所示的相似,因此为了简洁起见不再重复。

447.鳍片312a和322a透过隔离结构304a彼此电隔离。在部分实施例中,隔离结构304a是浅沟槽隔离结构,其包括填充有一种或多种介电材料的沟槽。浅沟槽隔离结构304a的示例性材料和制造方法类似于关于图1b至图1d中所示的浅沟槽隔离结构104a的描述,因此为了简洁起见不再重复。

448.鳍片312a和322a包括多个源极/漏极区域314a和324a。源极/漏极区域314a和324a是位于相应的栅极结构331a至338a的相对侧上的掺杂的半导体区域。在部分实施例中,源极/漏极区域314a和324a包括p型掺杂剂(例如,硼),以用于形成p型场效应晶体管。在其他实施例中,源极/漏极区域314a和324a包括n型掺杂剂(例如,磷),以用于形成n型场效应晶体管。源极/漏极区域314a和324a的示例性材料和制造方法类似于关于图1b至图1d中所示的关于源极/漏极区域114a和124a的描述,因此为了简洁起见不再重复。

449.栅极结构331a至338a沿着y方向延伸跨越第一鳍片312a和第二鳍片322a。在部分实施例中,栅极结构331a至338a可以是使用后栅极制程流程形成的高介电常数金属栅极结构(如先前关于图1b至图1d所示的栅极结构131a至134a所描述的)。

450.半导体元件300a进一步包括第一源极/漏极接触342a和第二源极/漏极接触344a,其中每个第一源极/漏极接触342a均延伸跨越三个第一鳍片312a的第一源极/漏极区域314a,而每个第二源极/漏极接触344a均延伸跨越三个第二鳍片322a的第二源极/漏极区域324a。半导体元件300a进一步包括分别在对应的栅极结构332a、334a、335a和338a之上的栅极接触371a、372a、373a和374a。源极/漏极接触342a、344a和栅极接触371a至374a的示例性材料和制造方法与图1b至图1d中关于源极/漏极接触143a、144a和栅极接触171a、173a的描述相似,因此为了简洁起见不再重复。

451.半导体元件300a进一步包括多条金属线361a、362a、363a、364a、365a、366a和367a,它们沿着x方向在栅极接触371a至374a上方的下一层上延伸。金属线363a和364a彼此不电连接,因此用于不同的网络。金属线364a与栅极接触371a和373a重叠,并且因此将栅极结构332a和335a电连接到第一网络net_1。金属线363a与栅极接触372a和374a重叠,并且因此将栅极结构334a和338a电连接到第二网络net_2。因此,透过使用两条m0线可以实现不同的网络,从而节省了绕线资源并提高了绕线灵活性。

452.图3b所示的最上面的金属线361a是vdd线,而图3b所示的最下面的金属线367a是vss线。vdd线361a电连接到vdd电压(例如,正电压),而vss线367a电连接到vss电压(例如,接地或负电压)。金属线362a至366a配置在vdd线361a和vss线367a之间,并且可以连接到与vdd线361a和vss线367a不同的电压。金属线361a至367a的示例性材料和制造方法与图1b至图1d中关于金属线161a至167a的描述相似,因此为了简洁起见不再重复。

453.金属线361a至367a被移位并且因此相对于鳍片组310a和320a以不对称的方式配置。例如,vdd线361a与一个第一鳍片312a的整个部分重叠,然而vss线367a仅与一个第二鳍片322a的一部分(例如,此第二鳍片布局图案322a的长侧)重叠。金属线361a至367a的不对称配置允许金属线363a和364a配置在鳍片组310a和320a之间而不与鳍片312a和322a重叠。

454.图4a是根据一些其他实施例的半导体元件的布局400的视图。布局400可用于制造如图4b至图4c所示的半导体元件400a。布局400类似于布局100,除了附加的源极/漏极导孔布局图案和不同的切割图案(如以下更详细地描述的)。在以下实施例中可以采用与图1a至图1d所示的相同或相似的配置,并且可以省略其详细说明。

455.参考图4a,布局400包括第一鳍片组布局图案410和第二鳍片组布局图案420。第一鳍片组布局图案410和第二鳍片组布局图案420定义了半导体元件400a的相应的第一鳍片组区域410a和第二鳍片组区域420a(图4b至图4c)。第一鳍片组布局图案410包括三个第一鳍片布局图案412,并且第二鳍片组布局图案420包括三个第二鳍片布局图案422。第一鳍片布局图案412中的每一个均包括第一源极/漏极区域布局图案414,其定义半导体元件400a的对应的第一源极/漏极区域414a(图4b至图4c)。类似地,第二鳍片布局图案422中的每一个均包括第二源极/漏极区域布局图案424,其定义了半导体元件400a的对应的第二源极/漏极区域424a(图4b至图4c)。在部分实施例中,鳍片布局图案412和422的鳍片宽度和鳍片至鳍片间距与图1a所示的鳍片布局图案112和122的鳍片宽度和鳍片至鳍片间距相同,因此,为了避免重复,不再赘述。鳍片布局图案412和422透过隔离结构布局图案404彼此分离并与在同一布局层上的布局400的其他元件间隔开。隔离结构布局图案404定义了半导体元件400a的对应的隔离结构404a(图4b至图4c)。

456.布局400还包括沿着y方向延伸跨越鳍片组布局图案410和440的多个栅极布局图案431、432、433和434。栅极布局图案431至434定义半导体元件400a的对应的栅极结构431a、432a、433a和434a(图4b至图4c)。栅极布局图案431至434以及在栅极布局图案431至434的相对侧上的对应的源极/漏极区域布局图案414和424形成多个场效应晶体管。在部分实施例中,栅极布局图案431至434的栅极至栅极间距与图1a所示的栅极布局图案131至134的栅极至栅极间距相同,因此为了简洁起见不重复。

457.布局400包括多个第一源极/漏极接触布局图案442,其沿着y方向延伸跨越三个第一鳍片布局图案412的第一源极/漏极区域布局图案414,因此,三个第一鳍片布局图案412共享共用的源极/漏极接触布局图案442。类似地,布局400还包括多个第二源极/漏极接触布局图案444,其沿着y方向延伸跨越三个第二鳍片布局图案422的第二源极/漏极区域布局图案424,因此,三个第二鳍片布局图案422共享公共的源极/漏极接触布局图案444。源极/漏极接触布局图案442和444定义了半导体元件400a的对应的源极/漏极接触442a和444a(图4b至图4c)。

458.布局400还包括多个金属线布局图案461、462、463、464、465、466和467,其沿着x方向延伸并且沿着y方向彼此间隔开。金属线布局图案461至467定义了半导体元件400a的对应的金属线461a至467a(图4b至图4c)。布局400的上边界处的金属线布局图案461是vdd线布局图案,并且布局400的下边界处的金属线布局图案467是vss线布局图案,其中vss线布局图案的宽度小于vdd线布局图案461的宽度。金属线布局图案462至466配置在vdd线布局图案461和vss线布局图案467之间。

459.金属线布局图案462至466被偏移并因此对于鳍片组布局图案410和420以非对称方式配置。例如,金属线布局图案462至466朝着第二鳍片组布局图案420偏移。金属线布局图案462至466的不对称配置允许金属线布局图案463和464配置在鳍片组布局图案410和420之间,而不与鳍片布局图案412和422中的任何一个重叠。在部分实施例中,金属线布局图案461至467的线宽、线至线间距和不对称配置与图1a所示的金属线布局图案161至167相同,因此不再重复为了简洁起见。

460.布局400还包括分别覆盖在对应的栅极布局图案433和432上的栅极接触布局图案471和472。栅极接触布局图案471和472定义了半导体元件400a的对应的栅极接触471a和

472a(图4b至图4c)。栅极接触布局图案471与栅极布局图案433和金属线布局图案463的相交处重叠,从而提供了栅极布局图案433和金属线布局图案463之间的电连接。栅极接触布局图案472与栅极布局图案432和金属线布局图案464的相交处重叠,从而在栅极布局图案432和金属线布局图案464之间提供电连接。透过这种方式,栅极结构432a和433a电连接到不同的金属线464a和463a(图4b至图4c),其将允许栅极结构432a和433a电连接到不同的网络。

461.布局400还包括沿y方向延伸跨越金属线布局图案466的两个切割布局图案450。切割布局图案450仅与金属线布局图案465的一部分重叠。换句话说,切割布局图案450延伸超过金属线布局图案465的下部长侧,并且从金属线布局图案465的上部长侧向后缩回。切割布局图案450代表根据集成电路设计去除金属线布局图案465和466的切割部分或图案化区域。

462.布局400还包括分别位于对应的源极/漏极接触布局图案444上方的源极/漏极导孔布局图案481、482和483。源极/漏极导孔布局图案481、482和483定义了半导体元件400a的对应的源极/漏极导孔481a、482a和483a(图4b至图4c)。源极/漏极导孔布局图案481与左侧的源极/漏极接触布局图案444和金属线布局图案466的相交处重叠,从而在其间提供电连接。源极/漏极导孔布局图案482与中间的源极/漏极接触布局图案444和金属线布局图案465的相交处重叠,从而在它们之间提供电连接。源极/漏极导孔布局图案483与右侧的源极/漏极接触布局图案444和金属线布局图案466的相交处重叠,从而在其间提供电连接。因此,布局400可以仅使用四个m0线布局图案(即,线图案463、464、465和466)来对栅极接触和源极/漏极导孔进行布线,这将节省布线资源并提高布线灵活性。

463.图4b和图4c是根据部分实施例的使用布局400制造的半导体元件400a的视图,因此,半导体元件400a继承了布局400中那些图案的几何形状(如下面更详细地描述的)。图4b是半导体元件400a的上视图。图4c是图4b中沿着线c-c’截取的的半导体元件400a的剖面图。半导体元件400a是用于帮助本揭露的说明的非限制性示例。

464.参考图4b和图4c,半导体元件400a包括基板402a,从基板402a向上延伸的第一鳍片组410a和第二鳍片组420a,以及沿y方向延伸跨越鳍片组410a和440a的栅极结构431a、434a、433a和434a。第一鳍片组410a包括沿着x方向延伸的三个第一鳍片412a,而第二鳍片组420a也包括沿着x方向延伸的三个第二鳍片422a。基板402a和鳍片412a、422a的示例性材料和制造方法与图1b至图1d中所示的相似,因此为了简洁起见不再重复。在部分实施例中,鳍片412a和422a的鳍片宽度和鳍片至鳍片间距与图1b所示的鳍片112a和122a的鳍片宽度和鳍片至鳍片间距相同,因此为简洁起见不再重复。

465.鳍片412a和422a透过隔离结构404a彼此电隔离。在部分实施例中,隔离结构404a是浅沟槽隔离结构,其包括填充有一种或多种介电材料的沟槽。浅沟槽隔离结构404a的示例性材料和制造方法类似于在图1b至图1d中所示的浅沟槽隔离结构104a的描述,因此为了简洁起见不再重复。

466.鳍片412a和422a包括多个源极/漏极区域414a和424a。源极/漏极区域414a和424a是位于相应的栅极结构431a至434a的相对侧上的掺杂的半导体区域。在部分实施例中,源极/漏极区域414a和424a包括p型掺杂剂(例如,硼),以用于形成p型场效应晶体管。在其他实施例中,源极/漏极区域414a和424a包括n型掺杂剂(例如,磷),以用于形成n型场效应晶

体管。源极/漏极区域414a和424a的示例性制造方法类似于在图1b至图1d中所示的关于源极/漏极区域114a和124a的描述,因此为了简洁起见不再重复。

467.栅极结构431a至434a沿着y方向延伸跨第一鳍片412a和第二鳍片422a。在部分实施例中,栅极结构431a至434a可以是使用后栅极制程流程形成的高介电常数金属栅极结构(如先前相对于图1b至图1d所示的栅极结构131a至134a所描述的)。因此,为了简洁起见,不再重复高介电常数金属栅极结构的示例性材料和制造方法。栅极结构431a至434a的栅极至栅极间距与栅极结构131a至134a的栅极至栅极间距相同,因此为了简洁起见不再重复。

468.半导体元件400a还包括第一源极/漏极接触442a和第二源极/漏极接触444a,其中每个第一源极/漏极接触442a均延伸跨越三个第一鳍片412a的第一源极/漏极区域414a,而每个第二源极/漏极接触444a均延伸跨越三个第二鳍片422a的第二源极/漏极区域424a。半导体元件400a还包括在栅极结构433a上方的栅极接触471a和在栅极结构432a上方的栅极接触472a。源极/漏极接触442a、444a和栅极接触471a、474a的示例性材料和制造方法与在图1b至图1d所示的源极/漏极接触142a、144a和栅极接触171a、172a的描述相似,因此为了简洁起见不再重复。

469.半导体元件400a还包括多条金属线461a、462a、463a、464a、465a、466a和467a,它们沿着x方向在栅极接触471a和474a上方的下一层上延伸。图4b所示的最上面的金属线461a是vdd线,而图4b所示的最下面的金属线467a是vss线。vdd线461a电连接至vdd电压(例如,正电压),而vss线467a电连接至vss电压(例如,接地或负电压)。金属线462a至466a配置在vdd线461a和vss线467a之间,并且可以连接到与vdd线461a和vss线467a不同的电压。金属线461a至467a的示例性材料和制造方法与在图1b至图1d中所示的金属线161a至167a的描述相似,因此为了简洁起见不再重复。金属线461a至467a的线宽、线至线间距和不对称的配置与前所述的金属线161a至167a的线宽、线至线间距和不对称配置相同,因此为了简洁起见不再重复。

470.在如图4b所示的实施例中,当从上方观察时,金属线465a具有凹陷区域r,并且金属线466a是不连续的线。这是因为使用切割布局图案450(图4a)对金属线465a和466a进行图案化。例如,首先将光阻涂覆在半导体元件400a上,然后使用布局400中的切割布局图案450进行图案化,接着,透过使用图案化的光阻作为蚀刻遮罩的蚀刻制程对金属线465a至466a进行图案化。作为蚀刻制程的结果,金属线466a被分成不连续的金属线,并且金属线465a具有凹陷区域r(如图4b所示)。此外,金属线461a至464a和467a在图案化金属线465a和466a期间保持完整,这是因为切割布局图案450不与布局400中的金属线布局图案461至464和467重叠。

471.半导体元件400a还包括分别在源极/漏极接触444a上方的源极/漏极导孔481a、482a和483a。源极/漏极导孔481a位于金属线466a和左侧的源极/漏极接触444a的相交处,从而在其间提供电连接。源极/漏极导孔482a位于金属线465a和中间的源极/漏极接触444a的相交处,从而在其间提供电连接。源极/漏极导孔483a位于金属线466a和右侧的源极/漏极接触444a的相交处,从而在其间提供电连接。因为左侧的源极/漏极接触444a和右侧的源极/漏极接触444a均电连接到金属线466a,因此它们可以电连接到相同的电压。

472.在部分实施例中,源极/漏极导孔481a至483a包括导电材料(例如,钴、铜、钨或其他合适的金属)。源极/漏极导孔481a至483a的形成包括例如在源极/漏极接触444a上方的

第二层间介电质层(其形成在未绘示的第一层间介电质层上方)中蚀刻源极/漏极导孔开口,在源极/漏极导孔开口中沉积一种或多种导电材料,并透过使用例如化学机械平坦化制程来平坦化一种或多种导电材料。在部分实施例中,源极/漏极导孔481a至483a与栅极接触471a和472a同时形成,因此源极/漏极导孔481a至483a与栅极接触471a和472a具有相同的导电材料。如图4b所示,半导体元件400a可以仅使用四条m0线(即,金属线463a、464a、465a和466a)来对栅极接触471a、472a和源极/漏极导孔481a至483a进行布线,这将节省绕线资源并提高绕线灵活性。

473.图5a是根据一些其他实施例的半导体元件的布局500的视图。布局500可用于制造如图5b至图5c所示的半导体元件500a。布局500类似于布局200,除了附加的源极/漏极导孔布局图案和不同的切割图案以外(如下文更详细地描述)。在以下实施例中可以采用与图2a至图2c所描述的相同或相似的配置,并且可以省略详细说明。

474.参照图5a,布局500包括第一鳍片组布局图案510和第二鳍片组布局图案520。第一鳍片组布局图案510和第二鳍片组布局图案520定义了半导体元件500a的相应的第一鳍片组区域510a和第二鳍片组区域520a(图5b至图5c)。第一鳍片组布局图案510包括三个第一鳍片布局图案512,而第二鳍片组布局图案520包括三个第二鳍片布局图案522。第一鳍片布局图案512中的每一个均包括第一源极/漏极区域布局图案514,其定义半导体元件500a的对应的第一源极/漏极区域514a(图5b至图5c)。类似地,第二鳍片布局图案522中的每一个均包括第二源极/漏极区域布局图案524,其定义了半导体元件500a的对应的第二源极/漏极区域524a(图5b至图5c)。在部分实施例中,鳍片布局图案512和522的鳍片宽度和鳍片至鳍片间距与图2a所示的鳍片布局图案212和222的鳍片宽度和鳍片至鳍片间距相同,因此,为了避免重复,不再赘述。鳍片布局图案512和522透过隔离结构布局图案504彼此分离并在相同的布局层上与布局500的其他元件间隔开。隔离结构布局图案504定义了半导体元件500a的对应的隔离结构504a(图5b至图5c)。

475.布局500还包括沿着y方向延伸跨越鳍片组布局图案510和520的多个栅极布局图案531、532、533和534。栅极布局图案531至534定义了半导体元件500a的对应的栅极结构531a、532a、533a和534a(图5b至图5c)。栅极布局图案531至534以及在栅极布局图案531至534的相对侧上的对应的源极/漏极区域布局图案514和524形成多个场效应晶体管。在部分实施例中,栅极布局图案531至534的栅极至栅极间距与如图2a所示的栅极布局图案231至234的栅极至栅极间距相同,因此为了简洁起见不重复。

476.布局500包括沿y方向延伸跨越三个第一鳍片布局图案512的第一源极/漏极区域布局图案514的多个第一源极/漏极接触布局图案542,因此,三个第一鳍片布局图案512共享公共的源极/漏极接触布局图案542。类似地,布局500还包括沿着y方向延伸跨越三个第二鳍片布局图案522的第二源极/漏极区域布局图案524的多个第二源极/漏极接触布局图案544,因此,三个第二鳍片布局图案522共享公共的源极/漏极接触布局图案544。源极/漏极接触布局图案542和544定义了半导体元件500a的对应的源极/漏极接触542a和544a(图5b至图5c)。

477.布局500还包括沿着x方向延伸并且沿着y方向彼此间隔开的多个金属线布局图案561、562、563、564、565、566和567。金属线布局图案561至567定义半导体元件500a的对应的金属线561a至567a(图5b至图5c)。在布局500的上边界处的金属线布局图案561是vdd线布

局图案,并且在布局500的下边界处的金属线布局图案567是vss线布局图案,其中vss线布局图案的宽度大于vdd线布局图案561的宽度。金属线布局图案562至566配置在vdd线布局图案561和vss线布局图案567之间。

478.金属线布局图案562至566被移位,因此相对于鳍片组布局图案510和520以非对称方式配置。例如,金属线布局图案562至566朝着第一鳍片组偏移。金属线布局图案562至566的不对称配置允许金属线布局图案564和565配置在鳍片组布局图案510和520之间,而不与鳍片布局图案512和522中的任何一个重叠。在部分实施例中,金属线布局图案561至567的线宽、线至线间距和不对称配置与图2a所示的金属线布局图案261至267相同,因此为了简洁起见,不再重复描述。

479.布局500还包括分别覆盖在对应的栅极布局图案532和533上的栅极接触布局图案571和572。栅极接触布局图案571和572定义了半导体元件500a的对应的栅极接触571a和572a(图5b至图5c)。栅极接触布局图案571与栅极布局图案532和金属线布局图案564的相交处重叠,从而提供了在栅极布局图案532和金属线布局图案564之间的电连接。栅极接触布局图案572与栅极布局图案533和金属线布局图案565的相交处重叠,从而在栅极布局图案533和金属线布局图案565之间提供电连接。透过这种方式,栅极结构532a和533a电连接到不同的金属线564a和565a(图5b至图5c),其将允许栅极结构532a和533a电连接到不同的网络。

480.布局500进一步包括沿y方向延伸跨越金属线布局图案562的两个切割布局图案550。切割布局图案550仅与金属线布局图案563的一部分重叠。换句话说,切割布局图案550延伸超过金属线布局图案563的上部长侧,并且从金属线布局图案563的下部长侧向后缩回。切割布局图案550代表根据集成电路设计去除金属线布局图案562和563的切割部分或图案化区域。

481.布局500还包括分别覆盖在对应的源极/漏极接触布局图案542上的源极/漏极导孔布局图案581、582和583。源极/漏极导孔布局图案581、582和583定义了半导体元件500a的对应的源极/漏极导孔581a、582a和583a(图5b至图5c)。源极/漏极导孔布局图案581与左侧的源极/漏极接触布局图案542和金属线布局图案562的相交处重叠,从而在其间提供电连接。源极/漏极导孔布局图案582与中间的源极/漏极接触布局图案542和金属线布局图案563的相交处重叠,从而在其间提供电连接。源极/漏极导孔布局图案583与右侧的源极/漏极接触布局图案542和金属线布局图案562的相交处重叠,从而在其间提供电连接。因此,布局500可以仅使用四个m0线布局图案(即,线图案562、563、564和565)来对栅极接触和源极/漏极导孔进行布线,这将节省布线资源并提高布线灵活性。

482.图5b和图5c是根据部分实施例的使用布局500制造的半导体元件500a的视图,因此,半导体元件500a继承了布局500中的那些图案的几何形状(如下面更详细地描述的)。图5b是半导体元件500a的上视图。图5c是图5b沿线c-c’截取的半导体元件500a的剖面图。半导体元件500a是用于帮助本揭露的说明的非限制性示例。

483.参考图5b和图5c,半导体元件500a包括基板502a,从基板502a向上延伸的第一鳍片组510a和第二鳍片组520a,以及沿y方向延伸跨越鳍片组510a和520a的栅极结构531a、532a、533a和534a。第一鳍片组510a包括沿着x方向延伸的三个第一鳍片512a,而第二鳍片组520a也包括沿着x方向延伸的三个第二鳍片522a。基板502a、鳍片512a、522a的示例性材

料和制造方法与图2b至图2c中所示的相似,因此为了简洁起见不再重复。在部分实施例中,鳍片512a和522a的鳍片宽度和鳍片至鳍片间距与图2b所示的鳍片212a和222a的鳍片宽度和鳍片至鳍片间距相同,因此为简洁起见不再重复。

484.鳍片512a和522a透过隔离结构504a彼此电隔离。在部分实施例中,隔离结构504a是浅沟槽隔离结构,其包括填充有一种或多种介电材料的沟槽。浅沟槽隔离结构504a的示例性材料和制造方法类似于在图1b至图1d中所示的浅沟槽隔离结构104a的描述,因此为了简洁起见不再重复。

485.鳍片512a和522a包括多个源极/漏极区域514a和524a。源极/漏极区域514a和524a是位于相应的栅极结构431a至534a的相对侧上的掺杂的半导体区域。在部分实施例中,源极/漏极区域514a和524a包括p型掺杂剂(例如,硼),以用于形成p型场效应晶体管。在其他实施例中,源极/漏极区域514a和524a包括n型掺杂剂(例如,磷),以用于形成n型场效应晶体管。源极/漏极区域514a和524a的示例性制造方法类似于在图2b至图2c中所示的源极/漏极区域214a和224a的描述,因此为了简洁起见不再重复。

486.栅极结构531a至534a沿着y方向延伸跨越第一鳍片512a和第二鳍片522a。在部分实施例中,栅极结构531a至534a是高介电常数金属栅极结构,其可以使用后栅极制程流程形成(如先前关于图2b至图2c所示的栅极结构231a至234a所述)。因此,为了简洁起见,不再重复高介电常数金属栅极结构的示例性材料和制造方法。栅极结构531a至534a的栅极至栅极间距与栅极结构231a至234a的栅极至栅极间距相同,因此为了简洁起见不重复。

487.半导体元件500a进一步包括第一源极/漏极接触542a和第二源极/漏极接触544a,其中每个第一源极/漏极接触542a均延伸跨越三个第一鳍片512a的第一源极/漏极区域514a,而每个第二源极/漏极接触544a均延伸跨越三个第二鳍片522a的第二源极/漏极区域524a。半导体元件500a还包括在栅极结构532a上方的栅极接触571a和在栅极结构533a上方的栅极接触572a。源极/漏极接触542a、544a和栅极接触571a、572a的示例性材料和制造方法与在图2b至图2c所示的源极/漏极接触242a、244a和栅极接触271a、272a的描述相似,因此为了简洁起见不再重复。

488.半导体元件500a进一步包括多个金属线561a、562a、563a、564a、565a、566a和567a,其沿着x方向在栅极接触571a和572a上方的下一层上延伸。图5b所示的最上面的金属线561a是vdd线,而图5b所示的最下面的金属线567a是vss线。vdd线561a电连接至vdd电压(例如,正电压),而vss线567a电连接至vss电压(例如,接地或负电压)。金属线562a至566a配置在vdd线561a和vss线567a之间,并且可以连接到与vdd线561a和vss线567a不同的电压。金属线561a至567a的示例性材料和制造方法与在图1b至图1d中所示的金属线161a至167a的描述相似,因此为了简洁起见不再重复。金属线561a至567a的线宽、线至线间距和不对称的配置与如前所述的金属线261a至267a的线宽、线至线间距和不对称配置相同,因此为了简洁起见不再重复。

489.在如图5b所示的实施例中,当从上方观察时,金属线563a具有凹陷区域r并且金属线562a是不连续的线。这是因为使用切割布局图案550(图5a)对金属线562a和563a进行了图案化。例如,首先将光阻涂覆在半导体元件500a上,然后使用布局500中的切割布局图案550将其图案化,随后,透过使用图案化的光阻作为蚀刻遮罩的蚀刻制程来图案化金属线562a至563a。作为蚀刻制程的结果,金属线562a被分成不连续的金属线,并且金属线563a具

有凹陷区域r(如图5b所示)。此外,金属线561a和564a至567a在图案化金属线562a和563a期间保持完整,这是因为切割布局图案550不与布局500中的金属线布局图案561和564至567重叠。

490.半导体元件500a还包括分别在源极/漏极接触542a上方的源极/漏极导孔581a、582a和583a。源极/漏极导孔581a位于金属线562a与左侧的源极/漏极接触542a的相交处,从而在其间提供电连接。源极/漏极导孔582a位于金属线563a与中间的源极/漏极接触542a的相交处,从而在其间提供电连接。源极/漏极导孔583a位于金属线562a与右侧的源极/漏极接触542a的相交处,从而在其间提供电连接。因为左侧的源极/漏极接触542a和右侧的源极/漏极接触542a均电连接到金属线562a,所以它们可以电连接到相同的电压。源极/漏极导孔581a至583a的示例性材料和制造方法类似于在图4b和图4c所示的源极/漏极导孔481a至483a的描述,因此为了简洁起见不再重复。

491.图6是根据部分实施例的电子设计自动化(electronic design automation,eda)系统600的示意图。根据部分实施例,本文描述的根据一个或多个实施例产生的设计布局(例如,布局100、200、300、400和500)的方法可例如使用电子设计自动化系统600来实现。在部分实施例中,电子设计自动化系统600是通用计算机装置,其包括硬件处理器602和非暂态计算机可读储存媒体604。除其他之外,计算机可读储存媒体604被编码(即,储存)可执行指令集606、设计布局607、设计规则检查(design rule check,drc)平台609或用于执行指令集的任何中间数据。每个设计布局607包括集成晶片的图形表示(例如,gsii文件)。每个设计规则检查平台609包括特定用于制造设计布局607而选择的半导体制程的设计规则的列表。由硬件处理器602执行的指令606、设计布局607和设计规则检查平台609(至少部分地)表示根据一个或多个实现的方法的一部分或全部(以下简称为所提到的过程及/或方法)的电子设计自动化工具。

492.处理器602透过总线608电耦合到计算机可读储存媒体604。处理器602也透过总线608电耦合到输入/输出(i/o)接口610。网络接口612也透过总线608电耦合到处理器602。网络接口612连接到网络614,以便处理器602和计算机可读储存媒体604能够透过网络614连接到外部元件。处理器602配置为执行编码在计算机可读储存媒体604中的指令606,以使电子设计自动化系统600可用于执行所述过程及/或方法的一部分或全部。在一个或多个实施例中,处理器602是中央处理器(central processing unit,cpu)、多元处理器、分布式处理系统、特殊应用集成电路(application specific integrated circuit,asic)及/或合适的处理单元。

493.在一个或多个实施例中,计算机可读储存媒体604是电、磁、光、电磁、红外及/或半导体系统(或装置或设备)。例如,计算机可读储存媒体604包括半导体或固态记忆体、磁带、可移动计算机磁盘、随机存取记忆体(random access memory,ram)、只读记忆体(read-only memory,rom)、刚性磁盘及/或光盘。在使用光盘的一个或多个实施例中,计算机可读储存媒体604包括只读光盘(compact disk-read only memory,cd-rom)、读/写光盘(cd-r/w)及/或数字影音光盘(digital video disc,dvd)。

494.在一个或多个实施例中,计算机可读储存媒体604储存指令606,设计布局607(例如,先前讨论的布局100、200、300、400和500)和设计规则检查平台609被配置为使电子设计自动化系统600(其中这样的执行(至少部分地)代表电子设计自动化工具)可用于执行所提

到的过程及/或方法的一部分或全部。在一个或多个实施例中,计算机可读储存媒体604还储存有助于执行部分或全部所述过程及/或方法的讯息。

495.电子设计自动化系统600包括输入/输出(i/o)接口610。i/o接口610耦合到外部电路。在一个或多个实施例中,i/o接口610包括键盘、小键盘、鼠标、轨迹球、触控板、触摸屏及/或光标方向键,以用于将讯息和指令传达给处理器602。

496.电子设计自动化系统600还包括耦合到处理器602的网络接口612。网络接口612允许电子设计自动化系统600与一个或多个其他计算机系统连接到的网络614通讯。网络接口612包括无线网络接口(例如,蓝牙(bluetooth)、无线网络(wifi)、全球互通微波存取(wimax)、通用封包无线服务(gprs)或宽频分码多重进接(wcdma));或有线网络接口(例如,以太网络(ethernet)、通用序列总线(usb)或ieee-1364)。在一个或多个实施例中,在两个或更多个电子设计自动化系统600中执行一部分或全部所述过程及/或方法。

497.电子设计自动化系统600被配置为透过i/o接口610接收讯息。透过i/o接口610接收的讯息包括指令、数据、设计规则、标准单元库及/或经由处理器602处理的其他参数中的一个或多个。讯息经由总线608传输到处理器602。电子设计自动化系统600配置为透过i/o接口610接收与使用者界面(user interface,ui)616有关的讯息。此讯息储存在计算机可读储存媒体604中作为使用者界面616。

498.在部分实施例中,可使用诸如从cadence design systems公司获得的工具或另一种合适的布局生成工具来产生包括标准单元的布局图。

499.在部分实施例中,这些过程被实现为储存在非暂态计算机可读记录媒体中的程序的功能。非暂态计算机可读记录媒体的示例包括但不限于外部/可移动及/或内部/内置储存或记忆体单元(例如,光盘(例如,数字影音光盘)、磁盘(例如,硬盘)、半导体记忆体(例如,只读记忆体、随机存取记忆体、记忆卡等))。

500.在图6中绘示与电子设计自动化系统600相关联的制造工具。例如,遮罩室630透过诸如网络614从电子设计自动化系统600接收设计布局,遮罩室630具有遮罩制造工具632(例如,遮罩写入器(mask writer)),以用于从基于电子设计自动化系统600生成的设计布局来制造一个或多个光罩(例如,用于制造诸如半导体元件100a、200a、300a、400a及/或500a的光罩)。集成电路系统制造商(fab)620可以透过诸如网络614连接到遮罩室630和电子设计自动化系统600。制造商620包括用于使用由遮罩室630制造的光罩以制造集成电路晶片(例如,半导体元件100a、200a、300a、400a及/或500a)。作为示例而非限制,集成电路制造工具622包括一个或多个用于制造集成电路晶片的集结式加工机台(cluster tool)。集结式加工机台可以是多反应室型复合设备,其包括在其中心处插入有晶圆处理机器人的多面体传输室,其中多个处理室(例如,化学气相沉积室、物理气相沉积室、蚀刻室、退火室等)位在多面体传输室的每个壁面上,而晶圆装载室(loadlock chamber)安装在传输室的另一壁面上。

501.图7是根据部分实施例的半导体元件制造系统700以及与其相关联的装置制造流程的框图。在部分实施例中,基于设计布局(例如,布局100、200、300、400或500),使用制造系统700来制造一个或多个光罩中的至少一个或半导体元件中的一层中的至少一个元件。

502.在图7中,元件制造系统700包括多个实体(例如,设计厂720、光罩厂730和制造商750),它们在设计、开发和制造周期及/或与制造半导体元件760有关的服务中彼此关联。元

checking,lpc),其模拟将由制造商750执行以制造半导体元件760的制程。微影制程检查基于设计布局722来模拟此制程,以创建模拟的被制造元件装置(例如,被制造出的半导体元件760)。微影制程检查模拟中的处理参数可以包括与集成电路制造周期的各种过程相关的参数、与用于制造集成电路的工具相关的参数及/或与制造过程的其他方面相关的参数。微影制程检查考虑了各种因素(例如,空间影像对比度(aerial image contrast)、焦距深度(depth of focus,dof)、光罩误差增强因素(mask error enhancement factor,meef)和其他合适的因素等或其组合)。在部分实施例中,在微影制程检查已经建立了模拟的制造装置之后,如果模拟的装置在形状上不够接近以满足设计规则,则重复光学邻近修正及/或光罩规则检查器以进一步完善设计布局722。

508.可理解到,为了清楚起见,光罩数据准备732的以上描述已被简化。在部分实施例中,数据准备732包括诸如逻辑运算(logic operation,lop)之类的附加特征,以根据制造规则来修改设计布局722。另外,可以以各种不同的顺序执行在数据准备732期间应用于设计布局722的过程。

509.在光罩数据准备732之后以及在光罩制造744期间,基于设计布局722制造光罩745或一组光罩745。在部分实施例中,光罩制造744包括基于设计布局722执行的一个或多个微影曝光。在部分实施例中,基于设计布局722,使用电子束(e-beam)或多个电子束的机制在光罩745上形成图案。光罩745可以以各种技术形成。在部分实施例中,使用二进制技术形成光罩745。在部分实施例中,光罩图案包括不透明区域和透明区域。用于曝光已经涂覆在晶片上的辐射敏感材料层(例如,光阻)的辐射束(例如,紫外线(uv)束)被不透明区域阻挡并且穿透过透明区域。在一个示例中,光罩745的二元光罩版本包括透明基板(例如,熔融石英)和涂覆在二元光罩的不透明区域中的不透明材料(例如,铬)。在另一示例中,使用相位移技术形成光罩745。在光罩745的相位移光罩(phase shift mask,psm)版本中,形成在相位移光罩上的图案中的各种特征被配置为具有适当的相差以增强解析度和成像品质。在各种示例中,相位移光罩可以是衰减式相位移光罩或交替式相位移光罩。由光罩制造744产生的光罩可用于多种制程中。例如,可在离子布植制程中使用这样的光罩以在半导体晶片753中形成各种掺杂区域,可在蚀刻制程中使用这种光罩以在半导体晶片753中形成各种蚀刻区域,及/或可在其他合适的制程中使用这种光罩。

510.制造商750包括晶圆制造752。制造商750是包括一个或多个用于制造各种不同集成电路产品的制造设备的制造企业。在部分实施例中,制造商750是半导体代工厂。例如,可能有一个制造商用于多个集成电路产品的前段制程(front-end-of-line,feol),而第二个制造商可以为集成电路产品的互连和封装提供后段制程(back-end-of-line,beol),并且第三个制造商可以为代工厂提供其他服务。

511.制造商750使用由光罩厂730制造的光罩745来制造半导体元件760。因此,制造商750至少间接地使用设计布局722来制造半导体元件760。在部分实施例中,制造商750使用光罩745制造半导体晶片753以形成半导体元件760。在部分实施例中,装置制造包括至少间接地基于设计布局722执行一次或多次微影曝光。半导体晶片753包括硅基板或在其上具有材料层的其他合适的基板。半导体晶片753进一步包括各种掺杂区域、介电质特征、多层互连和(在随后的制造步骤中形成之)其他结构中的一个或多个。

512.基于以上讨论,可以看出提供了益处。然而,应当理解,其他实施例可以提供附加

的益处,并且在此不必公开所有益处,并且对于所有实施例均不需要特定的益处。其中一个益处是,m0线的不对称配置允许在相邻鳍片组之间配置多条m0线(例如,两条m0线)而不与鳍片组中的任何鳍片重叠,从而允许多个栅极接触(例如,两个栅极接触)与电连接到不同网络的m0线重叠,而无需减少鳍片数量或增加额外的微影和蚀刻步骤。另一个益处是,vdd线和vss线之间的宽度差有助于等距地排列非对称配置的m0线。

513.在部分实施例中,半导体元件包括第一组半导体鳍片、第二组半导体鳍片、第一栅极结构、vdd线和vss线。第一组半导体鳍片沿着第一方向延伸并且以第一鳍片至鳍片间距配置。第二组半导体鳍片沿着第一方向延伸并且以第二鳍片至鳍片间距配置。第二组半导体鳍片与第一组半导体鳍片透过无鳍片区域间隔开,其中此无鳍片区域大于第一鳍片至鳍片间距和第二鳍片至鳍片间距。第一栅极结构沿着与第一方向不同的第二方向延伸跨越第一组半导体鳍片、无鳍片区域和第二组半导体鳍片。vdd线和vss线沿着第一方向在第一栅极结构上延伸。从上视图来看,第一组半导体鳍片和第二组半导体鳍片在vdd线和vss线之间,并且从上视图看,vdd线和第一组半导体鳍片之间的重叠区域不同于vss线和第二组半导体鳍片之间的重叠区域。

514.在部分实施例中,在该上视图中,该vdd线与该第一组半导体鳍片之间的该重叠区域大于该vss线与该第二组半导体鳍片之间的该重叠区域。

515.在部分实施例中,在该上视图中,该vss线与该第二组半导体鳍片之间的该重叠面积大于该vdd线与该第一组半导体鳍片之间的该重叠面积。

516.在部分实施例中,该vdd线和该vss线具有不同的宽度。

517.在部分实施例中,在该上视图中,该vdd线比该vss线宽。

518.在部分实施例中,在该上视图中,该vss线比该vdd线宽。

519.在部分实施例中,半导体元件还包含多个第一金属线,在与该vdd线和该vss线相同的水平高度上延伸,所述多个第一金属线不与该第一组半导体鳍片和该第二组半导体鳍片重叠。

520.在部分实施例中,半导体元件还包含一第一栅极接触,将该第一栅极结构电连接到所述多个第一金属线之一。

521.在部分实施例中,半导体元件还包含一第二栅极结构以及一第二栅极接触。第二栅极结构沿该第二方向在该第一组半导体鳍片、该无鳍片区域和该第二组半导体鳍片上延伸。第二栅极接触,将该第二栅极结构电连接到所述多个第一金属线的另一个。

522.在部分实施例中,半导体元件还包含至少一第二金属线以及至少一第三金属线。第二金属线在与该vdd线和该vss线相同的水平高度上延伸,该至少一第二金属线在该vdd线和所述多个第一金属线之间。第三金属线在与该vdd线和该vss线相同的水平高度上延伸,该至少一第三金属线在该vss线和所述多个第一金属线之间,其中该至少一第二金属线的一数量与该至少一第三金属线的一数量不同。

523.在部分实施例中,半导体元件包括第一组半导体鳍片、第二组半导体鳍片、第一栅极结构、第二栅极结构、第一金属线、第二金属线、第一栅极接触、第二栅极接触、vdd线和vss线。第一组半导体鳍片和第二组半导体鳍片沿着第一方向延伸并且由无鳍片区域间隔开。第一栅极结构和第二栅极结构沿着不同于第一方向的第二方向延伸跨越第一组半导体鳍片、无鳍片区域和第二组半导体鳍片。第一金属线和第二金属线在无鳍片区域内沿着第

一方向延伸。从上视图来看,第一栅极接触与第一金属线和第一栅极结构的相交处重叠,并且从上视图来看,第二栅极接触与第二金属线和第二栅极结构的相交处重叠。vdd线和vss线在与第一金属线和第二金属线相同的水平上延伸。vdd线与第一组半导体鳍片相邻,vss线与第二组半导体鳍片相邻,并且vdd线和vss线具有不同的宽度。

524.在部分实施例中,该vdd线的该宽度大于该vss线的该宽度。

525.在部分实施例中,该vss线的该宽度大于该vdd线的该宽度。

526.在部分实施例中,半导体元件还包含多个第一源极/漏极接触,延伸跨越该第一组半导体鳍片,其中该第一金属线和该第二金属线均不与所述多个第一源极/漏极接触重叠。

527.在部分实施例中,半导体元件还包含多个第二源极/漏极接触,延伸跨越该第二组半导体鳍片,其中该第一金属线和该第二金属线均不与所述多个第二源极/漏极接触重叠。

528.在部分实施例中,半导体元件还包含多个源极/漏极导孔以及一第三金属线。所述多个源极/漏极导孔分别在所述多个第二源极/漏极接触上。第三金属线在与该第一金属线和该第二金属线相同的水平高度上延伸并且与所述多个源极/漏极导孔重叠。

529.在部分实施例中,半导体元件还包含多个源极/漏极导孔以及一第三金属线。所述多个源极/漏极导孔分别在所述多个第一源极/漏极接触上。第三金属线在与该第一金属线和该第二金属线相同的水平高度上延伸并且与所述多个源极/漏极导孔重叠。

530.在部分实施例中,一种方法包括在布局中生成沿着第一方向延伸的第一组鳍片布局图案和第二组鳍片布局图案,第一组鳍片布局图案和第二组鳍片布局图案对称于对称轴;在布局中产生沿第二方向延伸跨越第一组鳍片布局图案和第二组鳍片布局图案的多个栅极布局图案,第二方向不同于第一方向;在布局中生成沿第一方向延伸跨越多个栅极布局图案的多个金属线布局图案,金属线布局图案不对称于第一组鳍片布局图案和第二组鳍片布局图案的对称轴;根据布局制造半导体元件。

531.在部分实施例中,方法还包含于该布局中,生成与这些栅极布局图案中的一第一栅极布局图案和所述多个金属线布局图案中的一第一金属线布局图案的一相交处重叠的一第一栅极接触布局图案;以及于该布局中,生成与所述多个栅极布局图案中的一第二栅极布局图案和所述多个金属线布局图案中的一第二金属线布局图案的一相交处重叠的一第二栅极接触布局图案。该第一金属线布局图案和该第二金属线布局图案均不与该第一组鳍片布局图案和该第二组鳍片布局图案重叠。

532.于部分实施例中,方法还包含于该布局中,生成沿该第二方向延伸并跨越该第一组鳍片布局图案的多个第一源极/漏极接触布局图案;以及于该布局中,生成沿该第二方向延伸并跨越该第二组鳍片布局图案的多个第二源极/漏极接触布局图案。该第一金属线布局图案和该第二金属线布局图案均不与所述多个第一源极/漏极接触布局图案和所述多个第二源极/漏极接触布局图案重叠。

533.前述概述了几个实施例的特征,使得本领域技术人员可以更好地理解的各方面。本领域技术人员应当理解,他们可以容易地将用作设计或修改其他过程和结构的基础,以实现与本文介绍的实施例相同的目的及/或实现相同的益处。本领域技术人员还应该理解,这样的等效构造不脱离的精神和范围,并且在不脱离的精神和范围的情况下,它们可以进行各种改变、替换和变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。