1.本发明涉及逻辑计算器件技术领域,尤其涉及一种基于磁性存储器的逻辑计算单元、方法及全加器。

背景技术:

2.传统的全加器采用互补金属-氧化物-半导体(complementary metal-oxide-semiconductor,cmos)工艺设计,其存在一些缺点:首先,cmos晶体管的漏电流随着工艺尺寸的减小而增大,导致静态功耗日益加剧,其次cmos全加器基于冯诺依曼架构而设计,数据搬移的功耗大,所需带宽大。

技术实现要素:

3.本发明的一个目的在于提供一种基于磁性存储器的逻辑计算单元,无静态功耗,写入速度快。本发明的另一个目的在于提供一种基于磁性存储器的逻辑计算方法。本发明的再一个目的在于提供一种基于磁性存储器的全加器。

4.为了达到以上目的,本发明一方面公开了一种基于磁性存储器的逻辑计算单元,包括加法电路;

5.所述加法电路包括用于存储加数的第一磁性存储器、与所述第一磁性存储器连接的第一通路和第二通路;

6.所述第一通路用于响应于被加数信号进行加数与被加数的或运算,所述第二通路用于响应于加数信号和被加数信号完成加数与被加数的异或运算得到存储于所述第一磁性存储器中的第一异或结果。

7.优选的,

8.当所述被加数信号为第一电平时,所述第一通路导通,所述第一磁性存储器存储第一逻辑数字;

9.当所述加数信号和被加数信号为第一电平时,所述第二通路导通,所述第一磁性存储器存储第二逻辑数字。

10.优选的,所述第一通路进一步用于响应于进位信号进行进位数和所述第一异或结果的或运算,所述第二通路用于响应于所述进位信号和所述第一异或结果对应的信息完成所述进位数与所述第一异或结果的异或运算得到存储于所述第一磁性存储器中的全加运算结果。

11.优选的,

12.当所述进位信号为第一电平时,所述第一通路导通,所述第一磁性存储器存储第一逻辑数字;

13.当所述进位信号和第一异或结果对应的信号为第一电平时,所述第二通路导通,所述第一磁性存储器存储第二逻辑数字。

14.优选的,还包括进位电路;

15.所述进位电路包括第二磁性存储器、与所述第二磁性存储器连接的第三通路和第四通路;

16.所述第三通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第一进位结果,所述第四通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第二进位结果。

17.优选的,

18.当所述被加数信号和进位信号为第一电平时,所述第三通路导通,所述第二磁性存储器存储第一逻辑数字;

19.当所述进位信号或被加数信号为第二电平时,所述第四通路导通,所述第二磁性存储器存储第二逻辑数字。

20.优选的,所述进位电路进一步用于响应于被加数信号、加数信号和进位信号得到存储于所述第二磁性存储器中的第三进位结果。

21.优选的,

22.当所述加数信号和进位信号为第一电平或者所述加数信号和被加数信号为第一电平时,所述第三通路导通,所述第二磁性存储器存储第一逻辑数字。

23.优选的,所述第一磁性存储器包括第一重金属层和设于所述第一重金属层上的第一磁隧道结;

24.所述第一重金属层包括第一输入方向的第一端和第二端以及第二输入方向的第三端和第四端,当通过第一输入方向向所述第一重金属层输入电流,所述第一磁隧道结的阻态为第一逻辑数字对应的第一阻态,当通过第二输入方向向所述第一重金属层输入电流,所述第一磁隧道结的阻态为第二逻辑数字对应的第二阻态。

25.优选的,

26.所述第一通路包括第一开关元件和第二开关元件;

27.所述第一开关元件的控制端用于接收所述被加数信号,第一端与第一电源端连接,第二端与所述第一磁性存储器的第一端连接;

28.所述第二开关元件的控制端用于接收所述被加数信号,第一端与接地端连接,第二端与所述第一磁性存储器的第二端连接。

29.优选的,

30.所述第二通路包括第三开关元件和第四开关元件;

31.所述第三开关元件的控制端用于接收所述被加数信号,第一端与第二电源端连接,第二端与所述第一磁性存储器的第三端连接;

32.所述第四开关元件的控制端用于接收所述加数信号,第一端与接地端连接,第二端与所述第一磁性存储器的第四端连接;或者,

33.所述第三开关元件的控制端用于接收所述加数信号,第一端与第二电源端连接,第二端与所述第一磁性存储器的第三端连接;

34.所述第四开关元件的控制端用于接收所述被加数信号,第一端与接地端连接,第二端与所述第一磁性存储器的第四端连接。

35.优选的,所述第一通路进一步包括第五开关元件和第六开关元件;

36.所述第五开关元件的控制端用于接收所述进位信号,第一端与第一电源端和所述

第一开关元件的第一端分别连接,第二端与所述第一磁性存储器的第一端和所述第一开关元件的第二端分别连接;

37.所述第六开关元件的控制端用于接收所述进位信号,第一端与接地端和所述第二开关元件的第一端分别连接,第二端与所述第一磁性存储器的第二端和所述第二开关元件的第二端分别连接。

38.优选的,所述第二磁性存储器包括第二重金属层(重金属层)和设于所述第二重金属层上的第二磁隧道结;

39.所述第二重金属层包括第三输入方向的第五端和第六端以及第四输入方向的第七端和第八端,当通过第三输入方向向所述第二重金属层(重金属层)输入电流,所述第二磁隧道结的阻态为第一阻态,当通过第四输入方向向所述第二重金属层(重金属层)输入电流,所述第二磁隧道结的阻态为第二阻态。

40.优选的,所述第三通路包括第七开关元件和第八开关元件;

41.所述第七开关元件的控制端用于接收所述被加数信号,第一端与第三电源端连接,第二端与所述第二磁性存储器的第五端连接;

42.所述第八开关元件的控制端用于接收所述进位信号,第一端与接地端连接,第二端与所述第二磁性存储器的第六端连接;或者,

43.所述第七开关元件的控制端用于接收所述进位信号,第一端与第三电源端连接,第二端与所述第二磁性存储器的第五端连接;

44.所述第八开关元件的控制端用于接收所述被加数信号,第一端与接地端连接,第二端与所述第二磁性存储器的第六端连接。

45.优选的,所述第四通路包括第九开关元件和第十开关元件;

46.所述第九开关元件的控制端用于接收所述被加数信号,第一端与第四电源端和所述第十开关元件的第一端分别连接,第二端与所述第二磁性存储器的第七端和所述第十开关元件的第二端分别连接;

47.所述第十开关元件的控制端用于接收所述进位信号;

48.所述第二磁性存储器的第八端与接地端连接;或者,

49.所述第九开关元件的控制端用于接收所述被加数信号,第一端与接地端和所述第十开关元件的第一端分别连接,第二端与所述第二磁性存储器的第七端和所述第十开关元件的第二端分别连接;

50.所述第十开关元件的控制端用于接收所述进位信号;

51.所述第二磁性存储器的第八端与第四电源端连接。

52.优选的,所述第三通路包括第十一开关元件、第十二开关元件和第十三开关元件;

53.所述第十一开关元件的控制端用于接收所述加数信号,第一端与第五电源端连接,第二端与所述第二磁性存储器的第五端连接;

54.所述第十二开关元件的控制端用于接收所述被加数信号,第一端与接地端连接,第二端与所述第二磁性存储器的第六端连接;

55.所述第十三开关元件的控制端用于接收所述进位信号,第一端与接地端连接,第二端与所述第二磁性存储器的第六端连接。

56.本发明还公开了一种基于磁性存储器的逻辑计算方法,所述逻辑计算单元包括加

法电路,所述加法电路包括用于存储加数的第一磁性存储器、与所述第一磁性存储器连接的第一通路和第二通路,所述第一通路用于响应于被加数信号进行加数与被加数的或运算,所述第二通路用于响应于加数信号和被加数信号完成加数与被加数的异或运算得到存储于所述第一磁性存储器中的第一异或结果,所述方法包括:

57.在t1时刻:

58.响应于第一电平的被加数信号,所述第一通路导通,所述第一磁性存储器存储第一逻辑数字;

59.在t2时刻:

60.响应于第一电平的加数信号和被加数信号,所述第二通路导通,所述第一磁性存储器存储第二逻辑数字。

61.优选的,所述第一通路进一步用于响应于进位信号进行进位数和所述第一异或结果的或运算,所述第二通路用于响应于所述进位信号和所述第一异或结果对应的信息完成所述进位数与所述第一异或结果的异或运算得到存储于所述第一磁性存储器中的全加运算结果,所述方法进一步包括:

62.在t3时刻:

63.响应于第一电平的进位信号,所述第一通路导通,所述第一磁性存储器存储第一逻辑数字;

64.在t4时刻:

65.响应于第一电平的所述进位信号和第一异或结果对应的信号,所述第二通路导通,所述第一磁性存储器存储第二逻辑数字。

66.优选的,所述逻辑计算方法还包括进位电路,所述进位电路包括第二磁性存储器、与所述第二磁性存储器连接的第三通路和第四通路,所述第三通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第一进位结果,所述第四通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第二进位结果,所述方法进一步包括:

67.在t1时刻:

68.响应于第一电平的被加数信号和进位信号,所述第三通路导通,所述第二磁性存储器存储第一逻辑数字;

69.在t2时刻:

70.响应于第二电平的加数信号或进位信号,所述第四通路导通,所述第二磁性存储器存储第二逻辑数字。

71.优选的,所述进位电路进一步用于响应于被加数信号、加数信号和进位信号得到存储于所述第二磁性存储器中的第三进位结果,所述方法进一步包括:

72.在t3时刻:

73.响应于第一电平的加数信号和进位信号或者加数信号和被加数信号,所述第三通路导通,所述第二磁性存储器存储第一逻辑数字。

74.本发明还公开了一种基于磁性存储器的全加器,包括n个依次连接逻辑计算单元,n为正整数;

75.每个逻辑计算单元包括加法电路和进位电路;

76.所述加法电路包括用于存储加数的第一磁性存储器、与所述第一磁性存储器连接的第一通路和第二通路;

77.所述第一通路用于响应于被加数信号进行加数与被加数的或运算,所述第二通路用于响应于加数信号和被加数信号完成加数与被加数的异或运算得到存储于所述第一磁性存储器中的第一异或结果;

78.所述第一通路进一步用于响应于进位信号进行进位数和所述第一异或结果的或运算,所述第二通路用于响应于所述进位信号和所述第一异或结果对应的信息完成所述进位数与所述第一异或结果的异或运算得到存储于所述第一磁性存储器中的全加运算结果;

79.所述进位电路包括第二磁性存储器、与所述第二磁性存储器连接的第三通路和第四通路;

80.所述第三通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第一进位结果,所述第四通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第二进位结果;

81.所述进位电路进一步用于响应于被加数信号、加数信号和进位信号得到存储于所述第二磁性存储器中的第三进位结果;

82.其中,第n个逻辑计算单元的第三进位结果作为进位数以输入第n 1个逻辑计算单元,1<=n<n。

83.本发明通过采用第一磁性存储器及与第一磁性存储器连接的第一通路和第二通路形成逻辑计算单元,其中,第一磁性存储器中存储着加数。通过第一通路响应于被加数信号对第一磁性存储器中存储的数据进行写处理,从而实现加数和被加数的或运算。进一步的,通过加数对应的加数信号和被加数信号可以对第一磁性存储器中的或运算结果进行进一步处理,重写第一磁性存储器中加数和被加数相同时的或运算结果为加数与被加数的异或运算结果,从而第一磁性存储器中最终得到的第一异或结果为加数和被加数的异或运算结果,使基于磁性存储器形成全加器成为可能,且本发明基于磁性存储器的逻辑计算单元无静态功耗,写入速度快。

附图说明

84.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

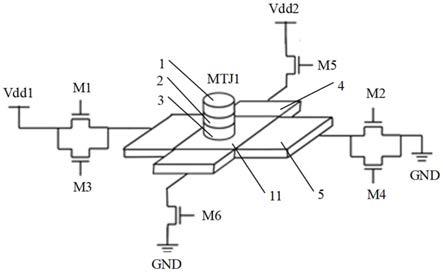

85.图1示出本发明基于磁性存储器的逻辑计算单元的加法电路;

86.图2示出本发明基于磁性存储器的逻辑计算单元的进位电路。

具体实施方式

87.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

88.现有技术中,采用互补金属-氧化物-半导体(complementary metal-oxide-semiconductor,cmos)工艺设计的全加器存在静态功耗日益加剧、数据搬移的功耗大以及所需带宽大的缺点。本技术发明人发现新型的mram(磁性随机存储器)可以实现非易失性存储,解决静态功耗过大的问题,且存算一体化结构有望解决传统冯诺依曼架构的带宽瓶颈。

89.在磁性(随机)存储器(mram)的发展历程中,主要经历了三代写入方式。第一代mram采用磁场实现数据写入,但所需电流较高,而且无法随着磁隧道结尺寸的缩小而降低,因此应用前景有限。第二代mram采用电流诱导自旋转移矩(spin transfer torque,stt)实现数据写入,解决了上述磁场写入方式所存在的弊端,但stt-mram的写入过程需要经历孵化延迟(incubation delay),严重制约写入速度,而且,写入电流与读取电流均直接经过磁隧道结,极易引起读取干扰(read disturb)和势垒击穿(barrier breakdown)等问题。第三代mram采用自旋轨道矩(spin orbit torque,sot)写入技术,可解决stt-mram中存在的问题。sot-mtj不易击穿,可靠性高,且读写路径分离,可独立优化。尤其是,对于目前普遍采用的具有垂直磁各向异性(perpendicular magnetic anisotropy,pma)的磁隧道结而言,sot-mram的写入速度有望达到亚纳秒级。

90.为了解决以上现有技术中的问题,本发明基于mram设计形成基于磁性存储器的逻辑计算单元。这种基于磁性存储器的逻辑计算单元基于sot-mtj设计,这种sot-mtj无需外加磁场,且写入状态仅由写入路径决定,即单向写入电流,且写入的数据可统一被擦除。针对这一性质设计的全加器,具有低功耗,写入速度快,读写路径完全分离,内部数据可擦除的优势。

91.基于此,根据本发明的一个方面,本实施例公开了一种基于磁性存储器的逻辑计算单元。其中,逻辑计算单元包括加法电路。

92.所述加法电路包括用于存储加数b的第一磁性存储器、与所述第一磁性存储器连接的第一通路和第二通路。

93.其中,所述第一通路用于响应于被加数信号进行加数b与被加数a的或运算,所述第二通路用于响应于加数信号和被加数信号完成加数b与被加数a的异或运算得到存储于所述第一磁性存储器中的第一异或结果。

94.本发明通过采用第一磁性存储器及与第一磁性存储器连接的第一通路和第二通路形成逻辑计算单元,其中,第一磁性存储器中存储着加数b。通过第一通路响应于被加数信号对第一磁性存储器中存储的数据进行写处理,从而实现加数b和被加数a的或运算。进一步的,通过加数b对应的加数信号和被加数信号可以对第一磁性存储器中的或运算结果进行进一步处理,重写第一磁性存储器中加数b和被加数a相同时的或运算结果为加数b与被加数a的异或运算结果,从而第一磁性存储器中最终得到的第一异或结果为加数b和被加数a的异或运算结果,使基于磁性存储器形成全加器成为可能,且本发明基于磁性存储器的逻辑计算单元无静态功耗,写入速度快。

95.在优选的实施方式中,当所述被加数信号为第一电平时,所述第一通路导通,所述第一磁性存储器存储第一逻辑数字。当所述加数信号和被加数信号为第一电平时,所述第二通路导通,所述第一磁性存储器存储第二逻辑数字。

96.具体的,本实施例中,以第一电平为高电平,其对应的第一逻辑数字为“1”,第二电平为低电平,其对应的第二逻辑数字为“0”为例来对本发明进行说明。当被加数a为1,被加

数信号为高电平时,第一通路导通,第一磁性存储器中存储的数字变为第一逻辑数字“1”,即当被加数a为1时,无论加数b是1还是0,第一磁性存储器中的数字变为1,实现加数b和被加数a的或运算。进一步的,当加数信号和被加数信号均为高电平,即加数b和被加数a均为1时,第二通路导通,第一磁性存储器中存储的数字变为第二逻辑数据“0”,即在或运算中加数b和被加数a均为1的情况下,对第一磁性存储器中的数字进行重写,实现加数b和被加数a的异或运算。

97.在优选的实施方式中,如图1所示,所述第一磁性存储器包括第一重金属层11和设于所述第一重金属层11上的第一磁隧道结mtj1。所述第一重金属层11包括第一输入方向5的第一端和第二端以及第二输入方向4的第三端和第四端,当通过第一输入方向5向所述第一重金属层11输入电流,所述第一磁隧道结mtj1的阻态为第一逻辑数字对应的第一阻态,当通过第二输入方向4向所述第一重金属层11输入电流,所述第一磁隧道结mtj1的阻态为第二逻辑数字对应的第二阻态。

98.其中,第一磁隧道结mtj1可包括从上向下依次设置的固定层1、势垒层2和自由层3。其中,固定层1可为铁磁金属层,势垒层2可为氧化物层,自由层3可为铁磁金属层。第一磁隧道结mtj1优选的选用椭圆柱形(椭圆的长宽比可以是任意值),并且椭圆的长轴与第一输入方向5和第二输入方向4均不重合或不平行,从而,可以实现通过第一输入方向5向所述第一重金属层11输入电流,所述第一磁隧道结mtj1的阻态为第一逻辑数字对应的第一阻态,通过第二输入方向4向所述第一重金属层11输入电流,所述第一磁隧道结mtj1的阻态为第二逻辑数字对应的第二阻态。

99.其中,优选的,第一输入方向5和第二输入方向4为正交的两个方向。作为优选的实施方式,本实施例中,第一重金属层11为长方形,第一输入方向5为沿长方形的长度方向,第二输入方向4为沿长方形的宽度方向。在其他实施方式中,第一输入方向5也可以是沿长方形的宽度方向,则第二输入方向4为沿长方形的长度方向。其中,第一重金属层11可以采用重金属条状薄膜或反铁磁条状薄膜等薄膜。第一重金属层11的面积大于第一磁隧道结mtj1,从而第一磁隧道结mtj1的底面形状可完全内嵌于重金属条状薄膜的顶面形状之中。

100.需要说明的是,第一阻态和第二阻态可分别对应于不同的逻辑数字,例如,本实施例中,第一阻态为低阻态,第二阻态为高阻态,第一阻态对应第一逻辑数字“1”,第二阻态对应第二逻辑数字“0”。在其他实施方式中,第一阻态为也可为高阻态,则第二阻态为低阻态,第一阻态可对应第一逻辑数字“0”,则第二阻态对应第二逻辑数字“1”。

101.在优选的实施方式中,加法电路可通过以下电路结构实现。再次参见图1,所述第一通路包括第一开关元件m1和第二开关元件m2。所述第一开关元件m1的控制端用于接收所述被加数信号,第一端与第一电源端vdd1连接,第二端与所述第一磁性存储器的第一端连接。所述第二开关元件m2的控制端用于接收所述被加数信号,第一端与接地端gnd连接,第二端与所述第一磁性存储器的第二端连接。

102.所述第二通路包括第三开关元件m3和第四开关元件m4。所述第三开关元件m3的控制端用于接收所述被加数信号,第一端与第二电源端vdd2连接,第二端与所述第一磁性存储器的第三端连接。所述第四开关元件m4的控制端用于接收所述加数信号,第一端与接地端gnd连接,第二端与所述第一磁性存储器的第四端连接。或者,所述第三开关元件m3的控制端用于接收所述加数信号,第一端与第二电源端vdd2连接,第二端与所述第一磁性存储

器的第三端连接。所述第四开关元件m4的控制端用于接收所述被加数信号,第一端与接地端gnd连接,第二端与所述第一磁性存储器的第四端连接。

103.具体的,本实施例以第一开关元件m1~第四开关元件m4为nmos晶体管为例进行说明。在t1时刻,当被加数信号为高电平时,第一开关元件m1和第二开关元件m2响应于高电平的被加数信号而导通,从而第一通路导通,在第一电源端vdd1的作用下,自由层3的磁矩方向与固定层1的磁矩方向相同,第一磁性存储器的阻态变为低阻态,从而使第一磁性存储器存储的逻辑数字变为“1”。而当被加数信号为低电平时,第一通路不导通,第一磁性存储器中仍存储加数b。

104.此时,当(加数b,被加数a)为(1,0)、(1,1)、(0,0)和(0,1)时,第一磁性存储器中得到的或运算结果分别为1,1,0,1。而在加数b和被加数a的异或运算中,当(加数b,被加数a)为(1,1)时,加数b和被加数a的异或运算结果应为0。为了实现异或运算,在t2时刻,当被加数信号和加数信号均为高电平时,第三开关元件m3和第四开关元件m4响应于高电平的进位信号而导通,从而第二通路导通。在第二电源端vdd2的作用下,第一磁性存储器自由层3的磁矩方向与固定层1的磁矩方向相反,从而使第一磁性存储器的阻态变为高阻态,使第一磁性存储器中存储的逻辑数字变为“0”。而当被加数信号和加数信号其中的至少一个为低电平时,第二通路不导通,不对或运算结果进行重写。从而在或运算中加数b和被加数a均为1情况下,对第一磁性存储器中的数字进行重写,通过第一通路和第二通路可以实现加数b和被加数a的异或运算。

105.在全加运算过程中,需要计算a

⊕

b

⊕

ci其中,a被加数a,b加数b,ci为进位数ci,通过第一异或结果的运算过程可以实现a

⊕

b,得到第一异或结果。同样的,可针对第一异或结果和进位数ci重复一次异或运算过程,从而实现a

⊕

b

⊕

ci得到全加运算结果。

106.在优选的实施方式中,所述第一通路进一步用于响应于进位信号进行进位数ci和所述第一异或结果的或运算,所述第二通路用于响应于所述进位信号和所述第一异或结果对应的信息完成所述进位数ci与所述第一异或结果的异或运算得到存储于所述第一磁性存储器中的全加运算结果。

107.在优选的实施方式中,当所述进位信号为第一电平时,所述第一通路导通,所述第一磁性存储器存储第一逻辑数字。当所述进位信号和第一异或结果对应的信号为第一电平时,所述第二通路导通,所述第一磁性存储器存储第二逻辑数字。

108.具体的,本实施例中,以第一电平为高电平,其对应的第一逻辑数字为“1”,第二电平为低电平,其对应的第二逻辑数字为“0”为例来对本发明进行说明。当进位数ci为1,进位信号为高电平时,第一通路导通,第一磁性存储器中存储的数字变为第一逻辑数字“1”,即当进位数ci为1时,无论加数b是1还是0,第一磁性存储器中的数字变为1,实现进位数ci和第一异或结果的或运算。进一步的,当进位信号和第一异或结果对应的信号均为高电平,即进位数ci和第一异或结果均为1时,第二通路导通,第一磁性存储器中存储的数字变为第二逻辑数据“0”,即在或运算中进位数ci和第一异或结果均为1的情况下,对第一磁性存储器中的数字进行重写,实现进位数ci和第一异或结果的异或运算,得到a

⊕

b

⊕

ci的全加运算结果。

109.在优选的实施方式中,加法电路可通过以下电路结构实现。再次参见图1,所述第一通路进一步包括第五开关元件m5和第六开关元件m6。其中,所述第五开关元件m5的控制

端用于接收所述进位信号,第一端与第一电源端vdd1和所述第一开关元件m1的第一端分别连接,第二端与所述第一磁性存储器的第一端和所述第一开关元件m1的第二端分别连接。所述第六开关元件m6的控制端用于接收所述进位信号,第一端与接地端gnd和所述第二开关元件m2的第一端分别连接,第二端与所述第一磁性存储器的第二端和所述第二开关元件m2的第二端分别连接。

110.具体的,以第五开关元件m5和第六开关元件m6为nmos晶体管为例进行说明。在t3时刻,当进位信号为高电平时,第五开关元件m5和第六开关元件m6响应于高电平的进位信号而导通,从而第一通路导通,在第一电源端vdd1的作用下,自由层3的磁矩方向与固定层1的磁矩方向相同,第一磁性存储器的阻态变为低阻态,从而使第一磁性存储器存储的逻辑数字变为“1”。而当进位信号为低电平时,第一通路不导通,第一磁性存储器中仍存储第一异或结果。

111.当进位数ci(第一异或结果)为(1,0)、(1,1)、(0,0)和(0,1)时,第一磁性存储器中得到的或运算结果分别为1,1,0,1。而在进位数ci和第一异或结果的异或运算中,当进位数ci(第一异或结果)为(1,1)时,进位数ci,第一异或结果的异或运算结果应为0。为了实现异或运算,在t4时刻,当进位信号和第一异或结果对应的信号均为高电平时,第三开关元件m3和第四开关元件m4响应于高电平的进位信号而导通,从而第二通路导通。在第二电源端vdd2的作用下,第一磁性存储器自由层3的磁矩方向与固定层1的磁矩方向相反,从而使第一磁性存储器的阻态变为高阻态,使第一磁性存储器中存储的逻辑数字变为“0”。而当被进位信号和第一异或结果对应的信号其中的至少一个为低电平时,第二通路不导通,不对或运算结果进行重写。从而在或运算中进位数ci和第一异或结果均为1情况下,对第一磁性存储器中的数字进行重写,通过第一通路和第二通路可以实现进位数ci和第一异或结果的异或运算。

112.在优选的实施方式中,逻辑计算单元还包括进位电路。所述进位电路包括第二磁性存储器、与所述第二磁性存储器连接的第三通路和第四通路。所述第三通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第一进位结果,所述第四通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第二进位结果。

113.在优选的实施方式中,当所述被加数信号和进位信号为第一电平时,所述第三通路导通,所述第二磁性存储器存储第一逻辑数字。当所述进位信号或被加数信号为第二电平时,所述第四通路导通,所述第二磁性存储器存储第二逻辑数字。

114.具体的,本实施例中,以第一电平为高电平,其对应的第一逻辑数字为“1”,第二电平为低电平,其对应的第二逻辑数字为“0”为例来对本发明进行说明。当被加数a为1,即被加数信号为高电平,并且进位数ci为1,即进位信号为高电平时,第三通路导通,第二磁性存储器中存储的数字变为第一逻辑数字“1”,即当被加数a为1且进位数ci为1时,第二磁性存储器中的数字变为1得到第一进位结果,表示当被加数a和进位数ci均为1时,全加运算后的进位数ci一定是为1的,即必然存在进位。而当进位信号和被加数信号中的至少一个为低电平,第三通路不导通,即进位数ci和被加数a中至少一个为0时,不确定全加运算后是否必然存在进位,第四通路导通,第二磁性存储器中存储的数字变为第二逻辑数据“0”,即在进位数ci和被加数a中至少一个为0的情况下,对第二磁性存储器中的数字进行重写得到第二进位结果,将不必然存在进位的情况均预置为0。

115.其中,优选的,如图2所示,所述第二磁性存储器包括第二重金属层21和设于所述第二重金属层21上的第二磁隧道结mtj2。所述第二重金属层21包括第三输入方向6的第五端和第六端以及第四输入方向7的第七端和第八端,当通过第三输入方向6向所述第二重金属层21输入电流,所述第二磁隧道结mtj2的阻态为第一阻态,当通过第四输入方向7向所述第二重金属层21输入电流,所述第二磁隧道结mtj2的阻态为第二阻态。

116.其中,第二磁隧道结mtj2可包括从上向下依次设置的固定层1、势垒层2和自由层3。其中,固定层1可为铁磁金属层,势垒层2可为氧化物层,自由层3可为铁磁金属层。第二磁隧道结mtj2优选的选用椭圆柱形(椭圆的长宽比可以是任意值),并且椭圆的长轴与第一输入方向5和第二输入方向4均不重合或不平行,从而,可以实现通过第一输入方向5向所述第二重金属层21输入电流,所述第二磁隧道结mtj2的阻态为第一逻辑数字对应的第一阻态,通过第二输入方向4向所述第二重金属层21输入电流,所述第二磁隧道结mtj2的阻态为第二逻辑数字对应的第二阻态。

117.其中,优选的,第一输入方向5和第二输入方向4为正交的两个方向。作为优选的实施方式,本实施例中,第二重金属层21为长方形,第一输入方向5为沿长方形的长度方向,第二输入方向4为沿长方形的宽度方向。在其他实施方式中,第一输入方向5也可以是沿长方形的宽度方向,则第二输入方向4为沿长方形的长度方向。其中,第二重金属层21可以采用重金属条状薄膜或反铁磁条状薄膜等薄膜。第二重金属层21的面积大于第二磁隧道结mtj2,从而第二磁隧道结mtj2的底面形状可完全内嵌于重金属条状薄膜的顶面形状之中。

118.需要说明的是,第一阻态和第二阻态可分别对应于不同的逻辑数字,例如,本实施例中,第一阻态为低阻态,第二阻态为高阻态,第一阻态对应第一逻辑数字“1”,第二阻态对应第二逻辑数字“0”。在其他实施方式中,第一阻态为也可为高阻态,则第二阻态为低阻态,第一阻态可对应第一逻辑数字“0”,则第二阻态对应第二逻辑数字“1”。

119.在优选的实施方式中,加法电路可通过以下电路结构实现。再次参见图2,所述第三通路包括第七开关元件m7和第八开关元件m8。所述第七开关元件m7的控制端用于接收所述被加数信号,第一端与第三电源端vdd3连接,第二端与所述第二磁性存储器的第五端连接,所述第八开关元件m8的控制端用于接收所述进位信号,第一端与接地端gnd连接,第二端与所述第二磁性存储器的第六端连接。或者,所述第七开关元件m7的控制端用于接收所述进位信号,第一端与第三电源端vdd3连接,第二端与所述第二磁性存储器的第五端连接,所述第八开关元件m8的控制端用于接收所述被加数信号,第一端与接地端gnd连接,第二端与所述第二磁性存储器的第六端连接。

120.所述第四通路包括第九开关元件m9和第十开关元件m10。所述第九开关元件m9的控制端用于接收所述被加数信号,第一端与第四电源端vdd4和所述第十开关元件m10的第一端分别连接,第二端与所述第二磁性存储器的第七端和所述第十开关元件m10的第二端分别连接,所述第十开关元件m10的控制端用于接收所述进位信号,所述第二磁性存储器的第八端与接地端gnd连接。或者,所述第九开关元件m9的控制端用于接收所述被加数信号,第一端与接地端gnd和所述第十开关元件m10的第一端分别连接,第二端与所述第二磁性存储器的第七端和所述第十开关元件m10的第二端分别连接,所述第十开关元件m10的控制端用于接收所述进位信号,所述第二磁性存储器的第八端与第四电源端vdd4连接。

121.具体的,本实施例以第七开关元件m7和第八开关元件m8为nmos晶体管,第九开关

元件m9和第十开关元件m10为pmos晶体管为例进行说明。在t1时刻,当进位信号和被加数信号为高电平时,第七开关元件m7和第八开关元件m8响应于高电平的进位信号和被加数信号而导通,从而第三通路导通,在第三电源端vdd3的作用下,自由层3的磁矩方向与固定层1的磁矩方向相同,第一磁性存储器的阻态变为低阻态,从而使第二磁性存储器存储的逻辑数字变为“1”。而当进位信号和被加数信号中的至少一个为低电平时,第三通路不导通,不对第二磁性存储器中的数字进行写入。

122.在t2时刻,当进位数ci和被加数a中的至少一个为0,即进位信号和被加数信号中的至少一个为低电平时,第九开关元件m9和/或第十开关元件m10分别响应于低电平的被加数信号和/或进位信号而导通,从而第四通路导通,在第四电源端vdd4的作用下,自由层3的磁矩方向与固定层1的磁矩方向相反,第二磁性存储器的阻态变为高阻态,从而使第二磁性存储器存储的逻辑数字变为“0”。即在进位数ci和被加数a中至少一个为0的情况下,对第二磁性存储器中的数字进行重写得到第二进位结果,将不必然存在进位的情况均预置为0。

123.在优选的实施方式中,所述进位电路进一步用于响应于被加数信号、加数信号和进位信号得到存储于所述第二磁性存储器中的第三进位结果。其中,作为优选的实施方式,当所述加数信号和进位信号为第一电平或者所述加数信号和被加数信号为第一电平时,所述第三通路导通,所述第二磁性存储器存储第一逻辑数字。

124.具体的,本实施例中,以第一电平为高电平,其对应的第一逻辑数字为“1”,第二电平为低电平,其对应的第二逻辑数字为“0”为例来对本发明进行说明。在t2时刻,可能存在由于被加数a和进位数ci的其中一个为1,一个为0而使第二磁性存储器的数字重写为0的情况。但是,此时,若加数b为1,则全加运算后会存在进位。为了保证进位运算的准确性,使第三通路在所述加数信号和进位信号为第一电平或者所述加数信号和被加数信号为第一电平时导通,从而使所述第二磁性存储器存储的数字变为第一逻辑数字。

125.在优选的实施方式中,进位电路可通过以下电路结构实现。再次参见图2,所述第三通路包括第十一开关元件m11、第十二开关元件m12和第十三开关元件m13。所述第十一开关元件m11的控制端用于接收所述加数信号,第一端与第五电源端vdd5连接,第二端与所述第二磁性存储器的第五端连接,所述第十二开关元件m12的控制端用于接收所述被加数信号,第一端与接地端gnd连接,第二端与所述第二磁性存储器的第六端连接,所述第十三开关元件m13的控制端用于接收所述进位信号,第一端与接地端gnd连接,第二端与所述第二磁性存储器的第六端连接。

126.在t3时刻,当加数b和进位数ci均为1或者被加数a与加数b均为1,即进位信号和被加数信号均为高电平或者加数信号和被加数信号均为高电平时,第十一开关元件m11和第十二开关元件m12响应于高电平的加数信号和被加数信号而导通,从而第三通路导通,在第五电源端vdd5的作用下,自由层3的磁矩方向与固定层1的磁矩方向相同,第二磁性存储器的阻态变为低阻态,从而使第二磁性存储器存储的逻辑数字变为“1”。或者,十一开关元件b和第十三开关元件m13响应于高电平的加数信号和进位信号而导通,从而第三通路导通,在第五电源端vdd5的作用下,自由层3的磁矩方向与固定层1的磁矩方向相同,第二磁性存储器的阻态变为低阻态,从而使第二磁性存储器存储的逻辑数字变为“1”。从而,可使第三通路在所述加数信号和进位信号为第一电平或者所述加数信号和被加数信号为第一电平时导通,从而使所述第二磁性存储器存储的数字变为第一逻辑数字。

127.在优选的实施方式中,所述第四通路进一步包括第十四开关元件m14和第十五开关元件m15,其中,第十四开关元件m14的控制端用于接收所述被加数信号,第一端与所述第二重金属层21的第八端连接,第二端接地;第十五开关元件m15的控制端用于接收所述进位信号,第一端与所述第二重金属层21的第八端连接,第二端接地。该优选的实施方式中,通过在第四通路上进一步设置第十四开关元件m14和第十五开关元件m15,从而可防止电流串扰。具体的,以第一电平为高电平,第二电平为低电平,第十四开关元件m14和第十五开关元件m15为pmos晶体管为例进行说明。在t2时刻,被加数信号和进位信号分别输入第九开关元件m9和第十开关元件m10的同时,被加数信号和进位信号分别输入第十四开关元件m14和第十五开关元件m15。则同样的,第九开关元件m9和第十四开关元件m14响应于低电平的被加数信号而导通,第十开关元件m10和第十五开关元件m15响应于低电平的进位信号而导通。从而,当被加数信号或进位信号为低电平时,第四通路导通,在第四电源端vdd4的作用下,自由层3的磁矩方向与固定层1的磁矩方向相反,第二磁性存储器的阻态变为高阻态,从而使第二磁性存储器存储的逻辑数字变为“0”。即在进位数ci和被加数a中至少一个为0的情况下,对第二磁性存储器中的数字进行重写得到第二进位结果,将不必然存在进位的情况均预置为0。

128.需要说明的是,第一磁性存储器和第二磁性存储器中存储的数字可以通过读取电路读取第一磁隧道结mtj1和第二磁隧道结mtj2的阻态,通过对第一磁隧道结mtj1和第二磁隧道结mtj2的阻态进行分析,确定第一磁隧道结mtj1和第二磁隧道结mtj2中存储的数字。对于在t2~t4时刻输入加法电路和进位电路的加数信号、被加数信号和进位信号可以通过对t1时刻对应的各信号的延时得到,也可以通过其他电路结构重新输入各信号,本发明对此并不作限定。以上用于实现本发明的读取电路、信号延时和时序控制等技术为本领域的常规技术手段,本领域技术人员可根据需求灵活设置,在此不再赘述。

129.基于相同原理,本实施例还公开了一种基于磁性存储器的逻辑计算方法。所述逻辑计算单元包括加法电路,所述加法电路包括用于存储加数b的第一磁性存储器、与所述第一磁性存储器连接的第一通路和第二通路,所述第一通路用于响应于被加数信号进行加数b与被加数a的或运算,所述第二通路用于响应于加数信号和被加数信号完成加数b与被加数a的异或运算得到存储于所述第一磁性存储器中的第一异或结果,所述方法包括:

130.在t1时刻:

131.响应于第一电平的被加数信号,所述第一通路导通,所述第一磁性存储器存储第一逻辑数字;

132.在t2时刻:

133.响应于第一电平的加数信号和被加数信号,所述第二通路导通,所述第一磁性存储器存储第二逻辑数字。

134.在优选的实施方式中,所述第一通路进一步用于响应于进位信号进行进位数ci和所述第一异或结果的或运算,所述第二通路用于响应于所述进位信号和所述第一异或结果对应的信息完成所述进位数ci与所述第一异或结果的异或运算得到存储于所述第一磁性存储器中的全加运算结果,所述方法进一步包括:

135.在t3时刻:

136.响应于第一电平的进位信号,所述第一通路导通,所述第一磁性存储器存储第一

逻辑数字;

137.在t4时刻:

138.响应于第一电平的所述进位信号和第一异或结果对应的信号,所述第二通路导通,所述第一磁性存储器存储第二逻辑数字。

139.在优选的实施方式中,所述逻辑计算方法还包括进位电路,所述进位电路包括第二磁性存储器、与所述第二磁性存储器连接的第三通路和第四通路,所述第三通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第一进位结果,所述第四通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第二进位结果,所述方法进一步包括:

140.在t1时刻:

141.响应于第一电平的被加数信号和进位信号,所述第三通路导通,所述第二磁性存储器存储第一逻辑数字;

142.在t2时刻:

143.响应于第二电平的进位信号或被加数信号,所述第四通路导通,所述第二磁性存储器存储第二逻辑数字。

144.在优选的实施方式中,所述进位电路进一步用于响应于被加数信号、加数信号和进位信号得到存储于所述第二磁性存储器中的第三进位结果,所述方法进一步包括:

145.在t3时刻:

146.响应于第一电平的加数信号和进位信号或者加数信号和被加数信号,所述第三通路导通,所述第二磁性存储器存储第一逻辑数字。

147.由于该方法解决问题的原理与以上逻辑计算单元类似,因此本方法的实施可以参见逻辑计算单元的实施,在此不再赘述。

148.基于相同原理,本实施例还公开了一种基于磁性存储器的全加器。全加器包括n个依次连接逻辑计算单元,n为正整数。

149.其中,每个逻辑计算单元包括加法电路和进位电路。

150.所述加法电路包括用于存储加数b的第一磁性存储器、与所述第一磁性存储器连接的第一通路和第二通路。

151.所述第一通路用于响应于被加数信号进行加数b与被加数a的或运算,所述第二通路用于响应于加数信号和被加数信号完成加数b与被加数a的异或运算得到存储于所述第一磁性存储器中的第一异或结果。

152.所述第一通路进一步用于响应于进位信号进行进位数ci和所述第一异或结果的或运算,所述第二通路用于响应于所述进位信号和所述第一异或结果对应的信息完成所述进位数ci与所述第一异或结果的异或运算得到存储于所述第一磁性存储器中的全加运算结果。

153.所述进位电路包括第二磁性存储器、与所述第二磁性存储器连接的第三通路和第四通路。

154.所述第三通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第一进位结果,所述第四通路用于响应于被加数信号和进位信号得到存储于所述第二磁性存储器中的第二进位结果。

155.所述进位电路进一步用于响应于被加数信号、加数信号和进位信号得到存储于所述第二磁性存储器中的第三进位结果。

156.其中,第n个逻辑计算单元的第三进位结果作为进位数ci以输入第n 1个逻辑计算单元,1<=n<n。

157.由于该全加器解决问题的原理与以上逻辑计算单元类似,因此本全加器的实施可以参见逻辑计算单元的实施,在此不再赘述。

158.本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。尤其,对于系统实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

159.以上所述仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。