一种基于virtex

‑

5系列fpga和tlk2711的星用高速串行接口

技术领域

1.本发明涉及一种星用高速串行接口设计,特别是一种基于virtex

‑

5系列fpga和tlk2711的星用高速串行接口设计。

背景技术:

2.高分辨率对地观测卫星如果采用光纤角度传感的方式将卫星中的微小角振动信息精确检测出来,进而采用图像处理等手段完成图像修复,可以提高光学载荷的成像水平。但该类卫星的载荷数据率已经从早先“资源”系列卫星的几百兆比特每秒发展到目前的数个g比特每秒,卫星各分系统之间的数据接口类型包括同步接口和异步接口,接口电平的选择一般包括ttl电平、ecl电平、rs422电平、lvds电平以及vml电平等。其中ttl电平的抗干扰能力差,传输距离有限制;ecl接口直流功耗大;rs422接口受传输速率限制,仅可以达到10mbps;lvds接口受接口时钟频率限制,也仅能达到100mbps左右。通常卫星上高速传输选用的是多路并行的方案,但多个接口芯片的并联势必增加通信成本及电路尺寸、重量。

3.卫星用产品,要考虑空间辐射和单粒子的问题。在电源管理方案中常规电路处理方式是采用具备抗辐照和单粒子指标的线性稳压电源msk系列或lw系列,然而线性电源的特性决定了低压大电流的供电需求会损失大部分功率,在整体功耗大幅度上升的同时,还采用占据大面积的印制板空间或结构上增加冷板的方式用于散热,这对产品低功耗、小型化的设计是不利的。而宇航用的小型开关电源芯片可选择方案很少,并成本极高且有很大的禁运风险,很难实现电路产品化和成本节约。

技术实现要素:

4.本发明解决的问题是:克服现有技术的不足,提供了一种基于virtex

‑

5系列fpga和tlk2711的星用高速串行接口设计,这种电路设计方案广泛适用于低成本商业卫星,且传输速率快、可靠性高、功耗小。

5.本发明的技术解决方案是:一种基于virtex

‑

5系列fpga和tlk2711的星用高速串行接口电路,包括设置在一块印制板上的电源输入接口、角速率信号输入接口、温度模拟信号输入接口、pps输入接口,高速通信接口、can总线通信接口;所述印制板上集成a/d转换器、virtex

‑

5系列fpga、tlk2711、存储芯片以及供电电路;

6.所述fpga通过pps输入接口接收pps信息、通过can接口与相机下位机进行通信,通过a/d转换器连接温度模拟信号输入接口,通过角速率信号输入接口接收陀螺数据,通过tlk2711与上位机进行通信,存储芯片用于存储fpga加载配置信息;

7.所述供电电路将电源输入接口输入的电压转换成印制板上各芯片需要的不同电压,其中采用加抗闩锁保护的开关电源供电方式为fpga提供内核电压,采用线型电源供电方式为fpga其余接口、存储芯片以及tlk2711提供所需电压。

8.进一步的,采用抗闩锁保护电路将输入电压进行异常保护,为开关电源芯片tps54310pwp提供可靠的输入电压,由开关电源芯片tps54310pwp向fpga提供稳定的内核电

压。

9.进一步的,所述的抗闩锁保护电路在后级芯片发生电流异常增大的情况下切断电源并自动上电,以模拟上电重启,超过3次后不再自动上电,直到重新加电或软复位。

10.进一步的,采用线性稳压芯片msk5230为fpga其余接口、存储芯片以及tlk2711提供稳定的所需电压。

11.进一步的,所述供电电路采用磁珠隔离的方式减少差模干扰。

12.进一步的,所述的存储芯片采用xcf16pvog48c存储器,fpga采用master serial和jtag两种模式进行配置,xcf16pvog48c存储器中存储在线调试源程序,fpga利用jtag模式直接从所述存储器中加载在线调试源程序进行在线调试,fpga利用master serial模式降低传输干扰。

13.进一步的,采用温补差分晶振为所述fpga提供全局时钟。

14.进一步的,采用了高速信号抗干扰传输方法,实现全温下工作期间高速通讯的误码率为0;所述的高速信号抗干扰传输方法包括在高密度pcb布局的基础上,通过差分对等长设计和阻抗匹配、避免传输数据线的跨电源分割,选择双绞磁屏蔽电缆作为通讯电缆、电源输入接口首先通过lc电源滤波再输出电压,印制板上每个芯片的所有供电口均加入旁路电容,由晶振直接为tlk2711提供参考时钟,tlk2711布线中数字信号和模拟信号之间进行隔离,印制板布线时电连接器各通道内布线长度进行补偿,印制板选择tu872。

15.本发明串行接口电路,用于接收高分辨率对地观测卫星信号检测电路输出的原始脉冲信号。

16.进一步的,在印制板上设置rs422测试通信接口,fpga与tlk2711连接的2711高速接口设置地检电路进行测试评定;

17.fpga将处理好的陀螺原始数据同步发送给rs422测试通信接口和2711高速接口,由rs422测试通信接口将所述陀螺原始数据输出至通用测试设备;

18.地检电路通过2711高速接口接收所述陀螺原始数据并进行数据完整性性判断,将判断结果传给通用测试设备,由通用测试设备根据结果判断误码率,同时对接收的陀螺原始数据进行打包保存,数据包发送给专用上位机,专用上位机对数据包进行解析后转换成陀螺原始数据,将转换的陀螺原始数据与rs422测试通信接口输出的陀螺原始数据进行比对,完成串行接口电路的测试评定。

19.本发明与现有技术相比的有益效果在于:

20.(1)本发明在电源管理上采用了更贴合电路需求的设计,采用了工业级开关电源芯片与抗闩锁保护芯片结合的方式为功耗最大的1v供电方案供电,两者结合在保证可靠性的前提下解决了功耗问题;

21.(2)本发明在功能实现上,对比传统信号处理电路fpga dsp为核心的架构,仅以单fpga为数据采集和处理平台,再将处理的数据输出至tlk2711a芯片接口,而采用vml差分信号技术的tlk2711可以实现单路串行传输速率达到2.5gbps,实现了通信成本及电路尺寸、重量的大大降低。

22.(3)本发明在解决高速通信误码率上采用了差分对等长设计和阻抗匹配设计,解决了跨电源分割问题,在印制板板材和接插件及通讯电缆的选择上充分论证分析,使高速信号在抗干扰传输上表现优异。

23.(4)本发明在缺乏需求方专用联调设备的条件下,在设计中增加了通用测试接口与专用的数据一致性评测方案实现了微振动测量系统的功能和性能测试,完成了单板级测试评定。

附图说明

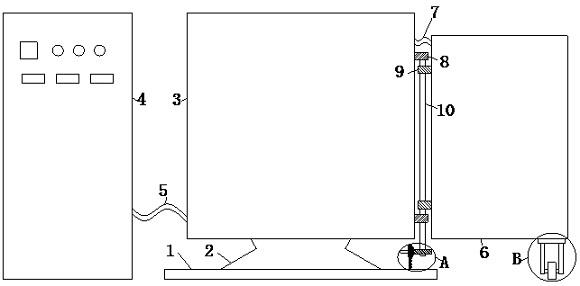

24.图1为本发明的功能结构示意图;

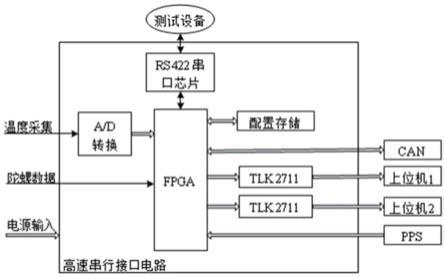

25.图2为本发明的基本构思框架示意图;

26.图3为开关电源及外围电路原理图;

27.图4为抗闩锁保护电路原理图;

28.图5为线性电源电路原理图;

29.图6为核心高速电路配置关系示意图;

30.图7为virtex

‑

5系列fpga配置管脚设计图;

31.图8为存储器外部配置管脚设计图;

32.图9为系统主晶振配置图;

33.图10为tlk2711内部原理图;

34.图11为tlk2711外部配置图;

35.图12为tlk2711通信时序图;

36.图13为数据帧的定义图;

37.图14为高速信号与反射信号波形对比示意图;

38.图15为不同粗糙度差入损耗对比图。

具体实施方式

39.下面结合附图及实例对本发明做详细说明。

40.本发明首先考虑的是核心接口芯片和数据处理器的选择。比对当前多种星用分系统通信接口,选用最符合应用要求的接口实现模式,匹配资源足够、功耗成本最低的原则选择fpga处理器及相应外部存储器。根据上述所选芯片类型确定fpga主时钟频率及晶振类型,确认设计电路所需的供电电平,根据不同供电电平需求和功耗最低原则选择电源管理方案。完成所需功能设计后对整体电路进行电磁兼容性设计,与需求方协商形成高速通信协议,编写fpga软件实现相应功能,之后设计可行的测试方案及相应测试设备,基本思路如图2所示。

41.本发明一种星用高速串行接口电路,用于完成接收高分辨率对地观测卫星信号检测电路输出的原始脉冲信号(代表光纤角度传感变量即陀螺数据,展现的是卫星镜头的微小角振动信息),通过高速串口向成像处理箱输出微小角振动和时间等信息;通过接收pps信息,进行时间处理;同时通过can接口与相机下位机进行时间校正、状态监控等功能。通过把上述各接口功能的实现,高分辨率对地观测卫星可以将卫星中的微小角振动信息精确检测出来,进而采用图像处理等手段完成图像修复,来提高光学载荷的成像水平。本发明以xilinx公司virtex

‑

5系列的fpga芯片为平台,以tlk2711为高速收发器,其中对外接口与相机下位机之间采用can2.0b总线通信,通信速率为500kbps,分为主备份通信;与成像处理单元采用高速通信接口完成通信,数据传输速率达到1.6gbps。设计方案特点为低功耗,电路

小型化,在低轨太空环境全温下可保证高速信号在工作期间误码率为0。按图1所示,本设计中按需求共有7个外部接口,还有4种不同的电源管理芯片,都要集成在110

×

110mm的印制板上,布局紧凑的同时还要处理好多种信号的干扰耦合问题、差分线等长以及阻抗连续匹配等需求,cs面以及ss面的高度也要受到限制,还要尽可能减少布板层数,降低成本

……

这些需求增加了电路的设计难度,如果设计的不合理就会影响高速信号的数据传输,无法使之全温下工作时间内零误码率为0。

42.(1)供电方案设计

43.本发明的核心fpga芯片xc5vlx50

‑

2ff324i和外部存储器xcf16pvog48c,以及高速接口芯片tlk2711共需要5种不同电平供电。针对不同的电源需求,主要采用两大类型的供电方案。

44.(a)开关电源供电方案

45.核心芯片xc5vlx50

‑

2ff324i的内核供电电压为1v,且功耗在1w左右。为了产品降低功耗,最佳供电方案就是选择开关电源,本技术采用的开关电源芯片tps54310pwp效率高达90%,输出电流最大可达到3a,工作温度在

‑

40℃~150℃,满足设计需求。如图3所示,为开关电源及外围电路原理图。但tps54310pwp外围反馈环路设计复杂,初测时按理论设计值输出电平不够稳定,输出电压纹波较大,本发明通过借助ti公司提供的电源方案仿真软件switchpro,优化设计参数完成该芯片的外围配置。

46.因为是卫星用产品,要考虑空间辐射和单粒子的问题。虽然开关电源芯片tps54310pwp可以满足空间环境温度的需求,但自身的cmos工艺让它容易受到单粒子影响。中电58所的抗闩锁保护芯片jsr71247l10可在后级芯片(位于抗闩锁保护电路之后的所有芯片)发生电流异常增大(模拟闩锁)的情况下切断电源并自动上电(模拟上电重启),超过3次后不再自动上电,直到重新加电或软复位,两者结合使用在保证可靠性的前提下解决了功耗问题。如图4所示,为抗闩锁保护电路原理图。

47.(b)线性电源供电方案

48.fpga与高速接口连接的bank使用2.5v电平,其它bank采用普通的3.3v lvttl电平标准,辅助电压vcca_aux也为3.3v;外部存储器xcf16pvog48c的供电电压为1.8v。这三种电平消耗掉功率较低,且对电压稳定度要求较高,尤其是tlk2711需要的2.5v电压,需要很高的供电稳定性,本技术采用的msk5230

‑

2.5h,外围电路如图5所示,输出电压变化:≤

±

1%;线性调整率:≤

±

0.5%;负载调整率:≤

±

1%,为国际领先水平,在做好滤波的情况下可成功保证tlk2711稳定传输工作。

49.对于电路设计中涉及的不同种类需要5v供电的芯片,采用磁珠隔离的方式来减少差模干扰。

50.(2)核心fpga以及2711接口设计

51.如图6所示,是核心高速电路配置关系示意图,设计时主要考虑的是器件的选型及核心芯片的功能配置。核心fpga选择的是选用的是xilinx公司的virtex

‑

5系列fpga,它的配置方式主要有master serial,spi,master select map,bpi,jtag,slave select map,slave serial等。其中模式的选择主要要考虑存储器的型号选定,因为选用了xcf16pvog48c存储器,因此不考虑spi和bpi配置模式。本设计方案使用的是master serial和jtag两种模式。初始方案选用master select map模式可以提供8bit或者16bit双向数据

总线接口,cclk时钟输出,主要的好处是支持共用数据总线实现多设备级联配置。因为本次研发不涉及多设备级联,无法体现该模式下的优势,而master serial模式的优势是线路成本低且抗干扰能力强。时钟频率比较低的情况下并行模式比串行模式传输速率快,但在高频时钟条件下,并行传输受到的干扰会特别严重,反而串行模式受到的影响较小,而设计方案主要是针对高速电路,因此采用了master serial模式。jtag模式在线调试源程序,在系统掉电之后,配置信息会丢失。采用这两种模式系统可以直接从存储器中直接加载程序,同时支持在线调试,灵活方便。图7是fpga配置管脚示意图,图8表示外部存储器管脚配置情况。

52.晶振采用的是温补差分晶振,温补晶振的优势是工作温度范围宽,频率温度稳定度很高,抗温度冲击能力强,可以在宇航环境下保证时钟稳定性,提高电路信号传输可靠性。由差分晶振为fpga提供全局时钟的设计,差分晶振相比于普通晶振,差分晶振具有低电平、低抖动、低功耗的特点,用于产品中能够从容精确地处理“双极”信号,轻易识别小信号,对外部的电磁干扰几乎是免疫的。而本方案选用的virtex

‑

5系列fpga共有32个时钟接口,其中就包含4对差分时钟输入接口,可以实现差分晶振作为主时钟的配置需求。如图9所示,为系统主晶振配置图。

53.本技术中使用的tlk2711作为高速传输链路中的核心器件,是一个支持串行接口速度为1.6gbps至2.7gbps的高速串行/解串器,可提供高达2.16gbps的数据带宽,主要完成数据的高速并串和串并转化功能。高速串行收发器分为发射器与接收器两大部分。发射器一端基于提供的参考时钟(txclk)锁存16bit的并行数据,内部使用8b/10b编码格式在内部变成20bit,编码后的20bit数据被以20倍参考时钟采用时分方式以差分串行传输出去。接收器部分执行对所输入的数据串/并转换,将所得的20bit的并行数据经过内部同步到恢复时钟(rxclk),时钟提取功能是作为物理层的接口设备实现的。然后再使用8b/10b解码格式解码20bit并行数据为16bit的原始数据。其内部原理图如图10所示。

54.在同类高速信号传输手段中,tlk2711接口采用串行传输方式,而传统的lvds并行数据接口采用时钟、门控、多路数据并行传输方式,两者在设计上有较大差别。tlk2711属于异步串口芯片,其内置有可靠的数据协议。传统的并行接口中使用的门控信号用来区分有效数据和无效数据,而2711的异步传输接口中无需使用门控信号。因为按照tlk2711推荐的协议,在不发送有效数据时,需发送k码,接收端检测到k码即可认为是无效数据。此外,lsm和msb信号提供k码指示功能,可以利用这两个信号在接收端恢复为同步信号,发送端按照数据协议生成k码后无需保留门控信号。如图11所示,为本设计中tlk2711的外部配置原理图。

55.tlk2711对时钟的要求非常高,时钟频率至少80mhz,且准确度优于1

×

10

‑5,时钟抖动(峰-峰值)优于40ps,因此设计时所使用参考时钟信号是由晶振直接提供的,不经过其他倍频或分频手段处理。

56.fpga采集光纤陀螺的脉冲信号,完成1ms周期计数,并通过内部ram进行存储,完成1.5秒的输出存储后(约15kb),通过tlk2711接口发送。fpga与控制系统的can总线通信通过sja1000接口芯片实现。fpga通过对sja1000的读写控制,接收控制系统的指令,完成can总线a/b主备份的切换,tlk2711数据发送的开启和关闭以及utc时间的校正等,并返回数据和状态字至控制系统。为保证提供给成像处理箱的数据是连续的,fpga需先进行大数据的存

储,然后发送。按照需求方的要求,每存储1.5秒的角振动数据后对外发送一帧数据,为保证数据发送的完整性,每发送一帧有效数据后发送511帧冗余数据。

57.其中高速接口tlk2711与fpga为并行数据接口,fpga输出16位并行数据和时钟txclk至tlk2711。该方案中tlk2711作为发送端,根据参考时钟txclk对16位并行数据进行锁存,而后在内部按照8b/10b编码将其转换为20位并行数据,并串转换后通过串行数据通道传送到接收端tlk2711。fpga与tlk2711的接口协议具体如下:

58.(a)tlk2711协议的控制字符

59.主要包括数据帧的帧头、帧尾以及同步字符三个部分。tlk2711是以16bit为一个基本的传输单位,因此每一个控制字符都定义成2个字节,分别由d码和k码组成。高8位和低8位编码方式是由控制信号tkmsb和tklsb决定的,具体协议控制字符定义如下表所示。如果控制信号tkmsb和tklsb均为低,则说明发送的数据是有效数据;如果控制信号tkmsb和tklsb均为高,则说明发送数据的是帧头或者帧尾;如果信号tkmsb为高,信号tklsb为低,则说明发送数据的是同步字符。tlk2711的通信时序图如图12所示。

[0060][0061]

(b)协议数据帧结构

[0062]

数据帧包括帧头(/sf/)、帧尾(/ef/)和数据单元(data)三部分组成,如图13所示。数据帧的帧长为1544字节,其中帧头和帧尾各占2个字节,数据单元则占1544个字节。传输时帧和帧之间发送32个同步字符/sp/保证传输链路的同步。其中:

[0063]

帧头:/k28.2/k27.7/;16进制为/5c/fb/,占用2bytes;

[0064]

帧尾:/k29.7/k30.7/;16进制为/fd/fe/,占用2bytes;

[0065]

同步码:助记符为/sp/;编码为/d5.6/k28.5/,16进制为/c5/bc/。

[0066]

其中,1544个数据单元包括微振动数据和utc时间等。一帧数据定义为图13所示的8个数据帧。fpga对工作时钟,tlk2711接口发送时钟和数据均进行了时序约束,满足接口芯片的时序要求。

[0067]

下表为fpga时钟和资源最终实现情况,经设计优化后资源占比仅57%,满足星用i级降额的设计需求。

[0068][0069]

(3)高速信号抗干扰传输技术

[0070]

tlk2711是高速的网络通信接口,最高速率可以达到2gbps以上,本项目使用速率为1.6gbps,在此通信速率下会带来极大的emc问题,当信号边沿时间小于4到6倍的走线传

输时延时,信号当作高速信号处理,当通信线路上出现阻抗不匹配,信号就会在阻抗不连续处发生反射,反射波回到接收端会二次反射。多次反射后传输线上信号达到稳定,加大通信误码率。如图14所示,为高速信号与反射信号波形对比示意图。为了高速信号的抗干扰设计实现全温下工作时间内零误码率,在设计过程中积累的注意事项如下:

[0071]

(a)注意差分对等长设计和阻抗匹配,同时考虑所有并行ttl信号等长和相互间的串扰;tlk2711可视为数字/模拟混合芯片,注意数字信号和模拟信号之间的隔离;差分信号对供电电源波动敏感,采用lc电源滤波、加入旁路电容等改善供电质量;设计电路与成像处理单元的高速信号连接电缆选择双绞磁屏蔽电缆,减少外界干扰对信号完整性的影响。各部分设计标准严格程度远超传统低速电路。

[0072]

(b)注意数据传输数据线的跨电源分割问题,尽量减少传输数据线上的过孔数量,走线需要考虑经过同一参考平面来保证该线路特征阻抗的连续性。电性件在设计之初未充分考虑该问题,全温下测试出现的情况是产品在常温和高温下通讯传输无异常,低温下2分钟左右出现误码率。

[0073]

(c)tlk2711对参考时钟的要求很高,时钟频率至少80mhz,准确度优于1

×

10

‑5,时钟抖动(峰-峰值)优于40ps,因此设计时所使用参考时钟信号是由晶振直接提供的。

[0074]

(d)电连接器选型为hsmk

‑

02l0系列,虽然可以满足高速信号通讯需求,提高传输信号抗干扰能力,但每个模块内的3,4通道比1,2通道长约2mm,pcb板布线时需要长度补偿。实验件设计之初未充分考虑这一差异,有一路通道未补偿,未补偿通道测试时全温下皆有误码率。

[0075]

(e)随着频率的升高,传输线横截面上的电流分布变得不均匀,开始趋近于导线表面的现象,称之为趋肤效应,此时表面粗糙度会对信号质量造成极大影响。材料的介质损耗通常不是一个常量,而是随频率、温度、湿度变化的函数。如图15和下表所示的不同板材的损耗对比可以看出,表面越光滑平坦,对应的差入损耗也越小,当平均表面粗糙度和趋肤深度相当时,材料的有效电阻值将明显增加,实际损耗比没有考虑导体粗糙度增加10%~50%。

[0076][0077]

表面粗糙度的最大因素为材料,不同的材料制作的板材表面粗糙度相差很大,但通常也意味着较高的价格,本次设计考虑到成本与可靠性的制约,最终选择了tu872。

[0078]

(4)单板级测试评定方案设计

[0079]

微振动测量系统其本质上为高精度、高采样率的光纤陀螺,基于需求方具体要求和现有技术基础,对微振动测量系统的技术指标进行分解,通过光纤陀螺的性能参数,侧面反映微振动测量系统的技术指标完成情况。但具体数据测试只能通过与需求方专用设备联调才能获得,采用can接口指令控制完成2711高速接口与相机下位机的对接,通过下行高速

数据帧,通过观察帧头、帧尾、utc时间验证数据是否完整来判断。但实际情况是需求方不可能给生产方提供这样的联调环境,只能在验收环节完成这一步,因此如何设计单板级的测试评定方案就成了本电路设计完成后的首要问题。

[0080]

经过多方论证和与需求方协商,最终形成如下测试评定方案:

[0081]

(a)在本设计中增加测试用rs422接口,fpga将处理好的数据同步发送给rs422接口和2711高速接口,通过通用的rs422接口完成对微振动系统的功能和性能测试。

[0082]

(b)设计2711接口的地检电路,地检电路具备接收功能,将从设计电路中得到的固定有序信号进行比对,判断帧头、帧尾、utc时间验证数据是否完整,将判断数据传给通用测试设备pc端,由软件判断误码率情况。

[0083]

(c)将2711接口得到的数据包传给需求方专用上位机,由需求方专用上位机解析后转换成的陀螺原始数与通用测试设备通过rs422接口得到的陀螺原始数进行对比,比对结果一致后判定该测试方法有效。

[0084]

本发明说明书中未作详细描述的内容属本领域技术人员的公知技术。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。