一种基于fpga的多张vpx板卡时间同步方法和装置

技术领域

1.本发明涉及通信领域,具体涉及一种基于fpga的多张vpx板卡时间同步方法和装置。

背景技术:

2.现有技术中,板卡时间信息来源于处理器,通过某些常见固定协议下发时间信息,时间信息和同步时钟传输过程中为单端传输,时间同步系统非全国产化设计,时间信息的精度普遍不高。现有技术具体存在以下缺点:处理器获取时间信息后再下发给fpga,会增加传输延时,降低时间信息的传输精度;板间时间信息和同步时钟的传输通常是通过每张板卡上的fpga的gpio直连实现的,是单端传输,抗干扰能力比较差;现有系统使用外国元器件完成系统设计,容易受限以及现有系统的时间信息精度不高,通常只有0.01秒。

技术实现要素:

3.本发明所要解决的技术问题是现有的vpx板卡处理器获取时间信息后再下发给fpga,会增加传输延时,降低时间信息的传输精度以及板卡间时间信息和同步时钟的传输通常是通过每张板卡上的fpga的gpio直连实现的,是单端传输,抗干扰能力比较差的问题,目的在于提供一种基于fpga的多张vpx板卡时间同步方法和装置,解决上述的问题。

4.本发明通过下述技术方案实现:

5.一种基于fpga的多张vpx板卡时间同步方法,包括以下步骤:

6.s1:采用主卡fpga芯片从以太网芯片中获取时间信息,并把时间信息上传到主卡处理器;在同一时间内,主卡fpga芯片进行同步计时,获得同步时钟;

7.s2:主卡fpga芯片将时间信息和同步时钟通过单端转差分芯片分别转换成差分时间信息和差分同步时钟,再将差分时间信息和差分同步时钟传输给从卡fpga芯片;

8.s3:从卡fpga芯片通过差分转单端芯片将差分时间信息和差分同步时钟分别转换成第二时间信息和第二同步时钟,再通过本地总线将第二时间信息和第二同步时钟上传给从卡处理器。

9.本发明工作原理:本发明主卡fpga芯片直接通过管理数据输入/输出接口mdio从以太网芯片ar8031中直接获取时间信息;时间信息和同步时钟通过主卡fpga芯片上的单端转差分芯片转换成差分信号,差分信号到达其余从卡fpga芯片后通过差分转单端芯片转换成单端信号供从卡fpga芯片使用。

10.进一步地,所述主卡fpga芯片数量为1;所述从卡fpga芯片数量为n,且n为大于或者等于2的整数。本发明的每张vpx板卡都可以选择充当主卡或是从卡,时间同步系统中只能有一张主卡,但是从卡可以有n张。

11.进一步地,步骤s1之前,还包括以太网芯片从网络中获取时间信息并将时间信息存储在以太网芯片的寄存器当中。

12.进一步地,步骤s1中,所述采用主卡fpga芯片从以太网芯片中获取时间信息,并把

时间信息上传到主卡处理器具体为:采用主卡fpga芯片通过秒脉冲信号和mdio接口从以太网芯片中获取时间信息,并且通过本地总线协议把时间信息上传到主卡处理器。

13.进一步地,所述主卡fpga芯片和从卡fpga芯片均为2v1000可编程门阵列。

14.进一步地,所述以太网芯片为ar8031芯片。

15.进一步地,所述主卡处理器和从卡处理器均为lsocam0201双核arm处理器。

16.一种基于fpga的多张vpx板卡时间同步装置,包括:一张主卡vpx板卡和n张从卡vpx板卡,n为大于或者等于2的整数;

17.所述主卡vpx板上设有包括主卡ar8031芯片、主卡fpga芯片、主卡arm处理器和单端转差分芯片;

18.所述从卡vpx板卡上设有包括从卡fpga芯片、从卡arm处理器和差分转单端芯片;

19.所述主卡ar8031芯片用于从网络中获取时间信息并将时间信息存储于主卡ar8031芯片的寄存器中;

20.所述主卡fpga芯片用于从主卡ar8031芯片的寄存器中获取时间信息,并且通过本地总线协议把时间信息上传到主卡arm处理器;所述主卡fpga芯片还用于同步计时,获得同步时钟;

21.所述单端转差分芯片用于将时间信息和同步时钟分别转换成差分时间信息和差分同步时钟,再将差分时间信息和差分同步时钟传输给差分转单端芯片;

22.所述差分转单端芯片用于将差分时间信息和差分同步时钟分别转换成第二时间信息和第二同步时钟;

23.所述从卡fpga芯片用于通过本地总线将第二时间信息和第二同步时钟上传给从卡arm处理器。

24.本发明与现有技术相比,具有如下的优点和有益效果:

25.1、本发明提供的一种基于fpga的多张vpx板卡时间同步方法和装置,主卡fpga芯片直接通过管理数据输入/输出接口mdio从以太网芯片ar8031中直接获取时间信息;时间信息和同步时钟通过主卡fpga芯片上的单端转差分芯片转换成差分信号,差分信号到达其余从卡fpga芯片后通过差分转单端芯片转换成单端信号供从卡fpga芯片使用。

26.2、本发明提供的一种基于fpga的多张vpx板卡时间同步方法和装置,系统由全国产化器件组成,时间信息的串行传输协议是自主设计的,能够做到传输参数可控。

27.3、本发明提供的一种基于fpga的多张vpx板卡时间同步方法和装置,时间信息和同步时钟为差分传输,抗干扰性强。

28.4、本发明提供的一种基于fpga的多张vpx板卡时间同步方法和装置,时间信息传输协议为串行传输,节约fpga可用端口。

附图说明

29.为了更清楚地说明本发明示例性实施方式的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。在附图中:

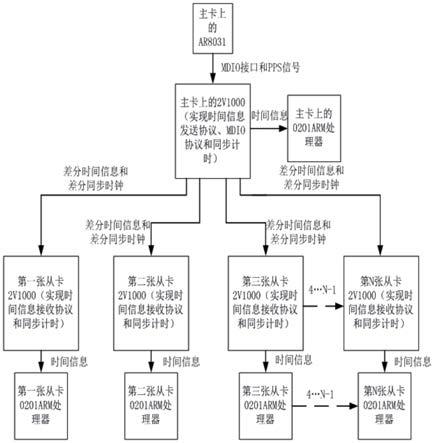

30.图1为本发明基于fpga的vpx板卡时间同步技术设计流程图。

具体实施方式

31.为使本发明的目的、技术方案和优点更加清楚明白,下面结合实施例和附图,对本发明作进一步的详细说明,本发明的示意性实施方式及其说明仅用于解释本发明,并不作为对本发明的限定。

32.实施例

33.如图1所示,一种基于fpga的多张vpx板卡时间同步方法,包括以下步骤:

34.s1:以太网芯片从网络中获取时间信息并将时间信息存储在以太网芯片的寄存器当中;采用主卡fpga芯片通过秒脉冲信号和mdio接口从以太网芯片中获取时间信息,并且通过本地总线协议把时间信息上传到主卡处理器;在同一时间内,主卡fpga芯片进行同步计时,获得同步时钟;

35.s2:主卡fpga芯片将时间信息和同步时钟通过单端转差分芯片分别转换成差分时间信息和差分同步时钟,再将差分时间信息和差分同步时钟传输给从卡fpga芯片;

36.s3:从卡fpga芯片通过差分转单端芯片将差分时间信息和差分同步时钟分别转换成第二时间信息和第二同步时钟,再通过本地总线将第二时间信息和第二同步时钟上传给从卡处理器。

37.所述主卡fpga芯片数量为1;所述从卡fpga芯片数量为n,且n为大于或者等于2的整数。

38.在本实施例中,主卡fpga芯片和从卡fpga芯片均采用国微的2v1000可编程门阵列。以太网芯片采用中电科三十二所的ar8031芯片。主卡处理器和从卡处理器均采用西安微电子研究所的lsocam0201双核arm处理器。

39.一种基于fpga的多张vpx板卡时间同步装置,包括:一张主卡vpx板卡和n张从卡vpx板卡,n为大于或者等于2的整数;

40.所述主卡vpx板上设有包括主卡ar8031芯片、主卡fpga芯片、主卡arm处理器和单端转差分芯片;

41.所述从卡vpx板卡上设有包括从卡fpga芯片、从卡arm处理器和差分转单端芯片;

42.所述主卡ar8031芯片用于从网络中获取时间信息并将时间信息存储于主卡ar8031芯片的寄存器中;

43.所述主卡fpga芯片用于从主卡ar8031芯片的寄存器中获取时间信息,并且通过本地总线协议把时间信息上传到主卡arm处理器;所述主卡fpga芯片还用于同步计时,获得同步时钟;

44.所述单端转差分芯片用于将时间信息和同步时钟分别转换成差分时间信息和差分同步时钟,再将差分时间信息和差分同步时钟传输给差分转单端芯片;

45.所述差分转单端芯片用于将差分时间信息和差分同步时钟分别转换成第二时间信息和第二同步时钟;

46.所述从卡fpga芯片用于通过本地总线将第二时间信息和第二同步时钟上传给从卡arm处理器。

47.本发明定义的系统工作流程:主卡上的ar8031从网络中获取时间信息,此时间信息精确到ns级,存储在ar8031的寄存器当中,主卡上的2v1000可编程门阵列通过秒脉冲信号(以下称为pps)和mdio接口从ar8031中获取时间信息,并且通过本地总线协议把时间信

息上传到主卡arm处理器,在同一时间内,主卡上的2v1000可编程门阵列通过时间信息发送协议把时间信息发给其余从卡并且在本地进行同步计时(计时精度10ns,下同),时间信息和同步时钟通过主卡上的gpio输出,经过单端转差分芯片转换成差分传输,提高传输的抗干扰性,从卡收到差分信号后,经过差分转单端芯片转换成单端信号,从卡上的2v1000可编程门阵列接收到单端信号后,通过时间信息接收协议的解析,得到时间信息并使用同步时钟进行同步计时,在同一时间,从卡通过本地总线把时间信息上传给处理器使用。本发明中的主卡只有一张,从卡可以有n张,并且每张卡既可以当主卡又能当从卡。设计流程图如图1所示。

48.以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。