1.本实用新型涉及构建记忆元件的技术领域,主要涉及一种记忆元件通用模拟器。

背景技术:

2.1971年,蔡少棠团队通过研究电流i、电压v、电荷q和磁通量之间的关系来预测除电阻、电容、电感之外还存在的第四种基本电路元件,该第四种基本电路元件称为忆阻器,忆阻器用于表示电荷q和磁通量的数学关系。

3.2008年,惠普实验室成功制作出具有忆阻器特性的纳米级固态元件。从此确定了忆阻器作为第四种基本电路元件的历史地位。忆阻器由于其独特的记忆特性和纳米结构,使得忆阻器在非易失性存储、人工智能领域(包括类脑运算和神经网络)、混沌电路和逻辑芯片等多个领域具有广阔的应用前景。2009年,蔡少棠团队根据忆阻器的概念进一步提出了忆容器和忆感器的概念,这两者的特性都和忆阻器一样表现出了记忆功能。因此,忆阻器、忆容器和忆感器又被统称为记忆元件。但相对于忆阻器而言,忆容器和忆感器更是作为新型广义储能元件存在。不同于忆阻器,在一些低功耗集成电路中,忆容器和忆感器在工作时不需要消耗能量。因此有理由相信忆容器和忆感器能在电子电路领域有更多的应用。

4.然而由于开发成本以及纳米级器件制作在技术上的困难,商用级的记忆元件在短时间内是不可能被攻克实现的。因此,为了探究这三种记忆元件后续应用,研究其仿真模型和等效电路模拟器是非常有必要的。

5.而在专利号为:cn201610580825,专利名称为:一种通用记忆器件模拟器的专利文献(下述专利文献a)中公开了使用五个电流反馈运算放大器和一个场效应管来分别模拟忆阻器、忆容器、忆感器使用的方法,由于专利文献a中依赖工作于线性区域的场效应管,才能实现模拟忆阻器、忆容器、忆感器的记忆特性,因此,根据专利文献a的方法所模拟出的忆阻器、忆容器、忆感器仅能用于频率为0.8khz的电路中,而现有电路的频率远远超出了0.8khz,可见,专利文献a中得到的通用记忆器件模拟器并不能符合实际的电路工作需求,无法真正地使用在常规电路中,因而无法将专利文献a中的通用记忆器件模拟器投入常规的生产,无法真正地将模拟出的忆阻器、忆容器、忆感器投入到工业生产当中。

技术实现要素:

6.本实用新型的目的在于提供一种记忆元件通用模拟器的硬件结构,该硬件结构在软件工程师对其中的控制器进行软件编程后,用于模拟忆阻器、忆容器和忆感器并能够将模拟出的忆阻器、忆容器和忆感器灵活地使用在频率为100khz量级的电路中,便于模拟出的忆阻器、忆容器和忆感器投入工业生产当中。

7.为此,提供一种记忆元件通用模拟器,包括控制器、四个用于高频放大信号的电流反馈运算放大芯片、乘法器、电源、积分器、多个电阻、电容、电感,四个电流反馈运算放大器分别标号为u1、u2、u3、u4,任意一个电流反馈运算放大芯片均具有x端、y端、p端、z端,电流反馈运算放大芯片u1的y端分出两条支路,其中一条支路连接至电流反馈运算放大芯片u3的z

端,并以另一条支路作为输入端a,以电流反馈运算放大芯片u1的x端作为第一变换记忆接口t1的正端,以电流反馈运算放大芯片u2的x端作为第一变换记忆接口t1的负端,第一变换记忆接口t1的正端和负端串联电阻或电感,电流反馈运算放大芯片u2的y端与分出两条支路,其中一条支路连接至电流反馈运算放大芯片u4的z端,并以另一条支路作为输入端b,电流反馈运算放大芯片u1的z端经积分器接地,电流反馈运算放大芯片u1的p端与乘法器u5的x1端连接,电流反馈运算放大芯片u2的z端经电阻接地,电流反馈运算放大芯片u2的p端与乘法器u5的y1端连接,乘法器u5的x2端经电源接地,乘法器u5的y2端、z端共接后接地,乘法器u5的w端与电流反馈运算放大芯片u3的y端连接,电流反馈运算放大芯片u3的p端开路,以电流反馈运算放大芯片u3的x端作为第二变换记忆接口t2的正端,以电流反馈运算放大芯片u4的x端作为第二变换记忆接口t2的负端,第二变换记忆接口t2的正端和负端串联电阻或电容,电流反馈运算放大芯片u4的p端开路,电流反馈运算放大芯片u4的y端接地,控制器与输入端a、输入端b连接,输入端a、输入端b的工作频率的范围为0khz至100khz。

8.进一步地,所述积分器为电容。

9.进一步地,从输入端a流入的电流为i

ab

,流入电流反馈运算放大芯片u3的z端的电流为i5,流向第一变换记忆接口t1的负端的电流为i1,从电流反馈运算放大芯片u4的z端流出的电流为i6,从电流反馈运算放大芯片u1的z端流出的电流为i2,从电流反馈运算放大芯片u2的z端流出的电流为i3,从电流反馈运算放大芯片u3的x端流出的电流为i4。

10.进一步地,若所述第一变换记忆接口t1的正端和第一变换记忆接口t1的负端之间串联一个电阻,第二变换记忆接口t2的正端和第二变换记忆接口t2的负端之间串联另外一个电阻,则输入端a、输入端b与外部电路连接来模拟忆阻器。

11.进一步地,若所述第一变换记忆接口t1的正端和第一变换记忆接口t1的负端之间串联一个电阻,第二变换记忆接口t2的正端和第二变换记忆接口t2的负端之间串联一个电容,则输入端a、输入端b与外部电路连接来模拟忆容器。

12.进一步地,若所述第一变换记忆接口t1的正端和第一变换记忆接口t1的负端之间串联一个电感,第二变换记忆接口t2的正端和第二变换记忆接口t2的负端之间串联一个电阻,则输入端a、输入端b与外部电路连接来模拟忆感器。

13.有益效果:

14.本实用新型所提供了一种记忆元件通用模拟器,通过包括控制器、四个电流反馈运算放大器、乘法器、电源、积分器、多个电阻、电容、电感的串联后,形成输入端a和输入端b用以作为记忆元件通用模拟器与外部电路连接的两个端口,在记忆元件通用模拟器中设置有第一变换记忆接口t1和第二变换记忆接口t2,通过在第一变换记忆接口t1中串联电阻或电感,在第二变换记忆接口t2中串联电阻或电容,该硬件结构在软件工程师对其中的控制器进行软件编程后,用于模拟忆阻器、忆容器和忆感器并能够将模拟出的忆阻器、忆容器和忆感器灵活地使用在频率为100khz量级的电路中,便于模拟出的忆阻器、忆容器和忆感器投入工业生产当中。

15.上述说明仅是本实用新型技术方案的概述,为了能够更清楚了解本实用新型的技术手段,而可依照说明书的内容予以实施,并且为了让本实用新型的上述和其它目的、特征和优点能够更明显易懂,以下特举本实用新型的具体实施方式。

附图说明

16.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本实用新型的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

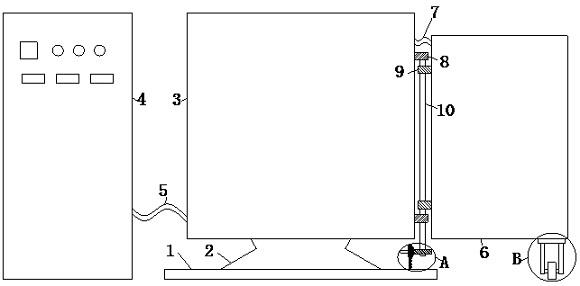

17.图1为本实用新型的记忆元件通用模拟器的结构示意图;

18.图2为本实用新型模拟忆阻器的结构示意图;

19.图3为本实用新型模拟忆容器的结构示意图;

20.图4为本实用新型模拟忆感器的结构示意图;

21.图5为本实用新型的模拟忆阻器的工作频率情况示意图;

22.图6为本实用新型的模拟忆容器的工作频率情况示意图;

23.图7为本实用新型的模拟忆感器的工作频率情况示意图。

具体实施方式

24.结合以下实施例对本实用新型作进一步描述。

25.见图1,本实施例的记忆元件通用模拟器,包括分别与控制器电连接的四个分别标记为电流反馈运算放大器u1、电流反馈运算放大器u2、电流反馈运算放大器u3和电流反馈运算放大器u4的电流反馈型电流反馈运算放大器ad844、一个乘法器u5、电阻r1、起积分器作用的电容c1、直流电压源vs,电流反馈运算放大器u1的y端与分出两条支路,其中一条支路连接至电流反馈运算放大器u3的z端,并以另一条支路作为记忆元件通用模拟器的输入端a,以输入端a的电压为v

a

,从输入端a流向两条支路节点的电流为i

ab

,流入电流反馈运算放大器u3的z端的电流为i5,以电流反馈运算放大器u1的x端作为第一变换记忆接口t1的正端,以电流反馈运算放大器u2的x端作为第一变换记忆接口t1的负端,第一变换记忆接口t1的正端和第一变换记忆接口t1的负端可串联电阻或电感,第一变换记忆接口t1的正端流向电流反馈运算放大器u2的x端的电流为i1,电流反馈运算放大器u2的y端与分出两条支路,其中一条支路连接至电流反馈运算放大器u4的z端,并以另一条支路作为记忆元件通用模拟器的输入端b,从电流反馈运算放大器u4的z端流出的电流为i6,电流反馈运算放大器u1的z端串联电容c1后接地,从电流反馈运算放大器u1的z端流出的电流为i2,电流反馈运算放大器u1的p端与乘法器u5的x1端连接,电流反馈运算放大器u2的z端串联电阻r1后接地,从电流反馈运算放大器u2的z端流出的电流为i3,电流反馈运算放大器u2的p端与乘法器u5的y1端连接,乘法器u5的x1端串联直流源v

s

后接地,乘法器u5的y2端与其z端共接到一起并接地,乘法器u5的w端与电流反馈运算放大器u3的y端连接,从电流反馈运算放大器u3的y端流出的电流为i4,电流反馈运算放大器u3的p端开路,以电流反馈运算放大器u3的x端作为第二变换记忆接口t2的正端,以电流反馈运算放大器u4的x端作为第二变换记忆接口t2的负端,第二变换记忆接口t2的正端和第二变换记忆接口t2的负端可串联电阻或电容,电流反馈运算放大器u4的p端开路,电流反馈运算放大器u4的y端接地。电流反馈运算放大器u1的x、y、p、z端分别对应电压v

1x

、v

1y

、v

1p

、v

1z

,电流反馈运算放大器u2的x、y、p、z端分别对应电压v

2x

、v

2y

、v

2p

、v

2z

,电流反馈运算放大器u3的x、y、p、z端分别对应电压v

3x

、v

3y

、v

3p

、v

3z

,电流反馈运算放大器u4的x、y、p、z端分别对应电压v

4x

、v

4y

、v

4p

、v

4z

。

26.输入端a和输入端b作为通用接口电路的外接端口,使记忆元件通用模拟器能够与

[0040][0041]

在电流反馈运算放大器u1、u2各自z端的输出电流为如下所述:

[0042]

i2=i1[0043][0044]

电容c1在通用接口电路中起积分作用,故v

c1

可表示为:

[0045][0046]

为输入端a、输入端b之间的电压v

ab

对时间的积分值,计算可得:

[0047][0048][0049]

可得乘法器u5的输出电压v

w

为:

[0050][0051]

电流反馈运算放大器u3、电流反馈运算放大器u4分别对应的电压和电流为:

[0052]

v

3x

=v

3y

=v

w

[0053]

v

4x

=v

4y

=0

[0054]

i4=

‑

i

ab

[0055]

故可得:

[0056][0057][0058][0059]

其中,忆阻器的忆导值是关于的函数,α1代表忆导值的变化率,β1代表忆导值的初始值,且α1、β1分别为:

[0060][0061]

将上述计算得到的参数放入本实施例的记忆元件通用模拟器,将输入端a、输入端b分别接入外部电路来模拟忆阻器使用。

[0062]

为了验证本实施例的记忆元件通用模拟器所模仿出的忆阻器的正确性,申请人根据激励电压的公式v

ab

=asin(2πft)=asin(ωt),得其中,为v

ab

对时间的积分值,比较可得忆阻器的磁通的幅值与呈正比关系。

[0063]

且根据公式变换得到算法并根据

算法在v

ab

‑

i

ab

平面中绘制出磁滞环曲线,比较可得,当激励电压v

ab

的幅值保持不变时,随着激励频率增加,磁通的幅值减小,电流i

ab

的幅值也随之减小,在v

ab

‑

i

ab

平面中绘制出磁滞环曲线向内收缩。

[0064]

根据上述的理论分析,申请人还采用pspice软件进行仿真实验,在pspice软件中搭建本实施例的记忆元件通用模拟器并将下述参数放入:正弦激励电压v

ab

为v

ab

=sin(2πft)(v)、电容c1=0.1nf、r1=45kω、r2=16kω、r3=55kω、v

s

=

‑

2.5v,在各个电流反馈型电流反馈运算放大器及乘法器u5的供电端分别接入幅值为

±

15v的直流供电电压。

[0065]

对于记忆元件通用模拟器,电流i

ab

为流经输入端a、输入端b之间的电流,在pspice软件仿真中可用表笔直接测量;电压v

ab

也可直接测量得出。

[0066]

当激励频率分别为80khz、100khz和130khz时,输入端a、输入端b之间的电压v

ab

和电流i

ab

的李萨如相轨迹如图5所示。

[0067]

可见,电压v

ab

和电流i

ab

的李萨如相轨迹在频率分别为80khz、100khz和130khz时,均能达到忆阻器的记忆特征,即忆阻值倒数w

m

在v

ab

‑

i

ab

平面内保持形如斜“8”字形的磁滞环,且随着激励电压频率的增大,电压幅值保持不变,电流i

ab

减小,磁滞环向内收缩。

[0068]

综上,仿真实验的结果与理论分析一致,因此本实施例的记忆元件通用模拟器是能够模拟出忆阻器的记忆特性的。

[0069]

实施例2

[0070]

对于忆容器,模拟器的内部状态变量的关系以及忆容值c

m

可定义为:

[0071][0072][0073]

其中α2代表c

m

的变化斜率,β2代表c

m

的初始值。

[0074]

见图3,在对输入端a、输入端b之间施加激励电压的情况下,通过如下方法完成本实施例的记忆元件通用模拟器中各个参数的匹配设置,来模拟忆容器使用:

[0075]

将电阻r2串联在第一变换记忆接口t1正负端之间,电阻c2串联在第二变换记忆接口t2正负端之间,由电流反馈运算放大器ad844的电压跟随特性,可得电容c2两端的电压为:

[0076][0077]

电流反馈运算放大器u3的x端输入电流等于其z端输入电流:

[0078]

i4=

‑

i

ab

[0079]

因此通过电容c2的电荷为:

[0080]

其中,是流经电容c2的电流i4对时间的积分,即

[0081][0082][0083]

其中c

m

为忆容器的忆容值,α2代表忆容值c

m

的变化率,β2代表忆容值c

m

的初始值,且

α2、β2分别为:

[0084][0085]

将上述计算得到的参数放入本实施例的记忆元件通用模拟器,将输入端a、输入端b分别接入外部电路来模拟忆容器使用。

[0086]

为了验证本实施例的记忆元件通用模拟器所模仿出的忆容器的正确性,申请人根据激励电压的公式v

ab

=a sin(2πft)=a sin(ωt),得其中,为v

ab

对时间的积分值,比较可得忆容器的磁通的幅值与呈正比关系。

[0087]

且根据公式变换得到算法并根据算法在v

ab

‑

q

ab

平面中绘制出磁滞环曲线,比较可得,当激励电压v

ab

的幅值保持不变时,随着激励频率增加,磁通的幅值减小,电荷q

ab

的幅值变小,在v

ab

‑

q

ab

平面中绘制出磁滞环曲线向内收缩。

[0088]

根据上述的理论分析,申请人还采用pspice软件进行仿真实验,在pspice软件中搭建本实施例的记忆元件通用模拟器并将下述参数放入:正弦激励电压v

ab

为v

ab

=sin(2πft)(v)、电容c1=0.25nf、c2=0.1nf、r1=3kω、r2=11kω、v

s

=

‑

0.5v,在各个电流反馈型电流反馈运算放大器及乘法器u5的供电端分别接入幅值为

±

15v的直流供电电压。

[0089]

由于本实施例的记忆元件通用模拟器,其内部某些待测变量不易于直接探测,为了实验结果分析需要,采用等效替代的方式,将正比例于待测变量的可测数据等效替代待测变量。这种方式适用于pspice软件仿真。

[0090]

对于本实施例的记忆元件通用模拟器,q

ab

为流经输入端a、输入端b之间的电流i

ab

对时间的积分值,基于电流反馈运算放大器ad844的电流跟随特性,得到i

ab

=

‑

i4。电容c2在记忆元件通用模拟器中起积分作用,可得其中,为电容c2两端的电压值,故有可见,q

ab

与呈正比关系,可用等效替代q

ab

用以计算,而v

ab

为输入端a、输入端b之间的电压,可直接测量得出。

[0091]

当激励频率为95khz、100khz和105khz时,输入端a、输入端b之间电压v

ab

和等效于电荷q

ab

的电压的李萨如相轨迹如图6所示。

[0092]

比较频率分别为95khz、100khz和105khz时的轨迹图,可以得到忆容器的重要特征:忆容值c

m

在v

ab

‑

q

ab

平面内保持形如斜“8”字形的磁滞环,且随着激励电压频率的增大,电压幅值保持不变,电荷q

ab

的变化范围缩小,磁滞环向内收缩。

[0093]

综上,仿真实验的结果与理论分析一致,因此本实施例的记忆元件通用模拟器是能够模拟出忆容器的记忆特性的。

[0094]

实施例3

[0095]

对于忆感器,模拟器的内部状态变量q

‑

ρ的关系以及忆感值的倒数l

m

‑1可定义为:

[0096]

[0097][0098]

其中α3代表l

m

‑1的变化斜率,β3代表l

m

‑1的初始值。

[0099]

见图4,在对a和b之间施加激励电压的情况下,通过如下方法完成本实施例的记忆元件通用模拟器中各个参数的匹配设置,来模拟忆感器使用:

[0100]

将电感l1串联在第一变换记忆接口t1正负端之间,电阻r2串联在第二变换记忆接口t2正负端之间,由电流反馈运算放大器ad844的电压跟随特性,可得电感l1两端的电压v

ab

和电流i1分别为:

[0101][0102]

其中,为忆感器的电压v

ab

对时间的积分。

[0103]

电流反馈运算放大器u1的z端上的电容c1提供了积分运算,电流反馈运算放大器u1的z端所输出的电流等于其x端所输出的电流,因此通过c1的电荷q为:

[0104][0105]

其中,ρ

ab

为磁通对时间的积分。

[0106]

可得乘法器u5的输出电压v

w

为:

[0107][0108]

电流反馈运算放大器u2的z端输出电压v

2z

可表示为:

[0109][0110][0111][0112]

其中,l

m

‑1(ρab)为磁通忆感器忆感值倒数值,α3代表l

m

‑1的变化率,β3代表l

m

‑1的初始值,且α3、β3分别为:

[0113][0114]

将上述计算得到的参数放入本实施例的记忆元件通用模拟器,将输入端a、输入端b分别接入外部电路来作模拟忆感器使用。

[0115]

为了验证本实施例的记忆元件通用模拟器所模仿出的忆容器的正确性,申请人根据激励电压的公式v

ab

=asin(2πft)=asin(ωt),其中,为v

ab

对时间的积分值,ρ

ab

为对时间的积分值,因此变换公式可得比较可得积分值ρ

ab

的幅值与呈正比关系。

[0116]

且根据公式变换得到算法并根据算法在平面中绘制出磁滞环曲线,比较可得,当激励电

压v

ab

的幅值保持不变时,随着激励频率增加,磁通和其积分值ρ

ab

会变小,使忆感值倒数值l

m

‑1逐渐趋近于β3,在平面中绘制出磁滞环曲线向内收缩。

[0117]

在pspice软件中搭建本实施例的记忆元件通用模拟器并将下述参数放入:正弦激励电压v

ab

为v

ab

=3sin(2πft)(v)、电容c1=0.02nf、r1=3kω、r2=8kω、l1=0.05h、v

s

=

‑

2.5v,在各个电流反馈型电流反馈运算放大器及乘法器u5的供电端分别接入幅值为

±

15v的直流供电电压。

[0118]

由于本实施例的记忆元件通用模拟器内部某些待测变量不易被探测,为了实验结果分析需要,下面我们将采用等效替代的方式,将正比例于待测变量的可测数据等效替代待测变量。这种方式适用于pspice软件仿真。

[0119]

对于本实施例的记忆元件通用模拟器所模拟出的忆感器,i

ab

为流经输入端a、输入端b之间的电流,在pspice软件仿真中可用表笔直接测量;基于电流反馈运算放大器ad844的电压跟随特性,且电感l1的两端电压为v

ab

,可推导出可见,与i1呈正比关系,可用i1等效替换用以算法计算。

[0120]

当激励频率分别为95khz、100khz和105khz时,电流i

ab

和等效于磁通的电流i1的李萨如相如图7所示。

[0121]

比较频率分别为95khz、100khz和105khz时的轨迹图,可以得到忆感器的重要特征:忆感值倒数l

m

‑1在i1‑

i

ab

平面内保持形如斜“8”字形的磁滞环,且随着激励电压频率的增大,电压幅值保持不变,磁通和ρ

ab

会变小,磁滞环向内收缩。

[0122]

综上,仿真实验的结果与理论分析一致,因此本实施例的记忆元件通用模拟器是能够模拟出忆感器的记忆特性的。

[0123]

有益效果:上述实施例1、实施例2、实施例3中,只改变第一变换记忆接口t1正负端、第二变换记忆接口t2正负端分别串联的电阻或电容或电感,就能模拟忆阻器、忆容器和忆感器的特性,而无须再额外的设备或辅助电路来实现忆阻器、忆容器和忆感器的特性,使得模拟得到的忆阻器、忆容器、忆感器能够灵活地与其他电路连接使用,同时本实施例的电路结构较为简洁,易于电路实验,并且所转化的忆阻器、忆容器和忆感器能在高于100khz的工作频率下呈现记忆特性。并且与现有技术相比,上述实施例1、实施例2、实施例3中分别模拟出的忆阻器、忆容器和忆感器,在使用过程中能够降低电路中频率的消耗达11.8%,但本实施例中的模拟出忆阻器、忆容器和忆感器能够在频率为100khz的电路中使用,比现有的0.8khz增加了162倍,因而,本实施例的记忆元件通用模拟器能够灵活地使用在频率为100khz的电路中,便于模拟出的忆阻器、忆容器和忆感器投入工业生产当中。

[0124]

最后应当说明的是,以上实施例仅用以说明本实用新型的技术方案,而非对本实用新型保护范围的限制,尽管参照较佳实施例对本实用新型作了详细地说明,本领域的普通技术人员应当理解,可以对本实用新型的技术方案进行修改或者等同替换,而不脱离本实用新型技术方案的实质和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。