技术特征:

1.一种多通道同步高速数据采集装置,其特征在于,包括一块处理板和两块采集子板,两块采集子板的结构相同,以并行方式采集数据,再发送给处理板;在采集子板与处理板内部具体又包括如下模块:一时钟管理模块,包括晶振和多片时钟芯片,时钟芯片采用时钟树级联结构,为整个系统提供足够多通道的同步时钟信号;晶振产生低频的源时钟信号发送给处理板上的时钟芯片,由处理板上的时钟芯片通过时钟输出通道向采集板上的时钟芯片提供时钟源,再通过脉冲输出通道向采集板时钟提供同步脉冲信号,采集板的时钟芯片接收到该同步信号后响应该信号,以调整时钟输出通道的相位,并通过配置为脉冲模式的输出通道向采集板fpga和adc提供脉冲信号,据此实现多时钟芯片的同步时钟输出;一多adc数据同步模块,包括时间戳添加模块、采样数据调序模块以及增加动态时延模块;时间戳添加模块根据adc数据手册,将adc芯片的时间戳功能打开;adc在sclk的驱动下对输入的模拟信号进行采样,将模拟信号转换为m个bit的采样点数据;随后,通过adc内部的串行通道映射单元为m个bit的采样点数据添加w个bit的冗余控制位,形成m w个bit的串行通道数据,默认情况下冗余控制位的值为0,当由时钟管理模块发送的时间戳标记信号sysref上升沿到来时,对上升沿之后的第一个采样点进行标记,具体方式是把冗余控制位中的其中一位进行置1,完成时间戳的添加;采样数据调序模块对由adc传输到fpga并完成降速之后的k路并行数据进行调序:检测时间戳标记出现在并行数据的位置,记为l,1≤l≤k;将原并行数据的第1至l

‑

1路延迟两个dclk周期,原并行数据的第l路至第k路延迟一个dclk周期,形成延迟后的并行数据;最后将延迟后的并行数据按第l路至第k路、第1路至第l

‑

1路的顺序重新依次排列,形成调序后的并行数据;增加动态时延模块使用多片fifo分别为每通道调序后的并行数据增加动态延迟,当某一通道调序后的并行数据被检测出含有时间戳标记位“1”时,则开启对应通道的fifo的写使能;当所有通道调序后的并行数据均被检测出含有时间戳标记位“1”后,则开启所有通道的fifo的读使能,且保持写使能开启,读写保持平衡,各通道并行数据被动态地增加延迟,形成最终的用户数据流。一时钟同步、时间戳添加和链路建立顺序管理模块,确定时钟同步、时间戳添加和传输链路建立三个独立过程的工作顺序,系统处理板上的fpga分三次向时间管理模块发送同步脉冲,具体处理流程如下:fpfa第一次发送的同步脉冲至时钟管理器后,时钟管理器内的时钟分配网络进行复位操作,完成时钟同步过程;随后,fpga向时钟管理器发送spi命令,一方面屏蔽时钟分配网络对同步脉冲的响应,另一方面打开脉冲分配网络对同步脉冲的响应;同时,fpga还向adc发送spi命令,对adc的默认寄存器数据进行改写,禁用adc中默认的多帧时钟对齐功能,打开时间戳功能;fpfa第二次发送的同步脉冲至时钟管理器后,时钟管理器内的脉冲分配网络进行复位操作,产生系统的参考脉冲sysref,并分别反馈给fpga和所有adc;当fpga内部的千兆收发器模块接收到参考脉冲sysref后,置高由fpga发送到每个adc的syncb信号,当adc接收到被

置高的syncb信号后,开始向fpga传输串行通道数据流,完成数据传输链路建立过程;fpfa第二次发送的同步脉冲至时钟管理器后,时钟管理器内的脉冲分配网络再次进行复位操作,第二次产生系统的参考脉冲sysref,并分别反馈给fpga和所有adc;当adc接收到参考脉冲sysref后,标记参考脉冲sysref上升沿时刻之后的第一个采样点数据,并将其所对应的串行通道数据的冗余控制位中的某一位置1,其余位保持为0,从而完成时间戳标记过程;一多通道采样同步模块,包括adc时序调整、通道间延迟测量以及通道间延迟校正;adc时序调整通过spi通讯协议回读adc内部寄存器数据,监测adc的sysref建立/保持时间窗口寄存器,若寄存器回读值为1,表示时序违例,即sysref的有效沿出现在sclk有效沿的窗口内,sysref不满足sclk的时序条件,此时应逐步增加对应的发送至adc的sysref延迟值,直至再次初始化后不显示时序违例,即回读值为0;通道间延迟测量通过选取一个通道作为基准通道,其余的通道作为待测通道,利用信号源输出已知频率的正弦信号,再通过功率分配器和等长传输线将正弦信号输入至基准通道和待测通道,使用fpga调试工具ila收集基准通道和待测通道在同一时间段内采集到的用户数据,计算出各通道间的相位差并进一步得到通道间延迟;通道间延迟校正通过按步进逐步增加待测通道的sclk延迟与sysref延迟,使得增加的延迟量尽可能接近通道间延迟值,直至增加的延迟量与测得的通道间延迟值之差的绝对值小于时钟芯片延迟的可调节最小步进;一基于触发的数据存储同步模块,在采集板数据同步之后,挑选一段时间内的波形数据送至处理板fpga进行处理并在上位机进行显示,这一过程称为触发,将被挑选的数据从实现同步的align fifo中暂存入采集板内另一级实现触发的block fifo中,block fifo的读写使能信号均由处理板fpga向两块采集板fpga发送,并使用fpga idelay2单元对跨板传输的控制信号实施精确延迟调节,使接收端控制信号远离亚稳态区间,保证多模块波形数据的存储同步。

技术总结

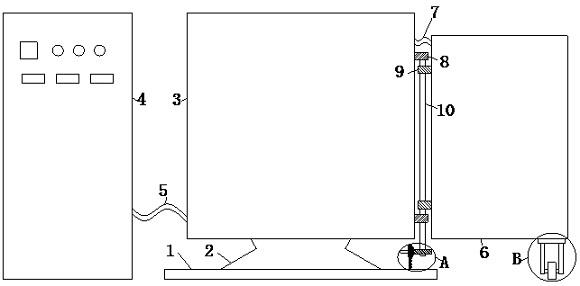

本发明公开了一种多通道同步高速数据采集装置,通过时钟管理模块提供同步时钟,ADC在采样时钟的驱动下对信号进行采样,得到采样数据后传输到采集FPGA,多ADC数据同步模块在ADC中为采样数据添加时间戳标记,在采集FPGA中对采样数据进行调序,将带有标记位的采样点调整为第一路,并通过增加动态时延实现多ADC数据流同步;时钟同步时间戳添加和链路建立顺序管理模块对时钟同步、时间戳功能和JESD204B链路三个独立过程的工作顺序进行管理,解决三者在多ADC数据同步中的冲突,多通道采样同步模块通过调节时间戳信号与发送端器件时钟的相位关系,避免两者时序为例而产生随机延迟,基于触发的数据存储同步模块对信号进行精确延迟调节,实现了不同板间的数据同步存储。实现了不同板间的数据同步存储。实现了不同板间的数据同步存储。

技术研发人员:黄武煌 袁春友 张松 邱渡裕 张沁川 杨扩军 潘卉青 叶芃 王厚军

受保护的技术使用者:电子科技大学

技术研发日:2021.06.29

技术公布日:2021/10/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。