1.所公开的实施例涉及设备,且具体地,涉及具有数据安全机制的设备和其操作方法。

背景技术:

2.在传统的计算系统中,在此类系统上运行的任何特许进程都具有访问(例如,读取和/或写入)任何存储器的能力。因此,恶意实体(例如黑客)如果能够以提升的权限运行进程就会利用这种能力来访问有价值的信息。虽然标准应用程序或web应用程序不按特许运行,但是恶意实体已能够获得特许访问或利用硬件安全漏洞。

技术实现要素:

3.根据本技术的一个方面,提供一种设备。所述设备包括:核心,其配置成处理数据;逻辑,其耦合到所述核心且配置为转换器以跟踪与所述数据相关联的加扰密钥;以及电路系统,其耦合到所述核心且配置成:在将所述数据写入到存储器之前,根据所述加扰密钥对所述数据进行加密,以及基于使用所述加扰密钥对从所述存储器读取的数据进行解密而恢复所述数据。

4.根据本技术的另一方面,提供一种方法。所述方法包括:在电路系统处接收要写入一或多个存储器地址的输入数据,所述电路系统配置成用加扰密钥对所述数据进行加密且用所述加扰密钥对所述数据进行解密;在所述电路系统处接收所述加扰密钥,其中所述加扰密钥包括与计算进程相关联的唯一标识符;以及根据所述加扰密钥传输待写入到存储器阵列的经加密数据或从所述存储器阵列读取的经解密数据。

5.根据本技术的又一方面,提供一种系统。所述系统包括:存储器,其配置成存储数据;以及处理器,其通信耦合到所述存储器,所述处理器包含:核心,其配置成处理用于计算进程的内容数据,逻辑,其耦合到所述核心且配置为转换器以确定与所述计算进程相关联的加扰密钥;以及电路系统,其耦合到所述核心且配置成:根据所述加扰密钥对所述内容数据进行加密以生成写入到所述存储器的所述数据,以及使用所述加扰密钥对从所述存储器读取的所述所存储数据进行解密。

附图说明

6.图1是计算系统的框图。

7.图2是根据本发明技术的实施例的系统的框图。

8.图3是根据本发明技术的实施例的存储器管理单元的详细框图。

9.图4是根据本发明技术的实施例的实例加扰电路的详细框图。

10.图5是根据本发明技术的实施例,图3的存储器管理单元处理未授权访问的图示。

11.图6是说明根据本发明技术的实施例操作设备的实例方法的流程图。

12.图7是包含根据本发明技术的实施例的设备的系统的示意图。

具体实施方式

13.图1是计算系统100的框图。计算系统100包含一或多个处理器102,所述处理器可操作地/电耦合到存储器104(例如,随机存取存储器(ram)、快闪存储器、硬盘驱动器(hdd)等),所述存储器配置成存储信息和提供对信息的访问。处理器102中的每一者包含耦合到存储器管理单元(mmu)113的至少一个处理核心112,所述mmu包含至少一个转换器114和至少一个本地高速缓冲存储器116。处理核心112例如通过根据软件指令对数据值执行逻辑、逐位和/或算术运算来处理数据。在处理数据时,处理核心112向转换器114提供虚拟存储器地址,所述转换器可以包含基于虚拟存储器地址(经由例如页表集或其它查找表)生成物理存储器地址的逻辑或其它电路系统。单独地或并行地,处理核心112向本地高速缓冲存储器116提供或从所述本地高速缓冲存储器接收存储器数据(例如,分别写入或读取内容)。本地高速缓冲存储器116可以包含用于存储各种类型信息的板载存储器(例如,mmu 113中存在的相对快速的易失性存储器类别)。

14.本地高速缓冲存储器116在功能上/电耦合到存储器控制器118,所述存储器控制器配置成控制存储器104的通信和/或功能。换句话说,存储器控制器118为处理器102外部的存储器104提供接口。因此,存储器控制器118与存储器104连接以实施存储器操作(例如,读取和/或写入)。对于写入操作,存储器控制器118接收写入数据和写入地址(例如,物理存储器地址),并向存储器104发出对应的存储器命令、写入数据和/或写入地址。对于读取操作,存储器控制器118向存储器104提供读取命令和对应的读取地址,并响应地接收读取数据。存储器控制器118经由本地高速缓冲存储器116(例如,临时存储装置)将读取的数据提供到处理核心112。存储器控制器118可以包含在处理器102中,或者是处理器102外部的单独装置(例如,裸片)。

15.给定上述结构,在处理核心112上运行的特许进程可以访问存储器104的各个部分。恶意实体(例如黑客)可能利用这种配置来获取存储器104中存储的有价值的信息。本发明技术的实施例通过提供数据安全机制来解决这些挑战,所述机制仅允许进程正确解释由这些进程写入到存储器的数据。

16.如下文更详细地描述的,本文公开的技术涉及用于保护所存储数据的设备,例如计算系统、处理系统、具有处理器装置的系统、相关方法等。设备(例如,处理器和/或包含处理器的系统)可以在硬件层对数据进行加密/解密。例如,处理器可以包含加扰器电路,所述加扰器电路配置成在存储器数据存储之前对其进行加密,并使用对于写入/读取存储器数据的计算进程唯一的密钥对来自存储装置的存储器数据进行解密。在一些实施例中,加密密钥可以对应于描述进程的物理页的每个页表条目。

17.基于硬件的存储器数据加密/解密为保护存储器数据免受恶意进程的伤害提供了更高的安全性。此外,由于安全性是在硬件层实施的(即对应用程序开发人员来说是透明的),因此所有应用程序/进程都可以获得增强的安全性,而不需要调整软件。此外,增强的安全性可以应用于不仅仅是特定的存储器范围,而是与进程相关联的所有存储器。

18.图2是根据本发明技术的实施例的系统200(例如,计算装置或包含计算装置的系统)的框图。系统200可以包含可操作地/电耦合到存储器204(例如ram、快闪存储器、hdd等)的处理器202,所述存储器配置成存储例如内容数据和/或软件指令等信息和提供对所述信息的访问。

19.处理器202可配置成执行软件指令。换句话说,处理器202可配置成例如通过根据指令和/或电路配置、根据软件指令对数据实施逻辑运算(例如,与、或等)、算术运算(例如,加法)和/或位级运算(例如,移位、掩蔽等)来处理信息。作为说明性实例,处理器202可配置成从预定位置访问初始指令/数据集,例如用于在系统上电复位事件之后启动/初始化系统200。一旦初始化,处理器202就可以迭代地获取和执行软件指令。在执行软件指令时,处理器202可以将内容数据(例如,处理值/结果)写入到存储器204并从存储器204读取所存储数据。

20.在一些实施例中,处理器202可以包含系统总线212、存储器管理单元(mmu)214、一组寄存器216(例如,高速缓冲存储器)、指令预取器218、指令解码器220、指令控制器222和/或用于处理信息的算术逻辑单元(alu)224。指令预取器218可以配置成确定要在预定数量的即将到来的处理周期内执行的被调度指令。指令预取器218可以向mmu214发送对即将到来的指令的请求。基于这些请求,mmu 214可以与系统总线212交互以接收软件指令。

21.系统总线212可以配置成与存储器204连接以在处理器202与存储器204之间传送指令和/或数据。例如,系统总线212可以从mmu 214接收关于存储在存储器204中的软件指令的请求。基于所接收的请求,系统总线212可以例如通过向存储器204发送命令、向所述存储器发送地址和/或接收来自所述存储器的对应软件指令而与存储器204交互。系统总线212可以类似地与存储器204连接,以读取和写入内容数据,作为执行软件指令的一部分。当系统总线212接收来自alu 224的读取或写入请求时,系统总线212可以类似地与存储器204传送命令、地址和/或内容数据。系统总线212可以向mmu214提供所接收/读取的内容数据,所述mmu可以进一步向寄存器216提供所读取的内容数据,以供alu 224处理。

22.系统总线212可以向指令解码器220提供所接收的软件指令。指令解码器220可以配置成将软件指令解码为可由alu 224执行的机器级指令。指令解码器220可以根据一或多个预定进程对软件指令进行解码。指令解码器220可以向指令控制器222提供机器级指令。

23.指令控制器222可以配置成根据处理器202的当前状态对机器级指令进行排序。例如,指令控制器222可以确定或跟踪当前加载在寄存器216中的内容数据。此处,指令控制器222可以确定可以在当前时间执行的机器级指令和可以在稍后时间执行的机器级指令,例如由于与软件指令和/或当前在寄存器216中的内容数据相关联的顺序。指令控制器222可以根据所产生的顺序向其alu 224提供机器级指令。

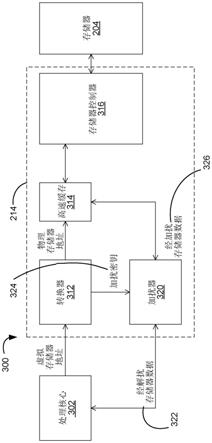

24.alu 224(例如,处理核心)配置成执行机器级指令。alu 224可以根据机器级指令访问和操作存储在寄存器216中的内容数据。alu 224可以将机器级指令的结果发送到待写入到存储器204的mmu 214。

25.mmu 214配置成管理对存储器204的访问,例如用于读取和/或写入操作。mmu 214可以将虚拟存储器地址(例如,由操作系统和/或软件指令使用的存储器地址)转换为由存储器204使用的物理地址。mmu 214可以进一步处理存储器保护、高速缓存控制、总线仲裁和/或存储器组切换。

26.如下文进一步详细描述,mmu 214可以包含配置成跟踪加扰密钥的hw电路系统以及用于处理器202执行的进程的页表集。mmu 214可进一步包含配置成使用加扰密钥对内容数据进行加密/解密的加扰器电路。在写入数据时,mmu 214可以使用加扰器电路,根据特定于写入数据的计算进程的密钥来对写入数据进行加密。mmu 214可以将经加扰结果发送到

存储器以进行存储。在读回数据时,mmu 214可以从存储器204接收经加扰结果,然后根据与读取数据的计算进程相关联的密钥,使用加扰器电路对经加扰结果进行解密。因此,当相同的计算进程写入和读取相同的数据时,加扰器电路可以恢复原始内容数据。然而,当计算进程(例如,恶意软件/进程)试图读取由不同进程写入的内容数据时,由于用于对数据进行加密和解密的进程特定的密钥不同,因此加扰器电路可以产生与最初存储的内容不同的结果。

27.图3是根据本发明技术的实施例的存储器管理单元(例如,mmu 214)的详细框图。如上所述,mmu 214可以耦合到处理核心302(例如图2的alu 224)和存储器204。在一些实施例中,mmu 214可以包含转换器312、本地高速缓存314和/或用于管理对存储器204的访问/通信的存储器控制器316。

28.转换器312可配置成将操作系统和/或软件指令使用的虚拟存储器地址转换为存储器204使用的物理存储器地址。在一些实施例中,转换器312可以配置成管理和跟踪图2的处理器202执行的一或多个进程的页表。页表可以包含对应进程的虚拟存储器地址与物理存储器地址之间的映射。作为说明性实例,转换器312可以在执行进程时从处理核心302接收虚拟存储器地址。转换器312可以访问对应进程的页表,并生成与虚拟存储器地址相对应的物理存储器地址。

29.转换器312可以将物理存储器地址提供到本地高速缓存314。本地高速缓存314(例如,mmu 214中的缓冲器和/或寄存器)可以配置成存储与存储器装置204之间传送的信息。例如,本地高速缓存314可以临时存储用于传送对应的读取或写入命令的物理地址。另外,本地高速缓存314可以临时存储用于传送到存储器204的写入数据和/或临时存储响应于读取命令而从存储器204接收到的读取数据。

30.存储器控制器316可以配置成与存储器204连接,例如通过控制存储器204的通信和/或一或多个功能/状态。存储器控制器316可以生成与来自处理核心302的请求相对应的存储器命令(例如,读取和/或写入命令)并将其发送到存储器204。存储器控制器316可以进一步将与请求相对应的经转换地址发送到存储器204以实施对应的读取和/或写入操作。存储器控制器316可以相应地将要写入的数据发送到存储器204(例如,在与经转换物理地址相对应的位置处)以进行写入操作,并且从存储器204接收先前写入的数据(例如,存储在与经转换物理地址相对应的位置处的数据)以进行读取操作。

31.mmu 214可以包含配置成对内容数据进行加密/解密的加扰器电路320。对于写入操作,加扰器电路320可以从处理核心302接收经解扰存储器数据322(例如,内容数据)。转换器312可以将与发起写入操作的计算进程相对应的加扰密钥324提供到加扰器电路320。加扰器电路320可以使用加扰密钥324和经解扰存储器数据322作为输入,以生成作为经解扰存储器数据322的经加密输出/结果的经加扰存储器数据326。加扰器电路320可以包含一或多个硬件配置以生成经加扰存储器数据326。在一些实施例中,例如,加扰器电路320可以基于对经解扰存储器数据322和加扰密钥324应用异或(xor)运算来生成经加扰存储器数据326。加扰器电路320可以将经加扰存储器数据326提供到本地高速缓存314,并且存储器控制器316可以将经加扰存储器数据326而不是原始经解扰存储器数据322写入到存储器204。

32.因此,处理器202可以从存储器204接收经加扰存储器数据326以用于运算。如上所述,可以将经加扰存储器数据326提供到加扰器电路320。加扰器电路320可以进一步从转换

器312接收用于发起读取操作的计算进程的加扰密钥324。加扰器电路320可以使用经加扰存储器数据326和加扰密钥324作为输入来生成经解扰存储器数据322。换句话说,加扰器电路320可以根据实施读取操作的计算进程的加扰密钥324对经加扰存储器数据326进行解密。加扰器电路320可以使用与加密相同的配置或与加密互补(即,反转)的不同配置来对经加扰存储器数据326进行解密。

33.结果,当加扰密钥324包含与加密进程期间使用的值相同的值时,处理器202可以恢复经解扰存储器数据322。换句话说,当写入数据的相同计算进程实施读取操作时,处理器202可以再现经解扰存储器数据322。否则,当计算进程(例如,恶意进程)发起读取操作以读取与不同进程相关联的数据时,处理器202可以生成与原始经解扰存储器数据322不同的值,因为计算进程与不同的加扰密钥相对应。

34.图4是根据本发明技术的实施例的实例加扰电路(例如,加扰器电路320)的详细框图。在一些实施例中,加扰器电路320可以基于(例如,根据一或多个预定的逻辑、逐位和/或算术运算)组合加扰密钥324和经解扰存储器数据322来生成图3的经加扰存储器数据326。例如,加扰器电路320可以包含xor门集,所述xor门集基于组合输入与加扰密钥324来生成输出。

35.在一些实施例中,加扰器电路320可以包含针对所存储数据中的每一位的xor门。换句话说,加扰器电路320可以包含与每个单元的所存储数据内的位数(例如,8位、16位等)匹配的数量的xor门。每个xor门可以对输入位中的一者和加扰密钥324的位中的一者进行操作。对于写入操作,每个xor门可以对经解扰存储器数据322中的位中的一者和加扰密钥324中的位中的一者进行操作,以生成经加扰存储器数据326中的位中的一者。对于读取操作,每个xor门可以对经加扰存储器数据326中的位中的一者和加扰密钥324中的位中的一者进行操作,以生成经解扰存储器数据322中的位中的一者。

36.图5是根据本发明技术的实施例,图3的mmu 214处理未授权访问300的图示。未授权访问300可对应于由第一进程502(例如,由一或多个线程执行的计算机程序的实例)发起的写入操作和由第二进程552(例如,恶意进程)针对同一存储器位置发起的读取操作。

37.对于第一进程502,mmu 214(例如,图3的转换器312)可以维护第一页表集504。在一些实施例中,mmu 214可以存储和跟踪分配给与所述进程相对应的页表集中的进程的图3的加扰密钥324。对于此类实施例,第一页表集504可以包含与第一进程502相对应的第一加扰密钥。

38.当第一进程502发起写入操作以存储数据'abc'时,图3的处理核心302可以将虚拟存储器地址提供到mmu 214,并将数据提供到加扰器电路320。因此,mmu 214(例如,转换器312)可以使用第一页表集504来生成物理存储器地址。此外,mmu 214还可以从第一页表集504读取第一加扰密钥,并将加扰密钥提供到加扰器电路320。如上所述,加扰器电路320可以基于对来自第一进程502的数据进行加密而生成图3的经加扰存储器数据326(例如,'123')。图2的处理器202可以在图2的存储器204中的经转换物理存储器地址处存储经加扰存储器数据326。

39.对于第二进程552,mmu 214(例如,转换器312)可以维护第二页表集554。因此,在一些实施例中,第二页表集554可以包含与第二进程552相对应的第二加扰密钥。

40.当第二进程552发起读取操作以从对存储器204寻址的相同物理存储器读取时,转

换器312可以接收用于处理核心302的相同虚拟存储器地址。因此,mmu 214可以访问第二页表集554以生成用于由第一进程502发起的写入操作的相同物理存储器地址。处理器202可以基于物理存储器地址检索经加扰存储器数据326。加扰器电路320可以接收经加扰存储器数据326。加扰器电路320还可以接收与第二进程552相关联的第二加扰密钥。加扰器电路320可以使用第二加扰密钥来实施解密。然而,由于第一和第二加扰密钥对应于不同的进程并且因此具有不同的值,因此经解密输出(例如,'x !')可以不同于原始写入数据(例如,'abc')。因此,通过根据特定于请求进程的加扰密钥对存储器数据进行加密和解密,mmu 214可以在硬件级别提供安全性以保护存储器数据。

41.图6是示出根据本发明技术的实施例操作设备(例如,图2的系统200、图2的处理器202和/或图2的mmu 214)的实例方法600的流程图。方法600可以包含根据对于实施写入和/或读取操作的计算进程唯一的加扰密钥(例如,图3的加扰密钥324)来对存储器数据进行加密和/或解密。

42.在框602,系统200(例如,其中的图2的处理器202和/或图3的处理核心302)可以发起操作,例如存储器操作(例如,写入操作或读取操作)。处理核心302可以实施计算进程,例如图5的第一进程502和/或图5的第二进程552。在实施计算进程时,处理核心302可以发起从图2的存储器204读取或向所述存储器写入存储器数据的操作。

43.在框604,系统200(例如,其中的处理器202和/或处理核心302)可以识别用于存储器操作的虚拟存储器地址。为了实施操作,处理核心302可以识别计算进程(例如,应用程序和/或操作系统)用于存储器操作的虚拟存储器地址。

44.在框605,系统200(例如,图3的转换器312)可以维护用于一或多个计算进程的页表(例如,第一页表集504和/或第二页表集554)。转换器312可以基于存储器数据的虚拟存储器地址与对应物理存储器地址之间的跟踪映射来维护页表。在一些实施例中,作为发起计算进程的一部分,转换器312和/或处理核心302可以生成页表和加扰密钥324。在一或多个实施例中,转换器312和/或处理核心302可以根据预定模式或功能或随机地(例如,经由随机数生成器)生成加扰密钥324。在一或多个实施例中,操作系统或其它特许软件可以生成页表和/或加扰密钥324。转换器312和/或处理核心302可以将计算进程中的每一者的加扰密钥324存储在对应页表中。

45.在框606,系统200(例如,转换器312)可以确定与虚拟存储器地址相对应的物理地址。如上所述,转换器312可以使用页表在与针对计算进程中的每一者的读取/写入操作和写入操作相关联的虚拟存储器地址与物理存储器地址之间进行转换。

46.在框608,系统200(例如,转换器312)可以确定进程特定的密钥(例如,加扰密钥324)。转换器312可以访问用于发起存储器操作的计算进程的页表,以确定对于发起计算进程唯一的加扰密钥324。因此,转换器312可以将加扰密钥324提供到加扰器电路320。

47.在框610,系统200(例如图3的加扰器电路320)可以获得用于加密/解密的输入。加扰器电路320可以从转换器312接收加扰密钥324。加扰器电路320可以接收用于写入操作和读取操作的不同输入存储器数据。对于写入操作,如框612所示,加扰器电路320可以从处理核心302接收写入数据(例如图3的经解扰存储器数据322)。对于读取操作,如框614所示,加扰器电路320可以从存储器204接收所存储读取数据(例如图3的经加扰存储器数据326)。换句话说,加扰器电路320可以根据经转换物理存储器地址接收存储在存储器204中的数据。

48.在框616,系统200(例如,加扰器电路320)可以根据加扰密钥324对输入数据进行加扰。如上所述,可以以硬件配置加扰器电路320,以实施逻辑函数、逐位函数、算术函数或其组合。例如,加扰器电路320可以包含用于输入数据的每一位的xor门。加扰器电路320可以基于经由加密/解密函数根据加扰密钥324对输入存储器数据进行加密或解密来生成输出存储器数据。

49.对于写入操作,如框618所示,加扰器电路320可以生成经加密数据(例如,经加扰存储器数据326)。加扰器电路320可以对来自处理核心302的数据(例如,经解扰存储器数据322)进行加密以生成经加扰存储器数据326。对于读取操作,如框620所示,加扰器电路320可以生成经解密数据(例如,经解扰存储器数据322)。加扰器电路320可以对从存储器204读取的数据进行解密以生成经解扰存储器数据322。

50.在框622,系统200可以使用加扰器电路320的输出来完成操作。对于写入操作,系统200可以通过存储经加密数据来完成操作。处理器202可以将经加扰存储器数据326发送到存储器204,并且存储器204可以存储用于写入操作的经加扰存储器数据326(即,代替原始的经解扰内容数据)。对于读取操作,加扰器电路320可以将经解密输出提供到处理核心302以供发起计算进程使用。

51.当一个计算进程对同一虚拟存储器地址发起读取操作和写入操作时,用于加密和解密信息的加扰密钥324可以是相同的。因此,加扰器电路320可以对经加扰存储器数据326进行解密,以恢复与写入操作相对应的原始内容数据。然而,当不同的计算进程针对同一虚拟存储器地址发起读取和写入操作时,用于加密和解密信息的加扰密钥324可以是不同的。因此,加扰器电路320可以生成不同于与由不同计算进程发起的写入操作相对应的原始内容数据的解密输出。

52.图7是包含根据本发明技术的实施例的设备的系统的示意图。上文参考图2

‑

6所描述的前述设备(例如,存储器装置)中的任一者可并入无数更大和/或更复杂系统中的任何一个,其代表性实例是图7中示意性地示出的系统790。系统790可以包含处理器792、存储器装置794、输入/输出装置796和/或其它子系统或组件798。

53.处理器792和/或存储器装置794可以包含与上文参考图2

‑

6所描述的设备的特征大体上类似的特征,因此可以包含用于保护所存储数据的各种特征。所得系统790可以执行广泛多种功能中的任一种,例如存储器存储、数据处理和/或其它合适的功能。因此,代表性系统790可以包含但不限于手持式装置(例如,移动电话、平板电脑、数字阅读器和数字音频播放器)、计算机、车辆、电器和其它产品。系统790的组件可容纳于单个单元中或分布在多个互连的单元中(例如,通过通信网络)。系统790的组件还可包含远程装置和多种计算机可读介质中的任一种。

54.综上所述,应了解,本文中已经出于说明的目的描述了本发明技术的具体实施例,但是可以在不偏离本公开的情况下进行各种修改。此外,在具体实施例的上下文中描述的新技术的某些方面还可在其它实施例中组合或去除。此外,尽管已经在那些实施例的上下文中描述了与新技术的某些实施例相关联的优点,但其它实施例也可以显示此类优点,且并非所有的实施例都要显示此类优点以落入本发明技术的范围内。因此,本公开和相关联的技术可以涵盖未明确地在本文中示出或描述的其它实施例。

55.在上文所示的实施例中,已在处理器的上下文中描述了设备。然而,根据本发明技

术的其它实施例配置的设备可以包含其它类型的合适的数字处理电路,例如现场可编程门阵列(fpga)、微处理器、中央处理单元(cpu)、图形处理单元(gpu)等。

56.如本文所使用的术语“处理”包含操控信号和数据,例如写入或编程、读取、擦除、刷新、调整或改变值、计算结果、执行指令、汇编、传输,和/或操控数据结构。术语数据结构包含布置为位、字或码字、块、文件、输入数据、系统产生的数据(例如计算的或产生的数据)和程序数据的信息。此外,如本文所使用的术语“动态”描述在对应装置、系统或实施例的操作、使用或部署期间以及在运行制造商或第三方固件之后或同时发生的进程、功能、动作或实施方案。动态发生的进程、功能、动作或实施方案可能在设计、制造和初始测试、设置或配置后或之后发生。

57.以充分细节描述上文实施例以使所属领域的技术人员能够制作和使用实施例。然而,相关领域的技术人员将理解,本发明技术可具有额外实施例,并且本发明技术可在没有上文参考图2到7描述的实施例的细节中的若干个的情况下实践。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。