1.本技术涉及集成电路领域,尤其涉及一种计算装置及神经网络系统。

背景技术:

2.神经网络广泛应用于语音、图像处理等各个领域,以flash存储器作为计算阵列实现神经网络的乘加计算,可以有效提高数据的处理速度,降低数据搬移的功耗,进而提高计算性能。

3.现有的计算阵列可由多个flash器件以阵列的形式搭建而成。若输入至计算阵列的输入数据为负值,由于flash器件自身性能的原因,会导致flash器件无法正常工作,进而无法完成计算。针对这种情况,将输入数据拆分成只保留输入数据中取值为正数的元素的第一矩阵,和只保留输入数据中取值为负数的元素的绝对值的第二矩阵,并分别将第一矩阵和第二矩阵输入到计算阵列进行计算,从而得到与第一矩阵对应的两个计算结果,以及与第二矩阵对应的两个计算结果,最后根据对该两个矩阵的计算结果获得所述输入数据的计算结果。

4.在上述计算过程中,增加了计算的次数,从而会占用更多的计算资源(例如,器件开销和功耗等等),导致计算效率不高。

技术实现要素:

5.本技术实施例提供了一种计算装置及神经网络系统,可以节省计算资源提升计算效率。

6.本技术实施例的第一方面提供了一种计算装置,该计算装置包括:输入处理电路和计算阵列,输入处理电路与计算阵列连接。所述输入处理电路在接收来自外部的第一输入数据后,可先确定第一输入数据的正负。在确定第一输入数据为负值后,所述输入处理电路则向所述计算阵列的第一输入端口输入第一输入信号,并向所述计算阵列的第二输入端口输入第二输入信号。第一输入信号用于指示第一输入数据的绝对值,第二输入信号用于指示第一输入数据为负值。所述计算阵列在接收第一输入信号和第二输入信号后,可以基于第一输入信号和第二输入信号将第一输入数据与计算阵列中存储的第一权重值进行计算,得到第一计算结果。

7.从上述计算装置可以看出:由于计算阵列具有两个输入端口,第一输入端口可接收用于指示第一输入数据的绝对值的第一输入信号,第二输入端口可接收用于指示第一输入数据为负值的第二输入信号,故计算阵列在接收来自输入处理电路的第一输入信号和第二输入信号后,相当于接收到为负值的第一输入数据,进而计算阵列可对为负值的第一输入数据完成计算。因此,本实施例提供的计算装置可以直接接收负值的输入数据,并对为负值的输入数据完成计算,从而可以减少计算次数,提升计算效率,节省计算资源,降低计算成本。

8.在一种可能实现的方式中,所述输入处理电路还用于在确定第二输入数据为正值

后,向计算阵列的第一输入端口输入第三输入信号,并向计算阵列的第二输入端口输入第四输入信号,其中第三输入信号用于指示第二输入数据的绝对值,第四输入信号用于指示第二输入数据为正值。所述计算阵列还用于基于第三输入信号和第四输入信号将第二输入数据与计算阵列中存储的第二权重值进行计算,得到第二计算结果。

9.通过上述实现方式,计算阵列既可以实现对为负值的输入数据的计算,也可实现对为正值的输入数据的计算。

10.在一种可能实现的方式中,所述计算阵列包括第一计算单元和第二计算单元,其中,所述第一计算单元和所述第二计算单元连接计算阵列中的第一位线。所述第一计算单元用于基于第一输入信号和第二输入信号将第一输入数据与计算阵列中存储的第一权重值进行计算,得到第一计算结果。所述第二计算单元用于基于第三输入信号和第四输入信号将第二输入数据与计算阵列中存储的第二权重值进行计算,得到第二计算结果。所述计算阵列还用于输出第一输出信号,第一输出信号用于指示连接第一位线的多个计算单元的计算结果,其中多个计算单元的计算结果包括第一计算结果和第二计算结果。

11.在一种可能实现的方式中,所述计算阵列包括多个计算单元,每个计算单元包括至少一个铁电场效应管。

12.上述实现方式中,计算阵列可通过铁电场效应管实现,其中,铁电场效应管工作在亚阈值区,其输出电流小,功耗低,可以进一步节省计算成本。

13.在一种可能实现的方式中,同一列计算单元中的场效应管的漏极连接同一根位线,同一行计算单元中的场效应管的栅极连接至同一根字线,同一行场效应管的源极连接至同一根源极线。

14.在一种可能实现的方式中,所述计算阵列还包括多个参考单元,每个参考单元包括至少一个铁电场效应管。位于同一行的一个参考单元和一个计算单元可构成电流镜。

15.本技术实施例的第二方面提供了一种神经网络系统,该神经网络系统包括:处理器,用于向神经网络计算芯片输入第一输入数据。神经网络芯片,连接所述处理器并包括输入电路以及与所述输入处理电路连接的计算阵列,其中:

16.所述输入处理电路用于接收第一输入数据,并在确定第一输入数据为负值后,向所述计算阵列的第一输入端口输入第一输入信号,并向所述计算阵列的第二输入端口输入第二输入信号,其中,第一输入信号用于指示第一输入数据的绝对值,第二输入信号用于指示第一输入数据为负值。所述计算阵列用于基于第一输入信号和第二输入信号将第一输入数据与所述计算阵列中存储的第一权重值进行计算,得到第一计算结果。

17.从上述神经网络系统可以看出:由于计算阵列具有两个输入端口,第一输入端口可接收用于指示第一输入数据的绝对值的第一输入信号,第二输入端口可接收用于指示第一输入数据为负值的第二输入信号,故计算阵列在接收来自输入处理电路的第一输入信号和第二输入信号后,相当于接收到为负值的第一输入数据,进而计算阵列可对为负值的第一输入数据完成计算。因此,本实施例提供的神经网络系统可以直接接收负值的输入数据,并对为负值的输入数据完成计算,从而可以减少计算次数,提升计算效率,节省计算资源,降低计算成本。

18.在一种可能实现的方式中,所述输入处理电路还用于在确定第二输入数据为正值后,向计算阵列的第一输入端口输入第三输入信号,并向计算阵列的第二输入端口输入第

四输入信号,其中第三输入信号用于指示第二输入数据的绝对值,第四输入信号用于指示第二输入数据为正值。所述计算阵列还用于基于第三输入信号和第四输入信号将第二输入数据与计算阵列中存储的第二权重值进行计算,得到第二计算结果。

19.通过上述实现方式,计算阵列既可以实现对为负值的输入数据的计算,也可实现对为正值的输入数据的计算。

20.在一种可能实现的方式中,所述计算阵列包括第一计算单元和第二计算单元,其中,所述第一计算单元和所述第二计算单元连接计算阵列中的第一位线。所述第一计算单元用于基于第一输入信号和第二输入信号将第一输入数据与计算阵列中存储的第一权重值进行计算,得到第一计算结果。所述第二计算单元用于基于第三输入信号和第四输入信号将第二输入数据与计算阵列中存储的第二权重值进行计算,得到第二计算结果。所述计算阵列还用于输出第一输出信号,第一输出信号用于指示连接第一位线的多个计算单元的计算结果,其中多个计算单元的计算结果包括第一计算结果和第二计算结果。

21.在一种可能实现的方式中,所述计算阵列包括多个计算单元,每个计算单元包括至少一个铁电场效应管。

22.上述实现方式中,计算阵列可通过铁电场效应管实现,其中,铁电场效应管工作在亚阈值区,其输出电流小,功耗低,可以进一步节省计算成本。

23.在一种可能实现的方式中,同一列计算单元中的场效应管的漏极连接同一根位线,同一行计算单元中的场效应管的栅极连接至同一根字线,同一行场效应管的源极连接至同一根源极线。

24.在一种可能实现的方式中,所述计算阵列还包括多个参考单元,每个参考单元包括至少一个铁电场效应管。位于同一行的一个参考单元和一个计算单元可构成电流镜。

25.从以上技术方案可以看出,本技术实施例提供的计算装置及神经网络系统中,由于计算阵列具有两个输入端口,第一输入端口可接收用于指示第一输入数据的绝对值的第一输入信号,第二输入端口可接收用于指示第一输入数据为负值的第二输入信号,故计算阵列在接收来自输入处理电路的第一输入信号和第二输入信号后,相当于接收到为负值的第一输入数据,进而计算阵列可对为负值的第一输入数据完成计算。因此,本技术提供的计算装置可以直接接收负值的输入数据,并对为负值的输入数据完成计算,从而可以减少计算次数,提升计算效率,节省计算资源,降低计算成本。

附图说明

26.图1为本技术实施例提供的神经网络系统的一个结构示意图;

27.图2为本技术实施例提供的计算装置的一个结构示意图;

28.图3为本技术实施例提供的权重数据的一个示意图;

29.图4为本技术实施例提供的计算装置的应用例示意图。

具体实施方式

30.本技术实施例提供了一种计算装置及神经网络系统。神经网络也可以称为人工神经网络(artificial neural network,ann),或者类神经网络,在机器学习和认知科学领域,是一种模仿生物神经网络(动物的中枢神经系统,特别是大脑)的结构和功能的数学模

型或计算模型,用于对函数进行估计或近似。人工神经网络可以包括卷积神经网络(convolutional neural network,cnn)、深度神经网络(deep neural network,dnn)、多层感知器(multilayer perceptron,mlp)等神经网络。

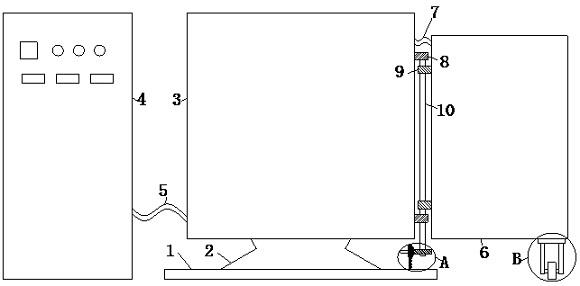

31.图1为本技术实施例提供的神经网络系统的一个结构示意图。如图1所示,神经网络系统100可以包括主机110以及神经网络电路120。神经网络电路120通过主机接口与主机110连接。主机接口可以包括标准的主机接口以及网络接口(network interface)。例如,主机接口可以包括快捷外设互联标准(peripheral component interconnect express,pcie)接口。如图1所示,神经网络电路120可以通过pcie总线130与主机110连接。因此,数据可以通过pcie总线130输入至神经网络电路120中,并通过pcie总线130接收神经网络电路120处理完成后的数据。并且,主机110也可以通过主机接口监测神经网络电路120的工作状态。

32.主机110可以包括处理器1102以及内存1104。应理解,除了图1所示的器件外,主机110还可以包括通信接口以及作为外存的磁盘等其他器件(图1中未示出),在此不做限制。

33.处理器(processor)1102是主机110的运算核心和控制核心(control unit)。处理器1102中可以包括多个处理器核(core)。处理器1102可以是一块超大规模的集成电路。在处理器1102中安装有操作系统和其他软件程序,从而处理器1102能够实现对内存1104、缓存、磁盘及外设设备(如图1中的神经网络电路)的访问。可以理解的是,在本技术实施例中,处理器1102中的core例如可以是中央处理器(central processing unit,cpu),还可以是其他特定集成电路(application specific integrated circuit,asic)。

34.内存1104是主机110的主存。内存1104通过双倍速率(double data rate,ddr)总线和处理器1102相连。内存1104通常用来存放操作系统中各种正在运行的软件、输入和输出数据以及与外存交换的信息等。为了提高处理器1102的访问速度,内存1104需要具备访问速度快的优点。在传统的计算机系统架构中,通常采用动态随机存取存储器(dynamic random access memory,dram)作为内存1104。处理器1102能够通过内存控制器(图1中未示出)高速访问内存1104,对内存1104中的任意一个存储单元进行读操作和写操作。在本发明实施例中,内存1104可以用来存储待进行神经网络计算的输入数据。

35.神经网络电路120是由多个神经网络芯片(chip)组成的芯片阵列。例如,如图1所示,神经网络电路120包括多个进行数据处理的神经网络芯片(chip)1201。为了描述方便,将本技术中的神经网络芯片1201简称为芯片1201。在神经网络电路120中,所述多个芯片1201相互连接,例如,某一个芯片1201可与相邻的一个或多个芯片1201连接。芯片1201之间可以进行数据传输。

36.神经网络系统可以包括多个神经网络层,在图1中仅示出了一个神经网络层,每个神经网络层可以通过输入端口1203输入数据,然后通过输出端口1204输出其计算结果至下一个神经网络层。在本技术实施例中,神经网络层为逻辑的层概念,神经网络层可以包括卷积层、池化层等(图1中未示出)。一个神经网络层是指要执行一次神经网络操作。

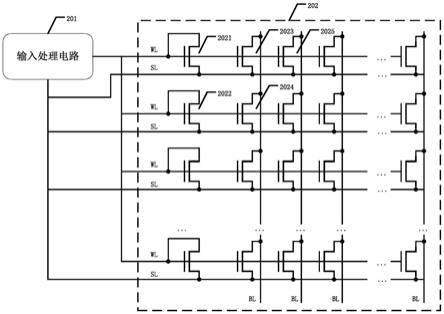

37.图2为本技术实施例提供的计算装置的一个结构示意图。需要说明的是,图2所示的计算装置可以是指图1中的神经网络芯片1201,也可以是神经网络芯片1201的一部分,此处不做限制。如图2所示,芯片1201中的计算装置包括:输入处理电路201和至少一个计算阵列202,输入处理电路201与计算阵列202连接。为了便于作图和说明,图2中仅示意出一个计

算阵列202,且下文以计算装置包含一个计算阵列202为例子进行介绍。计算阵列202目前采用的是存算一体交叉阵列架构,例如,可以是嵌入式闪存(embedded flash,eflash)crossbar或者非易失闪存(nor flash)crossbar或者阻变存储器(resistive random-access memory,reram)crossbar等,神经网络的权重数据可以在计算之前配置到计算阵列202中。当输入数据经过输入处理电路201和计算阵列202的处理后,则可以直接发送给下一个神经网络层进行流水线计算。

38.计算阵列202包含以阵列形式进行构建的多个存储单元,存储单元可包含至少一个存储器件,例如eflash或者nor flash或者reram或者铁电场效应管(ferroelectric field-effect transistor,fefet)等。为了便于说明,下文将以一个存储单元包含一个fefet进行介绍。需要说明的是,本技术实施例中的fefet通常工作于亚阈值区。此种情况指,fefet的栅极电压接近阈值电压,fefet的源极与漏极之间会有微弱的电流,该电流称为亚阈值电流,与栅极电压为指数关系。此时,fefet的输出电流小,功耗低,有利于节省计算成本。

39.如图2所示,计算阵列202为一个包含n行m列fefet的阵列。计算阵列202中,第1列fefet(即图2中的最左列fefet)中的每一个fefet可作为计算阵列202的参考单元。第2列fefet至第m列fefet中,每一个fefet可作为计算阵列202的计算单元。具体地,同一列参考单元的fefet的漏极与栅极连接,同一列计算单元的fefet的漏极连接至同一根位线(bit line,bl),同一行计算单元的fefet的栅极连接至同一根字线(word line,wl),同一行fefet的源极连接至同一根源极线(source line,sl)。值得注意的是,计算阵列202的所有wl即为计算阵列202的第一输入端口,计算阵列202的所有sl即为计算阵列202的第二输入端口,计算阵列202的所有bl即为计算阵列202的输出端口。

40.基于前述多个fefet的连接关系,位于同一行的一个参考单元与一个计算单元可构成电流镜,例如,图2中的第一参考单元2021与第一计算单元2023可构成一个电流镜,第二参考单元2022与第二计算单元2024可构成一个电流镜,第一参考单元2021与第三计算单元2025可构成一个电流镜等等。应理解,图2中仅以最左列的fefet为参考单元进行示意性说明,在实际应用中,计算阵列202的任意一列fefet均可作为参考单元,此处不做限制。

41.此外,权重数据通常用于表示输入数据对于输出数据的重要程度。在神经网络中,权重数据通常用一个实数矩阵表示。图3为本技术实施例提供的权重数据的一个示意图。如图3所示,权重数据为一个n行m列的矩阵,该矩阵中的每一个元素代表一个权重值。应理解,一个神经网络层可以包括如图3所示的一个或多个权重数据,此处不做限制。

42.在本技术实施例中,计算单元的权重可以提前配置完成。具体地,一个权重矩阵中的每个元素被配置在对应的计算阵列202的计算单元中,从而,可以通过计算阵列202对输入数据与配置的权重值进行计算。在配置过程中,可将图3所示的权重数据配置到图2所示的计算阵列202中,使得每个权重值被配置到相应的计算单元中。例如,图3的元素w

0,0

被配置到图3的第一计算单元2023中,图3的元素w

1,0

被配置到图2的第二计算单元2024中,图3的元素w0,1被配置到图2的第三计算单元2025中等。权重矩阵中的每一个元素对应一个计算单元,在配置完成后,计算阵列202则存储(被配置)有每个计算单元所对应的权重值。

43.在配置完成后,计算装置可进行神经网络计算。具体地,输入处理电路201在接收来自处理器1102的输入数据后,可对输入数据进行预处理。输入处理电路201可为数字电

路,其对输入数据进行处理后,处理结果可通过数模转换器(digital-to-analog converter,dac)转换为电压信号,输入到计算阵列202中。由于该处理结果可用于指示输入数据,故计算阵列202可根据输入数据与计算阵列存储的权重值进行计算,得到计算结果。该计算结果可经过偏置处理,并通过模数转换器(analog-to-digital converter,adc)转换为数字信号,作为计算阵列202最终的输出信号。

44.为了进一步理解,以下将结合图2对前述计算过程作进一步的介绍。

45.如图2所示,第一计算单元2023与第二计算单元2024连接于第一bl(在图2中按从左往右的顺序,设第一bl为所有bl中的第一根bl)。输入处理电路201确定第一输入数据为负值后,则生成第一输入信号和第二输入信号(均为电压信号),第一输入信号用于指示第一输入数据的绝对值,第二输入信号用于指示第一输入数据为负值。然后,输入处理电路201通过第一根wl(在图2中按从上往下的顺序,与第一行fefet连接的wl)将第一输入信号输入至第一行fefet,通过第一根sl(与第一行fefet连接的sl)将第二输入信号输入至第一行fefet。完成第一输入数据的输入操作后,可进行第二输入数据的输入操作。输入处理电路201确定第二输入数据为正值后,则生成第三输入信号和第四输入信号,第三输入信号用于指示第二输入数据的绝对值,第四输入信号用于指示第二输入数据为正值。然后输入处理电路201通过第二根wl将第三输入信号输入至第二行fefet,通过第二根sl将第四输入信号输入至第二行fefet。

46.除第一输入数据和第二输入数据外,还可有其余输入数据(例如第三输入数据、第四输入数据等等)需输入至计算阵列202中。其余输入数据在计算阵列202的输入位置为,除第一输入数据和第二输入数据所输入的fefet之外的其余fefet。例如,其余输入数据可输入至第三行fefet和/或第四行fefet等等。

47.在完成所有输入数据的输入操作后,则可进行输入数据的计算操作。具体地,第一计算单元2023在接收到第一输入信号和第二输入信号后(相当于接收到为负值的第一输入数据),则将第一输入数据与第一权重值(即计算阵列202存储的与第一计算单元2023对应的权重值)进行计算,得到第一计算结果。第二计算单元2024在接收到第三输入信号和第四输入信号后(相当于接收到为正值的第二输入数据),则将第二输入数据与第二权重值(即计算阵列202存储的与第二计算单元2024对应的权重值)进行计算,得到第二计算结果。同理,还可得到其余计算结果,即连接第一bl的多个计算单元中,除第一计算单元2023、第二计算单元2024外的其余计算单元对其余输入数据进行计算所得到的结果。

48.当第一bl的计算单元完成计算操作后,第一bl可输出第一输出信号。第一输出信号用于指示连接于第一bl的多个计算单元的计算结果,不仅包含第一计算结果和第二计算结果,还可包含其余计算结果。此外,其余bl(例如第二bl、第三bl等等)的相应计算单元也可执行如前述的计算操作,使得其余bl也可输出相应的输出信号,此处不再赘述。

49.本技术实施例中,由于计算阵列202具有两个输入端口,第一输入端口可接收用于指示第一输入数据的绝对值的第一输入信号,第二输入端口可接收用于指示第一输入数据为负值的第二输入信号,故计算阵列202在接收来自输入处理电路的第一输入信号和第二输入信号后,相当于接收到为负值的第一输入数据,进而计算阵列可对为负值的第一输入数据完成计算。因此,本技术实施例提供的计算装置可以直接接收负值的输入数据,并对为负值的输入数据完成计算,从而可以减少计算次数,提升计算效率,节省计算资源,降低计

算成本。

50.为了更进一步地理解,以下将结合一个应用例对本技术实施例提供的计算装置作进一步的介绍。图4为本技术实施例提供的计算装置的应用例示意图,如图4所示,计算装置包括:输入处理电路201和计算阵列202。

51.计算阵列202包括:n

×

m个阈值电压可变的fefet,需要说明的是,计算阵列202的一个计算单元包含一个fefet。其中,同一列fefet的漏极连接至同一根bl,同一行fefet的栅极连接至同一根wl,同一行fefet的源极连接至同一根sl,第k列fefet的漏极与栅极连接(图4中以k=1进行示意性说明)。n≥1,m≥2,k=1,2,...,m,i=1,2,...,n。

52.输入处理电路201包括:输入判断单元2011、输入处理单元2012和电位设置单元2013。输入判断单元2011分别和输入处理单元2012、电位设置单元2013连接。输入处理单元2012的输出端与计算阵列202的所有wl连接,电位设置单元2013的输出端与计算阵列202的所有sl连接。

53.设有n个输入数据需在计算阵列202上实现乘加计算。下面将对n个输入数据如何输入至计算阵列的过程进行说明。以第i个输入数据为例,第i个输入数据可输入至输入判断单元2011、输入处理单元2012以及电位设置单元2013。此外,伴随着第i个输入数据输入至输入处理单元2012以及电位设置单元2013,还可有第i个地址信号输入至输入处理单元2012以及电位设置单元2013,第i个地址信号用于指示第i行fefet。

54.输入判断单元2011接收第i个输入数据后,则先判断第i个输入数据的正负。在确定第i个输入数据的正负后,输入判断单元2011则根据第i个输入数据的正负生成第i个判断信号,并将第i个判断信号发送至输入处理单元2012和电位设置电路2013,第i个判断信号用于向输入处理单元2012和电位设置电路2013通知第i个输入数据的正负。

55.输入处理单元2012接收第i个输入数据、第i个判断信号和第i个地址信号后,则基于第i个判断信号确定第i个输入数据的正负。若第i个输入数据为负值,输入处理单元2012则生成第i个输入信号(即对第i个输入数据取绝对值,并基于第i个输入数据的绝对值生成第i个输入信号),并基于第i个地址信号,通过第i根wl将取第i个输入信号发送至第i行fefet。若第i个输入数据为正值,输入处理单元2012则生成第i个输入信号(即基于第i个输入数据生成第i个输入信号),并基于第i个地址信号,通过第i根wl将取第i个输入信号发送至第i行fefet。

56.电位设置单元2013接收第i个输入数据、第i个判断信号和第i个地址信号后,则基于第i个判断信号确定第i个输入数据的正负。若第i个输入数据为负值,电位设置单元2013则生成第i 1个输入信号,并基于第i个地址信号,通过第i根sl将第i 1个输入信号发送至第i行fefet,第i 1个输入信号用于将第i行fefet的源极电位设置为负电位。若第i个输入数据为正值,电位设置单元2013则生成第i 1个输入信号,并基于第i个地址信号,通过第i根sl将第i 1个输入信号发送至第i行fefet,第i 1个输入信号用于将第i行fefet的源极电位设置为正电位。可以理解的是,若第i行fefet的源极电位设置为正电位,则相当于输入至第i行fefet的第i个输入数据为正值。若第i行fefet的源极电位设置为负电位,则相当于输入至第i行fefet的第i个输入数据为负值。

57.在将第i个输入数据输入至计算阵列202后,可继续进行第i 1个输入数据的输入,直至完成n个输入数据的输入。计算阵列202在n行fefet均接收到相应的输入数据后,则根

据n个输入数据进行计算,最后通过除第k根bl外的其余bl输出m-1个输出信号。

58.值得注意的是,在m-1个输出信号中,第j个输出信号为:

59.o

j

=∑w

j,i

i

i-∑w

j,i

i

i

,

60.其中,o

j

为第j个输出信号;w

i,j

为第i行第j列fefet的权重值;若第i个输入数据为负值,则第i个输入数据记为-i

i

,若第i个输入数据为正值,则第i个输入数据记为i

i

;v

i,k

为第i行中第k个fefet的阈值电压;v

i,j

为第i行中第j个fefet的阈值电压;v

t

为预置电压参数,室温下约等于26mv;β为亚阈值斜率。

61.此外,输入判断单元2011、输入处理单元2012和电位设置单元2013通常为数字电路。本应用例中的计算装置可在计算阵列202和输入处理单元2012之间设置dac203。dac203用于将来自输入处理单元2012对输入数据的处理结果转换为电压信号(即前述的输入信号),再将电压信号发送至计算阵列202。

62.更进一步地,计算装置还包括adc204。adc204与计算阵列202中的bl连接,以将计算阵列202输出的m-1个输出信号转换为数字信号,供外部的目标数字电路使用。

63.本领域的技术人员可以清楚地了解到,为了描述的方便和简洁,上述描述的装置和设备的具体工作过程以及产生的技术效果,可以参考前述方法实施例中对应的过程和技术效果,在此不再赘述。

64.在本技术所提供的几个实施例中,所揭露的系统、装置和方法,可以通过其它的方式实现。例如,以上所描述的方法实施例的一些特征可以忽略,或不执行。以上所描述的装置实施例仅仅是示意性的,单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,多个单元或组件可以结合或者可以集成到另一个系统。另外,各单元之间的耦合或各个组件之间的耦合可以是直接耦合,也可以是间接耦合,上述耦合包括电的、机械的或其它形式的连接。

65.应理解,在本技术的各种实施例中,各过程的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本技术的实施例的实施过程构成任何限定。

66.另外,本文中术语“系统”和“网络”在本文中常被可互换使用。本文中的术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本文中字符“/”,一般表示前后关联对象是一种“或”的关系。

67.总之,以上所述仅为本技术技术方案的较佳实施例而已,并非用于限定本技术的保护范围。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。