1.本发明涉及用于二进制加权分压器电路的补偿。

背景技术:

2.加权分压器,诸如二进制加权分压器和阵列分压器,响应于数字二进制命令来使用开关设置以设置精确的模拟电压。开关设置选择分压器中的不同电阻器组合以调整模拟电压的期望值。用于此种电压设置的一个示例应用涉及设置直流(dc/dc)转换器的输出电压准确度,该准确度可以被控制在用于转换器的输出电压(vout)的范围内(例如,

±

1%)。例如,输出电压可由电阻分压器设置,该电阻分压器可连接到输出电压dc/dc转换器引脚vout、dc/dc转换器误差放大器反馈引脚和接地。通常,输出电压可以以小的电压步长改变,而输出电压范围很宽。通过选择启用或禁用分压器中的电阻器的开关来改变电阻分压器中的电阻值,就可以调整电压。如果电压步长是25毫伏(mv),并且如果转换器的电压范围例如是1.825v至5v,那么在该范围内可以指定转换器输出电压的128个可能值(7位)。电阻分压器不仅用于设置dc/dc转换器输出电压,它们还用于微调应用,诸如提供可编程的参考电压、可编程的偏置电流等。

技术实现要素:

3.在一个示例中,一种电路包括二进制加权分压器,该分压器具有在输入节点和反馈节点之间串联耦合的第一组开关。第一组开关被配置为响应于激活或停用第一组开关中的相应开关,在反馈节点处设置反馈电压。一组补偿开关耦合到第一组开关。该组补偿开关被配置为通过激活该组补偿开关中的一个或更多个开关为第一组开关中的被激活的相应开关中的每个提供一个或更多个相应的并联电流路径,来减小第一组开关中的被激活的相应开关中的一个或更多个的电阻。

4.在另一个示例中,一种装置包括在第一节点和第二节点之间耦合的第一电阻器。第一开关在第一节点和第二节点之间与第一电阻器并联耦合。第二电阻器在第二节点和第三节点之间耦合。第二开关在第二节点和第三节点之间与第二电阻器并联耦合。第三开关在第一节点和第二节点之间耦合。第四开关在第二节点和第三节点之间耦合。具有第一输入端的放大器耦合到第三节点和第二输入端,该第二输入端适合耦合到参考电压。放大器具有耦合到第一节点的输出端。

5.在又一个示例中,一种系统包括二进制加权分压器,其具有电阻器网络,该电阻器网络包括在输入节点和反馈节点之间串联耦合的n个加权电阻器的序列。第一组开关在输入节点和反馈节点之间串联耦合。第一组开关被配置为响应于激活或停用第一组开关中的相应开关,在反馈节点处设置反馈电压。放大器被配置为基于参考电压和来自反馈节点的反馈电压向输入节点提供输入电压。一组补偿开关耦合到第一组开关。该组补偿开关被配置为通过激活该组补偿开关中的一个或更多个开关为第一组开关中的被激活的一个或更多个相应开关提供一个或更多个相应的并联电流路径,来减小第一组开关中的被激活的相

应开关中的一个或更多个的电阻。控制逻辑电路被配置为基于指定二进制加权分压器的电阻的输入码,控制第一组开关和该组补偿开关的激活和停用。

附图说明

6.图1示出了电阻分压器电路。

7.图2示出了另一种类型的电阻分压器。

8.图3示出了包括补偿网络以减小二进制加权分压器的开关电阻的电路的示例框图。

9.图4示出了包括补偿开关网络以减小二进制加权分压器的开关电阻的示例电路。

10.图5示出了系统的示例实施例,其包括补偿开关网络以减小二进制加权分压器的开关电阻。

11.图6示出了控制图5的电路中的开关的控制逻辑电路的示例。

12.图7示出了电压误差作为输入码的函数的图示,表明与图2的现有二进制加权分压器相比,包括补偿开关网络的二进制加权分压器的提高的准确度,其中改进的分压器和现有分压器之间的总集成电路开关面积大约相同。

13.图8示出了电压误差作为输入码的函数的图示,表明与图2的现有二进制加权分压器相比,包括补偿开关网络的二进制加权分压器的提高的准确度,其中为现有分压器实施的总集成电路开关面积大于改进的分压器。

14.图9示出了针对使用补偿开关网络的二进制加权分压器的不同样品的电压误差作为输入码的函数的图示。

15.图10示出了包括二进制加权分压器的dc

‑

dc转换器的示例。

具体实施方式

16.本说明书涉及用于二进制加权分压器的阻抗补偿。例如,包括二进制加权分压器的电路可以包括补偿开关网络,其被配置为减小二进制加权分压器中的被激活开关的开关电阻。减小激活开关的开关电阻允许分压器中的选定电阻器更准确地反映其相关联的电阻值,同时相比现有分压器受开关电阻的影响较小。因此,与现有类型的分压器电路相比,补偿开关网络提高了分压器的准确度。与具有类似性能的现有分压器电路相比,补偿开关网络还能减少用于分压器电路的集成电路管芯面积。因为现在可以使用较小的开关(其具有的开关电阻比现有分压器电路中通常使用的较大开关大),所以可以使用较小的管芯面积,因为该较小开关的相应电阻被补偿开关网络减小。因此,补偿开关网络通过提供通过相应补偿开关的并联电流路径,减小了分压器中的激活开关的总电阻。补偿开关网络还可以减少现有分压器电路中的寄生电容,因为较小开关和最小开关配置可以在较小面积中为分压器实施。此外,与现有类型的阵列分压器电路(其实施指数级数量的开关和电阻器,取决于所采用的位数)相比,如本文中所述的二进制加权分压器和补偿网络可以使用比现有阵列分压器电路更少数量的电阻器和开关来实施,同时仍然提供与现有阵列分压器电路类似或改进的最低有效位准确度。

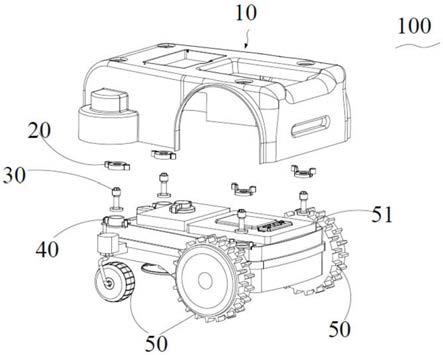

17.为了表明本文中所述的补偿开关网络的好处,图1和图2示出了不包括如本文中所述的用于分压器的补偿的现有类型的电阻分压器。图1示出了包括阵列分压器的电路100,

并且图2示出了包括二进制加权分压器的电路200。电路100或电路200都没有采用如本文中所述的补偿开关网络。

18.参考图1,电路100包括提供输出电压vout的放大器110。输出电压vout被反馈回到电阻分压器120的输入端,该电阻分压器包括电阻器r1至rn,其中n为正整数。通过控制相应的开关s1至sn,可以选择或取消选择电阻分压器120中的相应电阻器。控制连接在输入端和输出端之间的电阻器的这些开关缩放施加到放大器110的负输入端的输出电压vout的量,负输入端示出为v

‑

。放大器的正输入端与参考电压vin相连,根据选择的开关s1至sn从该参考电压vin调整输出vout。

19.输出电压vout可以根据公式vout=vin*(rtotal/rin)来描述,其中rin是从放大器110的节点v

‑

至接地观察的电阻之和,并且rtotal是从rn至接地观察的分压器电阻之和(rtotal=r1 r2

…

rn)。在图1中,开关s1至sn的一侧串联连接到放大器110高阻抗输入节点v

‑

。该阵列分压器方法减轻了开关对vout的影响,但缺点是电阻器(r1至rn)可能提供vout的非线性缩放以提供各种输出电压组合。在具有电阻值相等(r1=r2=r3=r4=r)的4个电阻器的2位分压器的示例中,rtotal=4r,并且取决于输入码,rin可以是rin=[r、2r、3r和4r],这意味着vout可以是v

out

=[4vin、2vin、4/3vin和vin]。从该2位示例看出,显然电路100的分压器不是线性的,其中不支持vout=3vin。

[0020]

除了非线性行为外,电路100的另一个缺点是涉及大量的开关。例如,分压器中的开关数量与位数成指数比例,其中电阻器和开关的总数量为2

n

,并且n为位数。由于有大量的开关来为vout选择期望的电压值,其中每个电阻都有一个开关,而开关的数量按照分压器中的位数成指数增长,因此,实施电路100的对应集成电路管芯面积往往比图2中的二进制加权分压器大得多,这继而增加了电路100的成本。

[0021]

图2的电路200示出了二进制加权分压器电路。该电路200克服了图1的电路100的问题中的一些,诸如非线性操作和大量的电阻器和开关来调整vout。在该示例中,相应开关的尺寸大,具有大的长度和宽度参数以减小开关电阻,以便具有小电阻,并且以便不影响分压器的准确度。然而,当开关过大时,开关寄生电容可能增加并降低分压器的性能,因为不需要的信号可能通过寄生电容耦合。电路200包括放大器210,其生成vout并驱动表示二进制加权电阻器的电阻分压器220,该电阻器的电阻器段为串联连接的r、2r、4r、...、2

n

‑1r,其中r是单位电阻器。

[0022]

改变电路200中的电阻值可以通过选择金属氧化物半导体(mos)开关来执行,该开关使电阻分压器220中的一个或更多个电阻器段(r、2r、4r、...、2

n

‑1r)短路。然而,mos开关也具有相对较高的电阻。在一个以上的mos开关处于活动状态的情况下,开关电阻被加在一起以在电阻分压器220的结果分压率中引入不准确度。不准确度对于分压器的最低有效位(lsb)更加明显,其中开关的电阻与lsb电阻器段(例如r或2r)串联连接,在电阻分压器220中具有最小值。例如,在7位二进制加权分压器的情况下,当除lsb(最低有效位)外的所有开关都处于活动状态时,最坏情况下的不准确度可以确定,因为电阻分压器220的总电阻是6个开关的电阻加上单位电阻器的电阻r之和。在实践中,单位电阻器r不应该太大,因为最高有效位(msb)是(2

n

‑1)*r。例如,7位msb分压器会是64r,这导致分压器所占的集成电路管芯面积大。

[0023]

本文中所述的补偿开关网络和二进制加权分压器(例如,见图3至图6)克服了电路

100和电路200两者的不足之处。通过在分压器电路中采用二进制加权分压器和补偿开关网络,如本文中所述,可以减小分压器电路中的非线性与巨大开关组合和电阻器管芯面积,因为可以采用较少数量的线性电阻器和开关组合来调整vout。例如,在5位示例中,实施二进制加权分压器和补偿开关网络的开关总数为15个,而在图1的电路100的阵列分压器中,实施了32个开关以提供5位分压器。此外,二进制加权分压器的最低有效位的准确度比图2所示的电路200有所改进,因为本文中所述的补偿开关网络被配置为激活补偿开关以提供并联电流路径,从而减小电阻分压器中激活开关的电阻。补偿开关网络还允许在二进制加权分压器中以较小的管芯面积实施选择开关,以减少寄生电容,并允许在现有二进制加权分压器电路的基础上减少集成电路实施成本。

[0024]

如本文中所用,术语“电路”可以包括执行电路功能的有源和/或无源元件的集合,诸如模拟电路或数字电路。此外或可替代地,例如,术语“电路”可以包括ic,其中电路元件中的全部或一些制造在共同衬底(例如,半导体衬底,诸如管芯或集成电路芯片)上,诸如本文中所述。例如,电路和/或相关联的控制电路系统可以作为相应的ic芯片或在多芯片模块内实施。控制逻辑电路可以包括被配置为执行控制功能的分立部件。在其他示例中,控制逻辑电路可以包括控制器、处理器、数字信号处理器或门阵列。

[0025]

而且,术语“耦合”可涵盖使功能关系与本说明书的描述一致的连接、通信或信号路径。例如,如果装置a生成信号以控制装置b来执行动作,则在第一示例中,装置a耦合到装置b,或者在第二示例中,如果干预部件c没有实质性地改变装置a和装置b之间的功能关系,则装置a通过干预部件c耦合到装置b,使得装置b经由装置a生成的控制信号被装置a控制。

[0026]

图3示出了电路300的示例,该电路包括被配置为减小二进制加权分压器320的开关电阻的补偿开关网络310。二进制加权分压器320包括第一开关网络330,该网络具有在输入节点340和反馈节点350之间串联耦合的第一组开关。第一开关网络330中的第一组开关被配置为响应于激活或停用第一组开关中的相应开关,在反馈节点350处设置反馈电压。例如,将输入码诸如指定电阻器控制码的二进制字施加到第一开关网络330中的第一组开关的输入端子,以选择激活和停用哪些开关,并由此设置输入节点340和反馈节点350之间的二进制加权分压器320的电阻。

[0027]

补偿开关网络310包括与第一开关网络330中的第一组开关耦合的一组补偿开关。该组补偿开关被配置为通过激活该组补偿开关中的一个或更多个开关而减小被激活的第一组开关中的相应开关中的一个或更多个的电阻。补偿网络中的激活开关为第一组开关中的被激活的开关中的每个提供一个或更多个相应的并联电流路径。通过基于第一开关网络330中的激活开关来激活补偿开关,通过补偿开关网络310中的开关为第一组开关中的被激活的相应开关建立一个或更多个并联电流路径,以减小第一开关网络中的激活开关的电阻。通过用补偿开关网络减小第一开关网络330的开关电阻,二进制加权分压器320的准确度得到改进,同时也允许在分压器中实施具有较大电阻值的较小开关。因此,与现有的分压器电路(例如图1和图2)相比,电路300中的整体集成电路管芯面积可以减小。

[0028]

例如,类似于并联电阻器网络,补偿开关网络310提供与第一开关网络330中的激活开关的开关电阻并联的并联开关电阻。这允许来自输入节点340的电流流经第一开关网络330和补偿开关网络310两者中的激活开关。因此,这些并联的开关电路充当分流器。因此,开关(各自具有相应开关电阻)被连接,使得从共同的电压源(例如,来自输入节点340处

的vin的电压)建立一个以上的电流路径,这减小了第一开关网络330中的被激活的相应开关的有效开关电阻。因此,基于补偿开关网络310被激活的等效电阻被减小,类似于在并联电阻器网络中添加并联电阻器。通过向流经第一开关网络330中的激活开关的电流提供一个或更多个相应的并联电流路径,总体开关电阻小于由给定的激活开关提供的最小电阻的电阻。

[0029]

在图3的示例中,二进制加权分压器320包括一组n个电阻器,示为r1、r2、r3至rn,其中n为大于二的正整数。这n个电阻器在输入节点340和反馈节点350之间串联耦合,并且其大小被设定,以具有从输入节点到反馈节点增加的电阻。因此,相应电阻器r1至rn被配置为使得串联耦合到输入节点340的第一电阻器具有比串联耦合到反馈节点350的后续电阻器低的电阻值。对于二进制加权分压器320的示例,r1的电阻值被设置为单位电阻值(例如,1k欧姆),并且在输入节点340和反馈节点350之间的电阻器序列中的每个后续电阻器的大小是该序列中紧接在前的电阻器的电阻值的两倍。如图所示,该组n个电阻器中的第一电阻器r1耦合到输入节点340以及电阻器r1与r2之间的中间节点。其他电阻器中的每个耦合在串联的连续中间节点之间,并且串联的最后电阻器rn耦合在先前中间节点和反馈节点350之间。第一开关网络330的第一组开关中的开关跨相应节点之间的该组n个电阻器中的相应电阻器耦合,如图1所示。

[0030]

用于指定第一开关网络中的开关设置的输入码可用于根据第一开关网络330的第一组开关中的相应开关中的哪些被激活,来激活补偿开关网络310的该组补偿开关中的一个或更多个补偿开关。例如,控制逻辑电路(参见例如图6)被配置为基于提供给该电路的输入二进制码来激活第一开关网络330和补偿开关网络310中的开关。控制逻辑电路采用输入码来设置电阻器控制码以激活第一开关网络330中的开关,并且还采用输入码来设置补偿码以激活补偿开关网络310中的开关。在示例中,电路100在电源转换器(例如,dc

‑

dc转换器)中实施,该转换器被配置为在一定电压电平下在节点处提供电压,该电压电平是基于开关网络330和310中的哪些开关被选择或取消选择(根据输入码)而准确设置的。下面的图4和图5示出了可用于实施二进制加权分压器320和补偿开关网络310的示例。

[0031]

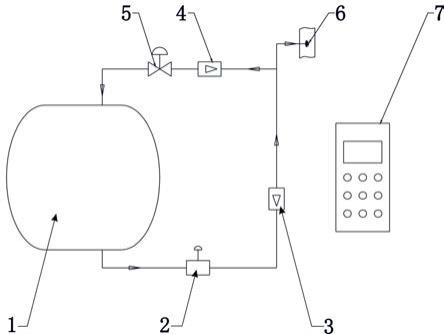

图4示出了示例电路400,其包括被配置为减小二进制加权分压器420的开关电阻的补偿开关网络410。二进制加权分压器420包括串联耦合并示为r1至rn的n个电阻器的序列。电阻器r1耦合到节点n1,该节点也耦合到接收电压vin的输入节点424。电阻器r1耦合在节点n1和随后的中间节点n2之间。电阻器r2耦合在节点n2和节点n3之间。电阻器r4耦合在节点n4和n5之间。电阻器rn在该示例中耦合在节点n5和最终节点nn之间,该最终节点也耦合到反馈节点430。电阻器r1以单位值为1的电阻值(例如,100ω、1kω或10kω)被加权,并且该序列中r1的每个后续的电阻器以该序列中在它之前的电阻器的电阻值的两倍被加权。例如,r2是r1的电阻值的两倍,r3是r2的电阻值的两倍,等等。第一开关网络440包括开关以基于哪些开关被选择(例如停用)以耦合序列中的电阻器,来选择二进制加权电阻值。补偿开关网络410包括补偿开关,其基于第一开关网络440中的哪些开关被激活而激活。

[0032]

如图所示,开关s1耦合到节点n1并跨电阻器r1耦合,并表示用于二进制加权分压器420的最低有效位设置。开关s2、s3、s4和sn也耦合到节点n1并被配置为补偿开关s1的开关电阻。因此,如果n=5表示5个电阻器和32位组合,则如果n=5,耦合到节点1的补偿开关将是补偿开关网络410中的开关s2、s3、s4和s5。每个后续节点包括的补偿开关比用于补偿

耦合到序列中前一节点的开关的补偿开关数量少一个。因此,在该示例中,如果n=5,则在节点n2处与电阻器r1串联耦合的电阻器r2采用开关sn 1(s6)作为其来自第一开关网络440的相应选择开关。

[0033]

耦合到节点n2的补偿开关被配置为补偿开关sn 1的电阻,并包括开关sn 2、sn 3,直至s2n

‑

1。如果像先前示例那样n=5,则第一开关网络440中的sn 1将是s6,sn 2将是s7,sn 3将是s8,并且sn 4将是s9。因此,对于五位示例,节点n2会有四个补偿开关,这比耦合到节点n1以补偿开关s1的电阻的五个开关少一个补偿开关。后续的节点n3、n4直至节点nn各自使用来自第一开关网络440的一个开关来选择二进制加权值,并对应地使用比先前节点少一个的所连接的补偿开关。以这种方式,可以用最少的开关数量来实施补偿开关的数量,同时仍然确保在补偿开关网络410中激活一个或更多个并联电流路径,以减小第一开关网络440中每个激活开关的电阻。

[0034]

如上所述,n个电阻器r1至rn的序列包括输入节点424和反馈节点430之间的每对相邻的电阻器之间的中间节点。如图所示,补偿开关网络410中的该组补偿开关包括在节点1处耦合到输入节点424的n

‑

1个补偿开关,其中n

‑

1个补偿开关中的每个都耦合在输入节点与中间节点和反馈节点430中的相应一个之间。耦合到电阻器序列中的每个中间节点的补偿开关的数量小于耦合到该序列中的先前节点的补偿开关的数量。在示例中,表示补偿开关网络和第一开关网络440中的该组补偿开关的开关的数量小于或等于n/2*(n 1),其中n表示电阻器序列中的电阻器的数量。

[0035]

图5示出了示例系统500,其采用补偿开关网络540来减小二进制加权分压器510的开关电阻。该系统500包括具有电阻器网络512的二进制加权分压器510,该电阻器网络包括在输入节点514和反馈节点516之间串联耦合的n个加权电阻器的序列。第一组开关(s1、s6、s10、s13和s15)520串联耦合在输入节点514和反馈节点516之间。在该示例中示出了5位分压器,其在电阻网络512中具有5个加权电阻器,但如本文中所述,多于或少于5位的配置是可能的。第一组开关520(n个开关)被配置为响应于激活或停用第一组开关中的相应开关而在反馈节点516处设置反馈电压。

[0036]

放大器530被配置为基于在参考输入端(放大器的 端子)处接收的示为vref的参考电压和在反馈输入端(放大器的

‑

端子)处接收的来自反馈节点516的反馈电压,从放大器输出端532向输入节点514提供输出电压vout。补偿开关网络540中的一组补偿开关(s2、s3、s4、s5、s7、s8、s9、s11、s12和s14)耦合到第一组开关520。补偿开关网络540中的该组补偿开关被配置为通过激活该组补偿开关中的一个或更多个开关为第一组开关中的被激活的一个或更多个相应开关提供一个或更多个相应的并联电流路径,来减小第一组开关520中的被激活的相应开关中的一个或更多个的电阻。

[0037]

控制逻辑电路550被配置为基于输入码554控制第一组开关520和补偿开关网络540中的该组补偿开关的激活和停用,以确定二进制加权分压器510的电阻。控制逻辑电路550包括适于接收输入码554的输入端。控制逻辑电路550被配置为基于输入码554生成电阻器控制码560,以控制第一组开关520来设置二进制加权分压器510的电阻。控制逻辑电路550进一步被配置为基于输入码554生成补偿码564,以激活补偿开关网络540中的补偿开关,从而为第一组开关520中的被激活的开关中的每个提供一个或更多个相应的并联电流路径,使得第一组开关中的激活开关的开关电阻减小。

[0038]

作为示例,输入码可以由用户确定,诸如从而设置跨分压器510(例如,节点514和516之间)的期望电压。例如,用户设置期望的输入码(例如,以设置期望电压),该输入码经由通信总线被传达给控制逻辑电路550。控制逻辑电路550被配置为解码输入码并计算第一组开关520和补偿开关网络540中的哪些开关将被激活(例如,短路)以设置分压器510的电阻。例如,输入码554是多位数字字,其为期望的输出电压电平的二进制表示。输入码可以是固定的,或可替代地在操作期间可以改变,诸如因此改变电压电平。控制逻辑电路550被配置为将554处的输入码解码为用于开关s1至s15中的每个的控制信号。

[0039]

对于图5的示例,控制逻辑电路550被配置为对输入码进行解码,如下所示:

[0040][0041][0042]

其中sx是用于开关x的控制信号,并且d[4:0]是在554处提供的输入码。控制逻辑电路550的示例关于图6被示出和描述。

[0043]

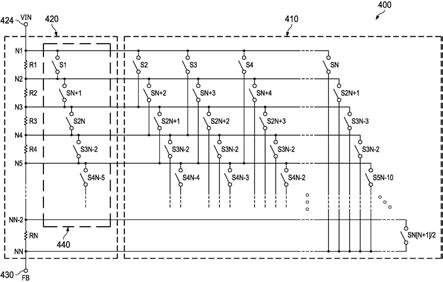

图6示出了被配置为控制诸如图5所示的补偿开关网络和二进制加权分压器电路的控制逻辑电路600。如本文中所用,控制逻辑电路600可以包括分立部件,其被配置为接收表示为二进制位d[0]、d[1]、d[2]、d[3]和d[4]的输入码,并基于输入码(例如,在554处的输入码)为图5的开关s1至s15生成控制信号c1至c15(例如,对应于信号560和564)。可替代地或额外地,控制逻辑电路600可以包括集成控制电路、控制器、微控制器、门阵列和/或处理器,它们执行机器可读指令以执行其控制功能,从而基于输入码生成相应的控制信号c1至c15。在该示例控制逻辑电路600中,示出了与门和反相器实施方式来执行控制功能。在其他示例中,控制逻辑电路600中所示的与门可以由或门代替,其中使用对应的非反相缓冲器来代替所示的反相器。在其他示例中,控制逻辑电路600中所示的分立逻辑可以被读取输入码并基于输入码生成对应控制信号c1至c15的控制器指令所代替。

[0044]

在示例控制逻辑电路600中,本文中所述的第一开关网络由控制信号c1、c6、c10、c13和c15控制。这些控制源自输入码,并定义电阻器控制码,以操作如本文中所述的第一开关网络(例如,330、420、510)的相应开关。控制信号c2、c3、c4、c5、c7、c8、c9、c11、c12和c14也源自输入码,并定义补偿控制码以操作本文中所述的补偿开关网络(例如310、410、540)的补偿开关。控制信号c1至c5统称为节点1控制,并控制开关的二进制加权分压器设置,该设置定义由开关s1选择的分压器的最低有效位用于补偿开关的对应的补偿开关控制c2、c3、c4和c5也连接到s1,并且也连接到本文中所述的输入节点。如本文中所述,序列中的每个后续节点使用少一个的补偿开关,并因此需要少一个的控制门来操作相应节点,诸如示为节点2控制、节点3控制、节点4控制和节点5控制的相应节点。

[0045]

如关于节点控制1所示,输入码d[0]驱动反相器i1以生成控制c1,其也被应用于门m1。门m1也接收来自i2的反相d[1]和来自i1的输出以生成控制信号c2,其被应用于门m2。门m2接收来自i3的反相d[2]并生成控制信号c3。门m3接收来自i4的反相d[3]和来自m2的输出以生成控制信号c4,其被应用于门m4。门m4接收来自i5的反相d[4]并生成控制信号c5。

[0046]

其他节点2至4中的每个被配置为与节点1类似地操作。例如,节点2控制包括反相器i6、i7、i8和i9以及门m5、m6和m7,它们被配置为响应于输入码d[1]、d[2]、d[3]和d[4]而生成控制信号c6、c7、c8和c9。节点3控制包括反相器i10、i11和i12以及门m8和m9,它们被配

置为响应于输入码d[2]、d[3]和d[4]而生成控制信号c10、c11和c12。节点4控制包括反相器i13和i14以及门m10,它们被配置为响应于输入码d[3]和d[4]而生成控制信号c13和c14。节点5控制包括反相器i15,其被配置为响应于输入码d[4]而生成控制信号c15。

[0047]

因此,控制逻辑电路600被配置为基于输入码,诸如从位d[0]到d[4]指定的输入码,控制第一组开关和该组补偿开关的激活和停用。控制逻辑电路600包括输入端,诸如分立逻辑输入电路或处理器输入电路。例如,输入码存储在寄存器或其他存储器装置中。因此,控制逻辑电路600适于接收输入码,并被配置为基于输入码生成电阻器控制码(例如,控制c1、c6、c10、c13和c15),以控制第一组开关来设置二进制加权分压器的电阻。例如,控制逻辑电路600被配置为根据第一组开关中的相应开关中的哪些被激活来激活该组补偿开关中的一个或更多个补偿开关,以减小激活开关的开关电阻。控制逻辑电路进一步被配置为基于输入码生成补偿码(例如,控制信号c2、c3、c4、c5、c7、c8、c9、c11、c12、c14和c15)以激活补偿开关,从而为第一组开关中的被激活的开关中的每个提供一个或更多个相应的并联电流路径,使得减小第一组开关中的激活开关的开关电阻。

[0048]

图7示出了电压误差作为输入码的函数的图示700,表明与提供曲线720并与图2的示例类似的现有二进制加权分压器相比,基于在曲线710处的包括补偿开关网络的二进制加权分压器的模拟结果的改进的准确度。在该比较中,用于改进的分压器和现有分压器实施方式中的每个的第一开关网络的总集成电路开关面积大约是相同的,曲线710和曲线720的模拟是由此生成的。在图示700的纵轴上,误差表示为百分比,并计算为verror=[(vbwd videal)/videal]*100%,其中vbwd表示基于开关选择和设置在其标注值之外的电阻器公差的在反馈节点处的二进制加权分压器电压,并且videal表示在电阻器按标注值模拟的理想条件下在分压器反馈节点处的理想电压输出。图示上的横轴表示各种分压器位输出设置,包括0、16、32......直至图示700上的横轴右侧上的128位分压器性能。

[0049]

如图所示,对于最低有效位0至16,在激活补偿开关的情况下生成的曲线710具有与不采用如本文中所述的补偿的曲线720相比的较低的输出电压误差百分比。例如,在横轴上的二进制设置为16的情况下,曲线710表明的电压误差百分比小于0.8%,而曲线720示出的电压误差百分比几乎为1.4%的误差。在横轴上设置为0时,采用补偿的曲线710略高于0.5%的误差,而没有采用补偿的曲线720示出超过1.8%的误差。

[0050]

图8示出了电压误差作为输入码的函数的图示800,表明与提供曲线820并与图2的示例类似的现有二进制加权分压器相比,基于在曲线810处的包括补偿开关网络的二进制加权分压器的模拟结果的改进的准确度。与图7所示的图示700相比,为现有分压器的第一开关网络实施的总集成电路开关面积大于为改进的分压器的第一开关网络采用的面积。与上述图示700类似,用于分压器的输出电压的误差百分比在纵轴上表示,其中生成相应输出电压的不同位设置在图示800的横轴上表示。

[0051]

如图所示,对于最低有效位0至16,在激活补偿开关的情况下生成的曲线810具有与不采用如本文中所述的补偿的曲线820相比的较低的输出电压误差百分比。例如在横轴上设置为0时,采用了补偿的曲线810的误差略高于0.5%,而没有使用补偿的曲线820示出了几乎1.6%的误差。注意在该示例中,用于生成曲线820的开关的开关面积比图7的720处所示的示例增加了25%,从而使分压器略有改进(例如,1.6%对比1.8%的误差)。然而,如图所示,曲线820改进了lsb性能,超过了试图通过实施更大的开关以减小其相应电阻来改

进准确度的现有实施方式。本文中描述的补偿开关网络允许第一开关网络和补偿开关网络两者中包含的开关的组合数量在较小的管芯中实施,而现有的分压器试图通过实施较大的开关来改进准确度。

[0052]

图9示出了图示900,其描绘了用于区分使用补偿开关网络的二进制加权分压器的制造样品的输出电压准确度。在该示例中,使用补偿开关网络的二进制加权分压器的实际生产样品被表示出来,并在85摄氏度的温度下测量。在曲线910、曲线920、曲线930和曲线940上表示的四个不同样品被测量,示出了纵轴上的输出电压误差百分比与横轴上的二进制设置。曲线910、曲线920、曲线、930和曲线940上示出的测量结果中的每个在纵轴上的测量误差百分比都比图7和图8的曲线中描绘的最坏情况下的模拟结果更低。

[0053]

图10示出了包括二进制加权分压器系统1002的dc

‑

dc转换器1000的示例。例如,二进制加权分压器系统1002可以根据本文中所述的实例,包括图3的系统300、图4的系统400或图5的系统500来实施。二进制加权分压器系统1002包括耦合在节点1006和1008之间的一串电阻器1004。二进制加权分压器系统1002被配置为响应于在1010处提供的输入码,设置节点1006和1008之间的电阻。在图5的示例中,电阻器中的每个具有表现为r、2r、4r、8r和16r的增加的电阻,其中r表示单位电阻值。

[0054]

节点1006耦合到dc

‑

dc转换器1000的输出端子1012以提供对应的输出电压vout。在图10的示例中,节点1008连接到另一个端子1014,其可以耦合到电接地或另一个低电压。一个或更多个端子1016的布置可以提供通信端口,其被耦合以根据通信协议接收输入指令。作为示例,端子1016对应于i2c总线的端口,该总线被配置为将用户输入指令作为一系列脉冲提供给转换器1000的用户接口控制1018。

[0055]

用户接口控制1018被配置为将在端子1016处接收到的输入指令(例如,脉冲)转换为对应的输入码,诸如本文中所述。例如,用户控制接口1018被配置为从端子1016提取串行脉冲并将脉冲转换为对应的输入码数据(例如,多位二进制数据)。输入码可以是表示电阻器串1004的电阻和/或要在输出端子1012处提供的电压vout的多位二进制字。用户控制接口1018将输入码数据提供给分压器系统1002的分压器控制逻辑电路1020。例如,分压器控制逻辑1020对应于图5的控制逻辑电路550和图6的逻辑电路600。分压器控制逻辑1020被配置为将输入码转换为一组开关控制信号,这些信号被提供给二进制加权分压器系统1002中的多个开关中的每个。在图10的示例中,开关包括开关s1至s15,诸如关于图5所述。在其他示例中,可以使用不同数量和配置的开关,并将开关解码器逻辑适当地配置为向相应开关提供控制信号。因此,分压器控制逻辑1020决定哪一个或哪些开关(s1至s15)将基于输入码数据被短路。

[0056]

在图10的示例转换器1000中,在二进制加权分压器系统1002的最后一个电阻器(具有电阻16r)和输入电阻(rin)之间的接合点处的节点1022耦合到反馈电路1024的输入端。节点1022提供表示通过电阻器串1004的输出电压或电流的反馈信号。例如,反馈信号被提供给运算放大器(运放)1026的反相输入端。参考电压v

ref

被提供给运放1026的非反相输入端。运放1026的输出端连接到比较器1028的负输入端。电流传感器1030被配置为监测响应于输入电压vin而供应给输入端子1032的电流。电流传感器1030向比较器1028的正输入端供应感测电流的指示(例如,跨感测电阻器的电压——未示出)。比较器1028被配置为基于感测输入电流和运放1026的输出的比较,向电源开关控件1034提供比较器信号。在示例

中,用户接口控件1018还向电源开关控件1034的另一个输入端供应控制信号,诸如以选择性地启用或禁用电源开关控件电路1034。电源开关控件1034基于由比较器1028提供的比较器输出信号连接到驱动开关装置1036和1038。例如,开关装置1036和1038可以实施为金属氧化物半导体场效应晶体管(mosfet)开关装置。在其他示例中,不同类型的晶体管(例如,双极结晶体管、结栅场效应晶体管)可用于开关1036和1038。开关装置1036连接在端子1032和端子1040之间,并且开关装置1038连接在端子1042和输出端子1012之间。电感器(例如,外部电感器)1044可以连接在端子1040和1042之间。

[0057]

电源开关控件1034被配置为控制开关装置1036和1038(例如,通过被耦合以驱动mosfet装置的栅极的驱动电路)以通过电感器1044供应电流。因此,该电流通过二进制加权分压器系统1002提供,以基于二进制加权分压器的电阻在1012处产生对应的输出电压vout。如本文中所述,该电阻基于响应于在端子1016处接收的指令信号而供应给分压器控制逻辑1020的输入码而变化。如本文中所述,供应给1016的指令信号可随时间变化,并由此改变连接在二进制加权分压器系统的节点1006和1008之间的电阻。因此,dc

‑

dc转换器可被包封在模制封装材料(例如,热固性聚合物或热塑性材料)内,以形成集成电路芯片或多芯片封装结构1050。例如,封装结构1050可以包括端子1012、1014、1016、1032、1040和1042。因此,封装的端子1014、1016、1032适于接收相应的信号和电压电平以操作dc

‑

dc转换器1000,并且外部(或内部)电感器可以耦合到端子1040和1042。

[0058]

例如,dc

‑

dc转换器被设计成根据步长(例如,在范围vout=1.9v

‑

5v内,步长为100mv)产生在电压范围内的输出电压vout。5位分压器足以覆盖该范围,诸如图10的示例(以及图5和图6中)所示。在该5位示例中,输入码的范围从0(十进制)到31(十进制),使得当输入码为0(十进制)时,vout=1.9v,并且当输入码为31(十进制)时,vout=5v。用户控制接口1016接收信号脉冲,得到的信号脉冲包括表示期望的输出电压的输入指令。例如,端口1016与总线或控制寄存器耦合,以接收表示期望电压的信号。用户控制接口将在1016处收到的信号转换为多位码(例如,5位字)。响应于在1010处设置的输入码,分压器控制逻辑1020被配置为提供开关控制信号以控制哪些开关s1至s15将被短路和哪些将被打开。如本文中所述,与电阻器串1004的各个串联电阻器并联连接的辅助开关s2、s3、s4、s5、s7、s8、s9、s11、s12和s14的激活将减小分压器的开关电阻。当输入码(即开关电阻)被设置并且开关因此被激活和停用时,dcdc转换器中的反馈电路1024将以这样的方式调整vout,即反馈电压等于电压vref(例如,稳定的电压电平)。因此,反馈电路1024被配置为迫使电压vfb=vref。例如,电压vfb可以表示如下:

[0059]

vfb=rin/(rin sum_of_r)*vout,

[0060]

其中sum_of_r是从节点1006至1022观察的电阻之和。

[0061]

为了设置期望的vout,sum_of_r是根据输入码改变的。如本文中所述,由于运放,vfb=vref(例如,vfb被设置为固定的dc电压)。因为sum_of_r等于响应输入码而设置(例如,固定)的电阻,dc

‑

dc转换器1000的电源开关控件1034通过控制电流通过开关1036和1038来调整vout,以提供vfb=vref。该相同的反馈机制和分压器电路的使用可用于其他电源转换器。如本文中所述,二进制加权分压器系统1002因此可以改进要提供的期望电压,这被认为优于现有的分压器电路。二进制加权分压器系统1002可以根据应用要求在各种不同的电路拓扑结构和电源转换器中实施。

[0062]

在权利要求的范围内,在所描述的实施例中可以进行修改,并且其他实施例也是可能的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。