1.本发明涉及显示技术领域,具体涉及一种时钟信号线路、栅极驱动电路及显示面板。

背景技术:

2.栅极驱动电路在tft阵列基板上(gate driver onarray,简称goa),也就是利用现有的阵列(array)制程将栅极驱动电路制作在tft阵列基板上,以实现对栅极逐行扫描的驱动方式,该技术取代了传统的gate

‑

ic(栅极集成电路)进行驱动,节省了生产成本。goa电路包括goa驱动单元(circuit)和母线单元(busline),其中母线单元(busline)包括时钟(clock,ck)信号线等。由于goa技术本身具有低成本,低功耗,窄边框等优点,越来越多的面板生产商采用goa技术进行生产。

3.随着液晶面板goa技术的普及,产品解析度由4k转向8k,goa电路的ck信号线数量逐步增加(从8根增加到12根),未来4k、8k产品逐步成熟并导入dual

‑

gate或者tri

‑

gate后,goa电路的ck信号线数量将进一步增加。而随着ck信号线数量的增大,问题随之而来。

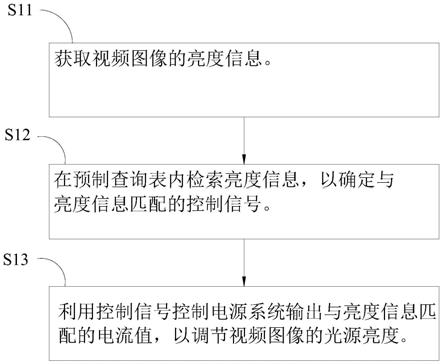

4.参见图1,现有技术中,ck信号线材料相同、线宽相等、电阻大小一致,以8ck设计为例,假设ck1~ck8的电容(暂不计其他引线导致的电容)分别为c1~c8:

5.c1=1

×

(n

‑

1)

×

c0 8

×

c0;

6.c2=2

×

(n

‑

1)

×

c0 7

×

c0;

7.c3=3

×

(n

‑

1)

×

c0 6

×

c0;

8.c4=4

×

(n

‑

1)

×

c0 5

×

c0;

9.c5=5

×

(n

‑

1)

×

c0 4

×

c0;

10.c6=6

×

(n

‑

1)

×

c0 3

×

c0;

11.c7=7

×

(n

‑

1)

×

c0 2

×

c0;

12.c8=8

×

(n

‑

1)

×

c0 1

×

c0;

13.其中,n为大于零的整数,表示ck信号线路组数;c0表示ck信号线的单根主线101与单根支线102重合处的电容,参见图1中虚线框图部分;

14.由上式可知,在第n组ck信号线路中,ck8和ck1的电容差异为:

15.c8

‑

c1=7

×

(n

‑

1)

×

c0‑7×

c0;并且n值越大,差异越大;

16.由此可知,goa电路的ck信号线从第一根至最后一根的电阻电容延时(rc delay)时间存在梯度差异,而rc延时时间差异会导致点灯画面存在水平密集线状不良,参见图2。因此,亟待一种优化线路以改善上述问题。

技术实现要素:

17.本发明的目的在于提供一种时钟信号线路,该时钟信号线路能够保证时钟信号线之间rc delay的一致性,以改善点灯画面水平密集线状不良的问题。

18.本发明的另一目的在于提供一种栅极驱动电路及显示面板。

19.本发明解决技术问题是采用以下技术方案来实现的:

20.一种时钟信号线路,包括m根时钟信号线,每根时钟信号线均包括主线和支线,支线与主线的每个相交处的电容均相等,m根主线的线宽逐渐增大,其中,m为大于零的整数。

21.可选的,在本发明的一些实施例中,主线包括相互连接的第一线和第二线,m根主线的第一线的线宽逐渐增大,第二线由支线与主线相交的部分形成。

22.可选的,在本发明的一些实施例中,每根第二线的线宽相等,每根支线的线宽相等。

23.可选的,在本发明的一些实施例中,主线的线宽为0.2~2.1mm。

24.可选的,在本发明的一些实施例中,第y根主线的线宽与第一根主线的线宽的比值为第y根时钟信号线上的总电容与第一根时钟信号线上的总电容的比值,其中,y为大于零的整数,并且y小于或等于m。

25.可选的,在本发明的一些实施例中,第y根主线的线宽与第一根主线的线宽的比值为y

±

0.5。

26.可选的,在本发明的一些实施例中,第y根主线的线宽与第一根主线的线宽的比值为

[0027][0028]

其中,n表示时钟信号线路的组数,n为大于零的整数,c0表示支线与主线相交处的电容,c表示主线的外围引线处的电容。

[0029]

可选的,在本发明的一些实施例中,当n在10以上时,第y根主线的线宽与第一根主线的线宽的比值为

[0030][0031]

另外,一种栅极驱动电路,包括栅极驱动单元和向栅极驱动单元提供时钟信号的时钟信号线路,时钟信号线路包括m根时钟信号线,每根时钟信号线均包括主线和支线,支线与主线的每个相交处的电容均相等,m根主线的线宽逐渐增大,其中,m为大于零的整数。

[0032]

另外,一种显示面板,包括栅极驱动电路,栅极驱动电路包括栅极驱动单元和向栅极驱动单元提供时钟信号的时钟信号线路,时钟信号线路包括m根时钟信号线,每根时钟信号线均包括主线和支线,支线与主线的每个相交处的电容均相等,m根主线的线宽逐渐增大,其中,m为大于零的整数。

[0033]

相对于现有技术,本发明包括以下有益效果:由于本发明中保持各处支线与主线相交的电容相等,并且设置了渐变线宽的主线,此种设置能够使得时钟信号线之间的rc延时时间保持一致,从而改善点灯画面水平密集线状不良的问题。

附图说明

[0034]

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0035]

图1是现有技术中的多组时钟信号线路的布局示意图;

[0036]

图2是采用现有的时钟信号线路出现的点灯画面示意图;

[0037]

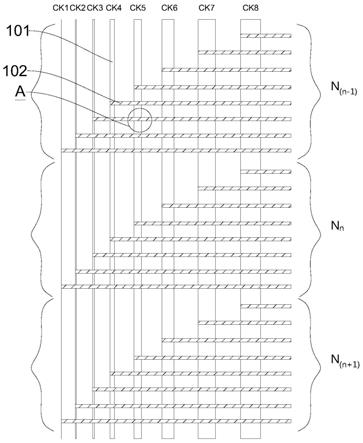

图3是本发明实施例提供的多组时钟信号线路的布局示意图;

[0038]

图4是本发明实施例提供的图3的a部放大示意图;

[0039]

图5是本发明实施例提供的主线的外围引线局部示意图。

具体实施方式

[0040]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0041]

本发明提供的技术方案将在以下内容进行详细说明。需要说明的是,以下实施例的描述顺序不作为对实施例优选顺序的限定。另外,在本发明的描述中,术语“包括”是指“包括但不限于”。用语“第一”、“第二”等仅仅作为标示使用,并没有强加数字要求或建立顺序。本发明的各种实施例可以以一个范围的形式存在;应当理解,以一范围形式的描述仅仅是因为方便及简洁,不应理解为对本发明范围的硬性限制;因此,应当认为所述的范围描述已经具体公开所有可能的子范围以及该范围内的单一数值。

[0042]

参见图3,本发明实施例提供的一种时钟信号线路,包括m根时钟信号线,每根时钟信号线均包括主线101和支线102,支线102与主线101的每个相交处的电容均相等,m根主线101的线宽逐渐增大,其中,m为大于零的整数。在本实施例中,m为8,在其他实施例中,m可以为其他数值,例如10、12。主线101与支线102的连接为本领域熟知的技术,因此在此不再赘述。本实施例中,主线101为tft

‑

lcd的栅极线,支线102为tft

‑

lcd的源极、漏极线。

[0043]

上述时钟信号线路可以看作一组时钟信号线路,实际制作时,存在多组时钟信号线路,图3展示了3组时钟信号线路,分别以n

(n

‑

1)

、n

n

、n

(n 1)

表示,其中,n为大于2的整数。因此,若n为2,则n

(n

‑

1)

、n

n

、n

(n 1)

分别表示第1组、第2组、第3组。

[0044]

主线101包括相互连接的第一线1011和第二线1012,8根主线101的第一线1011的线宽逐渐增大,第二线1012由支线102与主线101相交的部分形成,所有的该相交处的电容均相等。实际上,第一线1011与第二线1012的设置也可以看作是:主线101的线宽在主线101与支线102的相交处发生变化的设置,参见图4,在该相交处,呈现第一线1011与第二线1012的不同线宽。如图3示意的,在同一时钟信号线路中,除第一根主线101外,其他主线101均包括多根第一线1011和多根第二线1012,第一线1011与第二线1012间隔设置,如图所示的每一根第二线1012与支线102的相交处的电容均相同。对于各主线101上第一线1011的长度和数量限制,以主线101与支线102相交结果为准,各第一线1011与第二线1012的连接及布置情况参见图3和图4。单根主线101上的第二线1012、不同主线101上的第二线1012的线宽均相等。图示中支线102的长度不相同,但每根支线102的线宽均相等。

[0045]

本实施例中,8根主线101的线宽范围在0.2~2.1mm之间。当然,在其他实施例中,也可以另外取值。

[0046]

具体的,同一时钟信号线路中,第y根主线101的线宽与第一根主线101的线宽的比值为第y根时钟信号线上的总电容与第一根时钟信号线上的总电容的比值,其中,y为大于

零的整数,并且y小于或等于m,即,y小于或等于8。需要说明的是,除第1组时钟信号线路外,在其他组的时钟信号线路中,此处所指的总电容应包括主线101的外围引线103导致的电容、时钟信号线在所处时钟信号线路的电容以及在所处时钟信号线路的组数之前的时钟信号线路的电容,以图3中ck3举例来说,c3表示ck3的总电容(计入外围引线103导致的电容c,外围引线103的线路情况参见图5),则在第n组时钟信号线路中,c3=3

×

(n

‑

1)

×

c0 6

×

c0 c;其中c0表示支线102与第二线1012相交处的电容。

[0047]

通过计算可知,第y根主线101的线宽与第一根主线101的线宽的比值为y

±

0.5。

[0048]

参考如下:

[0049]

由于本实施例中时钟信号线数量为8,因此,以8ck计算,在每组时钟信号线路中,ck1~ck8的总电容(计入非时钟信号线——外围引线103导致的电容)分别为c1~c8:

[0050]

c1=1

×

(n

‑

1)

×

c0 8

×

c0 c;

[0051]

c2=2

×

(n

‑

1)

×

c0 7

×

c0 c;

[0052]

c3=3

×

(n

‑

1)

×

c0 6

×

c0 c;

[0053]

c4=4

×

(n

‑

1)

×

c0 5

×

c0 c;

[0054]

c5=5

×

(n

‑

1)

×

c0 4

×

c0 c;

[0055]

c6=6

×

(n

‑

1)

×

c0 3

×

c0 c;

[0056]

c7=7

×

(n

‑

1)

×

c0 2

×

c0 c;

[0057]

c8=8

×

(n

‑

1)

×

c0 1

×

c0 c;

[0058]

其中,n表示时钟信号线路的组数,n为大于零的整数,c0表示支线102与第二线1012相交处的电容,c表示主线101的外围引线103处的电容。

[0059]

本实施例中,n为10,图中n

(n

‑

1)

、n

n

、n

(n 1)

分别表示第9组时钟信号线路、第10组时钟信号线路、第11组时钟信号线路。

[0060]

为保证时钟信号线之间rc delay的一致,基于rc延时计算公式为延时时间d=

‑

r

×

c

×

in((e

‑

v)/e),要使d相同,则d1=d

y

,则r1c1=r

y

c

y

,由于

[0061]

(其中s=wh,w为宽度,h为厚度);

[0062][0063]

在电阻率ρ、长度l、厚度h相等的条件下,r1c1=r

y

c

y

,即:

[0064]

即因此,

[0065][0066]

所以,第y根主线101的线宽与第一根主线101的线宽的比值为

[0067][0068]

由于本实施例中,n为10,所以(m

‑

y 1)

×

c0、m

×

c0的数值较小,可忽略不计,第y根主线101的线宽与第一根主线101的线宽的比值为

[0069][0070]

且通过图3可知,每组时钟信号线路中,ck1~ck8的电阻为r1~r8,其中r1~r8表示第1~8根主线101上的电阻:

[0071][0072][0073][0074][0075][0076][0077][0078][0079]

根据rc延时计算公式可知d1~d8为:

[0080]

[0081][0082][0083][0084][0085][0086][0087][0088]

本发明的实施例还提供了一种栅极驱动电路,包括栅极驱动单元和向栅极驱动单元提供时钟信号的上述时钟信号线路,栅极驱动单元与时钟信号线路之间的连接为本领域的熟知技术,因此在此不再赘述。另外,本发明的实施例还提供了一种包括上述时钟信号线路的显示面板。采用本发明实施例提供的时钟信号线路,点灯画面良好,能够有效避免当前8k产品出现的rc delay不一致导致的点灯画面水平密集线状不良的现象。

[0089]

以上对本发明实施例所提供的技术方案进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。