1.本技术属于显示技术领域,尤其涉及一种显示面板的控制电路和显示装置。

背景技术:

2.随着显示技术的快速发展,显示面板在娱乐、教育、安防等各种领域得到广泛应用。gdl(gate driver less,阵列基板行驱动)技术是指将栅极驱动电路(gate driver ic)直接制作在阵列(array)基板上,通过输出行驱动信号实现对栅极进行逐行扫描。gdl技术能够简化显示面板的制备工序,省去水平扫描线方向的芯片邦定(bonding)工序,并降低生产成本,同时可以提高显示面板的集成度,使显示面板更轻薄化。

3.采用gdl技术的显示面板需要使用多个时钟信号来控制栅极驱动电路输出行驱动信号,随着显示面板的尺寸和分辨率不断提高,每个显示面板的栅极驱动电路数量也不断提高,导致单个时钟信号的负载过高,使显示面板的运行稳定性下降。

技术实现要素:

4.有鉴于此,本技术实施例提供了一种显示面板的控制电路和显示装置,以解决随着显示面板的尺寸和分辨率不断提高,每个显示面板的栅极驱动电路数量也不断提高,导致单个时钟信号的负载过高,使显示面板的运行稳定性下降的问题。

5.本技术实施例的第一方面提供了一种显示面板的控制电路,所述控制电路用于接收第一时钟信号、第一电平信号和第二电平信号,根据所述第一电平信号和所述第二电平信号,对所述第一时钟信号进行移相得到第二时钟信号并输出至栅极驱动电路;其中,所述第二时钟信号包括第三电平信号和第四电平信号,所述第三电平信号和所述第四电平信号的电平高低不同;

6.所述控制电路包括第一开关单元和第二开关单元,所述第一开关单元与所述第二开关单元连接;

7.所述第一开关单元用于接收所述第一时钟信号、所述第一电平信号和所述第二电平信号,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,输出第三电平信号至所述栅极驱动电路;

8.所述第二开关单元用于接收所述第一时钟信号、所述第一电平信号和所述第二电平信号,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,输出第四电平信号至所述栅极驱动电路。

9.在一个实施例中,所述第一开关单元,还用于当所述第一时钟信号为低电平时,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,导通并输出第三电平信号至所述栅极驱动电路,所述第三电平信号为高电平;还用于当所述第一时钟信号为高电平时,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,关断并停止输出所述第三电平信号至所述栅极驱动电路。

10.在一个实施例中,所述第二开关单元,还用于当所述第一时钟信号为高电平时,根

据所述第一时钟信号、所述第一电平信号和所述第二电平信号,导通并输出第四电平信号至所述栅极驱动电路,所述第四电平信号为低电平;还用于当所述第一时钟信号为低电平时,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,关断并停止输出所述第四电平信号至所述栅极驱动电路。

11.在一个实施例中,所述控制电路包括:

12.第三开关单元,用于接收所述第一时钟信号、所述第一电平信号和所述第二电平信号,当所述第一时钟信号为高电平时,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,导通并输出第五电平信号至所述栅极驱动电路,所述第五电平信号为高电平;还用于当所述第一时钟信号为低电平时,根据所述第一时钟信号、第一电平信号和第二电平信号,导通并输出第五电平信号至所述栅极驱动电路,所述第五电平信号为低电平。

13.在一个实施例中,所述控制电路包括:

14.第四开关单元,与第三开关单元连接,用于接收所述第一时钟信号、所述第一电平信号和所述第二电平信号,当所述第一时钟信号为高电平时,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,导通并输出第六电平信号至所述栅极驱动电路,所述第六电平信号为低电平;还用于当所述第一时钟信号为低电平时,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,关断并停止输出所述第六电平信号;

15.其中,所述第二时钟信号包括第五电平信号和所述第六电平信号。

16.本技术实施例的第二方面提供了一种显示面板的显示装置,包括显示面板;

17.以及控制单元,其中,所述控制单元包括上述第一方面所述的控制电路。

18.本技术实施例的第一方面提供一种显示面板的控制电路,用于接收第一时钟信号、第一电平信号和第二电平信号,根据所述第一电平信号和所述第二电平信号,对所述第一时钟信号进行移相得到第二时钟信号并输出至栅极驱动电路,实现对时钟信号的移相,以降低单个时钟信号的负载,并且可以减少显示面板中时钟发生器的数量,降低显示面板的生产成本。

19.可以理解的是,上述第二方面的有益效果可以参见上述第一方面中的相关描述,在此不再赘述。

附图说明

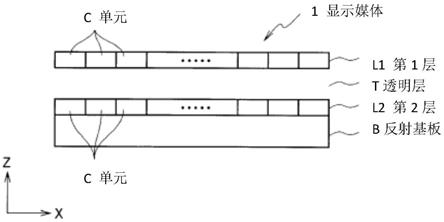

20.图1是本技术实施例提供的显示面板的控制电路的第一种结构示意图;

21.图2是本技术实施例提供的显示面板的控制电路的第二种结构示意图;

22.图3是本技术实施例提供的显示面板的控制电路的第三种结构示意图;

23.图4是本技术实施例提供的显示面板的控制电路的第四种结构示意图;

24.图5是本技术实施例提供的显示面板的控制电路的第五种结构示意图;

25.图6是本技术实施例提供的第一时钟信号、第二电子开关的栅极电平、第二电子开关的漏极电平、第四电子开关的栅极电平、第三电平信号、第四电平信号和第二时钟信号的时序示意图;

26.图7是本技术实施例提供的显示面板的控制电路的第六种结构示意图;

27.图8是本技术实施例提供的显示面板的控制电路的第七种结构示意图;

28.图9是本技术实施例提供的显示面板的控制电路的第八种结构示意图;

control register,tcon)或片上芯片(system on chip,soc)输入至控制电路的;控制电路可以根据第一电平信号和第二电平信号对第一时钟信号移相,移相得到的第二时钟信号和第一时钟信号的相位差的范围可以是0度至180度,第二时钟信号和第一时钟信号的相位差可以根据第一电平信号和第二电平信号的时序决定;第一时钟信号和第二时钟信号都可以用于输出至栅极驱动电路,以控制栅极驱动电路输出行驱动信号对显示面板的栅极进行逐行扫描;具体的,一个显示面板可以包括至少一个控制电路,控制电路的数量根据上述显示面板使用的时钟信号数量确定,每个控制电路和每个第一时钟信号一一对应,第n个控制电路接收第n个第一时钟信号,对第n个第一时钟信号进行移相得到第n个第一时钟信号对应的第n个第二时钟信号;每个控制电路移相得到的第二时钟信号输出至栅极驱动电路后,栅极驱动电路可以根据实际需要控制任意数量的行驱动信号输出以对显示面板的栅极进行逐行扫描,相比于使用n个第一时钟信号输入栅极驱动电路,通过控制电路生成与n个第一时钟信号一一对应的n个第二时钟信号后,可以使用n个第一时钟信号和n个第二时钟信号一共2n个时钟信号输入栅极驱动电路,由于单个时钟信号可以输入多个栅极驱动电路,当时钟信号的数量增加后,单个时钟信号可以减少输入栅极驱动电路的数量,从而可以降低单个时钟信号的负载,并可以减少用于生成时钟信号的时钟发生器的数量,降低显示面板的生产成本。其中,n为大于0的整数,控制电路的数量可以根据显示面板的实际需要进行设置。

41.图3示例性的示出了第一个控制电路101、第二个控制电路102至第n个控制电路103与栅极驱动电路20连接的结构示意图。

42.在应用中,控制电路可以包括多个开关单元,每个开关单元可以根据第一时钟信号的电平高低控制该开关单元是否输出电平信号,具体的,控制电路可以包括第一开关单元和第二开关单元,其中,第一开关单元用于根据第一时钟信号控制第三电平信号的输出,第二开关单元用于根据第一时钟信号控制第四电平信号的输出。例如,当第一时钟信号为高电平时,第一开关单元可以控制第三电平信号停止输出,第二开关单元可以控制第四电平信号开始输出;当第一时钟信号为低电平时,第一开关单元可以控制第三电平信号开始输出,第二开关单元可以控制第四电平信号停止输出。需要说明的是,在显示面板进入工作状态后,第三电平信号和第四电平信号的电平高低不同,具体的,当第三电平信号为高电平时,第四电平信号为低电平,或者,当第三电平信号为低电平时,第四电平信号为高电平,因此,通过整合第一开关单元输出的第三电平信号和第二开关单元输出的第四电平信号,可以得到连续不间断的第二时钟信号。

43.在一个实施例中,所述第一电平信号为高电平信号,所述第二电平信号为低电平信号。

44.在一个实施例中,第一开关单元11,还用于当所述第一时钟信号为低电平时,根据所述第一时钟信号、第一电平信号和第二电平信号,导通并输出第三电平信号至所述栅极驱动电路20,所述第三电平信号为高电平;还用于当所述第一时钟信号为高电平时,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,关断并停止输出所述第三电平信号至所述栅极驱动电路20;

45.第二开关单元12,还用于当所述第一时钟信号为高电平时,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,导通并输出第四电平信号至所述栅极驱动电

路20,所述第四电平信号为低电平;还用于当所述第一时钟信号为低电平时,根据所述第一时钟信号、所述第一电平信号和所述第二电平信号,关断并停止输出所述第四电平信号至所述栅极驱动电路20。

46.在应用中,控制电路进入工作状态后,当第一时钟信号为低电平时,第一开关单元导通并输出第三电平信号至栅极驱动电路,此时第三电平信号为高电平,第二开关单元关断并停止输出第四电平信号至栅极驱动电路,此时第四电平信号不输出,因此,此时第二时钟信号为高电平;当第一时钟信号为高电平时,第一开关单元关断并停止输出所述第三电平信号至所述栅极驱动电路,此时第三电平信号不输出,第二开关单元导通并输出第四电平信号至所述栅极驱动电路,此时第四电平信号为低电平,因此,此时第二时钟信号为低电平,从而实现对第一时钟信号的移相,移相得到的第二时钟信号和第一时钟信号的相位差为90度。

47.如图4所示,在一个实施例中,基于图2所对应的实施例,所述第一开关单元11包括第一电子开关111、第二电子开关112、第三电子开关113、第四电子开关114、第五电子开关115和第一电容116;

48.所述第一电子开关111的漏极与所述第二电子开关112的栅极连接,所述第一电子开关111的栅极和源极用于接收所述第一时钟信号;

49.所述第二电子开关112的漏极与所述第四电子开关114的源极连接,所述第二电子开关112的源极用于接收所述第一电平信号;

50.所述第三电子开关113的漏极分别与所述第五电子开关115的源极和所述第四电子开关114的栅极连接,所述第三电子开关113的源极用于接收所述第一电平信号;

51.所述第一电容116的第一级分别与所述第一电子开关111的漏极和所述第二电子开关112的栅极连接,所述第五电子开关115的漏极用于接收所述第二电平信号;

52.所述第三电子开关113的栅极、所述第五电子开关115的漏极、所述第四电子开关114的漏极和所述第一电容116的第二极分别与所述第二开关单元电性连接。

53.在应用中,第一电子开关至第五电子开关可以是任意的具有电子开关功能的器件或电路,例如,三极管或金属氧化物半导体场效应晶体管(metal oxide semiconductor field effect transistor,mosfet),具体的,可以是薄膜场效应晶体管(thin film transistor,tft);第一电容可以是陶瓷电容器、铝电解电容器、云母电容器、纸介电容器、钽铌电解电容器或薄膜电容器等不同类型的电容,第一电容的类型和电容值大小可以根据实际需要进行选择。

54.如图5所示,在一个实施例中,基于图4所对应的实施例,第二开关单元12包括第六电子开关121、第七电子开关122、第八电子开关123;

55.所述第六电子开关121的漏极分别与所述第三电子开关的栅极和所述第七电子开关122的源极连接,所述第六电子开关121的栅极和源极用于接收所述第一电平信号;

56.所述第七电子开关122的漏极分别与所述第五电子开关的漏极和所述第八电子开关123的源极连接,所述第七电子开关122的栅极用于接收所述第一时钟信号,所述第七电子开关122的漏极用于接收所述第二电平信号;

57.所述第八电子开关123的漏极分别与第五电子开关的漏极和第一电容的第二级连接,所述第八电子开关123的栅极用于接收所述第一时钟信号。

58.在应用中,第六电子开关至第八电子开关的元器件类型和上述第一电子开关至第五电子开关的元器件类型一致,在此不再赘述。

59.图6示例性的示出了第一时钟信号、第二电子开关的栅极电平、第二电子开关的漏极电平、第四电子开关的栅极电平、第三电平信号、第四电平信号和第二时钟信号的时序图。

60.在应用中,第一电平信号始终输出高电平信号,第二电平信号始终输出低电平信号,第一时钟信号为周期性的时钟信号,第一时钟信号的相邻的上升沿和下降沿的相位差为90度;在控制电路进入工作状态前,需要经过准备状态;第一时间段内控制电路进入第一准备状态,第一时钟信号接收低电平,因此第一时间段期间第一电子开关关断,第一电子开关的漏极电平为低电平,使第二电子开关的栅极电平为低电平,第二电子开关关断,则第二电子开关的漏极电平为低电平,因此,第四电子开关的源极电平为低电平;第六电子开关的栅极和源极都接收第一电平信号,使第六电子开关导通且漏极电平为高电平,则第三电子开关的栅极电平为高电平,使第三电子开关导通,且第三电子开关的源极接收第一电平信号,因此第三电子开关的漏极电平为高电平,使第四电子开关的栅极电平为高电平,第四电子开关导通,由于第四电子开关的源极电平为低电平,因此第四电子开关的漏极电平为低电平,第四电子开关的漏极电平即为第三电平信号,从而第三电平信号为低电平;由于第一时钟信号输入低电平,第一时间段第五电子开关、第七电子开关和第八电子开关关断,第八电子开关不输出第四电平信号;由于第三电平信号为低电平,第四电平信号不输出,因此,第二时钟信号为低电平。需要说明的是,在第一准备状态下,第三电平信号和第四电平信号的电压大小不同,具体的,第三电平信号可以是低电平,低电平具体可以是

‑

3v、

‑

5v、

‑

6v或

‑

8v等,第四电平信号的电压可以是0v;本技术实施例对低电平和高电平的具体电压值不作任何限制。

61.在应用中,第二时间段内控制电路进入第二准备状态,第一时钟信号从第一时间段的低电平改为输入高电平,因此第二时间段内,第一电子开关导通且漏极电平为高电平,使第二电子开关的栅极电平为高电平,第二电子开关导通,且第二电子开关的源极接收第一电平信号,因此第二电子开关的漏极电平为高电平;由于第七电子开关的栅极接收高电平的第一时钟信号使其导通,第六电子开关漏极输出的高电平可以经由第七电子开关、第二电平信号释放,使第三电子开关的栅极电平由高电平降至低电平,第三电子开关关断,还由于第五电子开关的栅极接收高电平的第一时钟信号使其导通,第五电子开关源极处的高电平经由第五电子开关、第二电平信号释放,结合第三电子开关关断,使第五电子开关的源极电平由高电平降至低电平,则第四电子开关的栅极电平由高电平降至低电平,第四电子开关关断,停止输出第三电平信号;由于第八电子开关的栅极接收高电平的第一时钟信号使第八电子开关导通,由于第八电子开关的源极接收第二电平信号并为低电平,则第八电子开关的漏极电平为低电平,从而第四电平信号为低电平;由于第三电平信号停止输出,第四电平信号为低电平,因此第二时钟信号为低电平。

62.在应用中,第三时间段为第二时钟信号输出高电平的时间段,控制电路进入第一工作状态,第一时钟信号从第二时间段的输入高电平改为输入低电平,因此第三时间段内第一电子开关关断,但是由于第二电子开关栅极处的电压为浮空状态,假设当前第二电子开关栅极处的电压为第一电压,第二电子开关的栅极电平仍然为高电平,第二电子开关导

通,第二电子开关的漏极电平和第二时间段的第二电子开关的漏极电平一致为高电平,第三电子开关的导通状态和上述第一时间段的第三电子开关的导通状态一致,在此不再赘述,由于第一时钟信号输入低电平,第五电子开关的栅极电平为低电平,第五电子开关关断,则第四电子开关的栅极电平为高电平,由于第四电子开关的源极电平为高电平,从而第三电平信号为高电平;由于第一时钟信号输入低电平,第七电子开关和第八电子开关的栅极电平为低电平,第七电子开关关断,第八电子开关关断并停止输出第四电平信号;由于第三电平信号为高电平,第四电平信号停止输出,因此,第二时钟信号为高电平;此外,由于第三电平信号为高电平,且由于第二电子开关栅极处的电压为浮空状态,第一电容的耦合作用使第二电子开关栅极处的第一电压升高至第二电压,第一电压的电压值由第一时钟信号输入高电平时的电压值确定,第二电压的电压值由第一时钟信号输出高电平时的电压值和第一电容的耦合作用确定。

63.在应用中,第四时间段为第二时钟信号输出低电平的时间段,控制电路进入第二工作状态,第一时钟信号从第三时间段的输入低电平改为输入高电平,因此第三时间段内第一电子开关导通,第二电子开关栅极处的电压的浮空状态解除,第二电子开关栅极处的电压由第二电压恢复到第一电压,第二电子开关导通,第四时间段内的第二电子开关的漏极电平和第三时间段内的第二电子开关的漏极电平一致并为高电平;由于第七电子开关的栅极接收高电平的第一时钟信号,使第七电子开关导通,第六电子开关漏极输出的高电平可以经由第七电子开关、第二电平信号释放,使第三电子开关的栅极电平由高电平降至低电平,第三电子开关关断,还由于第五电子开关的栅极接收高电平的第一时钟信号使其导通,第五电子开关源极处的高电平经由第五电子开关、第二电平信号释放,结合第三电子开关关断,使第五电子开关的源极电平由高电平降至低电平,则第四电子开关的栅极电平由高电平降至低电平,第四电子开关关断,停止输出第三电平信号;由于第八电子开关的栅极接收高电平的第一时钟信号使其导通,第八电子开关的源极接收第二电平信号并为低电平,则第八电子开关的漏极电平为低电平,从而第四电平信号为低电平;由于第三电平信号停止输出,第四电平信号为低电平,因此第二时钟信号为低电平。

64.在应用中,控制电路在第一时间段和第二时间段的准备结束后,控制电路的工作状态随着第一时钟信号的电平变化而变化,具体的,第一时钟信号为低电平时,控制电路的工作状态和上述第三时间段的第一工作状态一致,第一时钟信号为高电平时,控制电路的工作状态和上述第四时间的第二工作状态一致,从而使控制电路输出的第二时钟信号和第一时钟信号的相位差为90度,实现对时钟信号的移相,以降低单个时钟信号的负载,并且可以减少显示面板中时钟发生器的数量,降低显示面板的生产成本。

65.如图7所示,在一个实施例中,基于图1所对应的实施例,控制电路10包括:

66.第三开关单元13,用于接收第一时钟信号、第一电平信号和第二电平信号,当第一时钟信号为高电平时,根据第一时钟信号、第一电平信号和第二电平信号,导通并输出第五电平信号至栅极驱动电路20,第五电平信号为高电平;还用于当第一时钟信号为低电平时,根据第一时钟信号、第一电平信号和第二电平信号,导通并输出第五电平信号至栅极驱动电路20,第五电平信号为低电平;

67.第四开关单元14,与第三开关单元13连接,用于接收第一时钟信号、第一电平信号和第二电平信号,当第一时钟信号为高电平时,根据第一时钟信号、第一电平信号和第二电

平信号,导通并输出第六电平信号至栅极驱动电路20,第六电平信号为低电平;还用于当第一时钟信号为低电平时,根据第一时钟信号、第一电平信号和第二电平信号,关断并停止输出第六电平信号。

68.其中,第二时钟信号包括第五电平信号和第六电平信号。

69.在应用中,控制电路进入工作状态后,当第一时钟信号为低电平时,第三开关单元导通并输出第五电平信号至栅极驱动电路,此时第五电平信号为高电平,第四开关单元关断并停止输出第六电平信号至栅极驱动电路,此时第六电平信号不输出,因此,此时第二时钟信号为高电平;当第一时钟信号为高电平时,第三开关单元导通并输出所述第五电平信号至所述栅极驱动电路,此时第五电平信号为低电平,第四开关单元导通并输出第六电平信号至所述栅极驱动电路,此时第六电平信号为低电平,因此,此时第二时钟信号为低电平,从而实现对第一时钟信号的移相,移相得到的第二时钟信号和第一时钟信号的相位差为90度。

70.如图8所示,在一个实施例中,基于图7所对应的实施例,第三开关单元13包括第九电子开关131、第十电子开关132、第十一电子开关133、第十二电子开关134、第十三电子开关135、第二电容136和第三电容137;

71.第九电子开关131的漏极分别与第十电子开关132的栅极、第十三电子开关135的源极和第二电容136的第一极连接,第九电子开关131的源极用于接收第一电平信号;

72.第十电子开关132的漏极与第二电容136的第二极和第十二电子开关134的源极连接,第十电子开关132的源极用于接收第一电平信号;

73.第十一电子开关133的栅极和源极用于接收第一时钟信号;

74.第十二电子开关134的栅极分别与第三电容137的第一极和第十一电子开关133的漏极连接;

75.第十三电子开关135的栅极用于接收第一时钟信号;

76.第九电子开关131的栅极、第十二电子开关134的漏极、第十三电子开关135的漏极和第三电容137的第二极分别与第四开关单元电性连接。

77.在应用中,第九电子开关至第十三电子开关的元器件类型和上述第一电子开关至第五电子开关的元器件类型一致,以及,第二电容和第三电容的类型和上述第一电容的类型一致,在此不再赘述,第二电容和第三电容的电容值大小可以根据实际需要进行设置。

78.如图9所示,在一个实施例中,基于图8所对应的实施例,第四开关单元14包括第十四电子开关141、第十五电子开关142和第十六电子开关143;

79.第十四电子开关141的漏极与第九电子开关的栅极和第十五电子开关142的源极连接,第十四电子开关141的栅极和源极用于接收第一电平信号;

80.第十五电子开关142的漏极分别与第十三电子开关的漏极和第十六电子开关143的源极连接,第十五电子开关142的栅极用于接收第一时钟信号,第十五电子开关142的漏极用于接收第二电平信号;

81.第十六电子开关143的漏极分别与第十二电子开关的漏极和第三电容的第二极连接,第十六电子开关143的栅极用于接收第一时钟信号。

82.在应用中,第十四电子开关至第十六电子开关的元器件类型和上述第一电子开关至第五电子开关的元器件类型一致,在此不再赘述。

83.图10示例性的示出了第一时钟信号、第十电子开关的栅极电平、第十电子开关的漏极电平、第十二电子开关的栅极电平、第五电平信号、第六电平信号和第二时钟信号的时序图。

84.在应用中,第一电平信号始终输出高电平信号,第二电平信号始终输出低电平信号,第一时钟信号为周期性的时钟信号,第一时钟信号的相邻的上升沿和下降沿的相位差为90度;由于第十四电子开关的栅极和源极始终接收第一电平信号,因此第十四电子开关的漏极电平始终为高电平;在控制电路进入工作状态前,需要经过准备状态;第五时间段内控制电路进入第一准备状态,第一时钟信号输入低电平,第十一电子开关、第十三电子开关、第十五电子开关和第十六电子开关关断;第十四电子开关的漏极的高电平输出至第九电子开关的栅极,使第九电子开关导通,且第九电子开关的源极接收第一电平信号,因此第九电子开关的漏极电平为高电平,使第十电子开关的栅极电平为高电平,第十电子开关导通,第十电子开关的漏极电平为高电平;由于第十一电子开关关断,则第十二电子开关的栅极电平为低电平,第十二电子开关关断,第十二电子开关的漏极电平即为第五电平信号,从而第十二电子开关不输出第五电平信号;由于第十六电子开关关断,且第十六电子漏极电平即为第六电平信号,从而第十六电子开关不输出第六电平信号;由于第五电平信号和第六电平信号都不输出,因此,第二时钟信号为低电平。

85.在应用中,第六时间段内控制电路进入第二准备状态,第一时钟信号从第五时间段的输入低电平改为输入高电平,由于第十五电子开关的栅极接收高电平的第一时钟信号,第十五电子开关导通,第十四电子开关漏极输出的高电平可以经由第十五电子开关、第二电平信号释放,使第九电子开关的栅极电平由高电平降至低电平,第九电子开关关断,还由于第十三电子开关的栅极接收高电平的第一时钟信号,第十三电子开关导通,第十三电子开关源极处的高电平经由第十三电子开关、第二电平信号释放,结合第九电子开关关断,使第十电子开关的栅极电平由高电平降至低电平,第十电子开关关断,并且第十电子开关漏极处的电压会由于第二电容的耦合作用降低,因此,第十电子开关的漏极电平为低电平;由于第一时钟信号为高电平,第十一电子开关导通,第十二电子开关的栅极电平为高电平,第十二电子开关导通,第十二电子开关的漏极电平为低电平,从而第五电平信号为低电平;由于第一时钟信号为高电平,第十六电子开关导通,第十六电子开关的源极接收第二电平信号,因此,第十六电子开关的漏极电平为低电平,从而第六电平信号为低电平;由于第五电平信号和第六电平信号都为低电平,因此第二时钟信号为低电平。

86.在应用中,第七时间段为第二时钟信号输出高电平的时间段,控制电路进入第一工作状态,第一时钟信号从第六时间段的输入高电平改为输入低电平,因此第十五电子开关关断,第九电子开关导通,当前第十电子开关的栅极电平为高电平,第十电子开关导通,由于第十电子开关的源极接收第一电平信号,则第十电子开关的漏极电平为高电平,由于第三电容的耦合作用,第十电子开关栅极处的电压会进一步升高,第十电子开关导通更充分;由于第一时钟信号输入低电平,第十一电子开关关断,但是第十二电子开关的栅极处的电压为浮空状态,假设当前第十二电子开关栅极处的电压为第三电压,第十二电子开关的栅极电平仍然为高电平,第十二电子开关导通,第十二电子开关的漏极电平为高电平,从而第五电平信号为高电平;由于第一时钟信号输入低电平,第十三电子开关、第十五电子开关和第十六电子开关关断,由于第十六电子开关关断,从而停止输出第六电平信号;由于第五

电平信号为高电平,第六电平信号停止输出,第二时钟信号为高电平;此外,由于第五电平信号为高电平,且由于第十二电子开关栅极处的电压为浮空状态,当前第十二电子开关栅极处的电压为第三电压,第三电容的耦合作用使第十二电子开关栅极处的电压升高至第四电压,第十二电子开关导通更充分,第三电压的电压值由第一时钟信号输出高电平时的电压值确定,第四电压的电压值由第一时钟信号输出高电平时的电压值、第一电平信号的电压值和第三电容的耦合作用确定。

87.在应用中,第八时间段为第二时钟信号输出低电平的时间段,控制电路处于第二工作状态,控制电路的第二工作状态和上述控制电路的第一准备状态一致,在此不再赘述,区别在于,由于第一时钟信号输入高电平,第十一电子开关导通,第十二电子开关的栅极处的电压为浮空状态解除,第十二电子开关栅极处的电压由第四电压恢复至第三电压。

88.在应用中,控制电路在第五时间段和第六时间段的准备结束后,控制电路的电路状态随着第一时钟信号的电平变化而变化,具体的,第一时钟信号为低电平时,控制电路的工作状态和上述第七时间段的第一工作状态一致,第一时钟信号为高电平时,控制电路的工作状态和上述第四时间的第二工作状态一致,从而使控制电路输出的第二时钟信号和第一时钟信号的相位差为90度,相对于由第一开关单元和第二开关单元组成的控制电路,由第三开关单元和第四开关单元组成的控制电路可以在第一工作状态内使第三开关单元打开更充分,保证移相得到的时钟信号输出的稳定性。

89.本技术实施例提供的显示面板的控制电路,用于接收第一时钟信号、第一电平信号和第二电平信号,根据所述第一电平信号和所述第二电平信号,对所述第一时钟信号进行移相得到第二时钟信号并输出至栅极驱动电路,实现对时钟信号的移相,以降低单个时钟信号的负载,并且可以减少显示面板中时钟发生器的数量,降低显示面板的生产成本。

90.如图11所示,本技术实施例还提供一种显示装置1,显示装置1包括显示面板2以及控制单元3,其中,控制单元3包括上述各个控制电路。

91.控制单元包括存储器、处理器以及存储在存储器中并可在处理器上运行的计算机程序,处理器执行计算机程序时实现上述各个显示面板的控制电路实施例中的功能。

92.在应用中,处理器可以是时序控制器(timer control register,tcon)或片上芯片(system on chip,soc),也可以是中央处理单元(central processing unit,cpu),该处理器还可以是其他通用处理器、数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、现成可编程门阵列(field

‑

programmable gate array,fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。

93.在应用中,存储器在一些实施例中可以是终端设备的内部存储单元,例如终端设备的硬盘或内存。存储器在另一些实施例中也可以是终端设备的外部存储设备,例如终端设备上配备的插接式硬盘,智能存储卡(smart media card,smc),安全数字(secure digital,sd)卡,闪存卡(flash card)等。进一步地,存储器还可以既包括终端设备的内部存储单元也包括外部存储设备。存储器用于存储操作系统、应用程序、引导装载程序(bootloader)、数据以及其他程序等,例如计算机程序的程序代码等。存储器还可以用于暂时地存储已经输出或者将要输出的数据。

94.以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。