技术特征:

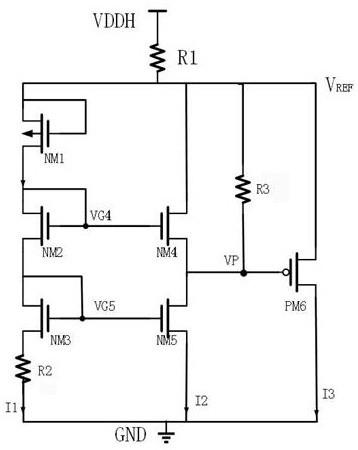

1.一种适用于低压器件实现可耐高压的电源基准电路,其特征在于,包括与高压电源相连的电阻r1,r1的pos端连接高压电源,r1的neg端连接nm1的漏端,nm4的漏端,r3的pos端以及pm6的源端;所述nm1、nm2、nm3采用二极管接法,nm1的源端接nm2漏端,nm2的源端接nm3漏端,nm3的源端接电阻r2的pos端,r2的neg端接公共地端;所述nm4的栅极接nm2的漏端,其源端接r3的neg端,所述r3的neg端接nm5的漏端,所述nm5的栅极接nm3的漏端,nm5的源端接公共地端,作为反馈支路;所述pm6的栅极连接nm5的漏端,漏端接公共地端;r1的neg端作为vref信号输出端。2.根据权利要求1所述的适用于低压器件实现可耐高压的电源基准电路,其特征在于,所述nm1、nm2、nm3、nm4为低压3.3v工艺 nmos器件,pm6为3.3v工艺pmos器件,r1为电路实现耐压功能的电阻,r2为偏置电阻,r3为反馈网络电阻。3.一种利用如权利要求1或2所述的电路实现可耐高压的电源的方法,其特征在于,包括如下步骤:步骤1:从高压电源电压输入端vddh输入的电压vh,通过电阻r1转换成电流,分成支路电流i1,i2,i3;步骤2:高压电源电压输入端vddh开始上电,在r1上产生压降,产生电压vref,同时令二极管接法的nmos管nm1,nm2,nm3,r3导通产生电流i1,并生成偏置电压vg4,vg5;步骤3:偏置电压vg5升高,为nmos管nm5的栅压,产生电流i2,经过r2流入nm5并产生反馈电压vp,并随着vg5的升高而被拉低;步骤4:nm4在电源过压的时候,提高电压vp,保护mos管pm6的栅极不会在电源过压的情况下而损坏;步骤5:反馈电压vp作为pmos管pm6的栅压,随着vp的降低,pm6内产生反馈电流i3;步骤6:pm6的衬底电位与源端相接,pm6的源端作为vref输出;步骤7:vref的值通过调节r1,r2的比例进行调整。4.根据权利要求3所述的实现可耐高压的电源的方法,其特征在于,所述步骤5包括如下具体步骤:步骤5.1:当vddh开始上电,在r1上产生压降,同时nm1,nm2,nm3,r3开始导通,电流i1增大;步骤5.2:节点压降vg4,vg5增大,vg5令nm5导通,产生电流i2,流过r2和nm5;步骤5.3:随着vddh升高,vref升高,vg5升高,i2增大,节点压降vp降低,令pm6导通,电流i3增大;步骤5.4:节点vref的电流开始被泄放,使增大的 vref降低保持不变,电路的高压压降,都被r1承受。5.根据权利要求4所述的实现可耐高压的电源的方法,其特征在于,所述步骤4包括如下具体步骤:步骤4.1当vddh继续升高,达到pm6的电流泄放的极限时,即达到电路的工作电压极限;步骤4.2:当电路达到工作电压极限时,vddh继续升高,vref开始升高,节点vg4升高到令nm4导通,令节点vp升高形成保护,使pm6的栅极不被过压击穿。

技术总结

本发明属于集成电路中的电压基准电路领域,公开了一种适用于低压器件实现可耐高压的电源基准电路,包括承受电路高压的高值电阻R1,产生偏置的电阻R2,低压3.3V工艺的NMOS器件,偏置管NM1~NM3,过压电路保护管NM4,令电源电压稳定为设计低压值的反馈管NM5,高值电阻R3,低压3.3V工艺的PMOS反馈管PM6。通过上述设计可实现采用低压工艺令电路产生可承受100V以上高压电源的低压基准,无需高压工艺或者其他特殊的耐高压器件,降低了设计电路的工艺要求和成本,有很高的使用价值和推广价值。有很高的使用价值和推广价值。有很高的使用价值和推广价值。

技术研发人员:张琪 姜秀彬 郑志渊 袁剑涛 黄凯 郑丹丹

受保护的技术使用者:杭州朔天科技有限公司

技术研发日:2021.07.23

技术公布日:2021/10/26

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。