包括延迟补偿电路的半导体装置

1.本技术要求于2020年4月10日在韩国知识产权局提交的第10

‑

2020

‑

0044008号韩国专利申请的优先权的权益,该韩国专利申请的公开通过引用全部包含于此。

技术领域

2.本公开的示例实施例涉及一种半导体装置。

背景技术:

3.半导体装置可以包括根据时钟信号而操作的电路,两个或更多个电路可以通过接收相同的时钟信号来操作。为了将相同的时钟信号输入到两个或更多个电路,提供时钟信号的传送路径的时钟树可以被包括在半导体装置中。时钟树可以被对称地设置以减小输入到电路的时钟信号之间的时钟偏差(clock skew,又称为“时钟歪斜”),但当这样的时钟树被设置为对称结构时,包括在时钟树中的器件的数量可能增加,使得半导体装置的集成密度可能劣化。

技术实现要素:

4.本公开的示例实施例将提供这样的半导体装置:该半导体装置可以有效地补偿时钟信号之间的偏差,可以减少包括在时钟树中的器件的数量,并且可以减小时钟信号的波动。

5.根据本公开的示例实施例,一种半导体装置包括:内部时钟产生电路,被配置为接收外部时钟并且产生内部时钟;多个单元电路,被配置为具有第一单元电路和第二单元电路,第一单元电路和第二单元电路在与内部时钟同步时进行操作;多个传送电路,包括第一传送电路和第二传送电路,第一传送电路被配置为提供具有第一延迟时间的第一传送路径并且连接在第一单元电路与内部时钟产生电路之间,第二传送电路被配置为提供具有第二延迟时间的第二传送路径并且连接在第二单元电路与内部时钟产生电路之间,第二延迟时间与第一延迟时间不同;以及延迟补偿电路,被配置为:将通过第一传送路径输入到第一单元电路的第一操作时钟与通过第二传送路径输入到第二单元电路的第二操作时钟进行比较,并且调整第二延迟时间,使得调整后的第二延迟时间与第一延迟时间匹配。第一延迟时间可以是内部时钟产生电路与所述多个单元电路中的不同的单元电路之间的延迟时间之中的最长延迟时间。

6.根据本公开的示例实施例,一种半导体装置包括:输入/输出电路,被配置为根据时钟信号输入和输出数据信号;延迟锁定环电路,被配置为产生时钟信号;多个中继器,连接在延迟锁定环电路与输入/输出电路之间,并且被配置为将时钟信号发送到输入/输出电路;比较器,连接在输入/输出电路之中的第一输入/输出电路和第二输入/输出电路之间,并且被配置为将输入到第一输入/输出电路的第一时钟信号与输入到第二输入/输出电路的第二时钟信号进行比较;以及延迟链,被配置为:基于比较器的输出来调整第二时钟信号的相位,以使得第一时钟信号和第二时钟信号具有相同的相位。

7.根据本公开的示例实施例,一种半导体装置包括:时钟产生电路,被配置为产生时钟信号;第一延迟电路,被配置为:将时钟信号延迟第一延迟时间,并且将被延迟了第一延迟时间的时钟信号输入到第一单元电路;第二延迟电路,被配置为:将时钟信号延迟比第一延迟时间短的第二延迟时间,并且将被延迟了第二延迟时间的时钟信号输入到与第一单元电路不同的第二单元电路;以及延迟补偿电路,被配置为:将第一延迟时间与第二延迟时间进行比较,并且增大第二延迟时间以得到与第一延迟时间匹配的增大后的第二延迟时间。

附图说明

8.从下面结合附图进行的详细描述,将更清楚地理解本公开的以上和其他方面、特征和优点,在附图中:

9.图1是示出根据本公开的示例实施例的半导体装置的框图;

10.图2是示出根据本公开的示例实施例的半导体装置的框图;

11.图3和图4是示出根据本公开的示例实施例的半导体装置的操作的示图;

12.图5是示出根据本公开的示例实施例的半导体装置的框图;

13.图6是示出根据本公开的示例实施例的包括在半导体装置中的延迟补偿电路的框图;

14.图7和图8是示出根据本公开的示例实施例的延迟补偿电路的操作的示图;

15.图9是示出根据本公开的示例实施例的半导体装置的操作的示图;

16.图10至图12是示出根据本公开的示例实施例的半导体装置的操作的示图;

17.图13至图16是示出根据本公开的示例实施例的半导体装置的操作的示图;

18.图17至图20是示出根据本公开的示例实施例的半导体装置的操作的示图;

19.图21和图22是示出根据本公开的示例实施例的半导体装置的示图;以及

20.图23是示出根据本公开的示例实施例的包括半导体装置的电子装置的框图。

具体实施方式

21.在下文中,将如下参照附图描述本公开的实施例。在描述和附图中,除非另外清楚地指示,否则相同或相似的参考标号表示相同或相似的元件/组件。

22.图1是示出根据示例实施例的半导体装置的框图。

23.参照图1,示例实施例中的半导体装置1可以包括时钟产生电路10、时钟树20以及多个单元电路31至34(30)。时钟产生电路10可以使用由半导体装置1从外部装置(例如,存储器控制器)接收的外部时钟来产生用于半导体装置1的操作的内部时钟。在一个示例实施例中,时钟产生电路10可以包括延迟锁定环(delay locked loop,dll)电路。

24.时钟树20可以是提供用于将由时钟产生电路10产生的内部时钟传送到单元电路30的传送路径的电路。时钟树20可以包括用于传送内部时钟的多个中继器。作为示例,每个中继器可以包括至少一个缓冲器。因此,当内部时钟通过中继器被传送到单元电路30时,可能发生信号延迟。为了使传送到单元电路30中的每个的内部时钟同步,用于补偿连接到单元电路30的传送路径的延迟时间的差异的各种方法可以被应用于时钟树20。

25.单元电路30可以是使用内部时钟进行操作的电路。作为示例,单元电路30可以是用于将信号发送到外部装置(例如,存储器控制器)和从外部装置(例如,存储器控制器)接

收信号的输入和输出电路。输入和输出电路可以与内部时钟同步,并且可以用于发送信号或接收信号。这里描述的输入和输出电路还被描述为输入/输出电路,每个输入/输出电路被配置为输入和输出数据信号或数据选通信号。在示例实施例中,单元电路31至34可以具有相同的操作和结构。例如,单元电路31至34可以是输入/输出电路(例如,相同的输入/输出电路)。在示例实施例中,单元电路31至34的至少一部分可以具有不同的操作和结构。例如,单元电路31和32可以是输入/输出电路,单元电路33可以是被配置为输出数据选通信号dqs或dqsb的数据选通缓冲器,单元电路34可以是被配置为输出数据掩蔽信号(dm或dmi)以提供数据总线反转(dbi)功能的数据反转缓冲器。

26.当在时钟树20的用于传输内部时钟的传送路径之间存在延迟时间的差异时,单元电路30的操作时序可能不同,半导体装置1的可靠性可能劣化。为了解决这样的问题,时钟树20可以被设计为使得时钟树20的传送路径具有相同延迟时间。然而,当时钟树20被设计为使得传送路径具有相同的延延迟时间时,用于实现传送路径的器件的数量可能增加,使得半导体装置1的集成密度可能劣化。此外,设置在传送路径之间以减小寄生电容等的屏蔽空间可能无法被充分地设置,因此,当内部时钟的频率高时,可能发生抖动,使得眼裕度(eye margin)可能被减小,或者可能发生其他问题。

27.在一个示例实施例中,通过时钟树20中的具有最长延迟时间的传送路径传送的内部时钟可以被选择为参考时钟,其他传送路径的延迟时间可以参照参考时钟的延迟时间被调整。因此,包括在时钟树20中的器件的数量可以被减少,使得半导体装置1的集成密度可以被改善,并且足够的屏蔽空间可以被设置在传送路径之间,使得稳定的高速操作可以被提供。

28.图2是示出根据示例实施例的半导体装置的框图。

29.参照图2,示例实施例中的半导体装置100可以包括时钟缓冲器110、时钟产生电路120、时钟树130以及多个单元电路141至144(140)。时钟缓冲器110可以缓冲半导体装置100已经从外部实体(例如,存储器控制器)接收的外部时钟ck_ext,并且可以输出外部时钟。

30.时钟产生电路120可以使用由时钟缓冲器110缓冲的外部时钟ck_ext来产生内部时钟ck_int,并且可以包括例如dll电路、锁相环(phase locked loop,pll)电路等。在图2中示出的示例实施例中,时钟产生电路120可以包括延迟链121、相位检测器122、复制电路123等。延迟链121可以根据特定控制信号进行操作,可以延迟外部时钟ck_ext,并且可以输出内部时钟ck_int。内部时钟ck_int可以通过dll电路或pll电路而与外部时钟ck_ext同步。

31.复制电路123可以复制时钟树130的延迟属性,并且可以提供复制的延迟属性。作为示例,当信号通过时钟树130时发生的延迟量可以与当信号通过复制电路123时发生的延迟量基本相同。复制电路123可以根据时钟树130的延迟属性反映的延迟量来延迟由延迟链121输出的内部时钟ck_int,并且可以将内部时钟ck_int输出到相位检测器122。

32.相位检测器122可以将复制电路123的输出与时钟缓冲器110的输出进行比较,并且可以产生相位比较信号。在一个示例实施例中,当复制电路123的输出具有比时钟缓冲器110的输出的相位快(早)的相位时,相位检测器122可以启用相位比较信号,并且当复制电路123的输出具有比时钟缓冲器110的输出的相位慢(迟)的相位时,相位检测器122可以禁用相位比较信号。由相位检测器122输出的相位比较信号可以作为控制信号被输入到延迟

链121。

33.延迟链121可以通过根据相位比较信号而增大或减小外部时钟ck_ext的延迟量来产生内部时钟ck_int。作为示例,在相位比较信号被启用时,延迟链121可以增大外部时钟ck_ext的延迟量,并且在相位比较信号被禁用时,延迟链121可以减小外部时钟ck_ext的延迟量。

34.时钟树130可以包括用于将内部时钟ck_int传送到单元电路140的多个传送电路。作为示例,每个传送电路可以提供一条或多条传送路径,每条传送路径可以被实现为多个中继器。当在单元电路140中的每个中产生内部时钟ck_int的偏差时,单元电路140中的每个的操作时序可能不同,因此,在半导体装置100的操作中可能发生错误。因此,时钟树130可以被设计为使得将内部时钟ck_int传送到单元电路140的传送路径具有彼此相同的延迟时间。

35.图3和图4是示出根据示例实施例的半导体装置的操作的示图。

36.参照图3,半导体装置200可以包括用于使用外部时钟ck_ext来产生内部时钟ck_int的时钟产生电路210以及用于将内部时钟ck_int传送到多个单元电路230的时钟树220。例如,时钟树220可以包括多个中继器rpt 225,多个中继器225中的每个可以包括至少一个缓冲器。单元电路230可以是通过与由时钟树220输出的操作时钟ck同步而操作的电路。在下文中,外部时钟ck_ext可以从半导体装置的外部或从包括在半导体装置中的时钟缓冲器被接收。

37.在图3中示出的示例实施例中,包括在时钟树220中的中继器225可以根据h树结构彼此连接。用于将时钟产生电路210连接到单元电路230的传送路径可以具有彼此相同的延迟时间。例如,单元电路230中的每个可以从时钟树220接收操作时钟ck。因此,输入到单元电路230的操作时钟ck可以具有基本相同的相位。

38.图4是示出输入到时钟树220的内部时钟ck_int和从时钟树220输出的操作时钟ck的示图。参照图4,根据包括在时钟树220中的每个中继器225的延迟量,在内部时钟ck_int与操作时钟ck之间可能发生特定的延迟时间td。延迟时间td可以根据包括在内部时钟ck_int的传送路径中的中继器225的数量、在制造包括时钟树220的半导体装置200的过程中发生的错误、半导体装置200的操作环境等而变化。

39.当时钟树220如图3和图4中一样被配置时,实现操作时钟ck通过其被传送到单元电路230的传送路径需要的中继器225的数量可能增加。因此,半导体装置200的集成密度可能劣化。此外,随着中继器225的数量增加,可能难以充分地确保传送路径之间的屏蔽空间,因此,操作时钟ck的抖动分量(jitter element)可能增大。

40.在一个示例实施例中,时钟树可以被实现为飞越型时钟树(fly

‑

by type clock tree)。因此,实现连接到与图3相同的数量的单元电路的时钟树需要的中继器的数量可以被减少,每个操作时钟ck的抖动分量可以被减小。此外,在输入到单元电路的操作时钟ck之中,可以参照具有最长延迟时间的操作时钟来调整其他操作时钟中的每个的延迟时间。在半导体装置被制造和装运之后由于操作环境、操作电压等的改变而可能发生的每个操作时钟的偏差可以被有效地补偿。

41.图5是示出根据示例实施例的半导体装置的框图。

42.参照图5,示例实施例中的半导体装置300可以包括时钟产生电路310、时钟树320、

多个单元电路330和340以及延迟补偿电路350。时钟产生电路310可以使用外部时钟ck_ext来产生内部时钟ck_int。作为示例,时钟产生电路310可以包括延迟锁定环电路或锁相环电路。

43.时钟树320可以包括第一传送电路321和第二传送电路322。单元电路330和340可以包括连接到第一传送电路321的第一单元电路330和连接到第二传送电路322的第二单元电路340。第一传送电路321可以输出第一操作时钟ck1,第二传送电路322可以输出第二操作时钟ck2。在一个示例实施例中,第一操作时钟ck1和第二操作时钟ck2可以具有相同的频率。

44.如图5中所示,内部时钟ck_int可以通过第二传送电路322从时钟产生电路310被输入到第一传送电路321。因此,第一传送电路321将第一操作时钟ck1传送到第一单元电路330所通过的第一传送路径可以具有比第二传送电路322将第二操作时钟ck2传输到第二单元电路340所通过的第二传送路径的延迟量大的延迟量。作为示例,在半导体装置300的操作的初始状态下,相对于内部时钟ck_int,第一操作时钟ck1的延迟时间可以比第二操作时钟ck2的延迟时间长。可选地,可以理解的是,在半导体装置300的操作的初始状态下,第一操作时钟ck1可以具有比第二操作时钟ck2的相位慢的相位。

45.在一个示例实施例中,延迟补偿电路350可以将从第一单元电路331输出的第一操作时钟ck1与从第二单元电路341输出的第二操作时钟ck2进行比较。在一个示例实施例中,延迟补偿电路350可以将输入到第一单元电路330中的至少一个的第一操作时钟ck1与输入到第二单元电路340中的至少一个的第二操作时钟ck2进行比较,并且可以根据比较的结果来调整第二传送电路322的延迟量。作为示例,第二传送电路322可以包括可调整第二操作时钟ck2的延迟时间的延迟链等。第二传送电路322中的延迟链可以连接在彼此直接连接的中继器之间。延迟补偿电路350可以根据第一操作时钟ck1与第二操作时钟ck2之间的比较的结果,调整包括在第二传送电路322中的延迟链的延迟量,使得第一操作时钟ck1和第二操作时钟ck2可以具有基本相同的相位。

46.在一个示例实施例中,延迟补偿电路350可以以特定间隔或者响应于包括在半导体装置300中的控制逻辑等的请求而控制第二操作时钟ck2与第一操作时钟ck1同步。当半导体装置300的操作环境等改变时,第一操作时钟ck1和第二操作时钟ck2中的每个的延迟量可能被改变,因此,第一操作时钟ck1与第二操作时钟ck2之间可能会发生相位差。因此,延迟补偿电路350可以以预定间隔或基于已经感测到操作环境的变化的控制逻辑的请求,根据第一操作时钟ck1来调整第二操作时钟ck2的延迟时间,因此,半导体装置300的性能可以被改善。

47.图6是示出根据示例实施例的包括在半导体装置中的延迟补偿电路的框图。

48.参照图6,示例实施例中的延迟补偿电路400可以包括比较器410、计数器420和延迟链430。比较器410可以将输入到第一单元电路401的第一操作时钟ck1与输入到第二单元电路402的第二操作时钟ck2进行比较。

49.计数器420可以对比较器410的输出进行计数。作为示例,计数器420可以对第一操作时钟ck1大于第二操作时钟ck2的时间或者第二操作时钟ck2大于第一操作时钟ck1的时间进行计数。延迟链430可以参照第一操作时钟ck1和第二操作时钟ck2中的一个而通过延迟第一操作时钟ck1和第二操作时钟ck2中的另一个而使第一操作时钟ck1和第二操作时钟

ck2彼此同步。

50.在以下描述中,将参照图7和图8更详细地描述延迟补偿电路400的操作。

51.图7和图8是示出根据示例实施例的半导体装置的对比示例的示图。

52.图7和图8是示出输入到第一单元电路401的第一操作时钟ck1、输入到第二单元电路402的第二操作时钟ck2以及内部时钟ck_int的示图。在图7和图8中示出的示例实施例中,内部时钟ck_int可以是时钟树所接收的时钟,时钟树将第一操作时钟ck1和第二操作时钟ck2提供给第一单元电路401和第二单元电路402。内部时钟ck_int可以具有与第一操作时钟ck1和第二操作时钟ck2的频率和占空比相同的频率和占空比。

53.图7是示出在延迟补偿电路400补偿第一操作时钟ck1与第二操作时钟ck2之间的延迟量的差异之前的状态的示图。参照图7,相对于内部时钟ck_int,第一操作时钟ck1可以被延迟第一延迟时间td1,第二操作时钟ck2可以被延迟第二延迟时间td2。第一延迟时间td1可以比第二延迟时间td2长。

54.作为示例,当第一操作时钟ck1和第二操作时钟ck2被输入到比较器410时,计数器420可以对第一操作时钟ck1和第二操作时钟ck2具有不同值的时间进行计数。在图7中示出的示例实施例中,计数器420可以对第一延迟时间td1与第二延迟时间td2之间的时间差δt进行计数。

55.由计数器420对第一延迟时间td1与第二延迟时间td2之间的时间差δt进行计数的结果可以被传送到延迟链430。作为示例,延迟链430可以以数字代码(编码)的形式接收由计数器420进行计数的时间差δt。延迟链430可以参照时间差δt调整第一操作时钟ck1和第二操作时钟ck2中的至少一个,以使得第一延迟时间td1与第二延迟时间td2之间的差异为0。

56.作为示例,延迟链430可以根据相对于内部时钟ck_int具有较长延迟时间的第一操作时钟ck1来调整第二操作时钟ck2的延迟时间。参照图8,延迟链430可以基于从计数器420接收的时间差δt将第二操作时钟ck2的延迟时间调整为第一延迟时间td1。因此,第一操作时钟ck1和第二操作时钟ck2的偏差可以减小。

57.图9是示出根据示例实施例的半导体装置的操作的示图。

58.参照图9,示例实施例中的半导体装置500可以包括时钟产生电路510、时钟树520以及多个单元电路530。

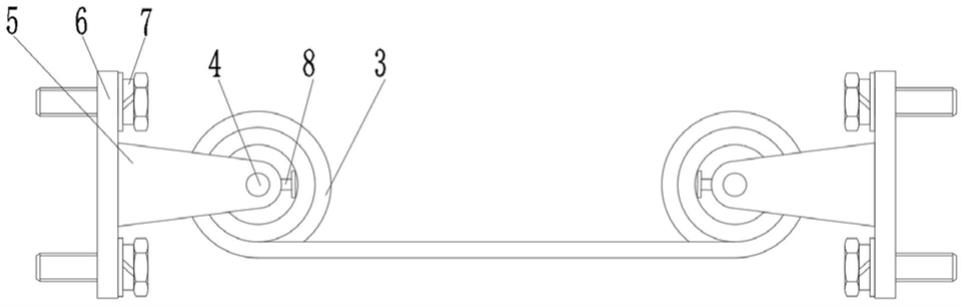

59.内部时钟ck_int可以被输入到时钟树520。时钟树520可以包括将内部时钟ck_int传送到多个单元电路530的第一传送电路521和第二传送电路522。第一传送电路521和第二传送电路522中的每个可以包括多个中继器rpt。每个中继器rpt可以包括至少一个缓冲器,内部时钟ck_int可以在中继器rpt中被延迟。

60.单元电路530可以包括第一单元电路531和第二单元电路532。第一传送电路521可以被定义为第一延迟电路,第一延迟电路可以将内部时钟ck_int延迟第一延迟时间并且可以将延迟的内部时钟ck_int输入到第一单元电路531,第二传送电路522可以被定义为第二延迟电路,第二延迟电路可以将内部时钟ck_int延迟第二延迟时间并且可以将延迟的内部时钟ck_int输入到第二单元电路532。

61.第二延迟时间可以比第一延迟时间短。参照图9,第一传送电路521可以通过第二传送电路522从时钟产生电路510接收内部时钟ck_int。由于当被输入到第一传送电路521

的内部时钟ck_int已经通过包括在第二传送电路522中的中继器的至少一部分,所以第一延迟时间可以比第二延迟时间长。

62.在图9中示出的示例实施例中,第一传送电路521可以接收已经通过包括在第二传送电路522中的四个中继器rpt的内部时钟ck_int,因此,由于四个中继器rpt的延迟时间,在第一延迟时间与第二延迟时间之间可能发生差异。第一延迟时间与第二延迟时间之间的差异可能导致输入到第一单元电路531的第一操作时钟ck1与输入到第二单元电路532的第二操作时钟ck2之间的差异。作为示例,由于第一延迟时间与第二延迟时间之间的差异,在第一操作时钟ck1与第二操作时钟ck2之间可能发生相位差。

63.当在第一操作时钟ck1与第二操作时钟ck2之间发生相位差时,第一单元电路531的操作时序和第二单元电路532的操作时序可能不匹配,并且在半导体装置500的操作中可能发生错误。在一个示例实施例中,延迟补偿电路可以将从第一单元电路531的输入端检测的第一操作时钟ck1与从第二单元电路532的输入端检测的第二操作时钟ck2进行比较,并且可以根据比较的结果来调整第二延迟时间。因此,第一操作时钟ck1与第二操作时钟ck2之间的相位差可以被减小。

64.作为示例,延迟补偿电路可以包括比较器541、计数器542和延迟链543。比较器541可以接收第一操作时钟ck1和第二操作时钟ck2,并且可以将第一操作时钟ck1与第二操作时钟ck2进行比较。参照图9,比较器541可以从第一单元电路531的输入端接收第一操作时钟ck1并从第二单元电路532的输入端接收第二操作时钟ck2。在示例实施例中,比较器541的输入端还可以连接到包括在第一单元电路531和第二单元电路532中的节点,或者还可以连接到第一单元电路531和第二单元电路532的输出端。

65.计数器542可以对第一操作时钟ck1和第二操作时钟ck2具有不同值的区段(section,或“时段”)进行计数,并且可以将计数的结果输出到延迟链543。延迟链543可以基于从计数器542接收的信息来调整第二传送电路522的第二延迟时间。作为示例,延迟链543可以将第二延迟时间增大为与第一延迟时间匹配。

66.延迟链543可以连接在第二传送电路522中的第一中继器522a和第二中继器522b之间。延迟链543还可以将已经通过第一中继器522a的内部时钟ck_int延迟第一延迟时间与第二延迟时间之间的差异,并且可以将延迟的内部时钟ck_int输入到第二中继器522b。作为示例,第二中继器522b可以通过多个中继器rpt连接到所有的第二单元电路532。因此,由延迟链543基于第一延迟时间与第二延迟时间之间的差异而对输入到第二传送电路522的内部时钟ck_int的延迟可以被反映在输入到第二单元电路532的所有的第二操作时钟ck2中。

67.在图9中示出的示例实施例中,可以参照具有最长延迟时间的第一操作时钟ck1来调整第二操作时钟ck2。由于第一操作时钟ck1用作一种类型的参考时钟,因此延迟链可以不被包括在将第一操作时钟ck1提供给第一单元电路531的第一传送电路521中。例如,延迟链543可以仅被包括在第二传送电路522中,使得第一操作时钟ck1与第二操作时钟ck2之间的时钟偏差可以被去除,由时钟树520占据的电路面积可以被有效地减小。此外,通过减少延迟链543的数量,可以减小工艺

‑

电压

‑

温度(process

‑

voltage

‑

temperature,pvt)波动和抖动,并且也可以减小由包括在时钟产生电路510中的复制电路产生的延迟时间与时钟树520的延迟时间之间的差异。

68.在图9中示出的示例实施例中,时钟树520可以包括两个传送电路521和522,连接到第一传送电路521的第一单元电路531的数量可以与连接到第二传送电路522的第二单元电路532的数量相同,但它们的示例实施例不限于此。在示例实施例中,包括在时钟树520中的传送电路的数量和连接到传送电路的单元电路的数量可以变化。

69.第一传送电路521的延迟时间可以是时钟产生电路510与单元电路530中的不同的单元电路之间的延迟时间之中的最长延迟时间。在一个示例实施例中,最长延迟时间可以由一组单元电路(例如,第一单元电路531)共享。

70.图10至图12是示出根据示例实施例的半导体装置的操作的示图。

71.参照图10,示例实施例中的半导体装置600可以包括时钟产生电路610、时钟树620以及多个单元电路630。时钟产生电路610可以使用外部时钟ck_ext来产生内部时钟ck_int,内部时钟ck_int可以被输入到时钟树620。

72.时钟树620可以包括第一传送电路621至第四传送电路624,第一传送电路621至第四传送电路624中的每个可以包括多个中继器rpt。第一传送电路621至第四传送电路624可以将操作时钟ck1至ck4输入到多个单元电路630。

73.单元电路630可以包括第一单元电路631、第二单元电路632、第三单元电路633和第四单元电路634。作为示例,第一传送电路621可以将第一操作时钟ck1输入到第一单元电路631,第二传送电路622可以将第二操作时钟ck2输入到第二单元电路632。第三传送电路623可以将第三操作时钟ck3输入到第三单元电路633,第四传送电路624可以将第四操作时钟ck4输入到第四单元电路634。

74.参照图11,操作时钟ck1至ck4可以具有彼此不同的相位。在一个示例实施例中,在操作时钟ck1至ck4之中,相对于内部时钟ck_int,第一操作时钟ck1可以具有最长的第一延迟时间td1,第四操作时钟ck4可以具有最短的第四延迟时间td4。第二操作时钟ck2可以具有第二长的第二延迟时间td2,第三操作时钟ck3可以具有第二短的第三延迟时间td3。因此,多个单元电路630的操作时序的至少一部分可能彼此不匹配,这可能导致半导体装置600的性能的劣化。

75.在一个示例实施例中,操作时钟ck1至ck4的延迟时间的差异可以使用延迟补偿电路来补偿。作为示例,操作时钟ck1至ck4的延迟时间的差异可以通过将第二延迟时间td2至第四延迟时间td4增大为与第一延迟时间td1匹配来减小。参照图12,延迟补偿电路可以将操作时钟ck1至ck4的延迟时间调整为第一延迟时间td1。

76.返回参照图10和图11,第一比较器641可以将第一操作时钟ck1与第二操作时钟ck2进行比较,第一计数器642可以对第一比较器641的输出进行计数并且可以将输出(计数的结果)传送到第一延迟链643。第一延迟链643可以连接在第二传送电路622中的第一中继器622a与第二中继器622b之间,并且可以通过参照第一计数器642的输出来调整第二操作时钟ck2。作为示例,第一计数器642可以对与第一延迟时间td1与第二延迟时间td2之间的差异对应的第一时间差δt1进行计数。第一时间差δt1越大,第一延迟链643可以将第二延迟时间td2增大得越多。第一延迟链643可以增大第二延迟时间td2,以使得第一延迟时间td1和第二延迟时间td2彼此匹配。

77.第二比较器651、第二计数器652、第二延迟链653、第三比较器661、第三计数器662和第三延迟链663的操作可以与第一比较器641、第一计数器642和第一延迟链643的操作类

似。类似地,第二延迟链653可以连接在第三传送电路623中的第一中继器623a与第二中继器623b之间,第三延迟链663可以连接在第四传送电路624中的第一中继器624a与第二中继器624b之间。作为示例,第二延迟链653可以通过参照第二延迟时间td2与第三延迟时间td3之间的差异而将第三延迟时间td3增大为与第二延迟时间td2匹配。在一个示例实施例中,连接到第二延迟链653的第二比较器651可以将由第一延迟链643调整后的第二操作时钟ck2与第三操作时钟ck3进行比较。因此,如图12中所示,第二延迟链653可以将第三操作时钟ck3的相位延迟第二时间差δt2。

78.类似地,第三延迟链663可以通过参照第三延迟时间td3与第四延迟时间td4之间的差异来将第四延迟时间td4增大为与第三延迟时间td3匹配,连接到第三延迟链663的第三比较器661可以将由第二延迟链653调整后的第三操作时钟ck3与第四操作时钟ck4进行比较。例如,第三比较器661可以将其相位已经被第二延迟链653延迟第二时间差δt2的第三操作时钟ck3与第四操作时钟ck4进行比较。因此,如图12中所示,第三延迟链663可以将第四操作时钟ck4的第四延迟时间td4增大第三时间差δt3,并且可以使第四操作时钟ck4与其他操作时钟ck1至ck3同步。

79.在图10中示出的示例实施例中,第一延迟链643、第二延迟链653和第三延迟链663可以根据第一操作时钟ck1顺序地调整第二操作时钟ck2、第三操作时钟ck3和第四操作时钟ck4。此外,在一个示例实施例中,第一延迟链643、第二延迟链653和第三延迟链663可以同时调整第二操作时钟ck2、第三操作时钟ck3和第四操作时钟ck4。作为示例,第二比较器651可以将第三操作时钟ck3与第一操作时钟ck1而不是与第二操作时钟ck2进行比较,第二延迟链653可以基于比较的结果来调整第三操作时钟ck3。此外,第三比较器661可以将第四操作时钟ck4与第一操作时钟ck1进行比较,第三延迟链663可以基于比较的结果来调整第四操作时钟ck4。

80.图13至图16是示出根据示例实施例的半导体装置的操作的示图。

81.参照图13,示例实施例中的半导体装置700可以包括时钟产生电路710、时钟树720以及多个单元电路730。时钟产生电路710可以使用外部时钟ck_ext来产生内部时钟ck_int,内部时钟ck_int可以被输入到时钟树720。

82.时钟树720可以包括第一传送电路721至第三传送电路723,第一传送电路721至第三传送电路723中的每个可以包括多个中继器rpt。第一传送电路721至第三传送电路723可以将操作时钟ck1至ck3输入到多个单元电路730。在一个示例实施例中,连接到第一传送电路721的单元电路的数量可以与连接到第二传送电路722和第三传送电路723中的每个的单元电路的数量不同。参照图13,连接到第一传送电路721的第一单元电路731的数量可以比连接到第二传送电路722的第二单元电路732的数量和连接到第三传送电路723的第三单元电路733的数量大。此外,第一传送电路721可以包括比第二传送电路722的中继器rpt的数量和第三传送电路723的中继器rpt的数量大的数量的中继器rpt。

83.半导体装置700可以包括用于补偿由第一传送电路721至第三传送电路723中的每个提供的传送路径之间的延迟时间的差异的延迟补偿电路。延迟补偿电路可以包括第一比较器741、第一计数器742、第一延迟链743、第二比较器751、第二计数器752、第二延迟链753等。第一延迟链743可以连接在包括在第二传送电路722中的第一中继器722a与第二中继器722b之间,第二延迟链753可以连接在包括在第三传送电路723中的第一中继器723a与第二

中继器723b之间。

84.单元电路730可以包括第一单元电路731、第二单元电路732和第三单元电路733。作为示例,相对于内部时钟ck_int,由十个中继器rpt导致的延迟时间可以被反映在输入到每个第一单元电路731的第一操作时钟ck1中。相对于内部时钟ck_int,由六个中继器rpt导致的延迟时间可以被反映在输入到每个第二单元电路732的第二操作时钟ck2中。相对于内部时钟ck_int,由四个中继器rpt导致的延迟时间可以被反映在输入到每个第三单元电路733的第三操作时钟ck3中。

85.第一延迟链743可以通过参照第一操作时钟ck1与第二操作时钟ck2之间的比较结果来延迟第二操作时钟ck2,使第一操作时钟ck1的相位和第二操作时钟ck2的相位匹配。作为示例,当假设中继器rpt中发生的延迟时间相同时,第一延迟链743可以将内部时钟ck_int延迟由四个中继器rpt导致的延迟时间。类似地,第二延迟链753可以将内部时钟ck_int延迟由六个中继器rpt导致的延迟时间。

86.参照图14,示例实施例中的半导体装置700a可以包括时钟产生电路710、时钟树720a以及多个单元电路730a。时钟树720a可以包括第一传送电路721a至第三传送电路723a,第一传送电路721a至第三传送电路723a中的每个可以包括多个中继器rpt。

87.第一传送电路721a至第三传送电路723a可以连接到多个单元电路730。在图14中示出的示例实施例中,连接到第一传送电路721a的第一单元电路731a的数量可以与连接到第二传送电路722a的第二单元电路732a的数量相同。在一个示例实施例中,连接到第三传送电路723a的第三单元电路733a的数量可以比第一单元电路731a的数量和第二单元电路732a的数量大。

88.延迟补偿电路的操作可以与参照图13描述的示例实施例类似。延迟补偿电路可以包括第一比较器741a、第一计数器742a、第一延迟链743a、第二比较器751a、第二计数器752a、第二延迟链753a等。第一操作时钟ck1可以相对于内部时钟ck_int被延迟由九个中继器rpt产生的延迟时间。第二操作时钟ck2可以从内部时钟ck_int被延迟由八个中继器rpt产生的延迟时间。因此,第一延迟链743a可以将第二操作时钟ck2进一步延迟与单个中继器rpt对应的延迟时间,并且可以使第二操作时钟ck2与第一操作时钟ck1同步。类似地,第二延迟链753a可以将第三操作时钟ck3进一步延迟与四个中继器rpt对应的延迟时间。

89.参照图15,示例实施例中的半导体装置800可以包括时钟产生电路810、时钟树820以及多个单元电路830。时钟树820可以包括第一传送电路821和第二传送电路822。单元电路830可以包括第一单元电路831和第二单元电路832。第一传送电路821可以将第一操作时钟ck1输入到第一单元电路831,第二传送电路822可以将第二操作时钟ck2输入到第二单元电路832。

90.与前述示例实施例不同,在图15中示出的示例实施例中,延迟链812可以被包括在时钟产生电路810中,而不是被包括在时钟树820中。参照图15,时钟产生电路810可以包括驱动器811,驱动器811用于使用外部时钟ck_ext来产生内部时钟ck_int并且输出内部时钟ck_int。驱动器811可以包括第一输出端和第二输出端,第一输出端连接到第一传送电路821,第二输出端通过连接在第二输出端子与第二传送电路822之间的延迟链812连接到第二传送电路822。因此,在图15中示出的示例实施例中,第一传送电路821和第二传送电路822可以并联连接到时钟产生电路810的输出端子。

91.参照图15,第一操作时钟ck1可以相对于内部时钟ck_int被延迟与九个中继器rpt对应的延迟时间。第二操作时钟ck2可以相对于内部时钟ck_int被延迟与七个中继器rpt对应的延迟时间。因此,当延迟链812将内部时钟ck_int进一步延迟与两个中继器rpt对应的延迟时间时,第一操作时钟ck1和第二操作时钟ck2可以彼此同步。

92.由延迟链812进一步延迟内部时钟ck_int所需要的附加延迟时间可以由比较器841和计数器842确定。比较器841可以将第一操作时钟ck1与第二操作时钟ck2进行比较,计数器842可以对比较器841的输出进行计数。因此,延迟链812可以根据操作环境(诸如,温度、电压等)的变化、考虑操作时钟ck1和ck2的波动来确定附加延迟时间,因此第一操作时钟ck1和第二操作时钟ck2可以准确地彼此同步。

93.在图16中示出的示例实施例中,半导体装置900可以包括时钟产生电路910、时钟树920以及多个单元电路930。时钟树920可以包括第一传送电路921至第四传送电路924,第一传送电路921至第四传送电路924可以输出第一操作时钟ck1至第四操作时钟ck4。用于补偿第一传送电路921至第四传送电路924的延迟时间的差异的操作可以参考参照图10描述的示例实施例来理解。

94.在图16中示出的示例实施例中,第一计数器942的输出可以被输入到第一延迟链943,并且还可以被输入到第二延迟链953和第三延迟链963。此外,第二计数器952的输出可以被输入到第二延迟链953和第三延迟链963。

95.参照图16,第一操作时钟ck1可以是相对于内部时钟ck_int被延迟与九个中继器rpt对应的延迟时间的时钟,第二操作时钟ck2可以是相对于内部时钟ck_int被延迟与八个中继器rpt对应的延迟时间的时钟。第三操作时钟ck3可以是相对于内部时钟ck_int被延迟与六个中继器rpt对应的延迟时间的时钟,第四操作时钟ck4可以是相对于内部时钟ck_int被延迟与四个中继器rpt对应的延迟时间的时钟。

96.由于第一比较器941将第一操作时钟ck1与第二操作时钟ck2进行比较,第二比较器951将第二操作时钟ck2与第三操作时钟ck3进行比较,并且第三比较器961将第三操作时钟ck3与第四操作时钟ck4进行比较,因此可能无法在使用第一操作时钟ck1调整第二操作时钟ck2之前完成第三操作时钟ck3的调整,并且可能无法在使用第二操作时钟ck2调整第三操作时钟ck3之前完成第四操作时钟ck4的调整。例如,第二操作时钟ck2、第三操作时钟ck3和第四操作时钟ck4可能需要按顺序被调整,这可能导致操作时钟ck1至ck4的同步操作需要的时间增大。在图16示出的示例实施例中,当计数器942、952和962的输出被发送到下级的延迟链943、953和963时,由延迟链943、953和963对操作时钟ck1至ck4进行同步的操作可以被同时执行。

97.作为示例,第一计数器942还可以将通过对单个中继器rpt的延迟时间(对应于第一传送电路921的延迟时间与第二传送电路922的延迟时间之间的差异)进行计数而获得的第一信息发送到第一延迟链943,并且还发送到下级的第二延迟链953和第三延迟链963。此外,第二计数器952可以将通过对与两个中继器rpt对应的延迟时间(对应于第二传送电路922的延迟时间与第三传送电路923的延迟时间之间的差异)进行计数而获得的第二信息发送到第二延迟链953和第三延迟链963。

98.当时钟产生电路910产生内部时钟ck_int,并且时钟树920将操作时钟ck1至ck4输入到单元电路930时,第一延迟链943可以从第一计数器942接收第一信息。此外,第二延迟

链953可以从第一计数器942接收第一信息,并且可以从第二计数器952接收第二信息。第一延迟链943可以基于第一信息将第二操作时钟ck2延迟与单个中继器rpt对应的延迟时间。第二延迟链953可以基于第一信息和第二信息将第三操作时钟ck3延迟与三个中继器rpt对应的延迟时间。因此,第二操作时钟ck2和第三操作时钟ck3可以与第一操作时钟ck1同时同步。第三延迟链963可以与第二延迟链953类似地操作。

99.在图16中示出的示例实施例中,第二延迟链953可以同时从第一计数器942和第二计数器952接收第一信息和第二信息。作为示例,第二延迟链953可以包括根据第一信息来延迟第二操作时钟ck2的延迟链和根据第二信息来延迟第二操作时钟ck2的延迟链。因此,第二延迟链953可以具有比第一延迟链943的面积相对大的面积。类似地,第三延迟链963可以具有比第一延迟链943的面积和第二延迟链953的面积大的面积。

100.图17至图20是示出根据示例实施例的半导体装置的操作的示图。

101.参照图17,示例实施例中的半导体装置1000可以被实现为可存储数据的存储器装置。时钟产生电路1010可以使用外部时钟ck_ext来产生内部时钟ck_int,内部时钟ck_int可以通过时钟树1020被输入到单元电路1030。外部时钟ck_ext可以是从存储器控制器输入的时钟。单元电路1030可以连接到多个垫(pad,或称为“焊盘”)pad。多个数据信号dq0至dq7以及数据选通信号dqs和dqsb可以通过垫pad被输入到单元电路1030和从单元电路1030被输出。垫pad中的至少一个可以被分配为虚设件dmy。此外,垫pad中的至少一个可以被分配为dmi垫dmi_p。dmi垫dmi_p可以按照预定的比特单元来设置,并且可以被配置为用于提供数据总线反转(dbi)功能的垫。

102.时钟树1020可以包括第一传送电路1021至第四传送电路1024,第一传送电路1021至第四传送电路1024可以连接到第一单元电路1031至第四单元电路1034。第一单元电路1031至第四单元电路1034的至少一部分可以具有不同的结构。在一个示例实施例中,第一单元电路1031到第四单元电路1034中的每个的结构可以根据输入到垫pad和从垫pad输出的信号来确定。

103.参照图18,第一单元电路1031可以将第一数据d0和第二数据d1串行化,并且可以输出串行化的数据。作为示例,第一数据d0和第二数据d1可以被输入到复用器mux,复用器mux可以响应于第一操作时钟ck1而交替地输出第一数据d0和第二数据d1。第一数据d0和第二数据d1可以被串行化,并且可以作为第一数据信号dq0通过垫pad被输出。在一个示例实施例中,第一操作时钟ck1的频率可以是第一数据d0和第二数据d1中的每个的输出频率的两倍。

104.返回参照图17,第一传送电路1021至第四传送电路1024中的至少一个可以具有不连接到单元电路1030的输出端。作为示例,第四传送电路1024的输出端的一部分可以不连接到单元电路1030,并且可以输出反馈信号fb1和fb2。反馈信号fb1和fb2可以被输入到时钟产生电路1010。作为示例,第一反馈信号fb1可以被输入到占空比校正器(duty cycle corrector,dcc),第二反馈信号fb2可以是用于提供对从内部时钟ck_int到实际的数据信号dq0至dq7被输出为止的延迟时间的反馈的信号,并且可以被输入到时钟产生电路1010的复制电路。

105.可以参照前述示例实施例来理解时钟树1020的操作。第一比较器1041可以将由第一传送电路1021输出的第一操作时钟ck1与由第二传送电路1022输出的第二操作时钟ck2

进行比较,第一计数器1042可以对第一比较器1041的输出进行计数并且可以将输出(计数的结果)传送到第一延迟链1043。第一延迟链1043可以基于从第一计数器1042接收的信息来进一步延迟第二操作时钟ck2。图17中示出的示例实施例中的第一延迟链1043可以将第二操作时钟ck2延迟内部时钟ck_int通过单个中继器rpt时所产生的延迟时间。可以参照对第一比较器1041、第一计数器1042和第一延迟链1043的描述来理解第二比较器1051、第二计数器1052和第二延迟链1053的操作以及第三比较器1061、第三计数器1062和第三延迟链1063的操作。

106.在以下描述中,将参照图19和图20更详细地描述半导体装置1000的操作。

107.参照图19,将描述在时钟树1020中调整操作时钟ck1至ck4的延迟时间之间的差异之前的操作。参照图19,第一操作时钟ck1可以是相对于内部时钟ck_int被延迟第一延迟时间td1的时钟,第二操作时钟ck2可以是相对于内部时钟ck_int被延迟第二延迟时间td2的时钟。第一延迟时间td1可以比第二延迟时间td2大。

108.第一数据信号dq0可以与第一操作时钟ck1同步并且可以被输出,数据选通信号dqs可以与第二操作时钟ck2同步并且可以被输出。如图19中所示,由于第一操作时钟ck1的相位可能由于第一延迟时间td1与第二延迟时间td2之间的差异而与第二操作时钟ck2的相位不匹配,因此第一数据信号dq0和数据选通信号dqs可能无法准确地彼此同步。为了使第一数据信号dq0和数据选通信号dqs准确地彼此同步,数据选通信号dqs的上升沿和下降沿可能需要与第一数据信号dq0匹配。

109.在一个示例实施例中,第一操作时钟ck1和第二操作时钟ck2可以通过由第一延迟链1043将第二操作时钟ck2延迟第一延迟时间td1与第二延迟时间td2之间的差异来彼此同步。参照图20,第一操作时钟ck1和第二操作时钟ck2可以通过第一延迟链1043来彼此同步。因此,第二操作时钟ck2可以相对于内部时钟ck_int被延迟第一延迟时间td1,第一数据信号dq0和数据选通信号dqs可以彼此同步,使得半导体装置1000的可靠性可以被改善。

110.图21和图22是示出根据示例实施例的半导体装置的示图。

111.在图21和图22中示出的示例实施例中,半导体装置1100和1200中的每个可以由存储器装置实现。例如,图21中的半导体装置1100可以包括易失性动态随机存取存储器(dram),图22中的半导体装置1200可以包括非易失性闪存装置。除了存储器装置之外,示例实施例中的半导体装置1100和1200可以广泛地应用于按照特定内部时钟操作的装置。

112.参照图21,半导体装置1100可以包括存储器控制器1110和存储器装置1120,存储器装置1120可以包括多个存储器芯片1121至1123。在多个存储器芯片1121至1123中的每个中,存储器单元可以被划分为多个通道ch0至chn。存储器控制器1110可以将用于控制存储器装置1120的信号(诸如,以数据信号dq、命令/地址信号cmd/addr和外部时钟ck_ext为例)输入到存储器装置1120。

113.存储器装置1120可以包括在前述示例实施例中描述的时钟产生电路、时钟树等。时钟产生电路可以使用外部时钟ck_ext来产生内部时钟,时钟树可以将内部时钟传送到单元电路,单元电路在与内部时钟同步的同时操作。

114.来自时钟树的输入到单元电路的内部时钟可以从由时钟产生电路产生的内部时钟被延迟特定延迟时间。由时钟产生电路与单元电路之间的时钟树提供的传送路径的至少一部分可以具有不同的延迟时间。在一个示例实施例中,时钟树可以将从最长的第一传送

路径检测的第一延迟时间与从相对短的第二传送路径检测的第二延迟时间进行比较。时钟树可以根据第一延迟时间来增大第二延迟时间,使得通过第一传送路径输出的内部时钟与通过第二传送路径输出的内部时钟之间的延迟时间的差异可以被减小。

115.在图22中示出的示例实施例中,半导体装置1200可以包括存储器单元阵列1210和外围电路1220,存储器单元阵列1210可以包括多个存储器块blk。外围电路1220可以包括行解码器1221、页缓冲器1222、输入和输出电路1223和控制逻辑1224。行解码器1221可以通过地选择线gsl、字线wl和串选择线ssl连接到存储器单元阵列1210,页缓冲器1222可以通过位线bl连接到存储器单元阵列1210。

116.控制逻辑1224可以包括在前述示例实施例中描述的时钟产生电路、时钟树等。时钟产生电路可以使用从外部实体接收的外部时钟来产生内部时钟,时钟树可以将内部时钟发送到在与内部时钟同步时进行操作的电路。时钟树可以提供具有不同的延迟时间的多条传送路径,用于补偿传送路径之间的延迟时间的差异的延迟补偿电路可以被包括在控制逻辑1224中。延迟补偿电路可以通过参照在时钟树中产生的最长延迟时间而增大另一延迟时间来补偿延迟时间的差异。

117.图23是示出根据示例实施例的包括半导体装置的电子装置的框图。

118.参照图23,移动系统2000可以包括相机2100、显示器2200、音频处理单元2300、调制解调器2400、dram 2500a和2500b、闪存装置2600a和2600b、输入和输出装置2700a和2700b以及应用处理器2800(在下文中,“ap”)。

119.移动系统2000可以被实现为膝上型计算机、便携式终端、智能电话、平板pc、可穿戴装置、医疗保健装置或物联网(iot)装置。此外,移动系统2000可以被实现为服务器或个人计算机。

120.包括移动系统2000中的各种组件可以在与预定时钟同步时进行操作。例如,显示器2200可以根据预定刷新率显示屏幕,并且可以包括根据时钟来操作以实现刷新率的栅极驱动器、源极驱动器等。此外,dram 2500a和2500b以及闪存装置2600a和2600b可以根据预定时钟进行操作,从而以预定速度存储和读取数据或者与其他外部装置交换数据。输入和输出装置2700a和2700b以及应用处理器2800也可以根据预定时钟进行操作。

121.这里公开的实施例中的半导体装置可以应用于在与移动系统2000中的的时钟同步时进行操作的组件。例如,示例实施例的半导体装置可以应用于这样的电路:该电路用于在显示器2200中产生内部时钟并且将内部时钟传送到栅极驱动器和/或源极驱动器。示例实施例的半导体装置还可以应用于在相机2100与ap 2800之间和/或在显示器2200与ap 2800之间交换图像数据的输入和输出接口。此外,示例实施例的半导体装置还可以应用于其他组件(包括dram 2500a和2500b以及闪存装置2600a和2600b)。

122.相机2100可以根据用户的控制而获得静止图像或视频。移动系统2000可以使用由相机2100获得的静止图像/视频来获取特定信息,或者移动系统2000可以将静止图像/视频转换为不同类型的数据(诸如,文本)并且可以存储该数据。可选地,移动系统2000可以识别包括在由相机2100获得的静止图像/视频中的字符串,并且可以提供与字符串对应的文本或音频翻译。因此,相机2100在移动系统2000中的使用已经越来越多样化。在一个示例实施例中,相机2100可以根据基于mipi标准的d

‑

phy或c

‑

phy接口向ap 2800发送数据(诸如,静止图像/视频)。

2500b可以附加地连接到加速器块2820或加速器芯片。加速器块2820可以是专门执行ap 2800的特定功能的功能块,并且可以包括用于专门执行图形数据处理的图形处理单元(gpu)、用于专门执行ai计算和推断的神经处理单元(npu)、用于专门执行数据传输的数据处理单元(dpu)。

131.在一个示例实施例中,移动系统2000可以包括多个dram 2500a和2500b。在一个示例实施例中,ap 2800可以包括用于控制dram 2500a和2500b的控制器2810,dram 2500a可以直接连接到ap 2800的控制器2810。

132.ap 2800可以通过设置符合jedec标准的命令和模式寄存器组(mode register set,mrs)来控制dram,可以设置移动系统2000需要的规范和功能(诸如,低电压/高速/可靠性以及用于crc/ecc的dram接口协议),并且可以执行通信。例如,ap 2800可以通过符合jedec标准(诸如,lpddr4和lpddr5)的接口与dram 2500a通信。可选地,ap 2800可以为可与加速器块2820或ap 2800分离地布置的加速器芯片设置新的dram接口协议,以控制具有比dram 2500a的带宽高的带宽的用于加速器的dram 2500b,并且ap 2800可以执行通信。

133.图23仅示出了dram 2500a和2500b,但移动系统2000的示例实施例不限于此,并且根据电压条件以及ap 2800和/或加速器块2820的带宽和反应速度,除了dram 2500a和2500b之外的存储器可以被包括在移动系统2000中。作为示例,控制器2810和/或加速器块2820可以控制各种存储器(诸如,pram、sram、mram、rram、fram、混合ram等)。dram 2500a和dram 2500b可以具有比输入和输出装置2700a和2700b或闪存装置2600a和2600b的延迟小的延迟,并且还可以具有比输入和输出装置2700a和2700b或者闪存装置2600a和2600b的带宽大的带宽。dram 2500a和2500b可以在移动系统2000上电时被初始化,并且当操作系统和应用数据被加载时,dram 2500a和2500b可以用作用于操作系统和应用数据的临时存储位置或者用作用于各种软件代码的执行空间。

134.在dram 2500a和2500b中,可以存储加法/减法/乘法/除法算术运算、向量运算、地址运算和/或fft运算数据。在另一示例实施例中,dram 2500a和2500b可以被提供为配备有计算功能的存储器中处理(processing in memory,pim)。例如,dram 2500a和2500b中的将用于推断的函数可以被执行。推断可以在使用人工神经网络的深度学习算法中被执行。深度学习算法可以包括通过各种数据来学习模型的训练步骤和用学习的模型来识别数据的推断步骤。例如,用于推断的函数可以包括双曲正切函数、s型函数和修正线性单元(relu)函数。

135.作为示例实施例,由用户通过相机获得的图像可以进行信号处理并且可以被存储在dram 2500b中,加速器块2820或加速器芯片可以使用存储在dram 2500b中的数据和用于推断的函数来执行用于识别数据的ai数据计算。

136.根据示例实施例,移动系统2000可以包括具有比dram 2500a和2500b的容量大的容量的多个存储装置或者多个闪存装置2600a和2600b。闪存装置2600a和2600b中的每个可以包括存储器控制器2610和闪存2620。存储器控制器2610可以从ap 2800接收控制命令和数据并且可以响应于控制命令将数据写入闪存2620,和/或可以读出存储在闪存2620中的数据并且可以将数据发送到ap 2800。在一个示例实施例中,闪存装置2600a和2600b中的每个可以是图22中的半导体装置1200。在这种情况下,存储器控制器2610可以与图22中的外围电路1220对应,闪存2620可以与图22中的存储器单元阵列1210对应。在一个示例实施例

中,闪存2620可以与图22中的半导体装置1200对应。

137.根据示例实施例,加速器块2820或加速器芯片可以使用闪存装置2600a和2600b来执行训练步骤和ai数据计算。在一个示例实施例中,能够执行预定计算的运算逻辑可以被实现在闪存装置2600a和2600b中的存储器控制器2610中,该运算逻辑可以使用存储在闪存2620中的数据来执行由ap 2800和/或加速器块2820执行的训练步骤和推断ai数据计算的至少一部分。

138.在一个示例实施例中,ap 2800可以包括接口2830,因此,闪存装置2600a和2600b可以直接连接到ap 2800。例如,ap 2800可以被实现为soc,闪存装置2600a可以被实现为与ap 2800分离的芯片,ap 2800和闪存装置2600a可以被安装在单个封装中。然而,它们的示例实施例不限于此,并且多个闪存装置2600a和2600b可以通过连接件电连接到移动系统2000。

139.闪存装置2600a和2600b可以存储诸如由相机2100获得的静止图像/视频的数据和/或通过包括在输入和输出装置2700a和2700b中的通信网络和/或端口接收的数据。例如,闪存装置2600a和2600b可以存储增强现实/虚拟现实内容、高清晰度(hd)内容或超高清晰度(uhd)内容。

140.在以上公开的示例实施例中,dram 2500a和2500b以及闪存装置2600a和2600b中的至少一者可以被实现为存储器装置。例如,dram 2500a和2500b以及闪存装置2600a和2600b中的至少一者可以每预定间隔地执行验证操作,并且如果需要则可以执行刷新操作和/或修复操作。因此,移动系统2000的操作性能和可靠性可以改善。

141.根据前述示例实施例,半导体装置的用于将内部时钟传送到单元电路的传送电路可以被包括在时钟树中。在传送电路之中,具有最长的传送路径的传送电路的内部时钟可以用作调整其他传送电路的内部时钟的参考时钟,并且输入到单元电路的内部时钟之间的时钟偏差可以被减小。此外,通过减少实现时钟树的器件的数量,半导体装置的集成密度可以改善。

142.尽管以上已经示出和描述了示例实施例,但对本领域技术人员将清楚的是,在不脱离如由所附权利要求限定的本公开的范围的情况下,可以做出修改和变型。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。