1.本发明实施例涉及一种封装结构。

背景技术:

2.由于各种电子组件(即,晶体管、二极管、电阻器、电容器等)的集 成密度的持续提高,半导体行业已经历快速增长。在很大程度上,集成密 度的此种提高来自于最小特征尺寸(minimum feature size)的连续减小,此 使得更多较小的组件能够集成到给定区域中。这些较小的电子组件也需要 与先前的封装相比利用较小区域的较小的封装。用于半导体组件的一些较 小类型的封装包括方形扁平封装(quad flat package,qfp)、引脚栅阵列(pingrid array,pga)封装、球栅阵列(ball grid array,bga)封装、倒装芯片 (flip chip,fc)、三维集成电路(three

‑

dimensional integrated circuit,3dic)、 晶片级封装(wafer level package,wlp)及层叠封装(package on package, pop)装置等。

3.3dic封装提供更高的集成密度及其他优势。然而,3dic技术还有许 多挑战需要应对。

技术实现要素:

4.本发明实施例提供一种封装结构,其包括第一管芯、管芯堆叠结构、 支撑结构以及绝缘结构。管芯堆叠结构接合到第一管芯。支撑结构设置在 管芯堆叠结构上,其中支撑结构的宽度大于管芯堆叠结构的宽度并且小于 第一管芯的宽度。绝缘结构至少在侧向上包裹在管芯堆叠结构及支撑结构 周围。

5.本发明实施例提供一种封装结构,其包括第一管芯、至少一个第二管 芯以及虚设管芯结构。至少一个第二管芯接合到第一管芯,其中第一管芯 在侧向上延伸超出至少一个第二管芯的侧壁。虚设管芯结构接合到至少一 个第二管芯。第一管芯的侧壁、至少一个第二管芯的侧壁及虚设管芯结构 的侧壁在侧向上彼此偏移。

6.本发明实施例提供一种形成封装结构的方法,其包括:提供第一管芯; 将管芯堆叠结构接合到第一管芯,其中管芯堆叠结构包括至少一个第二管 芯;通过熔融接合工艺将支撑结构接合到管芯堆叠结构,其中支撑结构的 宽度大于管芯堆叠结构的宽度并且小于第一管芯的宽度;以及形成绝缘结 构以在侧向上包裹在支撑结构及管芯堆叠结构周围,其中绝缘结构的至少 一部分是在将支撑结构接合到管芯堆叠结构之后形成。

附图说明

7.结合附图阅读以下详细说明,会最好地理解本公开的各个方面。应注 意,根据本行业中的标准惯例,各种特征并非按比例绘制。事实上,为论 述清晰起见,可任意增大或减小各种特征的尺寸。

8.图1是示出根据本公开一些实施例的管芯的制备的示意性剖视图。

9.图2a到图2d是示出根据本公开一些实施例的管芯制造方法中的各种 阶段的示意

性剖视图。

10.图3a到图3c是示出根据本公开一些实施例的管芯制造方法中的各种 阶段的示意性剖视图。

11.图4a到图4g是示出根据本公开第一实施例的形成半导体结构的方法 的示意性剖视图。

12.图5a到图5g是示出根据本公开第二实施例的形成半导体结构的方法 的示意性剖视图。

13.图6a及图6b是示出根据本公开一些实施例的半导体结构的示意性剖 视图。

14.图7是示出根据本公开一些其他实施例的半导体结构的示意性剖视图。

15.图8a到图8f是示出根据本公开第三实施例的形成半导体结构的方法 的示意性剖视图。

16.图9a到图9c是根据本公开的一些实施例,在图8a或图8c中概述的 用于形成隔离层的工艺期间的中间步骤中虚线区域c的放大示意性剖视 图。

17.图10a及图10b是示出根据本公开一些实施例的半导体结构的示意性 剖视图。

18.图11a到图11f是示出根据本公开第四实施例的形成半导体结构的方 法的示意性剖视图。

19.图12a及图12b是根据本公开一些实施例的半导体结构的俯视图。

20.图13是示出根据本公开一些其他实施例的半导体结构的示意性剖视 图。

21.图14是示出根据本公开一些实施例的半导体结构的应用的示意性剖视 图。

具体实施方式

22.以下公开内容提供用于实施所提供主题的不同特征的许多不同的实施 例或实例。以下阐述组件及排列的具体实例以简化本公开。当然,这些仅 为实例而非旨在进行限制。举例来说,以下说明中将第二特征形成在第一 特征“上方”或第一特征“上”可包括其中第二特征与第一特征被形成为直接 接触的实施例,且也可包括其中第二特征与第一特征之间可形成有附加特 征、进而使得所述第二特征与所述第一特征可能不直接接触的实施例。另 外,本公开内容可能在各种实例中重复参考编号和/或字母。这种重复是出 于简洁及清晰的目的,且不是自身表示所论述的各种实施例和/或配置之间 的关系。

23.此外,为易于说明,本文中可能使用例如“在

…

下”、“在

…

下方”、“下 部”、“在

…

上”、“在

…

上方”、“上部”等空间相对性用语来阐述图中所示一 个元件或特征与另一(其他)元件或特征的关系。除附图中所绘示的取向 以外,所述空间相对性用语旨在涵盖装置在使用或操作中的不同取向。设 备可以其他方式进行取向(旋转90度或处于其他取向),且本文所使用的 空间相对性描述语可同样相应地进行解释。

24.本公开也可包括其他特征及工艺。举例来说,可包括测试结构,以帮 助对三维(three

‑

dimensional,3d)封装或3dic装置进行验证测试。所述 测试结构可例如包括在重布线层中或在衬底上形成的测试接垫,以使得能 够对3d封装或3dic进行测试、对探针和/或探针卡(probe card)进行使 用等。可对中间结构以及最终结构执行验证测试。另外,本文中所公开的 结构及方法可结合包括对已知良好管芯(known good die,kgd)进行中间 验证的测试方法来使用,以提高良率并降低成本。

25.图1是示出根据本公开第一实施例的制备管芯以用于后续工艺的示意 性剖视图。参照图1,提供了多个管芯20。管芯20可形成在晶片(图中未 示出)中。举例来说,对晶片进行处理以包括多个管芯区,且然后在制造 完成之后,可测试晶片。举例来说,探测晶片的每个管芯区并测试其功能 及性能,并且仅选择已知良好管芯(kgd)并将其用于随后的工艺。在一 些实施例中,将晶片贴合到包括粘胶带的临时载体或框架,且然后沿着切 割线(图中未示出)对晶片进行单体化(singulated)以形成单独的管芯20。 举例来说,在单体化工艺期间,胶带框架(tape frame)tp用于将晶片保持 就位。

26.在一些实施例中,管芯20可以是逻辑管芯、存储器管芯、射频管芯、 电源管理管芯、微机电系统(micro

‑

electro

‑

mechanical

‑

system,mems)管 芯、系统芯片(system on chip,soc)、中央处理器(central processing unit, cpu)、图形处理单元(graphic processing unit,gpu)、xpu等。管芯20 具有彼此相对的前表面(即,有源表面)fs1及后表面bs1,并且具有在约 100微米到约600微米范围内的厚度t1。

27.在一些实施例中,管芯20包括衬底10、互连结构12、多个导通孔13 及接合结构16。举例来说,衬底10是半导体衬底,例如块状半导体(bulksemiconductor)、绝缘体上半导体(semiconductor

‑

on

‑

insulator,soi)衬底、 蓝宝石上半导体衬底、其他支撑衬底(例如石英、玻璃等)、或其组合等, 所述衬底可经掺杂或未经掺杂。在一些实施例中,衬底10由硅或其他半导 体材料制成。作为另外一种选择或另外地,衬底10包含其他元素半导体材 料,例如锗、镓砷或其他合适的半导体材料。在一些实施例中,衬底10还 可包括其他特征,例如各种掺杂区、掩埋层和/或外延层。此外,在一些实 施例中,衬底10由例如硅锗、硅锗碳化物、镓砷磷化物或镓铟磷化物等合 金半导体制成。

28.半导体衬底10可包括形成在其中和/或其上的多个装置(图中未示出), 并且这些装置可以是或者可包括有源装置(例如,晶体管、二极管等)和/ 或无源装置(例如,电容器、电阻器、电感器等)或其他合适的电子组件。

29.互连结构12形成在衬底10及所述装置上方,并且包括介电结构及嵌 置于所述介电结构中的导电结构。介电结构包括多层介电层,且导电结构 包括形成在所述多层介电层中的多层导电特征。导电特征连接到形成在衬 底10中/上的各种装置,以形成功能电路。在一些实施例中,介电层包括形 成在衬底10上方并覆盖半导体装置的层间介电(inter

‑

layer dielectric,ild) 层、以及形成在ild层上方的一个或多个金属间介电(inter

‑

metallizationdielectric,imd)层。在一些实施例中,ild层及imd层由低k介电材料 或极低k(extreme low

‑

k,elk)材料形成,所述材料例如为氧化物、二 氧化硅、硼磷硅酸盐玻璃(borophosphosilicate glass,bpsg)、磷硅酸盐玻 璃(phosphosilicate glass,psg)、氟化硅酸盐玻璃(fluorinated silicate glass, fsg)、sio

x

c

y

、旋涂玻璃(spin

‑

on

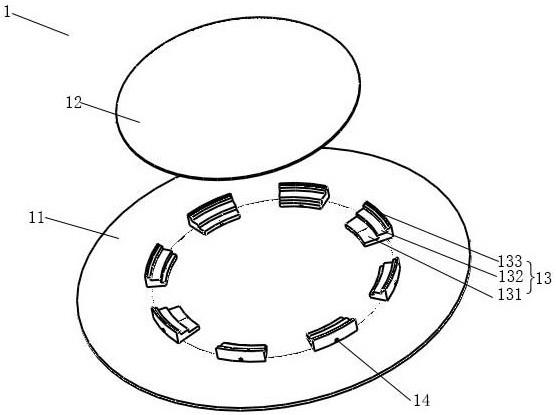

‑

glass)、旋涂聚合物(spin

‑

on

‑

polymer)、 硅碳材料、其化合物、其复合物、或其组合等。ild层及imd层可包括任 何合适数量的介电材料层。导电特征可嵌入在介电层中,并且包括多层金 属线及通孔(图中未示出)。导电特征可包含金属、金属合金等或其组合, 例如钨(w)、铜(cu)、铜合金、铝(al)、铝合金或其组合。在一些实施 例中,互连结构12还包括位于介电结构及导电结构上方的接垫及钝化层。 接垫电连接到导电结构的最顶部导电特征,并且钝化层可部分覆盖接垫并 暴露出接垫的一部分,用于进一步的电连接。接垫是金属接垫,例如铝接 垫。钝化层包含氮化物,例如氮化硅。

30.在一些实施例中,导通孔13形成在衬底10中,并电连接到互连结构12的导电特征。在一些实施例中,导通孔13包括导电柱及环绕导通孔的侧壁及底表面的衬垫(例如,图9a所示的衬垫dl),所述衬垫将导电柱与衬底分离。导电柱可包含铜、铜合金、铝、铝合金、ta、tan、ti、tin、cow或其组合。衬垫可包含介电材料,例如氧化硅、氮化硅等。导通孔13可延伸到互连结构12中,以与互连结构12的导电特征物理接触及电性接触。在一些实施例中,当最初形成导通孔13时,导通孔13嵌入在半导体衬底10中,并且可不延伸到衬底10的后表面bs1。

31.在一些实施例中,接合结构16形成在互连结构12上并电连接到互连结构12。举例来说,接合结构16包括介电层14及多个接合导体15。介电层14包括一层或多层介电材料(例如,无机介电材料),例如氮化硅、氧化硅、高密度等离子体(high

‑

densityplasma,hdp)氧化物、正硅酸四乙酯(tetra

‑

ethyl

‑

ortho

‑

silicate,teos)、未经掺杂的硅酸盐玻璃(undopedsilicateglass,usg)等或其组合。

32.接合导体15形成在介电层14中,并且电连接到互连结构12的导电特征,并且可进一步通过互连结构12电耦合到形成在衬底10中/上的装置,从而提供管芯20的外部电连接。接合导体15可由例如铜、金、铝、镍、钨等或其组合等导电材料形成。接合导体15可包括接合接垫和/或接合通孔,并且可通过单镶嵌工艺或双镶嵌工艺形成。在一些实施例中,接合导体15可延伸到互连结构12中,以与接垫和/或导电结构的最顶部导电特征物理接触及电性接触。图中所示的接合导体15的形状及大小仅用于示例说明,并且本公开不限于此。在一些实施例中,接合导体15的顶表面实质上与介电层14的顶表面共面。

33.图2a到图2d是示出根据本公开第二实施例的制备管芯的各种阶段的示意性剖视图。除了所提供的管芯具有暴露出的导通孔之外,在第二实施例中提供的管芯类似于第一实施例。为了便于理解,相同的元件用相同的参考编号指示,并且在本文中对其细节不再予以赘述。

34.参照图2a,提供包括多个管芯20的晶片w1。管芯20位于管芯区中,并且通过切割区sr彼此间隔开。管芯20的配置类似于图1中所述的配置。举例来说,管芯20包括衬底10、互连结构12、导通孔13及接合结构16。

35.参照图2b,将晶片w1放置在临时载体tc上。在一些实施例中,通过临时接合层tb将晶片w1贴合到临时载体tc。临时载体tc的材料可包括玻璃、金属、陶瓷、硅、塑料、其组合、其多层、或可在后续处理中为晶片w1提供结构支撑的其他合适的材料。在一些实施例中,临时载体tc由玻璃制成,并且临时接合层tb包括粘合剂层(例如,管芯贴合膜(dieattachfilm,daf))、紫外线(ultra

‑

violet,uv)固化层(例如,光

‑

热转换(light

‑

to

‑

heatconversion,lthc)释放涂层、紫外线(uv)胶),所述uv固化层在暴露于辐射源(例如,uv光或激光)时降低或失去其粘合性。可使用其他合适的临时粘合剂。在一些实施例中,将晶片w1的前表面fs1贴合到临时载体tc,并且晶片w1的后表面bs1面向上以进行后续工艺。

36.参照图2b及图2c,通过例如研磨工艺、化学机械抛光(chemicalmechanicalpolishing,cmp)工艺、蚀刻工艺、其组合或其他合适的薄化技术将晶片w1薄化以形成薄化的晶片w1’。举例来说,对晶片w1的背侧执行薄化工艺,使得导通孔13在衬底10的后表面以可接触的方式露出。由于导通孔13延伸穿过衬底10,因此当衬底10是硅衬底时,导通孔13可被称为衬底穿孔(throughsubstratevia,tsv)或硅穿孔(throughsiliconvia)。在

一些实施例中,在薄化之后,薄化的晶片w1’的厚度t2在约5微米到约 500微米或约40微米到约400微米的范围内。tsv 13的露出的表面及衬底 10的后表面构成晶片w1’的后表面bs1。

37.参照图2c及图2d,在晶片背侧薄化之后,将薄化的晶片w1’安装在 胶带框架tp上。在一些实施例中,将图2c所示的结构翻转,并且将管芯 20a的后表面bs1设置在胶带框架tp上。接下来,执行剥离工艺(de

‑

bondingprocess)以从薄化的晶片w1’释放临时载体tc。举例来说,将外部能量(例 如,uv光或激光)施加到临时接合层tb上,以降低或失去其粘合性。在 一些实施例中,通过使用合适的溶剂、清洗化学品或其他清洗技术执行清 洗工艺,以从薄化的晶片w1移除临时接合层tb的残留物。随后,对薄化 的晶片w1’执行单体化工艺。举例来说,在单体化工艺期间,胶带框架tp 将薄化的晶片w1保持就位,并且可使用切割工具(例如,锯)沿着切割 区sr切穿薄化的晶片w1,以将晶片的多个管芯区切分成多个管芯20a。

38.在一些实施例中,可由胶带框架代替图2b及图2c所示的临时载体tc。 举例来说,将半导体晶片w1’安装到第一胶带框架上,使前表面fs1面向 第一胶带框架,且然后对晶片w1’的背侧进行薄化工艺,直到露出导通孔 13。随后,转移薄化的晶片w1’以将其安装在第二胶带框架tp上,使得后 表面bs1面向第二胶带框架,且然后执行单体化工艺,并且在单体化工艺 期间第二胶带框架将薄化的晶片w1’保持就位。

39.在一些实施例中,除了管芯20的导通孔13未被露出、而管芯20a已 被薄化并且其导通孔13被露出之外,管芯20a与在图1中阐述的管芯20 在功能及性质上类似。应注意,提供以上实例是出于说明目的,且本公开 的管芯20a的形成并不限于此,且可以任何逻辑顺序来形成。

40.图3a到图3c是示出根据本公开一些实施例的管芯制造方法中的各种 阶段的示意性剖视图。参照图3a,提供一个或多个管芯40。管芯40可以 是逻辑管芯、存储器管芯、射频管芯、电源管理管芯、微机电系统(mems) 管芯、系统芯片(soc)、中央处理器、图形处理单元、xpu等。管芯40可 包括类似于管芯20的结构。举例来说,管芯40包括衬底30、多个导通孔 33及互连结构32,管芯40的结构特征实质上类似于管芯20(图1)的结 构特征,且在此不再对其予以赘述。管芯40具有彼此相对的前表面fs及 后表面bs。管芯40切自晶片,并且在单体化之前可对晶片进行探测及测 试。在执行单体化工艺之后,仅将已知良好管芯40提供给后续工艺。在一 些实施例中,所提供的管芯40在其互连结构32上方不具有接合结构,但 本公开不限于此。

41.在一些实施例中,类似于管芯20的互连结构12,管芯40的互连结构 32也包括位于介电结构及导电结构(图中未示出)上方的接垫及钝化层。 接垫电连接到导电结构的最顶部导电特征。在一些实施例中,钝化层覆盖 接垫的顶表面及侧壁,并且接垫此时可能不会被钝化层暴露出。也就是说, 钝化层的表面构成管芯40的前表面fs。

42.在一些实施例中,管芯20及管芯20a和/或管芯40是从不同的晶片单 体化的,并且在功能及性质上可不同。举例来说,管芯40是逻辑管芯(例 如,系统芯片(soc)、中央处理器(cpu)、图形处理单元(gpu)等)。 管芯20(图1)或管芯20a(图2d)可以是存储器管芯(例如,动态随机 存取存储器(dynamic random access memory,dram)管芯、静态随机存 取存储器(static random access memory,sram)管芯、同步动态随机存取 存储器(synchronous dynamic random access memory,sdram)、与非 (nand)闪存等)。

43.参照图3b,将管芯40设置在临时载体100上。在一些实施例中,将 临时接合层(图中未示出)沉积在临时载体100上,并且通过临时接合层 将管芯40的前表面fs贴合到临时载体100。临时载体100及临时接合层的 材料可类似于上述临时载体tc及临时接合层tb的材料。

44.参照图3c,对管芯40的背侧执行薄化工艺,直到其导通孔33被衬底 30以可接触的方式露出,由此形成管芯40a。薄化工艺可包括研磨工艺、 cmp工艺、蚀刻工艺等或其组合。在薄化工艺之后,导通孔33穿过衬底 30,并且当衬底30是硅衬底时,导通孔33可被称为衬底穿孔(tsv)或硅 穿孔。导通孔33的顶表面与衬底30的顶表面可实质上彼此共面,并且一 起构成管芯40a的后表面bs。在一些实施例中,薄化的管芯40a具有小于 100微米、例如为约5微米到约100微米的厚度t3。在一些实施例中,厚 度t3至少约为20微米。

45.图4a到图4g是示出根据本公开第一实施例的形成半导体结构的方法 的示意性剖视图。

46.参照图4a,在一些实施例中,在将管芯40a放置在载体100上之后, 可从胶带框架tp(图1中示出)移除在图1中制备的管芯20,以使用例如 拾取及放置工艺(pick

‑

and

‑

place process)或其他合适的贴合技术将管芯20 安装在管芯40a上。在一些实施例中,在将管芯20拾取并放置在管芯40a 上之前,可通过初始薄化工艺薄化管芯20。举例来说,执行初始薄化工艺 以将管芯20的厚度减小到约100微米到约150微米的范围,而不露出管芯20的导通孔13。在将管芯20堆叠在管芯40a上之前,可对管芯20进行测 试,使得仅已知良好管芯(kgd)被用于管芯堆叠。在一些实施例中,管 芯20可以面对背配置(face

‑

to

‑

back configuration)设置在管芯40a上。举 例来说,半导体管芯20的前表面fs1面向管芯40a的后表面bs。也就是 说,接合结构16接合到管芯40a的衬底30及导通孔33。

47.在一些实施例中,通过例如混合接合工艺、熔融接合工艺或其组合等 接合工艺将管芯20接合到管芯40。举例来说,管芯20与管芯40之间的接 合界面包括金属对金属的接合(例如,铜对铜的接合)、金属对介电质的接 合(例如,铜对氧化物的接合)、氧化物对半导体的接合(例如,氧化物对 硅的接合)、介电质对介电质的接合(例如,氧化物对氧化物的接合)、粘 合剂接合和/或其任意组合等。举例来说,通过金属对金属的接合将管芯20 的接合导体15接合到管芯40a的tsv 33,并且通过介电质对半导体的接合 将管芯20的介电层14接合到管芯40a的衬底30。

48.在一些实施例中,接合工艺可执行如下:首先,为了避免出现未接合 区域(即,界面气泡),将管芯20及管芯40a的待接合表面(例如,管芯 20的前表面fs1及管芯40a的后表面bs)处理成足够干净及光滑。然后, 在室温及轻微压力下将管芯20与管芯40a对齐并放置成物理接触,以启动 接合操作。举例来说,接合结构16的接合导体15与导通孔33对齐并放置 成物理接触,且接合结构16的介电层14与衬底30和/或导通孔33对齐并 物理接触。此后,执行热处理,例如在升高温度下的退火工艺,以加强管 芯20与管芯40a的待接合表面之间的化学键,并将化学键转化为共价键。

49.在一些实施例中,接合导体15的尺寸(例如,宽度)小于相应的导通 孔33的尺寸(例如,宽度),并且管芯20的紧邻接合导体15的介电层14 可接合到管芯40a的导通孔33的一部分。在本实施例中,接合导体15的 较小尺寸可有助于防止接合导体15的金属扩散到衬底30中。然而,本公 开不限于此。在一些替代实施例中,接合导体15的尺寸可等于或大于相

应 的导通孔33。

50.在替代实施例中,在薄化管芯40a之后,使衬底30进一步凹陷,使得 导通孔33从衬底30的后表面突出,然后在衬底30的后表面上以及在导通 孔33的侧边形成隔离层。隔离层可包含介电材料,例如氮化硅。此后,在 接合工艺期间,将管芯20的介电结构16接合到管芯40a的导通孔33及隔 离层,其中介电层14通过介电质对介电质的接合而被接合到隔离层,并且 接合导体15通过金属对金属的接合而被接合到导通孔33。在此实施例中, 即使接合导体15的尺寸大于相应tsv的尺寸,隔离层也可有助于防止接合 导体15的金属扩散到衬底30中。在一些其他实施例中,在将管芯20接合 到管芯40a之前,在管芯40a的后表面bs上形成包括接合介电层(图中未 示出;例如,接合氧化物)及接合导体(图中未示出)的接合结构,使得 两个管芯的接合导体通过金属对金属的接合而彼此接合,并且两个管芯中 的一者的接合介电膜通过介电质对介电质的接合而接合到另一管芯的接合 介电膜。应注意,上述接合方法仅仅是实例,且不旨在为限制性的。

51.参照图4b,在将图1中提供的管芯20接合到管芯40a的一些实施例中, 对管芯20进一步执行薄化工艺,以形成管芯20a1。举例来说,执行薄化工 艺直到导通孔13从衬底10露出。在薄化工艺之后,导通孔13的顶表面可 实质上与衬底10的顶表面(即,后表面)共面。薄化工艺可包括研磨工艺、 cmp工艺、蚀刻工艺或其组合。换句话说,管芯20的薄化是在接合管芯 20与管芯40之后进行的。在替代实施例中,通过图2a到图2d中所述的 工艺形成的薄化的管芯20a可用于接合到管芯40a,即,管芯20的薄化工 艺可在接合工艺之前执行。举例来说,在如图2d所示形成管芯20a之后, 从胶带框架tp移除管芯20a,且然后将管芯20a接合到管芯40a。管芯20a 与管芯40a的接合实质上类似于如图4a所述的管芯20与管芯40a的接合。 在一些实施例中,管芯20a用作随后形成的管芯堆叠结构的第一层,且因 此被标记为管芯20a1。在一些实施例中,管芯20a1的厚度可在约5微米到 约100微米的范围内,例如为20微米或40微米。

52.参照图4c,在一些实施例中,随后将多个管芯20a2到20a7堆叠在管芯 40a上方,并且管芯20a1到20a7形成管芯堆叠结构102。管芯20a2到20a7中每一者的结构类似于管芯20a1的结构,在此不再对其予以赘述。举例来 说,在将管芯20a1接合到管芯40a之后,将管芯20a2接合到管芯20a1,并 且管芯20a2与管芯20a1的接合工艺类似于管芯20a1与管芯40a的接合工艺。 可将管芯20a2薄化,并且露出管芯20a2的导通孔13用于进一步的电连接。 用于露出导通孔13的对管芯20a2的薄化可在接合工艺之前或之后执行,此 类似于在图4a及图4b中所述的那样。此后,重复接合工艺和/或薄化工艺, 以在管芯40a上堆叠期望层数的管芯20a。在一些实施例中,管芯20a8是管 芯堆叠结构102的最顶部管芯,并且管芯20a8可设置有嵌入在衬底10中并 且不穿透衬底10的导通孔13。在一些替代实施例中,最顶部管芯20a8被 设置为不具有导通孔13。在一些实施例中,管芯20a1到20a8以面对背配置 彼此堆叠,但本公开不限于此。管芯堆叠结构102可利用任何合适的配置, 例如面对面(face

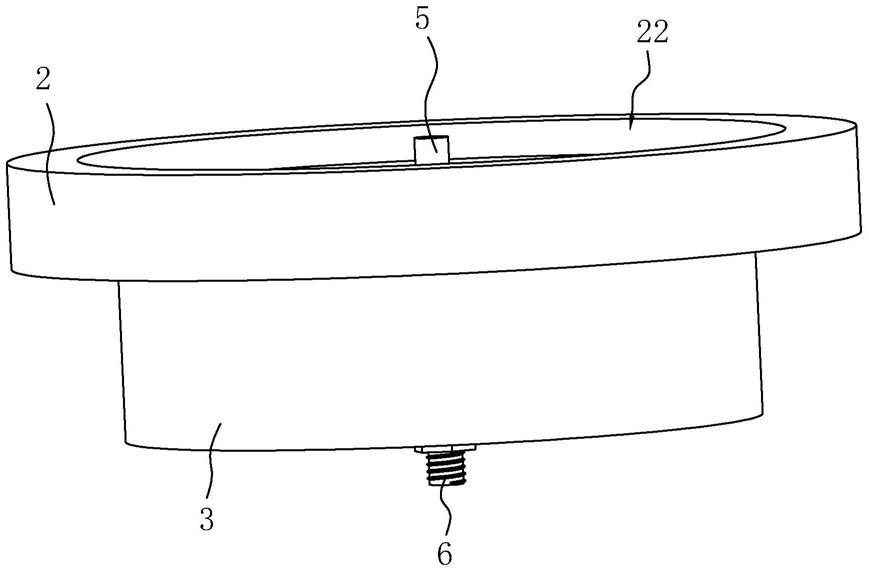

‑

to

‑

face)、面对背(face

‑

to

‑

back)、背对背(back

‑

to

‑

back) 或其组合。应注意,图中所示的堆叠结构102中所包括的管芯的数量仅用 于说明,且本公开不限于此。举例来说,堆叠结构102包括堆叠在管芯40a 上的至少一个管芯。在一些实施例中,堆叠结构102包括至少两个管芯, 并且堆叠结构102中所包括的管芯20a的数量可介于2到64或大于64的 范围内,例如为2、4、8、12、16或64。

53.仍参照图4c,在一些实施例中,将支撑结构109安装在管芯堆叠结构 102上。举例来说,将支撑结构109接合到管芯堆叠结构102的最顶部管芯 20a8。支撑结构109可包括衬底108及接合膜107,并且支撑结构109通过 接合膜107接合到管芯堆叠结构102。在一些实施例中,支撑结构109用于 保护位于其下方的管芯堆叠结构102,并改善所得半导体结构的机械性能和 /或散热性能。在一些实施例中,可将例如盖(例如,图14中所示的盖301) 等其他组件进一步设置在管芯堆叠结构102上方。支撑结构109可为管芯 堆叠结构102上方的组件提供机械支撑,并且用作所述组件与管芯堆叠结 构102之间的缓冲结构,以防止来自所述组件的应力直接施加到管芯堆叠 结构102。因此,避免了可能由直接来自所述组件的应力引起的例如管芯堆 叠结构102的裂纹等损坏。在一些实施例中,支撑结构109具有足够的尺 寸(例如,宽度、厚度)以减小来自所述组件的可被施加到管芯堆叠结构 102上的应力。举例来说,支撑结构109的厚度t4可在约50微米到200 微米的范围内。支撑结构109的宽度可大于管芯堆叠结构102的宽度并且 小于管芯40a的宽度。支撑结构109的宽度将在随后伴随俯视图进行详细 论述。

54.在一些实施例中,支撑结构109还可具有良好的热导率,以高效地从 管芯堆叠结构102传导热量使热量离开管芯堆叠结构102,从而提高所得半 导体结构的散热性能。在一些实施例中,支撑结构109既用作缓冲结构又 用作散热结构,并且选择合适的材料来形成支撑结构109,以改善所得结构 的机械性能以及散热性能。举例来说,支撑结构109(或其衬底108)的杨 氏模量不大于(例如,小于或等于)管芯20a的衬底10的杨氏模量,并且 支撑结构109(或其衬底108)的热导率可大于或等于管芯20a的衬底10 的热导率。在一些实施例中,支撑结构109的衬底108的杨氏模量及热导 率接近管芯20a1到20a8的衬底10的杨氏模量及热导率。

55.在一些实施例中,支撑结构109的衬底108可包含与管芯20a1到20a8的衬底10的材料相同或不同的材料。举例来说,衬底108包含半导体材料, 例如硅芯片、或者薄的铜或铝板。在一些实施例中,支撑结构109的衬底 108可以是切割自晶片的空白硅管芯(blank silicon die),并且支撑结构109 也可被称为虚设管芯结构。空白硅管芯不具有形成在其中的有源或无源装 置。此外,空白硅管芯中可不形成任何金属线、通孔等。此外,衬底108 的材料可以是同质的。举例来说,支撑结构109的整个衬底108可由相同 的材料形成,所述材料在衬底108的所有部分中包含相同的元素,并且元 素的原子百分比在整个衬底108中可以是均匀的。在一些其他实施例中, 衬底108可包含不同于管芯20a1到20a8的衬底10的材料。也可使用其他合 适的材料,只要支撑结构109能够提供如上所述的机械性质及散热性质即 可。

56.在一些实施例中,在将支撑结构109接合到管芯堆叠结构102之前, 通过例如化学气相沉积(chemical vapor deposition,cvd)等沉积工艺在衬 底108上形成接合膜107。接合膜107包含介电材料,例如氧化物(例如, 氧化硅)、未经掺杂的硅酸盐玻璃(usg)、正硅酸四乙酯(teos)等或其 组合。在其中衬底108是切自晶片的空白管芯的一些实施例中,可在晶片 上形成接合膜107,并且将上面具有接合膜的晶片单体化以形成单独的支撑 结构109。

57.在衬底108上形成接合膜107之后,将具有接合膜107的支撑结构109 接合到管芯堆叠结构102。举例来说,通过熔融接合工艺将接合膜107接合 到管芯20a8的后表面bs1,并

且在支撑结构109的接合膜107与管芯20a8的衬底10之间形成介电质对半导体接合界面。在一些其他实施例中,在接 合工艺之前,可进一步在管芯20a8的后表面上形成介电接合膜,并且通过 熔融接合将接合膜107接合到管芯20a8上的介电接合膜,因此可在支撑结 构109与管芯20a8之间形成介电质对介电质接合界面。在替代实施例中, 支撑结构109可仅包括衬底108且不具有接合膜107,并且介电接合膜形成 在管芯20a8的后表面上以接合到衬底108。

58.参照图4d,在一些实施例中,可通过包覆成型工艺(over

‑

moldingprocess)在载体100上方形成包封件材料层110’。包封件材料层110’具有 高于支撑结构109的顶表面的实质上平坦的顶表面,以包封管芯40a、管芯 堆叠结构102及支撑结构109的顶表面及侧壁。包封件材料层110’可包含 模制化合物、模制底部填充材料、例如环氧树脂等树脂、其组合等。在一 些其他实施例中,包封件材料层110’包含光敏材料,例如聚苯并恶唑 (polybenzoxazole,pbo)、聚酰亚胺(polyimide,pi)、苯并环丁烯 (benzocyclobutene,bcb)、其组合等。在替代实施例中,包封件材料层 110’包含氮化物(例如,氮化硅)、氧化物(例如,氧化硅)、磷硅酸盐玻璃 (psg)、硼硅酸盐玻璃(borosilicate glass,bsg)、掺杂有硼的磷硅酸盐玻 璃(boron

‑

doped phosphosilicate glass,bpsg)、其组合等。

59.在一些实施例中,包封件材料层110’是模制化合物,所述模制化合物 是包括基材b及基材b中的多个填料(filler)f的复合材料。在一些实施 例中,包封件材料层110’还可包含添加剂,例如硬化剂。基材b可包括树 脂,例如环氧树脂等。填料f可包括单一元素、化合物(例如,氮化物、 氧化物或其组合)。举例来说,填料f可包括氧化硅、氧化铝、氮化硼、铝 氧化物、二氧化硅等或其组合。在一些实施例中,填料f是球形颗粒或类 似物。填料f的横截面形状可以是圆形、椭圆形或任何其他合适的形状。 在一些实施例中,填料f是实心填料,但本公开不限于此。在一些实施例 中,一小部分填充剂f可以是空心填料。

60.参照图4d及图4e,执行平坦化工艺(例如,研磨工艺、cmp工艺或 其组合)以移除支撑结构109的顶表面上方的包封件材料层110’,从而形 成包封件110。在一些实施例中,包封件110的顶表面实质上与支撑结构 109的顶表面共面。包封件在侧向上包封管芯40a、管芯堆叠结构102及支 撑结构109。在一些实施例中,包封件110也可被称为绝缘结构is1。

61.在本实施例中,在已将支撑结构109接合到管芯堆叠结构102之后形 成包封件110,并且支撑结构109的尺寸被配置成大于管芯堆叠结构102的 尺寸并且小于管芯40a的尺寸,使得包封件材料可进入支撑结构109与管 芯40a之间的空间以在侧向上包封管芯堆叠结构102。在一些实施例中,在 接合支撑结构109之后形成包封件110具有一些优点。举例来说,如果首 先在管芯堆叠结构102的侧边形成包封件,并且随后通过熔融接合工艺将 支撑衬底109接合到管芯堆叠结构102及包封件,那么包封件的有机材料 可能不能很好地熔融接合到接合膜107的无机材料。

62.参照图4f,可选择性地将另一临时载体101贴合到绝缘结构is1及的 支撑结构109的与临时载体100相对的一侧。执行剥离工艺以从上覆结构 释放临时载体100,使得管芯40a的前表面fs被暴露出。在一些实施例中, 在剥离临时载体100之后,清洁管芯40a的前表面fs以用于进一步处理。

63.参照图4f及图4g,在移除临时载体100之后,管芯40a的前表面fs 暴露出来。可随后在管芯40a的前表面fs上形成多个导电端子150,以电 连接到管芯40a及管芯堆叠结构

102。在互连结构32包括覆盖接垫(金属特征)的钝化层(图中未示出)的一些实施例中,移除钝化层的一部分以形成开口。钝化层的开口可以可接触的方式暴露出位于下方的金属特征的至少一部分。接下来,可使用例如溅射、印刷、镀覆、沉积等在钝化层的开口中形成导电端子150,以与互连结构32的金属特征电接触。导电端子150可由包括铜、铝、金、镍、银、钯、锡、焊料、金属合金等或其组合的导电材料形成。作为另外一种选择,在形成导电端子150之前,依据设计要求,可在管芯40a的前表面fs处执行其他工艺。

64.举例来说,导电端子150包括导电凸块148。导电凸块148可以是微凸块、金属柱、化镍钯浸金(electrolessnickel

‑

electrolesspalladium

‑

immersiongold,enepig)形成的凸块、受控塌陷芯片连接(controlledcollapsechipconnection,c4)凸块、球栅阵列(bga)凸块等。导电凸块148可以是无焊料的,并且可具有实质上垂直的侧壁。在一些实施例中,每个导电端子150包括通过例如镀覆、印刷等形成在导电凸块148顶部上的金属帽149。举例来说,金属帽149的材料包括镍、锡、锡

‑

铅、金、银、钯、镍

‑

钯

‑

金、镍

‑

金等或其组合。

65.在一些实施例中,在形成导电端子150之后,从绝缘结构is1及支撑结构109剥离临时载体101(图4f所示)。随后,执行单体化工艺以形成多个半导体结构s1。可通过例如锯切、激光切割等或其组合沿着切割线(图中未示出)执行单体化。在一些实施例中,管芯40a的侧壁在单体化后被绝缘结构is1暴露出,但本公开不限于此。在替代实施例中,管芯40a的侧壁可被绝缘结构is1覆盖。

66.参照图4g,如此一来便形成了半导体结构s1。半导体结构s1也可被称为封装结构,例如三维集成电路(integratedcircuit,ic)封装。在一些实施例中,半导体结构s1包括管芯40a、管芯堆叠结构102、支撑结构109、绝缘结构is1及导电端子150。管芯堆叠结构102的顶表面可(完全或部分)被支撑结构109覆盖。管芯堆叠结构102包括电连接到管芯40a的多个管芯(例如,管芯20a1到20a8)。在一些实施例中,管芯40a例如是被配置成执行读取、编程、擦除和/或其他操作的逻辑管芯,并且管芯堆叠结构102例如是包括彼此堆叠并由管芯40a编程的存储器管芯的存储器堆叠。在一些实施例中,半导体结构s1的从支撑结构109的顶表面到管芯40a的底表面的高度可在约500微米到约780微米的范围内。

67.将支撑结构109设置在管芯堆叠结构102上,以改善半导体结构s1的机械性能及散热性能。在一些实施例中,绝缘结构is1设置在管芯40a上,并且在侧向上包裹在管芯堆叠结构102及支撑结构109周围。在一些实施例中,绝缘结构is1是单层结构,并且包括在侧向上包封管芯堆叠结构102及支撑结构109的包封件110。绝缘结构is1的侧壁可与管芯40a的侧壁对齐。在一些实施例中,支撑结构109的侧壁及底表面的一部分被绝缘结构is1覆盖并与绝缘结构is1物理接触,并且支撑结构109的顶表面实质上与绝缘结构is1的顶表面共面。

68.图12a及图12b是根据本公开一些实施例的半导体结构s1的俯视图,且图4g是沿着图12a及图12b的i

‑

i’线的剖视图。为简洁起见,在俯视图中未示出导电端子150。

69.参照图4g及图12a,管芯堆叠结构102垂直地位于管芯40a与支撑结构109之间。在一些实施例中,管芯堆叠结构102中所包括的管芯20a1到20a8的侧壁实质上彼此对齐。支撑结构109、管芯堆叠结构102及管芯40a的侧壁可在侧向上彼此偏移。举例来说,管芯40a在侧向上延伸超出管芯堆叠结构102的侧壁(或边缘)及支撑结构109的侧壁(或边缘),并且

支 撑结构109在侧向上延伸超出管芯堆叠结构102的侧壁(或边缘)。当在俯 视图中观察时,支撑结构109的侧壁可在平行于管芯堆叠结构102的顶表 面的侧向方向上侧向地位于管芯堆叠结构102的相应侧壁与管芯40a(或包 封件110)的侧壁之间。在一些实施例中,支撑结构109在侧向上延伸超出 管芯堆叠结构102的四个侧壁中的至少两个相对侧壁。

70.换句话说,管芯40a具有比管芯堆叠结构102及支撑结构109更大的 尺寸(例如,宽度或面积),并且支撑结构109的尺寸可大于管芯堆叠结构 102的尺寸并且小于管芯40a的尺寸。在一些实施例中,从俯视图来看,管 芯40a、管芯堆叠结构102及支撑结构109的形状可分别是正方形、矩形、 其类似形状或任何合适的形状。

71.举例来说,支撑结构109、管芯堆叠结构102及管芯40a中的每一者包 括分别沿着第一方向d1及第二方向d2延伸的两组相对的侧壁。举例来说, 第一方向d1与第二方向d2彼此垂直。管芯堆叠结构102在第一方向d1 上具有第一宽度w0,且在第二方向d2上具有第二宽度w4。支撑结构109 在第一方向d1上具有第一宽度w2,且在第二方向d2上具有第二宽度w5。 管芯40a在第一方向d1上具有第一宽度w3,且在第二方向d2上具有第 二宽度w6。举例来说,在相同的方向d1或d2上,管芯40a的第一宽度 w3/第二宽度w6分别大于支撑结构109的相应第一宽度w2/第二宽度w5 以及管芯堆叠结构102的相应第一宽度w0/第二宽度w4。支撑结构109的 第一宽度w2/第二宽度w5中的至少一者大于管芯堆叠结构102的相应第 一宽度w0/第二宽度w4。在一些实施例中,支撑结构109的第一宽度w2 及第二宽度w5两者均大于管芯堆叠结构102的相应第一宽度w0及第二宽 度w4。举例来说,管芯堆叠结构102的宽度w0对支撑结构109的宽度 w2对管芯40a的宽度w3的比率(w0:w2:w3)可大约为1:2:2.5。管芯堆 叠结构102的宽度w4对支撑结构109的宽度w5对管芯40a的宽度w6 的比率(w4:w5:w6)可大约为1:2:2.5。

72.在一些其他实施例中,支撑结构109可包括多个分立的区块(或称为 分区),例如多个虚设管芯分区。举例来说,如图12b所示,支撑结构109 可包括被配置为并排位于管芯堆叠结构102上的第一支撑结构109a及第二 支撑结构109b。第一支撑结构109a及第二支撑结构109b中的每一者可具 有如图4g所示的剖面结构。在此实施例中,绝缘结构is1还设置在第一支 撑结构109a与第二支撑结构109b之间,并且管芯堆叠结构102的顶表面 的一部分被在侧向上位于第一支撑结构109a与第二支撑结构109b之间的 绝缘结构is1覆盖并与绝缘结构is1接触。应理解,俯视图中示出的支撑结 构的尺寸、配置及数量仅用于例示说明,并且本公开不限于此。在替代实 施例中,可将具有任何合适尺寸的两个以上的支撑结构以任何合适的配置 设置在管芯堆叠结构上,只要支撑结构提供如上所述的机械性质及散热性 质即可。

73.参照图4g,在一些实施例中,管芯堆叠结构102的管芯可具有为直角 的拐角或圆化拐角。举例来说,管芯堆叠结构102的管芯20a1到20a8中的 一者或多者可具有圆化拐角rc或圆化边缘。在一些实施例中,圆化拐角 rc可能产生于背侧薄化工艺期间(例如,结合图4b所阐述的步骤)。举例 来说,与半导体管芯的边缘接触的研磨垫使半导体管芯的边缘圆化。作为 另外一种情况,在单体化工艺期间,圆化拐角rc可通过连续及周边切割而 产生。

74.圆化拐角rc连接到相应管芯的后表面bs1及侧壁。管芯的后表面bs1 可与上覆管芯的介电层14或与支撑结构109接触。在一些实施例中,介电 层14的底表面及支撑结构109的底表面实质上是平坦的,并且在相应管芯 的介电层14的底表面与圆化拐角rc之间和/或

在支撑结构109的底表面与 圆化拐角rc之间形成间隙。在此实施例中,绝缘结构is1可填充到间隙中, 以覆盖圆化拐角rc及相应管芯的介电层14的底表面的一部分,和/或覆盖 圆化拐角rc及支撑结构109的底表面的一部分。换句话说,绝缘结构is1 的一部分可垂直夹置在管芯堆叠结构102的相邻两个管芯之间,和/或垂直 夹置在管芯堆叠结构102的最顶部管芯与支撑结构109之间。

75.在一些实施例中,具有圆化拐角rc的管芯可有利地用于装置封装配置 中。举例来说,由于应力(例如,热应力和/或机械应力)在堆叠结构中的 边界以及管芯的拐角及边缘处最高,因此管芯的拐角及边缘是最高应力位 置,并且易于开裂。而通过形成圆化拐角rc,管芯可分散边缘/拐角区域的 应力。

76.图5a到图5g是示出根据本公开第二实施例的形成半导体结构的方法 的剖视图,第二实施例与第一实施例的不同之处在于绝缘结构是介电结构 (例如,无机介电结构)与包封件的组合,具体阐述如下。

77.参照图3c及图5a,在一些实施例中,在将管芯40a安装在载体100 上之后,在载体100上形成介电材料层200,以覆盖管芯40a的侧壁及顶表 面(例如,后表面bs)。在形成介电材料层200之前,管芯40a的导通孔 33可能已被露出,但本公开不限于此。在一些实施例中,介电材料层200 包含无机介电材料,例如氧化物(例如,氧化硅)、氮化物(例如,氮化硅)、 氮氧化物(例如,氮氧化硅)、碳氮化硅(sicn)、碳氧化硅(sico)或其 组合。介电材料层200的形成方法包括沉积工艺,例如化学气相沉积(cvd)、 等离子体增强化学气相沉积(plasma

‑

enhanced chemical vapor deposition, pecvd)等。

78.在一些实施例中,介电材料层200与载体100上的管芯40a共形,并 且具有非平面表面。举例来说,介电材料层200包括位于管芯40a的顶表 面上的多个突起及位于管芯40a之间的间隙填充部分。

79.参照图5a到图5b,此后,对介电材料层200执行平坦化工艺,以在 管芯40a的侧边形成介电层200a。平坦化工艺可包括蚀刻工艺、研磨工艺、cmp工艺或其组合。在一些实施例中,通过平坦化工艺移除介电材料层200 的位于管芯40a的顶表面上方的一部分。在一些其他实施例中,平坦化工 艺可进一步移除管芯40a的一些部分及介电材料层200的位于管芯40a侧边 的一部分。举例来说,在一些实施例中,在形成介电材料层200之前,管 芯40a的导通孔33可不被露出,并且平坦化工艺可移除管芯40a的一些部 分以露出导通孔33。在一些实施例中,在执行平坦化工艺之后,介电层200a 的顶表面实质上与管芯40a的顶表面共面。

80.参照图5c,将管芯20a1电性接合到管芯40a,并且在管芯40a及介电 层200a上方形成介电材料层201,以覆盖管芯20a的顶表面(例如,后表 面)及侧壁。在一些实施例中,在形成介电材料层201之前,导通孔13可 能已被露出。介电材料层201可包含与介电材料层200相同或不同的材料。 在一些实施例中,介电材料层201包含无机介电材料,例如氧化物(例如, 氧化硅)、氮化物(例如,氮化硅)、氮氧化物(例如,氮氧化硅)、碳氮化 硅(sicn)、碳氧化硅(sico)或其组合。介电材料层201的形成方法包 括沉积工艺,例如化学气相沉积(cvd)、等离子体增强化学气相沉积 (pecvd)等。

81.在一些实施例中,介电材料层201与管芯20a1共形,并且具有非平面 表面。举例来说,介电材料层201包括位于管芯20a的顶表面上的多个突 起及位于管芯20a1之间的间隙填充部分。

82.参照图5c到图5d,此后,对介电材料层201执行平坦化工艺,以在 管芯20a1的侧边形成介电层201a。平坦化工艺可包括蚀刻工艺、研磨工艺、 cmp工艺或其组合。在一些实施例中,通过平坦化工艺移除介电材料层201 的位于管芯20a1的顶表面上方的一部分。在一些其他实施例中,平坦化工 艺可进一步移除管芯20a1的一些部分及介电材料层201的位于管芯20a1侧 边的一部分。在一些实施例中,在平坦化工艺期间实现对导通孔13的露出。 举例来说,在形成介电材料层201之前,管芯20a1的导通孔13可不被露出, 并且平坦化工艺可移除管芯20a1的一些部分以露出tsv 13。在一些实施例 中,在执行平坦化工艺之后,介电层201a在侧向上环绕管芯20a1,并且填 充在侧向上位于管芯20a1之间的空间,并且也可被称为间隙填充结构。介 电层201a的顶表面实质上与管芯20a1的顶表面共面。

83.参照图5e,在一些实施例中,随后将多个管芯(例如,管芯20a2到20a8) 堆叠在管芯20a1上及介电层201a上方,并且将支撑结构109接合到最顶部 管芯20a8。管芯20a1到20a8构成电接合到管芯40a的管芯堆叠结构102。 管芯与支撑结构109的接合工艺类似于第一实施例中所阐述者,在此不再 予以赘述。

84.参照图5f,在介电层201a上形成包封件210,以在侧向上包封管芯20a2到20a8及支撑结构109的侧壁。可通过包覆成型工艺及平坦化工艺形成包 封件210。包封件210的材料类似于在第一实施例中阐述的包封件110的材 料,在此不再予以赘述。

85.参照图5f及图5g,此后,执行类似于在图4e到图4f中所阐述的工 艺。举例来说,可将临时载体贴合到包封件210及支撑结构109,并且从上 覆结构释放临时载体100。此后,在管芯40a上形成导电端子150,以电连 接到管芯40a及管芯堆叠结构102。然后释放临时载体,并执行单体化工艺 以形成单独的半导体结构s2。在一些实施例中,可通过单体化工艺移除介 电层200a,并且介电层200a不保留在半导体结构s2中,但本公开不限于 此。在替代实施例中,介电层200a可保留在半导体结构s2中,并且保留 的介电层200a的侧壁可实质上与介电层201a的侧壁及包封件210的侧壁对 齐。

86.参照图5g,半导体结构s2包括管芯40a、管芯堆叠结构102、支撑结 构109、包括介电层201a的介电结构di及包封件210。在一些实施例中, 介电层201a在侧向上包裹在管芯20a1周围。包封件210在侧向上包封管芯 20a2到20a8及支撑结构109。介电结构di及包封件210一起构成在侧向上 包裹在管芯堆叠结构102及支撑结构109周围的绝缘结构is2。介电结构 di也可被称为第一绝缘结构,且包封件210也可被称为第二绝缘结构。

87.介电层201a与包封件210包含彼此不同的材料。举例来说,介电层201a 包含无机介电材料,且包封件210包含有机材料。在一些实施例中,包封 件210包含填料(图4d中所示),而介电层201a不含填料。包封件210的 一些填料可与介电结构di的顶表面接触。介电结构di与包封件210之间 存在界面if。举例来说,界面if是无机/有机界面。在一些实施例中,界面 if实质上与管芯20a1的顶表面(例如,后表面)共面。

88.在一些实施例中,包封件210的热膨胀系数(coefficients of thermalexpansion,cte)大于管芯堆叠结构102及支撑结构109的cte,介电结 构di的cte小于包封件210的cte,并且更接近管芯堆叠结构102的管 芯(例如,所述管芯的衬底10)的cte及支撑结构109的cte。因此,介 电结构di可有助于减小绝缘结构is2的cte,并因此减小绝缘结构is2与 管芯堆叠结构102/支撑结构109之间的cte失配。在一些实施例中,绝缘 结构中的介电结构di的比例越高,绝缘结构的cte可减小得越多。

89.在图5g所示的半导体结构s2中,介电结构di仅形成在管芯堆叠结构 102的第一层(即,管芯20a1)的侧边,并且管芯堆叠结构102的更上层(即, 管芯20a1到20a7)在侧向上被包封件210包封。然而,本公开不限于此。 在绝缘结构包括介电结构与包封件的组合的实施例中,管芯堆叠结构102 的被介电结构di包围的管芯数量及管芯堆叠结构102的被包封件210包封 的管芯数量不限于此。

90.图6a及图6b示出根据本公开一些其他实施例的半导体结构s3/s4。 除了半导体结构s3/s4的介电结构di在绝缘结构中占据更大的比例之外, 半导体结构s3/s4类似于半导体结构s2。

91.参照图6a,半导体结构s3包括在侧向上包裹在管芯堆叠结构102及 支撑结构109周围的绝缘结构is3。半导体结构s3包括介电结构di及位于 介电结构di上的包封件210。绝缘介电结构di包括多个介电层,并且所述 多个介电层中的每一者在侧向上包裹在管芯堆叠结构102的一个或多个管 芯周围。所述多个介电层可通过类似于介电层201a的工艺形成。举例来说, 如图5a到图5d所述,可通过重复管芯接合及在管芯侧边形成介电层的工 艺来形成在其侧边具有介电结构的堆叠管芯。

92.换句话说,管芯堆叠结构102的多于一个层(例如,管芯20a1及20a2、 管芯20a1到20a3、管芯20a1到20a4、管芯20a1到20a5、管芯20a1到20a6或管芯20a1到20a7)可在侧向上被介电结构di包围,而管芯堆叠结构102 相应的其他上部层(例如,管芯20a3到20a8、管芯20a4到20a8、管芯20a5到20a8、管芯20a6到20a8、管芯20a7到20a8、管芯20a8)及支撑结构109 在侧向上被包封件210包封。在一些实施例中,管芯堆叠结构102的所有 管芯20a1到20a8在侧向上被介电结构di包围,且支撑结构109在侧向上 被包封件210包封。在此类实施例中,绝缘结构is3可包括位于介电结构 di的两个相邻介电层之间的无机/无机界面、以及位于介电结构di的最顶 部介电层与包封件210之间的无机/有机界面。

93.参照图6b,在替代实施例中,半导体结构s4包括绝缘结构is4,绝缘 结构is4仅包括(无机)介电结构di,并且不含包封件(无机材料)。换句 话说,管芯堆叠结构102的所有管芯20a1到20a8及支撑结构109在侧向上 被介电结构di包围。在一些实施例中,介电结构di包括分别位于管芯20a1到20a8及支撑结构109侧边的多个介电层201a1到201a9。举例来说,介电 结构di包括位于相邻介电层之间的多个无机/无机界面。介电层201a1到 201a9中的每一者的顶表面可实质上与相应管芯20a1到20a8或支撑结构109 的顶表面共面。在此类实施例中,在最顶部管芯20a8旁边形成介电层201a8之后,通过熔融接合工艺将支撑结构109接合到管芯20a8及介电层201a8, 并且在支撑结构109的接合膜107与管芯20a8的衬底10之间、以及在支撑 结构109的接合膜107与介电层201a8之间形成接合界面。举例来说,接合 支撑结构109与管芯20a8之间的接合界面可包括介电质对半导体的接合, 且接合支撑结构109与介电层201a8之间的接合界面可包括介电质对介电质 的接合。

94.图7示出根据本公开一些其他实施例的半导体结构s5。除了半导体结 构s5不具有绝缘结构之外,半导体结构s5类似于上述半导体结构。

95.参照图7,在一些实施例中,半导体结构s5包括管芯40a、管芯堆叠 结构102、支撑结构109及导电端子150。在一些实施例中,管芯40a、管 芯堆叠结构102及支撑结构109的侧壁被暴露出。举例来说,可跳过形成 绝缘结构的工艺。

96.图8a到图8f是示出根据本公开第三实施例的形成半导体结构的方法 的剖视图。

除了在将另一管芯接合到管芯之前在管芯上进一步形成隔离层 之外,第三实施例类似于第一实施例及第二实施例。图9a到图9c是根据 本公开的一些示例性实施例的在图8a或图8c中概述的用于形成隔离层的 工艺期间的中间步骤的虚线区域c的放大示意性剖视图。

97.参照图3c及图8a,在一些实施例中,在载体100上形成管芯40a之 后,使管芯40a的衬底30进一步凹陷,使得导通孔33从衬底30的顶表面 (例如,后表面)突出。此后,在载体100上形成隔离层il0,以覆盖管芯 40a的衬底30的侧壁及顶表面。隔离层il0的最顶部表面可实质上与导通 孔33的顶表面共面或者低于导通孔33的顶表面。下面接合图9a到图9c 的放大图进行详细阐述。

98.参照图8a及图9a,在导通孔33从衬底30的顶表面露出之后,可通 过蚀刻工艺使衬底30进一步凹陷,使得导通孔(即,tsv)33从衬底30 的后表面突出。tsv 33可从衬底30的后表面突出约几微米。在一些实施例 中,将介电衬垫dl插置于衬底30与tsv 33之间,并且介电衬垫dl也可 随着衬底10凹陷而凹陷,并且介电衬垫dl的顶表面可与衬底30的顶表面 (例如,后表面)实质上共面,但本公开不限于此。在替代实施例中,可 不使介电衬垫dl凹陷。

99.参照图8a、图9b及图9c,通过例如旋涂、化学气相沉积(cvd)工 艺等将隔离材料层il’(例如,氮化硅、氧化物、氮氧化硅、碳化硅、聚合 物等)共形地形成在载体100及管芯40a上。作为另外一种选择,可在衬 底30的后表面上形成原生氧化物(native oxide)。隔离材料层il’可足够厚 以覆盖tsv 33的突出部分。在此类实施例中,可通过任何合适的薄化工艺 (例如,蚀刻、例如研磨、化学机械抛光(cmp)工艺等平坦化工艺)移 除隔离材料层il’的一部分,从而以可接触的方式露出tsv 33,用于进一步 的电连接。举例来说,可执行在tsv 33与隔离材料层il’的材料之间具有 高蚀刻速率选择性的蚀刻工艺,以移除隔离材料层il’的在tsv 33的顶表 面上的一部分,从而形成隔离层il0。在一些实施例中,如图9c所示,突 出于衬底30的后表面的tsv 33的底部在侧向上被隔离层il0覆盖,并且 突出于衬底30的后表面的tsv 33的顶部被隔离层il0暴露出。然而,本 公开不限于此。在替代实施例中,隔离材料层il’被形成为足够厚,并且执 行平坦化工艺以移除在tsv 33上方的隔离材料层,并且在平坦化工艺之后, tsv 33的突出部分可在侧向上被隔离层il0完全覆盖,并且tsv 33的顶 表面可与隔离层il0的最顶部表面实质上共面(如图8a所示)。

100.参照图8b,然后通过类似于图4a到图4b中阐述的接合工艺将管芯 20a1接合到管芯40a。举例来说,以面对背的配置将管芯20a1接合到管芯 40a,并且将管芯20a1的接合结构16接合到管芯40a。在本实施例中,由于 隔离层il0形成在管芯40a的衬底30的后表面上,因此管芯20a1的接合结 构16接合到管芯40的tsv 33及隔离层il0。举例来说,接合结构16的介 电层14通过介电质对介电质的接合(例如,氧化物对氮化物的接合)而接 合到隔离层il0,并且接合结构16的接合导体15通过金属对金属的接合而 接合到tsv 33。在此类实施例中,接合导体15的尺寸(例如,底部宽度) 可小于、等于或大于相应tsv 33的尺寸(例如,顶部宽度)。如果接合导 体15的尺寸大于相应tsv 33的尺寸,那么隔离层il0可有助于防止接合 导体15的金属扩散到管芯40a的衬底10中。

101.参照图8b及图8c,在管芯20a1的导通孔13被衬底10露出之后,可 使管芯20a1的衬底10进一步凹陷,使得导通孔13突出于衬底10的顶表面 (例如,后表面),并且在载体10上方进一步形成隔离层il1以覆盖管芯 20a1的侧壁、衬底10的顶表面及隔离层il0的未被管

芯20a1覆盖的部分。 导通孔13的突出于衬底10的顶表面的部分可在侧向上被隔离层il1部分 地或完全地覆盖,并且导通孔13的顶表面可低于隔离层il1的最顶部表面 或者实质上与隔离层il1的最顶部表面共面。隔离层il1的材料及形成方法 类似于隔离层il0的材料及形成方法,在此不再予以赘述。

102.参照图8d,此后,重复与在图8b到图8c中阐述的工艺类似的工艺, 以在管芯20a1上接合多个管芯(例如,管芯20a2到20a8),并且在接合工艺 之前在相应管芯的后表面上形成隔离层(il2到il8)。举例来说,将管芯 20a3接合到管芯20a2,将管芯20a4接合到管芯20a3,将管芯20a5接合到管 芯20a4,将管芯20a6接合到管芯20a5,将管芯20a7接合到管芯20a6,并且 将管芯20a8接合到管芯20a7。在执行管芯接合工艺之前,分别在相应的管 芯上形成隔离层il2到il7。在管芯20a8是管芯堆叠结构102的最顶部管芯 的一些实施例中,可省略在管芯20a8上形成隔离层,并且管芯20a8的侧壁 及顶表面可不被隔离层覆盖。

103.仍参照图8d,隔离层il0到il7的厚度及材料可彼此相同或不同。在 一些实施例中,在较低水平高度处覆盖管芯侧壁的隔离层的层数及厚度大 于在较高水平高度处覆盖管芯侧壁的隔离层的层数及厚度。举例来说,覆 盖各个管芯侧壁的隔离层的层数及厚度从底部到顶部逐渐减小。举例来说, 在本实施例中,覆盖管芯40a的侧壁的八层隔离层(il0到il7)的厚度大 于覆盖管芯堆叠结构102的最底部管芯20a1的侧壁的七层隔离层(il1到 il7)的厚度。在一些实施例中,在管芯堆叠结构102中,最底部的管芯20a1具有覆盖其衬底10的侧壁的最厚隔离层(il1到il7),并且紧接在最顶部 管芯20a8下方的管芯20a7具有覆盖其衬底10的侧壁的最薄隔离层(il7)。

104.仍参照图8d,在一些实施例中,最顶部管芯20a8的导通孔13可不从 管芯20a8的后表面露出,或者最顶部管芯20a8可在衬底中不包括导通孔。 在将管芯堆叠结构102的最顶部管芯20a8接合到下方的管芯20a7之后,通 过接合膜107将支撑结构109接合到管芯20a8。

105.参照图8e,此后,可执行类似于图4e到图4g中所述的工艺。举例来 说,可在载体100上形成绝缘结构is1(例如,包封件110)以在侧向上包 封管芯40a、管芯堆叠结构102及支撑结构109。可通过包覆成型工艺及平 坦化工艺形成绝缘结构is1。绝缘结构is1的顶表面可实质上与支撑结构109 的顶表面共面。此后,可选择性地将载体101贴合到支撑结构109及绝缘 结构110。将载体100从上覆结构脱离。

106.参照图8e及图8f,在移除临时载体100之后,可在管芯40a的前表面 上形成导电端子150。在一些实施例中,在形成导电端子150之前,在管芯 40a的前表面fs上形成保护层pt。在一些实施例中,保护层pt可延伸以 覆盖隔离层il0。举例来说,保护层pt包含钝化材料,例如氧化硅、氮化 硅、未经掺杂的硅酸盐玻璃、聚酰亚胺或用于保护下方结构的其他合适的 绝缘材料。作为另外一种选择,可省略保护层pt。在一些实施例中,保护 层pt包括多个开口,所述多个开口暴露出管芯40a的导电特征的至少一部 分,以进行进一步的电连接。举例来说,在保护层pt的开口中形成导电端 子150以与管芯40a的互连结构32的导电特征物理接触及电性接触。导电 端子150的形成工艺可类似于结合图4f所阐述的工艺,并且为简洁起见不 再对其予以赘述。

107.参照图8f,因此便完成了半导体结构s6。半导体结构s6包括管芯40a、 管芯堆叠结构102、隔离层il0到il7、支撑结构109、绝缘结构is1及导 电端子150。在一些实施例中,管芯侧边的隔离层il0到il7的一些部分彼 此堆叠,并且最顶部的隔离层il7被包封件110覆

盖并与包封件110接触。 其他隔离层il0到il6与包封件110分离。在一些实施例中,绝缘结构is1 的侧壁可实质上与隔离层il0到il7的侧壁对齐。管芯40a的侧壁可被隔离 层覆盖或暴露出。

108.图10a及图10b是根据本公开一些其他实施例的半导体结构s7/s8的 剖视图。除了使用包括无机介电结构的绝缘结构之外,图10a及图10b中 所示的半导体结构s7/s8类似于半导体结构s6。

109.参照图10a,在一些实施例中,半导体结构s6包括介电结构di及位 于介电结构di上方的包封件210。介电结构di可包括多个介电层,且隔离 层与介电层可彼此交替堆叠。举例来说,介电结构di包括位于管芯40a侧 边的介电层200a及位于管芯20a1侧边的介电层201a1。在一些实施例中, 介电层200a与介电层201a1通过位于两者之间的隔离层il1彼此分离,且 介电层201a1与包封件210通过位于两者之间的隔离层il2彼此分离。

110.在一些实施例中,介电结构di及包封件210可如下形成:在将隔离层 il0形成为在管芯40a上及管芯40a侧边延伸之后,在管芯40a侧边形成介 电层200a,使得介电层200a的顶表面实质上与隔离层il0的最顶部表面以 及管芯40a的tsv 33的最顶部表面共面。此后,将管芯20a1接合到管芯 40a,并且将隔离层il1形成为沿着管芯20a1的表面、隔离层il0的顶表面 及介电层200a的顶表面延伸。然后在管芯20a1的侧边形成介电层201a1。 之后,将管芯20a2到20a8接合到管芯20a1上,并且在相应的接合工艺之前, 分别在管芯20a2到20a7的后表面上形成隔离层il2到il7。在将支撑结构 109接合到管芯堆叠结构102之后,形成包封件210以在侧向上包封管芯 20a2到20a7及支撑结构109。

111.参照图10b,在一些实施例中,半导体结构s8包括不含包封件的绝缘 结构is3。在一些实施例中,在管芯40a上形成隔离层il0并且在管芯40a 的侧边形成介电层200a之后,重复执行包括管芯接合、在管芯上形成隔离 层以及在隔离层上及在管芯的侧边形成介电层的工艺,以堆叠管芯20a1到 20a7并且在管芯40a上方形成隔离层il1到il7及介电层201a1到201a7。 在管芯20a8是管芯堆叠结构102的最顶部管芯的一些实施例中,在将管芯 20a8接合到管芯20a7之后,在介电层201a7上及管芯20a8的侧边形成介电 层201a8,而不形成隔离层。此后,将保护层109接合到管芯20a8及介电层 201a8,且然后在支撑结构109的侧边形成介电层201a9。

112.绝缘结构is3包括多个介电层200a及201a1到201a9。介电层200a在 侧向上位于管芯40a侧边,介电层201a1到201a8分别在侧向上位于管芯20a1到20a8侧边,且介电层201a9在侧向上位于支撑结构109侧边。在一些实施 例中,隔离层il0到il7分别被形成为沿着相应的管芯及介电层延伸。隔离 层il0到il7的一些部分与介电层200a及201a1到201a7交替堆叠。介电层 201a1到201a7的相邻两个介电层被其间的相应隔离层分隔开。在一些实施 例中,管芯20a8是管芯堆叠结构102的最顶部管芯并且不具有隔离层,并 且介电层201a7到201a8彼此接触。

113.图11a到图11f是示出根据本公开第四实施例的形成半导体结构的方 法的剖视图。除了在接合到管芯40a之前形成管芯堆叠结构之外,第四实 施例类似于前述实施例。

114.参照图2c及图11a,在一些实施例中,在临时载体tc上形成包括多 个管芯20a的晶片w1’之后,可例如以面对背配置将另一晶片w1(如图 2a所示)接合到晶片w1’。此后,可薄化另一晶片w1,以在临时载体tc 上方形成另一薄化的晶片w1’。

115.接合及薄化工艺可类似于上文所描述的工艺。应理解,可采用各种方 法来进行晶片与晶片的接合。举例来说,晶片与晶片的接合包括共晶接合、 熔融接合、直接金属接合、混合接合、其任意组合和/或类似接合工艺。在 发生共晶接合的一些实施例中,将两种共晶材料放置在一起,且然后施加 高压及高温使得共晶材料熔化,并且当熔化的共晶材料固化时,半导体晶 片接合在一起。在发生熔融接合的一些实施例中,另一晶片的氧化物表面 接合到晶片的氧化物表面或半导体表面(例如,硅表面)。在发生直接金属 对金属的接合的一些实施例中,两个接合导体在升高的温度下彼此压靠, 并且接合导体的相互扩散可导致接合导体的接合。在发生混合接合的一些 实施例中,两个半导体晶片的接合导体通过直接金属对金属的接合而接合 在一起,并且两个半导体晶片中的一者的氧化物表面接合到另一半导体晶 片的氧化物表面或硅表面。

116.在一些实施例中,将接合及薄化工艺重复几次,以形成具有多个层级 的晶片堆叠ws。应理解,晶片堆叠ws可包括任意数量的层级。根据产品 要求,晶片堆叠ws的最顶部层级处的晶片可被薄化以露出导通孔13或可 不被薄化。

117.参照图11a及图11b,可将晶片堆叠ws安装在胶带框架tp上,用于 执行单体化工艺。举例来说,将图11a中所示的结构翻转(例如,上下翻 转)并贴合到胶带框架tp。接下来,从晶片堆叠ws剥离临时载体tc。 在临时接合层tb设置在晶片堆叠ws与临时载体tc之间的一些实施例中, 可选择性地执行清洁工艺,以移除残留在薄化的晶片w1’的表面处的临时 接合层tb的不期望的残留物。随后,对晶片堆叠ws执行单体化工艺,以 形成多个管芯堆叠结构102a1。在一些实施例中,管芯堆叠结构102a1包括 管芯20a1到20a4。应注意,以上实例是出于说明目的而提供的,管芯堆叠 结构102a1的形成并不以此为限,且可以任何逻辑顺序来形成。在一些实施 例中,个别管芯堆叠结构102a1包括具有相同或相似功能并且彼此堆叠的几 个半导体管芯。在实施例中,管芯堆叠结构102a1是适用于快速数据访问应 用的存储器立方体(memory cube)。管芯堆叠结构102a1中所包括的管芯的 数量仅用于说明,并且本公开不限于此。

118.参照图3c、图11b及图11c,在一些实施例中,将包括管芯20a1到20a4的管芯堆叠结构102a1接合到载体100上方的管芯40a。此后,参照图11d, 将另一管芯堆叠结构102a2接合到管芯堆叠结构102a1,且管芯堆叠结构 102a2的结构及形成方法可类似于管芯堆叠结构102a1的结构及形成方法, 并且管芯堆叠结构102a2中所包括的管芯的数量可与管芯堆叠结构102a1中 所包括的管芯的数量相同或不同。在实施例中,管芯堆叠结构102a2包括管 芯20a5到20a8,并且管芯20a8的导通孔13可不被露出。因此,管芯堆叠结 构102a1与管芯堆叠结构102a2一起构成管芯堆叠结构102。在一些实施例 中,管芯堆叠结构102a1及102a2也可被称为子堆叠结构。应注意,图中所 示的管芯堆叠结构102中所包括的子堆叠结构的数量及每个子堆叠结构中 所包括的管芯的数量仅用于说明,并且本公开不限于此。在替代实施例中, 管芯堆叠结构102可包括在接合到管芯40a之前形成的单个管芯堆叠结构。

119.参照图11d,在形成管芯堆叠结构102之后,通过接合膜107将支撑 结构109接合到管芯堆叠结构102。

120.参照图11e及图11f,此后,执行类似于图4d及图4g中所述的工艺。 举例来说,将绝缘结构110形成为在侧向上包封管芯40a、管芯堆叠结构 102及支撑结构109。可将载体101贴合到支撑结构109及绝缘结构110。 然后将载体100从上覆结构脱离。之后,在管芯40a的

前侧上形成导电端 子150。然后释放载体101,并且可执行单体化工艺来单体化半导体结构s9。 半导体结构s9的结构类似于半导体结构s1。

121.在前述实施例中,通过混合接合工艺和/或熔融接合工艺接合管芯,但 本公开不限于此。举例来说,图13示出其中管芯通过连接件接合的半导体 结构s10。

122.参照图13,在一些实施例中,半导体结构s10包括管芯40a、管芯堆 叠结构102、支撑结构109、底部填充层61及绝缘结构is1。管芯40a及20a1到20a8通过连接件60彼此接合。连接件60可以是微凸块。在一些实施例 中,连接件60可包括焊料凸块、银凸块、铜凸块或任何其他合适的金属凸 块。举例来说,管芯20a1到20a8的互连结构12可包括多个导电接垫pa, 其可被钝化层(图中未示出)部分覆盖。管芯20a1的导电接垫pa可通过多 个连接件60电连接到管芯40a的导通孔33。管芯20a1到20a8中的一者的 导电接垫pa通过连接件60电连接到管芯20a1到20a8中的另一相应管芯的 导通孔13。连接件60位于管芯40a的导通孔33与管芯20a1的导电接垫pa 之间以及管芯堆叠结构102的相应管芯的导通孔13与导电接垫pa之间, 以提供电连接。

123.在一些实施例中,通过点胶工艺(dispensing process)形成底部填充层 61以填充相邻管芯之间的空间。举例来说,底部填充分配工艺可在每个管 芯接合工艺之后执行,并且被分配以填充处于较高水平高度处的两个管芯 之间的空间的底部填充材料可流动以覆盖处于较低水平高度处的管芯的侧 壁。覆盖不同管芯的侧壁的底部填充层61的厚度可能不均匀。通过熔融接 合工艺将支撑结构109接合到最顶部管芯。绝缘结构(例如,包括包封件110的绝缘结构is1)在侧向上包封底部填充层61、管芯20a8及支撑结构 109。在一些实施例中,也可将其他种类的绝缘结构(例如,包括上述介电 结构和/或包封件的绝缘结构)以及隔离层应用在本实施例中。

124.在一些实施例中,半导体结构s1到s10可经受进一步的封装工艺,并 且可进一步耦合到其他封装组件。举例来说,半导体结构s1到s10可进一 步集成在扇出封装结构、晶片上芯片(chip

‑

on

‑

wafer,cow)封装、衬底上 晶片上芯片(chip

‑

on

‑

wafer

‑

on

‑

substrate,cowos)封装或类似封装中。包 括半导体结构s1到s10的封装可以是用于例如计算机(例如,高性能计算 机)、结合人工智能系统使用的计算装置、无线通信装置、计算机相关外围 设备、娱乐装置等电子系统的一部分。包括本文中所论述的半导体结构的 封装可提供高带宽数据通信。应注意,其他电子应用也是可能的。

125.举例来说,参照图14,在一些实施例中,提供半导体结构s。半导体 结构s可以是上述半导体结构s1到s10中的一者。半导体结构s包括管芯 40a、管芯堆叠结构102、支撑结构109、以及至少包裹在管芯堆叠结构102 及支撑结构109周围的绝缘结构is。绝缘结构is可以是上述绝缘结构is1 到is4中的一者。应理解,为简洁起见,没有示出管芯堆叠结构102的具体 结构。

126.在一些实施例中,可通过导电端子150将半导体结构s电耦合到封装 组件pc。封装组件pc可以是或可包括中介物、封装衬底、印刷电路板 (printed circuit board,pcb)、印刷布线板和/或其他合适的封装组件。底部 填充层uf可填充半导体结构s与封装组件pc之间的空间。

127.在一些实施例中,盖301可设置在半导体结构s上,并且热界面材料 (thermal interface material,tim)300可设置在半导体结构s与盖301之 间。在一些实施例中,盖

301是具有高热导率的散热盖。因此,由半导体 结构s产生的热量可耗散到盖301,且然后耗散到外部环境。举例来说,盖 301可包含金属或金属合金,所述各金属选自由al、cu、ni、co、其类似 物或其组合组成的群组。盖301也可由选自包括碳化硅、氮化铝、石墨或 其组合物的群组中的复合材料形成。tim 300具有良好的热导率。在一些实 施例中,tim 300由硅酮制成,硅酮是包括硅、碳、氢、氧且有时包括其他 元素的聚合物。作为另外一种选择,tim 300也可由其他材料(例如,混合 有硅酮([r2sio]n)及其他可应用材料的铝氧化物(al2o3)或氧化锌(zno2)) 制成。

[0128]

在一些实施例中,可将tim 300分配到半导体结构s的支撑结构109 上。举例来说,支撑结构109的衬底108的顶表面可被tim 300覆盖(例 如,完全覆盖)。在将tim 300施加到半导体结构s上之后,将盖301安装 在半导体结构s上。在安装盖301期间,tim 300可被挤压并延伸以覆盖绝 缘结构is的顶表面的一部分。在一些实施例中,盖301也可着陆在封装组 件pc上。

[0129]

在一些实施例中,在将盖301安装在半导体结构s1上之后,可通过另 一tim将风扇或散热器(图中未示出)进一步安装在盖301上,以帮助耗 散由半导体结构s产生的热量。

[0130]

在本公开的实施例中,由于支撑结构109形成在管芯堆叠结构102上, 因此支撑结构109可用作盖301与管芯堆叠结构102之间的缓冲结构,以 避免来自盖301和/或散热器或风扇的机械应力直接施加在管芯堆叠结构 102上。因此,避免了可能由直接来自盖301的应力引起的管芯堆叠结构 102的损坏。另一方面,支撑结构109具有良好的热导率,并且还可用作散 热结构,以帮助将由管芯堆叠结构102及管芯40a产生的热量耗散到盖301。 换句话说,支撑结构的配置提高了半导体结构的机械性能及散热性能。

[0131]

根据本公开的一些实施例,一种封装结构包括第一管芯、管芯堆叠结 构、支撑结构以及绝缘结构。所述管芯堆叠结构接合到所述第一管芯。所 述支撑结构设置在所述管芯堆叠结构上。所述支撑结构的宽度大于所述管 芯堆叠结构的宽度并且小于所述第一管芯的宽度。所述绝缘结构至少在侧 向上包裹在所述管芯堆叠结构及所述支撑结构周围。

[0132]

在上述封装结构中,在所述支撑结构与所述管芯堆叠结构之间具有熔 融接合界面。

[0133]

在上述封装结构中,所述熔融接合界面还存在于所述支撑结构与所述 绝缘结构的介电层之间。

[0134]

在上述封装结构中,所述绝缘结构的顶表面与所述支撑结构的顶表面 共面。

[0135]

在上述封装结构中,所述绝缘结构包括第一绝缘结构及位于所述第一 绝缘结构上的第二绝缘结构,并且所述第一绝缘结构与所述第二绝缘结构 包含不同的材料。

[0136]

在上述封装结构中,所述第一绝缘结构的热膨胀系数比所述第二绝缘 结构的热膨胀系数更小,并且更接近所述管芯堆叠结构的衬底的热膨胀系 数。

[0137]

在上述封装结构中,还包括设置在所述管芯堆叠结构的两个相邻管芯 之间的隔离层,其中所述隔离层进一步延伸到所述绝缘结构下方或者延伸 到所述绝缘结构中。

[0138]

在上述封装结构中,还包括设置在所述管芯堆叠结构上方的盖,其中 所述支撑结构位于所述盖与所述管芯堆叠结构之间,并且被配置成缓冲应 力并散热。

[0139]

在上述封装结构中,所述管芯堆叠结构的最顶部管芯包括圆化拐角, 并且在垂直方向上在所述支撑结构的底表面与所述最顶部管芯的所述圆化 拐角之间存在间隙。

[0140]

根据本公开的替代实施例,一种封装结构包括第一管芯、至少一个第 二管芯以及虚设管芯结构。所述第一管芯在侧向上延伸超出所述至少一个 第二管芯的侧壁。所述虚设管芯结构接合到所述至少一个第二管芯。所述 第一管芯的侧壁、所述至少一个第二管芯的所述侧壁及所述虚设管芯结构 的侧壁在侧向上彼此偏移。

[0141]

在上述封装结构中,还包括至少在侧向上包封所述虚设管芯结构的包 封件。

[0142]

在上述封装结构中,还包括介电结构,所述介电结构位于所述包封件 与所述第一管芯之间并且在侧向上覆盖所述至少一个第二管芯。

[0143]

在上述封装结构中,还包括多个介电层,所述多个介电层在侧向上包 裹在所述至少一个第二管芯及所述虚设管芯结构周围。

[0144]

在上述封装结构中,所述虚设管芯结构的衬底的杨氏模量小于或等于 所述至少一个第二管芯的衬底的杨氏模量,并且所述虚设管芯结构的所述 衬底的热导率大于或等于所述至少一个第二管芯的所述衬底的热导率。

[0145]

在上述封装结构中,所述虚设管芯结构包括多个在侧向上彼此间隔开 的虚设管芯分区。

[0146]

根据本公开的一些实施例,一种形成封装结构的方法包括以下工艺。 提供第一管芯。将管芯堆叠结构接合到所述第一管芯。所述管芯堆叠结构 包括至少一个第二管芯。通过熔融接合工艺将支撑结构接合到所述管芯堆 叠结构。所述支撑结构的宽度大于所述管芯堆叠结构的宽度并且小于所述 第一管芯的宽度。形成绝缘结构以在侧向上包裹在所述支撑结构及所述管 芯堆叠结构周围。在将所述支撑结构接合到所述管芯堆叠结构之后形成所 述绝缘结构的至少一部分。

[0147]

在上述形成封装结构的方法中,所述绝缘结构包括包封件,并且形成 所述包封件包括:在将所述支撑结构接合到所述管芯堆叠结构之后,形成 包封件材料层以包封所述管芯堆叠结构的侧壁以及所述支撑结构的侧壁及 顶表面;以及对所述包封件材料层执行平坦化工艺,以形成在侧向上包封 所述管芯堆叠结构及所述支撑结构的包封件。

[0148]

在上述形成封装结构的方法中,所述绝缘结构还包括位于所述包封件 下方的介电层,其中在形成所述包封件材料层之前,形成在侧向上包裹在 所述管芯堆叠结构周围的所述介电层包括:将第二管芯接合到所述第一管 芯;在所述第一管芯上以及在所述第二管芯的侧边形成介电材料层;以及 对所述介电材料层执行平坦化工艺,以在侧向上在所述第二管芯侧边形成 介电层;以及将多个其他第二管芯接合到所述第二管芯上,所述第二管芯 及所述多个其他第二管芯构成所述管芯堆叠结构。

[0149]

在上述形成封装结构的方法中,所述绝缘结构包括多个介电层,并且 形成所述管芯堆叠结构、所述支撑结构及所述绝缘结构包括:将第二管芯 接合到所述第一管芯;在所述第一管芯上并在侧向上在所述第二管芯的侧 边形成第一介电层;将另一第二管芯接合到所述第二管芯;在所述第一介 电层上并在侧向上在所述另一第二管芯的侧边形成第二介电层;通过熔融 接合工艺将所述支撑结构接合到所述另一第二管芯及所述第二介电层;以 及在所述第二介电层上并在侧向上在所述支撑结构的侧边形成第三介电 层。

[0150]

在上述形成封装结构的方法中,所述至少一个第二管芯包括多个第二 管芯,所述第一管芯与所述多个第二管芯以面对背配置、面对面配置或背 对背配置彼此堆叠。

[0151]

以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地 理解本公

开的各个方面。所属领域中的技术人员应理解,其可容易地使用 本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实 施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域 中的技术人员还应认识到,这些等效构造并不背离本公开的精神及范围, 而且他们可在不背离本公开的精神及范围的条件下对其作出各种改变、代 替及变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。