1.本技术涉及半导体器件技术领域,特别是涉及一种显示面板。

背景技术:

2.随着显示技术的不断发展,用户对显示装置的要求越来越高,尤其近几年来高刷新涨势迅猛。目前技术而言,随着目前显示装置对高刷新频率的要求,充电时间越来越短,为保证初始化电源走线对电容及oled的有效初始化,对初始化电源走线的ir drop(压降)和rc loading(电阻电容负载)要求也越来越高。目前显示区的初始化电源走线在屏体中间和两侧的压降会有差异,高刷新频率下,会影响低亮度显示效果,引起色不均等不良。

技术实现要素:

3.有鉴于此,本技术主要解决的技术问题是提供一种显示面板,以改善显示不均的现象。

4.为解决上述技术问题,本技术采用的一个技术方案是:一种显示面板,具有显示区和位于显示区周围的非显示区,显示面板包括:初始化电源走线;初始化电源走线包括第一初始化电源走线、若干第二初始化电源走线和若干第三初始化电源走线,第一初始化电源走线环绕设置于显示区周围的非显示区;第二初始化电源走线设置于显示区,若干第二初始化电源走线分别沿第一方向延伸,若干第二初始化电源走线沿第二方向依次排布,若干第二初始化电源走线分别与第一初始化电源走线连接;第三初始化电源走线设置于显示区,若干第三初始化电源走线分别沿第二方向延伸,若干第三初始化电源走线沿第一方向依次排布,若干第三初始化电源走线分别与第一初始化电源走线连接。

5.其中,显示面板连接电路板以利用电路板而驱动显示面板;初始化电源走线还包括三条以上第四初始化电源走线,第四初始化电源走线连接于第一初始化电源走线与电路板之间。

6.其中,第一初始化电源走线包括沿第一方向延伸的第一子初始化电源走线和第二子初始化电源走线,沿第二方向延伸的第三子初始化电源走线和第四子初始化电源走线;第二子初始化电源走线设置于靠近电路板一侧,第一子初始化电源走线设置于远离电路板一侧,第一子初始化电源走线的一端与第三子初始化电源走线连接,另一端与第四子初始化电源走线连接。

7.其中一技术方案,第二子初始化电源走线包括若干沿第一方向间隔分布的子初始化电源走线段,子初始化电源走线段与一条第四初始化电源走线连接,子初始化电源走线段与第二初始化电源走线或第三初始化电源走线连接。

8.其中另一技术方案,第二子初始化电源走线为一体结构。

9.其中,第一子初始化电源走线为一体结构,或第一子初始化电源走线包括间隙,间隙设置于第一子初始化电源走线中间位置。

10.其中,显示面板还包括沿所述第一方向设置于所述显示区的扫描线,沿第二方向

设置于显示区的驱动电源线和数据线,以及若干像素单元;若干像素单元由扫描线和数据线交叉形成,且每列沿第二方向排列的像素单元分别对应连接一条驱动电源线和一条数据;沿第一方向的排列的相邻两个像素单元,其中一个像素单元对应第一驱动电源线和第一数据线;另一像素单元对应第二驱动电源线和第二数据线;第三初始化电源走线设置于靠近第一驱动电源线和第二数据线之间,或设置于第一数据线与第二驱动电源线之间。

11.其中,沿第一方向排列的相邻的像素单元为一组像素单元组,每两个相邻的像素单元组设置一条第三初始化电源走线。

12.其中,显示面板包括电容和晶体管,第二初始化电源走线与电容靠近显示面板出光面一侧的电极板同层设置;第三初始化电源走线与晶体管的源极走线或漏极走线同层设置。

13.其中,第二初始化电源走线与电容靠近显示面板出光面一侧的电极板的材质相同。

14.其中,第三初始化电源走线与晶体管的源极走线或漏极走线的材质相同。

15.其中,第二初始化电源走线和第三初始化电源走线之间设置绝缘层,第二初始化电源走线和第三初始化电源走线交叉位置处通过过孔连接。

16.其中,第三初始化电源走线在显示面板的深度方向上的投影设置于相邻两个像素单元之间,第三初始化电源走线的宽度为2

‑

3微米;第三初始化电源走线与对应同一像素单元的数据线或驱动电源线之间的距离为2.5微米

‑

4微米。

17.本技术的有益效果是:区别于现有技术本技术实施例的显示面板通过在显示面板设置沿第一方向延伸的第二初始化电源走线和沿第二方向延伸的第三初始化电源走线,使得位于显示面板显示区的初始化电源走线形成网状的初始化电源走线,使得显示区的第二初始化电源走线和第三初始化电源走线相对于第二初始化电源走线而言,电阻减小,可以减小显示区的初始化电源的走线的压降和电阻电容负载;本技术实施例通过将设置在非显示区的第一初始化电源走线设置在显示区的外周,使得第一初始化电源走线可以从四周向显示区网状的初始化电源走线提供参考电压信号,即可以为第二初始化电源走线和第三初始化电源走线提供参考电压信号,减少显示区的初始化电源走线在屏体中间和两侧的ir drop(压降)的差异,使得显示面板在高刷新频率下,低亮度的显示效果均匀,使得显示面板显示均匀。

附图说明

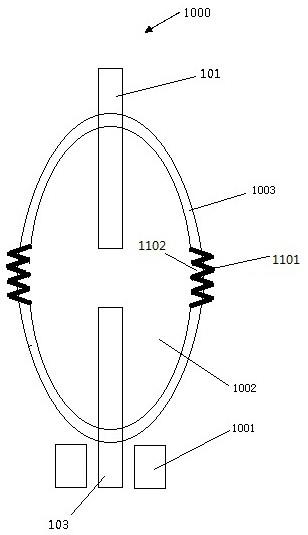

18.图1是本技术显示面板第一实施例的平面结构示意图;

19.图2是本技术显示面板第二实施例的平面结构示意图;

20.图3是本技术显示面板第三实施例的平面结构示意图;

21.图4是本技术显示面板局部区域电路走线结构示意图;

22.图5是本技术像素单元一实施例的电路图;

23.图6是的图4的局部剖面结构示意图;

24.图7是本技术显示面板第四实施例的平面结构示意图。

具体实施方式

25.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。

26.本技术实施例提供一种显示面板,如图1所示,显示面板具有显示区1和位于显示区1周围的非显示区2,显示面板包括:初始化电源走线100(vref);初始化电源走线100包括第一初始化电源走线110、若干第二初始化电源走线120和若干第三初始化电源走线130,第一初始化电源走线110环绕设置于显示区1周围的非显示区2;第二初始化电源走线120设置于显示区1,每条第二初始化电源走线120分别沿第一方向d1延伸,若干第二初始化电源走线120沿第二方向d2依次排布,每条第二初始化电源走线120分别与第一初始化电源走线110连接;第三初始化电源走线130设置于显示区1,每条第三初始化电源走线130分别沿第二方向d2延伸,若干第三初始化电源走线130沿第一方向d1依次排布,每条第三初始化电源走线130分别与第一初始化电源走线110连接。

27.本技术实施例中,通过在显示面板设置沿第一方向d1延伸的第二初始化电源走线120和沿第二方向d2延伸的第三初始化电源走线130,使得位于显示面板显示区1的初始化电源走线100形成网状的初始化电源走线100,使得显示区1的第二初始化电源走线120和第三初始化电源走线130相对于第二初始化电源走线120而言,电阻减小,可以减小显示区1的初始化电源的走线的压降和电阻电容负载;本技术实施例通过将设置在非显示区2的第一初始化电源走线110,且第一初始化电源走线110环绕设置在显示区1的外周,使得第一初始化电源走线110可以从四周向显示区1网状的初始化电源走线100提供参考电压信号,即可以为第二初始化电源走线120和第三初始化电源走线130提供参考电压信号,减少显示区1的初始化电源走线100在屏体中间和两侧的ir drop压降的差异,使得显示面板在高刷新频率下,低亮度的显示效果均匀,使得显示面板显示均匀。

28.本技术实施例中,第一方向d1为如图1所示的水平方向,第二方向d2为如图1所示的竖直方向。

29.本技术实施例中,第一初始化电源走线110的宽度为15微米,在其他实施例中,第一初始化电源走线110的宽度也可以为10

‑

30微米之间,例如可以是20微米等。

30.本技术实施例中,继续如图1所示,显示面板连接电路板300以利用电路板300而驱动显示面板;初始化电源走线100还包括三条以上第四初始化电源走线140,第四初始化电源走线140连接于第一初始化电源走线110与电路板300之间。本技术实施例中,电路板300与驱动芯片400连接,驱动芯片400输出驱动信号电路板300,并通过300传输;本技术实施例,电路板300可以是柔性电路板300,在其他实施例中,电路板300也可以是硬质电路板300。本技术实施例中,通过三条以上的第四初始化电源走线140向第一初始化电源走线110输入驱动信号。本技术实施例,通过设置三条以上的第四初始化电源走线140可以减少驱动信号在第一初始化电源走线110上的衰减,提高第一初始化电源走线110获得驱动信号的电压幅值的均一性。具体地,本技术实施例中,第四初始化电源走线140为六条,在其它实施例中,第四初始化电源走线140也可以为三条、四条、五条、七条、八条或九条,只要保证足够的布线空间,及能够使得本技术实施中第四初始化电源走线140不与其他金属走线发生短路风险,或第四初始化电源走线140之间互相不交叠、互不影响即可。

31.本技术实施例中,继续如图1所示,第一初始化电源走线110包括沿第一方向d1延

伸的第一子初始化电源走线111和第二子初始化电源走线112,沿第二方向d2延伸的第三子初始化电源走线113和第四子初始化电源走线114;第二子初始化电源走线112设置于靠近电路板300一侧,第一子初始化电源走线111设置于远离电路板300一侧,第一子初始化电源走线111的一端与第三子初始化电源走线113连接,第一子初始化电源走线111的另一端与第四子初始化电源走线114连接。本技术实施例中,第一子初始化电源走线111位于显示面板的上端、第二子初始化电源走线112位于显示面板的下端,第三子初始化电源走线113为显示面板的左侧、第四子初始化电源走线114为显示面板的右侧,本技术实施例中,第一初始化电源走线110包括四条子初始化电源走线,可以使得第一子初始化电源走线111可以从四个方向往显示区1的第二初始化电源走线120和第三初始化电源走线130输送参考电压信号。

32.其中一实施例中,第二子初始化电源走线112为一体结构,第二子初始化电源走线112与第三子初始化电源走线113、第四子初始化电源走线114以及第一子初始化电源走线111形成一封闭环状走线,通过第四初始化电源走线140可以将驱动信号传输至第二子初始化电源走线112,第二子初始化电源走线112输送参考电压信号至第三子初始化电源走线113、第四子初始化电源走线114以及第一子初始化电源走线111。

33.在本技术另一实施例中,如图2所示,第二子初始化电源走线112包括若干沿第一方向d1间隔分布的子初始化电源走线段1121,每个子初始化电源走线段1121与一条第四初始化电源走线140连接,每个子初始化电源走线段1121与第二初始化电源走线120。在其他实施例中,也可以是每个子初始化电源走线段1121与一条第四初始化电源走线140连接,每个子初始化电源走线段1121与第三初始化电源走线130连接。本技术实施例中,第二子初始化电源走线112设置成若干子初始化电源走线段1121,其中,靠近子初始化电源走线段1121之间设置间隔,使得子初始化电源走线段1121之间沿第一方向d1呈离散分布,本技术实施例中,靠近第三子初始化电源走线113的子初始化电源走线段1121与第三子初始化电源走线113连接,靠近第四子初始化电源走线114的子初始化电源走线段1121与第四子初始化电源走线114连接,通过若干第四初始化电源走线140分别与子初始化电源走线段1121连接,可以使得电路板300通过第四初始化电源走线140将驱动信号传输至子初始化电源走线段1121、并传输至第三子初始化电源走线113和第四子初始化电源走线114,以及传输至第一子初始化电源走线111;从而可以使得位于底端的子初始化电源走线100、位于两侧的第三子初始化电源走线113和第四子初始化电源走线114以及第一子初始化电源走线111向显示区1的网状初始化电源走提供参考电压信号。在其他实施例中,也可以是部分第四子初始化电源走线114分别与第三子初始化电源走线113、第四子初始化电源走线114连接,另一部分第四子初始化电源走线114分别与初始化电源走线段1121连接,此时子初始化电源走线可以与第三子初始化电源走线113、第四子初始化电源走线114不连接。

34.本技术实施例中,第一子初始化电源走线111为一体结构,便于第三子初始化电源走线113、第四子初始化电源走线114从两侧向第一子初始化电源走线111输送参考电压信号,以便于第一子初始化电源走线111向第二初始化电源走线120和第三初始化电源走线130输送参考电压信号。

35.本另一实施例中,如图3所示,第一子初始化电源走线111包括间隙1111,间隙1111设置于第一子初始化电源走线111中间位置。本技术实施例中,第一子初始化电源走线111

的中间位置形成间隙1111,可以确保第三子初始化电源走线113和第四子初始化电源走线114分别向与之相连接的第一子初始化电源走线111输送参考电压信号,且在中间位置设置间隙1111,可以使得第二子初始化电源走线112上形成的压降和电阻电容负载对称,从而确保第二子初始化电源走线112向第二初始化电源走线120和第三初始化电源走线130输送的参考电压信号均匀,使得显示区1的第二初始化电源走线120和第三初始化电源走线130的压降和电阻电容负载均匀。

36.本技术实施例中,如图1和图4所示,显示面板还包括沿第一方向d1设置于显示区1的扫描线230,沿第二方向d2设置于显示区1的驱动电源线210和数据线220,以及若干像素单元500;若干像素单元500由扫描线230和数据线220交叉形成,且每列沿第二方向d2排列的像素单元500分别对应连接一条驱动电源线210和一条数据线220;沿第一方向d1排列的相邻两个像素单元500,其中一个像素单元500对应第一驱动电源线211和第一数据线221;另一像素单元500对应第二驱动电源线212和第二数据线222;每个像素单元500对应一条第三初始化电源走线130,第三初始化电源走线130设置于靠近第一驱动电源线211和第二数据线222之间,或设置于第一数据线221与第二驱动电源线212之间。本技术实施例中,驱动电源线210(elvdd)可以向显示区1的输送电源信号,数据线220(v

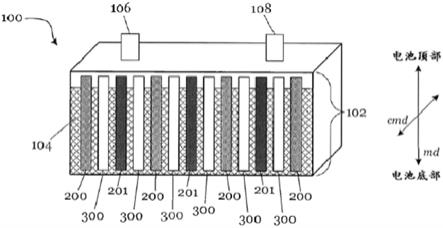

data

)可以输送数据信号,本技术实施例中数据线220(v

data

)均为沿第二方向d2设置,驱动电源线210(v

data

)包括沿第一方向d1和沿第二方向d2设置的驱动电源线210,其中沿第二方向d2设置的驱动电源线210与相邻像素单元500所对应的数据线220之间设置第三初始化电源走线130。本技术实施例中,第三初始化电源走线130与沿第二方向d2设置的驱动电源线210、数据线220同层设置,通过将第三初始化电源走线130设置于相邻像素单元500所对应的驱动电源线210、数据线220之间,可以使得三者互不影响,且每两个像素单元500均对应连接有第三初始化电源走线130,使得第三初始化电源走线130能够向像素单元500输送参考电压信号,从而使得显示面板的每个像素单元500的显示均匀性得到提高。

37.本技术实施例中,继续如图1和图4所示,显示面板还包括沿第二方向d2设置的竖向扫描线231和控制信号线240,竖向扫描线231用于输送扫描信号,控制信号线240用于输入控制信号。

38.本技术实施例中的像素单元是7t1c电路,在其他实施例中,也可以是2t1c、6t1c等电路。本技术实施例中,显示面板包括电容700和晶体管600。

39.图5是根据图1所示实施例的oled显示器的一个像素单元500(见图4)的电路图,具体为7t1c电路,包括一个电容700(cst)和七个晶体管600,晶体管600包括:第一晶体管m1、第二晶体管m2、第三晶体管m3、第四晶体管m4、第五晶体管m5、第六晶体管m6和第七晶体管m7。

40.其中,第二晶体管m2的第一端和数据信号端v

data

连接,第二晶体管m2的第二端和第二扫描线scan2连接,第二晶体管m2的第三端和第五晶体管m5的第三端连接。

41.第五晶体管m5的第一端和电压信号端v

dd

连接,第五晶体管m5的第二端和控制信号端em连接,第五晶体管m5的第三端和第二晶体管m2的第三端连接。

42.第一晶体管m1的第一端与第五晶体管m5的第三端连接,第一晶体管m1的第二端与电容cst的第二端连接,第一晶体管m1的第三端与第六晶体管m6的第一端连接。

43.第六晶体管m6的第二端与控制信号端em连接,第六晶体管m6的第三端与发光单元

940连接。

44.第三晶体管m3的第一端与电容cst的第二端连接,第三晶体管m3的第二端与第二扫描线scan2连接,第三晶体管m3的第三端与m1的第三端连接。

45.电容cst的第一端与电压信号端v

dd

连接,电容cst的第二端与第四晶体管的第一端连接。

46.第四晶体管m4的第二端与第一扫描线scan1连接,第四晶体管m4的第三端与初始化电源走线100(vref)连接。

47.第七晶体管m7的第一端与始化电源走线100(vref)连接,第七晶体管m7的第二端与第三扫描线scan3连接,第七晶体管m7的第三端与发光单元940连接。

48.本技术实施例中,晶体管600的第一端为漏极,第二端为栅极,第三端为源极。

49.本技术实施例中,如图4和图6所示,第二初始化电源走线120与电容700靠近显示面板出光面一侧的电极板710同层设置;第三初始化电源走线130与晶体管600的源极走线611或漏极走线621同层设置。显示面板的阵列基板中通过设置电容700和晶体管600,用于提供电容700以及控制像素单元500驱动发光单元940(见图5)发光。本技术实施例中,通过将第二初始化电源走线120与电容700靠近显示面板出光一侧电极板710(上极板)同层设置,使得第二初始化电源走线120在制作过程中可以节省制作步骤,同时,可以降低显示面板的厚度,实现显示面板的薄化。本技术实施例的第三初始化电源走线130与晶体管600的源极走线611或漏极走线621同层设置,同样可以使得第三初始化电源走线130在制作过程中可以节省制作步骤,同时,可以降低显示面板的厚度,实现显示面板的薄化。本技术实施例中,第三初始化电源走线130与晶体管600的源极走线611、漏极走线621、以及驱动电源线210、数据线220在同一层,使得显示面板的集成度化高,减少制作步骤,节约制作时间和制作成本,降低生产成本,且可以达到各层互不影响的效果。本技术实施例中,晶体管600的源极走线611为将晶体管600的源极610引出的走线,漏极走线621为将晶体管600的漏极620引出的走线。

50.在其他实施例中,也可以是仅第三初始化电源走线130与晶体管600的源极走线611或漏极走线621同层设置,也可以减少制作步骤,提高显示面板的集成度化强度,节约制作时间和制作成本,降低产品成本。

51.本技术实施例中,第二初始化电源走线120与电容700靠近显示面板出光面一侧的电极板710的材质相同。可以采用同一制作步骤完成,降低显示面板的厚度,例如,本技术实施例中第二初始化电源走线120与电容700靠近显示面板出光面一侧的电极板710的材质均为钼。在其他实施例中,也可以是第二初始化电源走线120与电容700靠近显示面板出光面一侧的电极板710的材质不同,可以降低显示面板的厚度。

52.本技术实施例中,第三初始化电源走线130与晶体管600的源极610或漏极620的材质相同。可以采用同一制作步骤完成,降低显示面板的厚度。例如本技术实施例中,第三初始化电源走线130、晶体管600的源极610、漏极620的材质均为tialti复合层,在其他实施例中,也可以为其他材质。

53.本技术实施例中,第三初始化电源走线130的电阻率小于第二初始化电源走线120的电阻率,可以减少电阻负载,减少压降。

54.本技术实施例中,如图4和图6所示,第二初始化电源走线120和第三初始化电源走

线130之间设置绝缘层800,第二初始化电源走线120和第三初始化电源走线130交叉位置处通过过孔910连接。本技术实施例中,第二初始化电源走线120所在层位于第三初始化电源走线130所在层的下方,即第二初始化电源走线120设置在远离显示面板出光面一侧,第三初始化电源走线130设置在朝向显示面板出光面一侧,第二初始化电源走线120与第三初始化电源走线130之间设置绝缘层800,可以防止第二初始化电源走线120与驱动电源线210、数据线220等出现短路的情况,本技术实施例中,通过在第二初始化电源走线120和第三初始化电源走线130交叉位置处的绝缘层800设置过孔910,通过过孔910连接第二初始化电源走线120和第三初始化电源走线130,以使得第三初始化电源走线130可以改善第二初始化电源走线120的压降和电阻电容负载。

55.本技术实施例中,沿第一方向d1排列的相邻的两个像素单元500为一组像素单元组,每两个相邻的像素单元组设置一条第三初始化电源走线130。

56.具体地,本技术实施例中,第三初始化电源走线130沿第一方向d1间隔设置于相邻的两个像素单元500之间,使得沿第一方向d1上,相邻两个第三初始化电源走线130之间有两个像素单元500。每条第二初始化电源走线120对应一排的像素单元500,每条第三初始化电源走线130对应两列像素单元500,使得第二初始化电源走线120和第三初始化电源走线130向每个像素单元500输送参考电压信号。

57.本技术实施例的显示面板,初始化电源走线100的设置可以实现显示面板的沿第一方向d1的中间位置和两侧位置的参考电压信号近似或相同,以使得显示面板在高刷新频率下,例如在90hz以上的刷新频率下,不会影响低亮度的显示效果。如图7所示,对于显示面板设置开孔920,乃至开孔920并非设置于显示面板中间位置的侧向偏孔,由于显示面板可以通过第三初始化电源走线130向侧向偏孔的周围的像素单元500输送参考电压信号,使得侧向偏孔周围的像素单元500、以及显示面板其他区域的像素单元500的参考电压相同或相近,使得显示面板发光显示均匀,改善显示面板上设置侧向偏孔所造成的其周围的像素单元500获得的参考电压受压降和电阻电容负载影响所造成的不同,改善显示面板侧向偏孔所造成的其周围的像素单元500在高刷新频率下低亮度显示不均的情况。

58.本技术实施例中,其中,如图1和图4所示,所述第三初始化电源走线130在显示面板深度方向上的投影设置于相邻每两个像素单元组之间,所述第三初始化电源走线130的宽度为2

‑

3微米;第三初始化电源走线130与对应同一像素单元500的数据线220或驱动电源线210之间的距离为2.5微米

‑

4微米。

59.本技术实施例中,第三初始化电源走线130在显示面板深度方向上的投影设置于同行的相邻每两个像素单元组之间。本技术实施例中仅为举例,在其他实施例中,像素单元500也可以采用其他的阵列设置方式,第三初始化电源走线130也可以设置成其他方式。

60.本技术实施例中,如图4所示,第三初始化电源走线130的宽度设置为2.5微米,在其他实施例中,第三初始化电源走线130的宽度也可以为2微米、2.8微米或3微米等,使得本技术实施例的第三初始化电源走线130在制作过程中易于制作出,且使得第三初始化电源走线130不会占据过多的面积。本技术实施例中,像素单元500在第三初始化电源走线130所在层设置对应的换线孔930,换线孔930用于将像素电路与像素单元500连通,本技术实施例中,同一个像素单元500所对应的数据线220与换线孔930之间的距离d为7

‑

10微米,本技术实施例中,第三初始化电源走线130与对应同一像素单元500的数据线220之间的距离为2.5

微米

‑

4微米,使得第三初始化电源走线130与数据线220之间的距离可以符合工艺制作的条件,使得第三初始化电源走线130与数据线220之间不会出现短路的情况。同时,本技术实施例中,第三初始化电源走线130与换线孔930之间的距离也为2.5微米

‑

4微米,第三初始化电源走线130与换线孔930不会出现短路的情况。本技术实施例中,第三初始化电源走线130与对应同一像素单元500的数据线220之间的距离为第三初始化电源走线130与对应同一发像素单元500之间的间隔的距离。本技术实施例中,同一像素单元500对应的数据线220靠近于第三初始化电源走线130,在其他实施例中,当同一像素单元500对应的驱动电源线210靠近第三初始化电源走线130时,第三初始化电源走线130与对应同一像素单元500的驱动电源线210之间的距离为2.5微米

‑

4微米,即第三初始化电源走线130与对应同一像素单元500之间的间隔的距离,本技术实施例中,第三初始化电源走线130与对应同一像素单元500的驱动电源线210之间的距离为2.5微米,在其他实施例中,也可以为3微米或4微米等。

61.以上仅为本技术的实施方式,并非因此限制本技术的专利范围,凡是利用本技术说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。