技术特征:

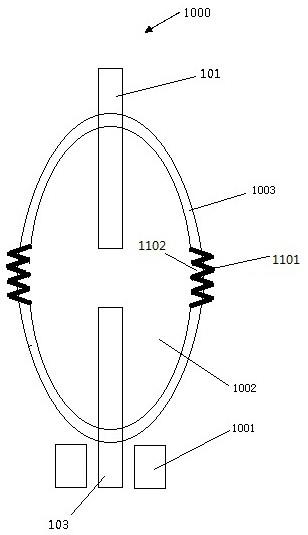

1.一种低表面漏电流的探测器,包括inp衬底,在inp衬底上依次生长有通过蚀刻形成的隔离台与p台,其特征在于:衬底、隔离台与p台的上表面以及隔离台、p台的侧面依次生长有第一钝化层与第二钝化层,隔离台的上表面设有穿过所述第一钝化层与第二钝化层的n型接触金属环,在p台上表面设有穿过所述第一钝化层与第二钝化层的p型接触金属环,所述第一钝化层为半绝缘inp或inalas,厚度为20

‑

100nm,掺杂原子为fe、ti、v、cr、mn、co、ni、au、rh、hf、zr、ru、cu或os,且掺杂浓度范围为0.5

‑

1.5e17cm

‑3,所述第二钝化层为氮化硅或氧化硅,厚度为200

‑

500nm。2.如权利要求1所述的一种低表面漏电流的探测器,其特征在于:所述隔离台的直径比所述p台的直径大10

‑

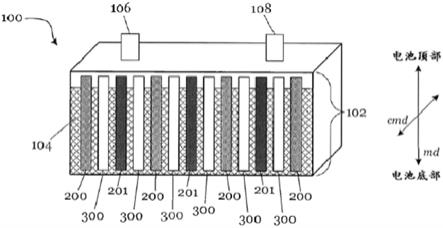

50um。3.如权利要求1所述的一种低表面漏电流的探测器,其特征在于:所述隔离台由下至上依次为inp缓冲层、n型掺杂inp层、n型掺杂接触层;所述p台由下至上依次为腐蚀截止层、光吸收层、过渡层、p型帽层、p型掺杂接触层。4.如权利要求3所述的一种低表面漏电流的探测器,其特征在于:所述inp缓冲层为n型掺杂,掺杂原子为si,且掺杂浓度大于1e18cm

‑3,厚度在200

‑

500nm;所述n型掺杂inp层掺杂原子为si,且掺杂浓度大于1e18cm

‑3,厚度大于1.5um;所述n型掺杂接触层为ingaas材料,厚度为20

‑

50nm,掺杂原子为si,且掺杂浓度大于1e19cm

‑3。5.如权利要求3所述的一种低表面漏电流的探测器,其特征在于:所述腐蚀截止层为n型掺杂inp材料,厚度为20

‑

50nm,掺杂原子为si,且掺杂浓度大于1e18cm

‑3;所述光吸收层为本征ingaas材料,厚度为500

‑

2000nm;所述过渡层为p型掺杂ingaasp材料,厚度为20

‑

50nm,掺杂原子为zn且掺杂浓度大于1e18cm

‑3;所述p型帽层为p型掺杂inp材料,厚度为300

‑

400nm,掺杂原子为zn,且掺杂浓度大于1e18cm

‑3;所述p型掺杂接触层为p型掺杂ingaas材料,厚度为20

‑

100nm,掺杂原子为zn,且掺杂浓度大于1e18cm

‑3。6.一种低表面漏电流的探测器的制作方法,包括如下步骤:步骤s401、在inp衬底上使用金属有机化学气相沉积法依次生长出inp缓冲层、n型掺杂inp层、n型掺杂接触层、腐蚀截止层、光吸收层、过渡层、p型帽层、p型掺杂接触层;步骤s402、通过增强等离子化学气相沉积方法、光刻与反应离子刻蚀工艺形成p台蚀刻掩膜sinx;步骤s403、通过电感耦合等离子体刻蚀与湿法蚀刻工艺形成p台;步骤s404、通过光刻与化学腐蚀工艺形成隔离台,腐蚀深度大于1.5um;步骤s405、通过金属有机化学气相沉积法,在inp衬底、隔离台、p台的上表面以及隔离台、p台的侧面沉积厚度为50nm的第一钝化层,第一钝化层掺杂原子为fe,掺杂浓度为1e17cm

‑3;步骤s406、通过增强等离子化学气相沉积方法,在第一钝化层上沉积第二钝化层。步骤s407、通过光刻工艺、反应离子刻蚀工艺对p台、隔离台上表面的第二钝化层进行刻蚀,通过化学腐蚀对p台、隔离台上表面的第一钝化层进行刻蚀,刻蚀出p型接触区与n型接触区;步骤s408、通过光刻工艺、电子束蒸发ti、pt、au金属层工艺和剥离工艺,在p型接触区形成p型接触金属环,n型接触区形成n型接触金属环。7.一种低表面漏电流的探测器的制作方法,包括如下步骤:

步骤s501、在inp衬底上使用金属有机化学气相沉积法依次生长出inp缓冲层、n型掺杂inp层、n型掺杂接触层、腐蚀截止层、光吸收层、过渡层、p型帽层、p型掺杂接触层;步骤s502、通过增强等离子化学气相沉积方法、光刻与反应离子刻蚀工艺形成p台蚀刻掩膜sinx;步骤s503、通过电感耦合等离子体刻蚀与湿法蚀刻工艺形成p台;步骤s504、通过光刻与化学腐蚀工艺形成隔离台,腐蚀深度大于1.5um;步骤s505、通过增强等离子化学气相沉积方法,在inp衬底、隔离台、p台的上表面以及隔离台、p台的侧面沉积n型接触区氮化硅绝缘介质膜和p型接触区氮化硅绝缘介质膜,通过光刻工艺、反应离子刻蚀工艺对氮化硅绝缘介质膜进行刻蚀,在p型接触区、n型接触区保留氮化硅绝缘介质膜;步骤s506、通过金属有机化学气相沉积法,在inp衬底、隔离台、p台的上表面以及隔离台、p台的侧面沉积第一钝化层,第一钝化层掺杂原子为fe,掺杂浓度为1e17cm

‑3,保留有氮化硅绝缘介质膜处不生长出外延层;步骤s507、通过增强等离子化学气相沉积方法,在第一钝化层、p型接触区氮化硅绝缘介质膜、n型接触区氮化硅绝缘介质膜表面沉积第二钝化层;步骤s508、通过光刻工艺、反应离子刻蚀工艺对p台、隔离台上表面第一钝化层、第二钝化层处p型接触区、n型接触区进行刻蚀,露出探测器p型掺杂接触层和n型掺杂接触层;步骤s509、通过光刻工艺、电子束蒸发ti、pt、au金属层工艺和剥离工艺,在所述p型接触区形成p型接触金属环,n型接触区形成n型接触金属环。8.一种低表面漏电流的探测器的制作方法,包括如下步骤:步骤s601、在inp衬底上使用金属有机化学气相沉积法依次生长出inp缓冲层、n型掺杂inp层、n型掺杂接触层、腐蚀截止层、光吸收层、过渡层、p型帽层、p型掺杂接触层;步骤s602、通过增强等离子化学气相沉积方法、光刻与反应离子刻蚀工艺形成p台蚀刻掩膜sinx;步骤s603、通过电感耦合等离子体刻蚀与湿法蚀刻工艺形成p台;步骤s604、通过光刻与化学腐蚀工艺形成隔离台,腐蚀深度大于1.5um;步骤s605、通过光刻工艺、电子束蒸发ti、pt、au金属层工艺和剥离工艺,在p型接触区形成p型接触金属环,n型接触区形成n型接触金属环;步骤s606、通过增强等离子化学气相沉积方法,在inp衬底、隔离台、p台、p型接触金属环、n型接触金属环的上表面以及隔离台、p台的侧面沉积氮化硅介质膜;通过光刻工艺、rie等离子刻蚀工艺对氮化硅介质膜进行刻蚀,在已蒸镀电极的p型接触区、n型接触区位置保留氮化硅介质膜;步骤s607、通过金属有机化学气相沉积法,在inp衬底、隔离台、p台的上表面以及隔离台、p台的侧面沉积第一钝化层,第一钝化层掺杂原子为fe,掺杂浓度为1e17cm

‑3;步骤s608、通过增强等离子化学气相沉积方法,在第一钝化层表面沉积第二钝化层;步骤s609、通过光刻工艺、反应离子刻蚀工艺对n型接触金属环氮化硅绝缘介质膜和p型接触金属环氮化硅绝缘介质膜进行刻蚀,露出p型接触金属环、n型接触金属环。

技术总结

本发明提供一种低表面漏电流的探测器,包括InP衬底,在InP衬底上依次生长有通过蚀刻形成的隔离台与P台。所述衬底、隔离台与P台的上表面以及隔离台、P台的侧面依次生长有第一钝化层与第二钝化层。所述隔离台的上表面设有穿过所述第一钝化层与第二钝化层的n型接触金属环,在所述P台上表面设有穿过所述第一钝化层与第二钝化层的p型接触金属环。本发明用复合钝化层(复合钝化层由下至上为半绝缘InP或InAlAs与介质膜钝化层)代替传统介质膜钝化层对探测器进行钝化,减少了钝化层与半导体界面之间的缺陷与界面态,有利于减小器件的漏电流。流。流。

技术研发人员:杨奕 缪笛 鄢静舟 薛婷

受保护的技术使用者:福建慧芯激光科技有限公司

技术研发日:2021.09.16

技术公布日:2021/10/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。