1.本发明属于芯片制造技术领域,尤其涉及一种低表面漏电流的探测器及其制作方法。

背景技术:

2.现有的台面型pd(光电二极管探测器)、台面型apd(雪崩光电二极管探测器)在台面刻蚀工艺完成后,其台面及侧面存在着大量的悬挂键及表面缺陷,这些悬挂键及缺陷会增大器件的表面漏电流。漏电流是表征探测器性能的最重要参数之一,它的大小直接影响了器件的性能。台面钝化工艺可起到降低表面漏电流的作用。

3.常规的台面钝化主要通过在台面沉积介质膜(sio2或sinx)来实现。以在inp基衬底探测器台面沉积介质膜钝化层为例,传统介质膜钝化层为sio2或sin

x

材料,其晶格常数与inp存在着巨大差异。虽然仍可起到钝化作用,但sio2或sin

x

介质膜与pd台面侧壁间还是会存在大量的悬挂键。另外,通过等离子增强化学气相沉积(pecvd)在台面侧壁沉积介质膜的过程也会对台面及其侧壁造成损伤。

4.因此,常规钝化方式制作出来的探测器仍然面临着表面缺陷及悬挂键的问题,表面特性需要进一步改善。

技术实现要素:

5.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种低表面漏电流的探测器。

6.为实现上述目的及其他相关目的,本发明提供一种低表面漏电流的探测器,包括inp衬底,在inp衬底上依次生长有通过蚀刻形成的隔离台与p台。所述衬底、隔离台与p台的上表面以及隔离台、p台的侧面依次生长有第一钝化层与第二钝化层。所述隔离台的上表面设有穿过所述第一钝化层与第二钝化层的n型接触金属环,在所述p台上表面设有穿过所述第一钝化层与第二钝化层的p型接触金属环。

7.进一步,所述隔离台的直径比p台的直径大10

‑

50um;更进一步,所述隔离台由下至上依次为inp缓冲层、n型掺杂inp层、n型掺杂接触层;所述p台由下至上依次为腐蚀截止层、光吸收层、过渡层、p型帽层、p型掺杂接触层。

8.再进一步,所述inp缓冲层为n型掺杂,掺杂原子为si,且掺杂浓度大于1e18cm

‑3,厚度在200

‑

500nm;所述n型掺杂inp层掺杂原子为si,且掺杂浓度大于1e18cm

‑3,厚度大于1.5um;所述n型掺杂接触层为ingaas材料,厚度为20

‑

50nm,掺杂原子为si,且掺杂浓度大于1e19cm

‑3;再进一步,所述腐蚀截止层为n型掺杂inp材料,厚度为20

‑

50nm,掺杂原子为si,且掺杂浓度大于1e18cm

‑3;所述光吸收层为本征ingaas材料,厚度为500

‑

2000nm;所述过渡层为p型掺杂ingaasp材料,厚度为20

‑

50nm,掺杂原子为zn且掺杂浓度大于1e18cm

‑3;所述p型帽层为p型掺杂inp材料,厚度为300

‑

400nm,掺杂原子为zn,且掺杂浓度大于1e18cm

‑3;所述p

型掺杂接触层为p型掺杂ingaas材料,厚度为20

‑

100nm,掺杂原子为zn,且掺杂浓度大于1e18cm

‑3;进一步,所述第一钝化层为半绝缘inp或inalas,厚度为20

‑

100nm,掺杂原子可以为但不限于fe、ti、ti zn(即掺杂原子为ti和zn,下文中掺杂浓度是两种原子总浓度)、ti cd(即掺杂原子为ti和cd,下文中掺杂浓度是两种原子总浓度)、ti hg(即掺杂原子为ti 和hg,下文中掺杂浓度是两种原子总浓度)、v、cr、mn、co、ni、au、rh、hf、zr、ru、cu或os,且掺杂浓度范围为0.5

‑

1.5e17cm

‑3;进一步,所述第二钝化层可以为氮化硅或氧化硅,厚度为200

‑

500nm;本发明还公开一种用于上述低表面漏电流的探测器的制作方法,包括如下步骤:1)在inp衬底上使用金属有机化学气相沉积法依次生长出inp缓冲层、n型掺杂inp层、n型掺杂接触层、腐蚀截止层、光吸收层、过渡层、p型帽层、p型掺杂接触层;2)通过增强等离子化学气相沉积方法(pecvd)、光刻与反应离子刻蚀(rie)工艺形成p台蚀刻掩膜sinx;3)通过电感耦合等离子体(icp)蚀刻与湿法蚀刻工艺形成p台。icp工艺所用气体为cl2,蚀刻至所述光吸收层中间位置(腐蚀截止层上方200

‑

300nm处)。随后用配比为1:1:25的h2so4/h2o2/h2o腐蚀液对剩余的光吸收层进行刻蚀至腐蚀截止层上界面,再用配比为4:1的h3po4/hcl腐蚀液对腐蚀截止层进行刻蚀。腐蚀截止层腐蚀完成后,用boe去除p台蚀刻掩膜sinx。

9.4)通过光刻与化学腐蚀工艺形成隔离台,所用化学腐蚀溶液为配比为6:150:700的br2/hbr/h2o腐蚀液,腐蚀深度大于1.5um。

10.5)通过金属有机化学气相沉积法,在inp衬底、隔离台、p台的上表面以及隔离台、p台的侧面沉积厚度为20

‑

100nm的第一钝化层。

11.6)通过pecvd,在第一钝化层表面沉积厚度为200

‑

500nm第二钝化层。

12.7)通过光刻工艺、rie刻蚀对第二钝化层进行刻蚀,通过icp蚀刻或化学腐蚀对第一钝化层进行刻蚀,最终刻蚀出p型接触区与n型接触区;8)通过光刻工艺、电子束蒸发金属层工艺和剥离工艺,在所述p型接触区形成p型接触金属环,n型接触区形成n区接触金属环。

13.本发明具有以下有益效果:以介质膜钝化层为例,传统介质膜钝化层为sio2或sin

x

,其晶格常数与inp存在着巨大差异。因此,传统介质膜钝化层与inp半导体界面的结合是通过分子力进行结合的,钝化层与半导体界面间仍然存在着较多的缺陷与界面态。用复合钝化层(复合钝化层由下至上为半绝缘inp或inalas与介质膜钝化层)代替传统介质膜钝化层对探测器进行钝化,减少了钝化层与半导体界面之间的缺陷与界面态,有利于减小器件的漏电流。

附图说明

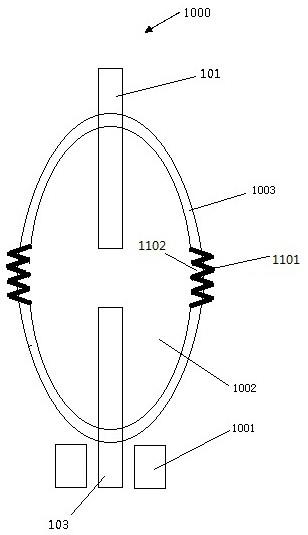

14.图1为本发明实施例提供的低表面漏电流探测器的剖视结构图。

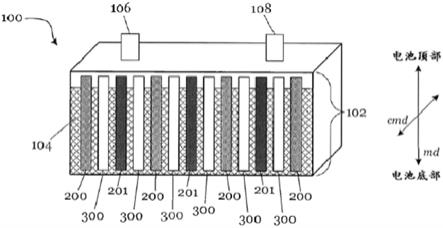

15.图2为本发明隔离台外延结构图。

16.图3为本发明p台外延结构图。

17.图4为本发明实施方式的工艺流程图。

18.图5为本发明实施方式的优化后的工艺流程图。

19.图6为本发明实施方式的优化后的另一种工艺流程图。

20.图中:inp衬底10;隔离台20;p台30;第一钝化层40;第二钝化层50;n型接触金属环60;p型接触金属环70;inp缓冲层21;n型掺杂inp层22;n型掺杂接触层23;腐蚀截止层31;光吸收层32;过渡层33;p型帽层34;p型掺杂接触层35;未刻蚀隔离台401;未刻蚀p台402;p台蚀刻掩膜sinx403;n型接触区氮化硅绝缘介质膜501;p型接触区氮化硅绝缘介质膜502;n型接触金属环氮化硅绝缘介质膜601;p型接触金属环氮化硅绝缘介质膜602。

具体实施方式

21.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行详细说明。此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

22.如图1所示,本发明提供一种低漏电流的探测器,包括inp衬底10,在inp衬底10上由下至上依次生长有通过蚀刻形成的隔离台20与p台30。inp衬底10、隔离台20与p台30的上表面以及隔离台20、p台30的侧面依次生长有第一钝化层40与第二钝化层50。隔离台20的上表面设有穿过所述第一钝化层40与第二钝化层50的n型接触金属环60,p台30上表面设有穿过所述第一钝化层40与第二钝化层50的p型接触金属环70。

23.如图2所示,隔离台20由下至上依次为inp缓冲层21、n型掺杂inp层22、n型掺杂接触层23;如图3所示,p台30由下至上依次为腐蚀截止层31、光吸收层32、过渡层33、p型帽层34、p型掺杂接触层35。

24.作为一种优选实施例,inp衬底10掺杂原子为fe,且掺杂浓度为3e17cm

‑3;inp缓冲层21为n型掺杂,掺杂原子为si,且掺杂浓度为2e18cm

‑3,厚度在200nm,为inp衬底10和功能外延层间的缓冲区,用于降低生长缺陷;n型掺杂inp层22掺杂原子为si,且掺杂浓度为5e18cm

‑3,厚度大于1.5um,为隔离台20的主要构成;n型掺杂接触层23为ingaas材料,厚度为30nm,掺杂原子为si,且掺杂浓度为2e19cm

‑3,其与n电极接触,降低接触电阻;腐蚀截止层31为n型掺杂inp材料,厚度为30nm,掺杂原子为si,且掺杂浓度为2e18cm

‑3,用于腐蚀ingaas吸收层的停止层;光吸收层32为本征ingaas材料,厚度为1000nm,光经过此区域后产生载流子(电子和空穴);所述过渡层33为p型掺杂ingaasp材料,厚度为30nm,掺杂原子为zn,且掺杂

浓度为2e18cm

‑3,用于缓解inp和ingaas的价带不连续;所述p型帽层34为p型掺杂inp材料,厚度为300nm,掺杂原子为zn,且掺杂浓度为2e18cm

‑3,用作空穴电流通道;所述p型掺杂接触层35为p型掺杂ingaas材料,厚度为50nm,掺杂原子为zn,且掺杂浓度为2e18cm

‑3,该与顶部p电极接触,降低接触电阻。

25.现有台面探测器在刻蚀过程中,台面及侧面存在大量的悬挂键及表面缺陷,造成漏电流较大,严重影响了探测器的性能。本实施例在探测器的表面设置了复合钝化层,复合钝化层由下至上为第一钝化层40、第二钝化层50。第一钝化层40为半绝缘inp材料,厚度为50nm,掺杂原子为fe,且掺杂浓度为1e10

17

cm

‑3;第二钝化层50为氮化硅,厚度为300nm;第一钝化层40材料与台面材料的晶格常数相互匹配,减少了表面缺陷与界面态,从而有利于减小漏电流。

26.另外,本实施例还提供了一种低表面漏电流的探测器的制作方法,如图4所示,包括如下步骤:步骤s401、在inp衬底10上使用金属有机化学气相沉积法依次生长出inp缓冲层21、n型掺杂inp层22、n型掺杂接触层23、腐蚀截止层31、光吸收层32、过渡层33、p型帽层34、p型掺杂接触层35。

27.步骤s402、通过增强等离子化学气相沉积方法(pecvd)、光刻与反应离子刻蚀(rie)工艺形成p台蚀刻掩膜sinx403。

28.步骤s403、通过电感耦合等离子体(icp)刻蚀与湿法蚀刻工艺形成p台30。icp工艺所用气体为cl2,蚀刻至所述光吸收层32中间位置(腐蚀截止层31上方200

‑

300nm处)。随后用配比为1:1:25的h2so4/h2o2/h2o腐蚀液对剩余的光吸收层32进行刻蚀至腐蚀截止层31上表面,再用配比为4:1的h3po4/hcl腐蚀液对腐蚀截止层31进行刻蚀。腐蚀截止层31腐蚀完成后,再用boe(即缓冲氧化物刻蚀液)去除p台蚀刻掩膜sinx403。

29.步骤s404、通过光刻与化学腐蚀工艺形成隔离台20,所用化学腐蚀溶液为配比为6:150:700的br2/hbr/h2o腐蚀液,腐蚀深度大于1.5um。

30.步骤s405、通过金属有机化学气相沉积法,在inp衬底10、隔离台20、p台30的上表面以及隔离台20、p台30的侧面沉积厚度为50nm 第一钝化层40,掺杂原子为fe,掺杂浓度为1e17cm

‑3。第一钝化层40与台面材料的晶格常数相互匹配,减少了表面缺陷与表面态,有利于减小漏电流。

31.步骤s406、通过pecvd,在第一钝化层40上沉积厚度为300nm的氮化硅第二钝化层50。

32.步骤s407、通过光刻工艺、rie刻蚀工艺对p台30、隔离台20上表面的第二钝化层50进行刻蚀,通过化学腐蚀对p台30、隔离台20上表面的第一钝化层40进行刻蚀,最终刻蚀出p型接触区与n型接触区。

33.步骤s408、通过光刻工艺、电子束蒸发ti、pt、au金属层工艺和剥离工艺,在所述p型接触区形成p型接触金属环70,n型接触区形成n型接触金属环60。

34.作为本实施例一种优选的制作方法,如图5所示,包括如下步骤:步骤s501、在inp衬底10上使用金属有机化学气相沉积法依次生长出inp缓冲层21、n型掺杂inp层22、n型掺杂接触层23、腐蚀截止层31、光吸收层32、过渡层33、p型帽层34、p型掺杂接触层35。

35.步骤s502、通过增强等离子化学气相沉积方法(pecvd)、光刻与反应离子刻蚀(rie)工艺形成p台蚀刻掩膜sinx 403。

36.步骤s503、通过电感耦合等离子体(icp)刻蚀与湿法蚀刻工艺形成p台30。icp工艺所用气体为cl2,蚀刻至所述光吸收层32中间位置(腐蚀截止层31上方200

‑

300nm处)。随后用配比为1:1:25的h2so4/h2o2/h2o腐蚀液对剩余的光吸收层32进行刻蚀至腐蚀截止层31上表面,再用配比为4:1的h3po4/hcl腐蚀液对腐蚀截止层31进行刻蚀。腐蚀截止层31腐蚀完成后,再用boe去除p台蚀刻掩膜sinx 403。

37.步骤s504、通过光刻与化学腐蚀工艺形成隔离台20,所用化学腐蚀溶液为配比为6:150:700的br2/hbr/h2o腐蚀液,腐蚀深度大于1.5um。

38.步骤s505、通过pecvd,在inp衬底10、隔离台20、p台30的上表面以及隔离台20、p台30的侧面沉积厚度为100nm 的n型接触区氮化硅绝缘介质膜501和p型接触区氮化硅绝缘介质膜502。通过光刻工艺、rie刻蚀工艺对氮化硅绝缘介质膜进行刻蚀,在p型接触区、n型接触区保留氮化硅绝缘介质膜。

39.步骤s506、通过金属有机化学气相沉积法,在inp衬底10、隔离台20、p台30的上表面以及隔离台20、p台30的侧面沉积厚度为50nm第一钝化层40,掺杂原子为fe,掺杂浓度为1e17cm

‑3。保留有氮化硅绝缘介质膜处不会生长出外延层。第一钝化层40与台面材料的晶格常数相互匹配,减少了表面缺陷与表面态,有利于减小漏电流。

40.步骤s507、通过pecvd,在第一钝化层40及n型接触区氮化硅绝缘介质膜501、p型接触区氮化硅绝缘介质膜502表面沉积厚度为300nm的氮化硅第二钝化层50。

41.步骤s508、通过光刻工艺、rie工艺对p台30、隔离台20上表面第一钝化层、第二钝化层处p型接触区、n型接触区进行刻蚀,露出探测器p型掺杂接触层35和n型掺杂接触层23。

42.步骤s509、通过光刻工艺、电子束蒸发ti、pt、au金属层工艺和剥离工艺,在所述p型接触区形成p型接触金属环70,n型接触区形成n型接触金属环60。

43.此优选方式在p型接触区与n型接触区优先沉积氮化硅介质绝缘膜,通过rie蚀刻介质膜的条件并不适用于inp或ingaas蚀刻,因此在rie蚀刻氮化硅介质绝缘膜时,不会对inp进行蚀刻;而icp刻蚀inp的条件同时适用于ingaas,因此通过icp对第一钝化层40进行蚀刻形成p/n型接触区时,会造成对p台30与隔离台20上p型掺杂接触层35和n型掺杂接触层23的过刻,采用此优选方式,可避免p型掺杂接触层35和n型掺杂接触层23的过刻;另外如果在s407中,采用化学腐蚀方式对第一钝化层40进行腐蚀,不会对p型掺杂接触层35和n型掺杂接触层23进行过腐蚀,但会造成第一钝化层40相对第二钝化层50的侧蚀,采用此优选方式,通过光刻版的合理设计,可避免第一钝化层40相对第二钝化层50的侧蚀。

44.作为本实施例一种优选的制作方法,如图6所示,包括如下步骤:步骤s601、在inp衬底10上使用金属有机化学气相沉积法依次生长出inp缓冲层21、n型掺杂inp层22、n型掺杂接触层23、腐蚀截止层31、光吸收层32、过渡层33、p型帽层34、p型掺杂接触层35。

45.步骤s602、通过增强等离子化学气相沉积方法(pecvd)、光刻与反应离子刻蚀(rie)工艺形成p台蚀刻掩膜sinx 403。

46.步骤s603、通过电感耦合等离子体(icp)刻蚀与湿法蚀刻工艺形成p台30。icp工艺

所用气体为cl2,蚀刻至所述光吸收层32中间位置(腐蚀截止层31上方200

‑

300nm处)。随后用配比为1:1:25的h2so4/h2o2/h2o腐蚀液对剩余的光吸收层32进行刻蚀至腐蚀截止层31上表面,再用配比为4:1的h3po4/hcl腐蚀液对腐蚀截止层31进行刻蚀。腐蚀截止层31腐蚀完成后,再用boe去除p台蚀刻掩膜sinx 403。

47.步骤s604、通过光刻与化学腐蚀工艺形成隔离台20,所用化学腐蚀溶液为配比为6:150:700的br2/hbr/h2o腐蚀液,腐蚀深度大于1.5um。

48.步骤s605、通过光刻工艺、电子束蒸发ti、pt、au金属层工艺和剥离工艺,在p型接触区形成p型接触金属环70,n型接触区形成n型接触金属环60。

49.步骤s606、通过pecvd,在inp衬底10、隔离台20、p台30、p型接触金属环70,n型接触金属环60的上表面以及隔离台20、p台30的侧面沉积厚度为50nm氮化硅介质膜;通过光刻工艺、rie等离子刻蚀工艺对氮化硅介质膜进行刻蚀,在已蒸镀电极的p型、n型接触区位置保留氮化硅介质膜(即n型接触金属环氮化硅绝缘介质膜601和p型接触金属环氮化硅绝缘介质膜602)以保护金属电极。

50.步骤s607、通过金属有机化学气相沉积法,在inp衬底10、隔离台20、p台30的上表面以及隔离台20、p台30的侧面沉积厚度为50nm第一钝化层40,掺杂原子为fe,掺杂浓度为1e17cm

‑3。保留有氮化硅绝缘介质膜处不会生长出外延层,第一钝化层40与台面材料的晶格常数相互匹配,减少了表面缺陷与表面态,有利于减小漏电流 。

51.步骤s608、通过pecvd,在第一钝化层40表面沉积厚度为300nm的氮化硅第二钝化层50。

52.步骤s609、通过光刻工艺、rie刻蚀工艺对n型接触金属环氮化硅绝缘介质膜601和p型接触金属环氮化硅绝缘介质膜602进行刻蚀,露出p型接触金属环70、n型接触金属环60。

53.该优选制作工艺优先制作p型接触金属环70、n型接触金属环60,避免了后续电极爬坡工艺困难,同时可减小电极寄生效应。

54.上述专利描述inp基衬底的台面型探测器,本发明还可以延伸至gaas基及si基材料的探测器,其台面可以采用相应的材质。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。