用于管芯向上的扇出型封装的玻璃载体及其制造方法

1.相关申请的交叉引用

2.本技术根据35u.s.c.

§

119要求2019年3月7日提交的系列号为62/815125的美国临时申请的优先权权益,本文以该申请的内容为基础并将其通过引用全文纳入本文。

技术领域

3.本公开涉及用作扇出型封装件的玻璃载体及其制造方法。此外,本公开涉及包含玻璃载体的集成电路封装件及其制造方法。

背景技术:

4.结构化玻璃制品可具有腔体或通道,这些腔体或通道可用于各种应用,例如包括但不限于集成电路封装件、光学包封件和微流体装置。微电子部件(例如,芯片、天线和传感器)的异构集成是利用由结构化玻璃制品形成的高密度封装的有效方式。然而,由于加工温度和/或微电子部件周围的环氧化合物的流动和固化,微电子部件可能位移。因此,需要能够使微电子部件定位具有高精度的扇出型封装。

技术实现要素:

5.根据一个方面,一种晶片级或面板级包封的封装件包括玻璃基材,所述玻璃基材包括与玻璃芯体层熔合的玻璃包覆层,所述玻璃基材包括腔体,其中,所述玻璃包覆层在蚀刻剂中具有比玻璃芯体层更高的蚀刻速率。所述晶片级或面板级包封的封装件还包括设置在腔体中的微电子部件,以及包封剂,所述包封剂对玻璃基材密封以使得微电子部件被包封在腔体内。

6.根据第2个方面,一种晶片级或面板级包封的封装件包括如前述方面所述的晶片级或面板级包封的封装件,其中,所述腔体延伸通过玻璃包覆层而到达玻璃基材的玻璃芯体层。

7.根据第3个方面,一种晶片级或面板级包封的封装件包括如前述任一方面所述的晶片级或面板级包封的封装件,其中,所述腔体的宽度比微电子部件的宽度大0.5至1.5μm。

8.根据第4个方面,一种晶片级或面板级包封的封装件包括如前述任一方面所述的晶片级或面板级包封的封装件,其中,所述腔体的深度等于玻璃包覆层的厚度。

9.根据第5个方面,一种晶片级或面板级包封的封装件包括如前述任一方面所述的晶片级或面板级包封的封装件,其中,玻璃包覆层的厚度为5μm至50μm。

10.根据第6个方面,一种晶片级或面板级包封的封装件包括如前述任一方面所述的晶片级或面板级包封的封装件,其还包括至少沉积在微电子部件与一部分腔体之间以及玻璃基材表面与包封剂之间的脱粘层。

11.根据第7个方面,一种晶片级或面板级包封的封装件包括如第6方面所述的晶片级或面板级包封的封装件,其中,脱粘层的厚度为1μm至5μm。

12.根据第8个方面,一种晶片级或面板级包封的封装件包括如前述任一方面所述的

晶片级或面板级包封的封装件,其中,腔体侧壁与腔体底板之间的角为75

°

至90

°

。

13.根据第9个方面,一种晶片级或面板级包封的封装件包括如前述任一方面所述的晶片级或面板级包封的封装件,其中,包封剂包含环氧化合物。

14.根据第10个方面,一种晶片级或面板级包封的封装件包括如前述任一方面所述的晶片级或面板级包封的封装件,其中,玻璃包覆层在蚀刻剂中的蚀刻速率与玻璃芯体层在蚀刻剂中的蚀刻速率的比值为10至65。

15.根据第11个方面,一种形成晶片级或面板级包封的封装件的方法包括:在玻璃基材中蚀刻腔体,所述玻璃基材包括与玻璃芯体层熔合的玻璃包覆层,其中,所述玻璃包覆层在蚀刻剂中具有比玻璃芯体层更高的蚀刻速率。所述方法还包括:将微电子部件沉积到腔体中以及将包封剂对玻璃基材密封,以使得微电子部件被包封在腔体内。所述晶片级或面板级包封的封装件在腔体与微电子部件之间不含粘合剂。

16.根据第12个方面,一种方法包括如第11个方面所述的方法,其中,使包封剂对玻璃基材密封包括:使环氧化合物沿着玻璃基材表面以及围绕微电子部件流动,以及使环氧化合物固化。

17.根据第13个方面,一种方法包括如第11或12个方面所述的方法,其中,蚀刻包括湿法蚀刻。

18.根据第14个方面,一种方法包括如第11至13个方面中任一方面所述的方法,其还包括:在微电子部件沉积在腔体中之前,先在腔体内沉积涂层。

19.根据第15个方面,一种方法包括如第14个方面所述的方法,其中,所述涂层包括脱粘层。

20.根据第16个方面,一种方法包括如第14至15个方面中任一方面所述的方法,其中,沉积涂层包括:使涂层至少沉积在腔体的底板上。

21.根据第17个方面,一种方法包括如第14至16个方面中任一方面所述的方法,其还包括:在使包封剂对玻璃基材密封之前,先在玻璃基材的表面上沉积涂层,其中,包封剂被密封到该表面。

22.根据第18个方面,一种方法包括如第11至17个方面中任一方面所述的方法,其中,玻璃包覆层在蚀刻剂中的蚀刻速率与玻璃芯体层在蚀刻剂中的蚀刻速率的比值为10至65。

23.根据第19个方面,一种方法包括如第11至18个方面中任一方面所述的方法,其中,腔体侧壁与腔体底板之间的角为75

°

至90

°

。

24.应理解,前面的一般性描述和以下的具体实施方式都仅仅是示例性的,并且旨在提供用于理解所要求保护的主题的性质和特性的总体评述或框架。所附附图提供了进一步理解,附图被结合在本说明书中并构成说明书的一部分。附图说明了一种或多种实施方式,并与说明书一起用来解释各种实施方式的原理和操作。

附图说明

25.图1是根据本文所示和所述的一个或多个实施方式的玻璃基材的截面示意图;

26.图2是根据本文所示和所述的一个或多个实施方式,当通过掩模来将图1的玻璃基材选择性暴露于蚀刻剂,以在包覆层中形成腔体时,图1的玻璃基材的截面示意图;

27.图3是根据本文所示和所述的一个或多个实施方式,在图1

‑

2的玻璃基材中形成腔

体并移除掩模后,图1

‑

2的玻璃基材的截面示意图;

28.图4是根据本文所示和所述的一个或多个实施方式,分别在图1

‑

2的玻璃基材中形成腔体并移除掩模后,图1

‑

2的玻璃基材的透视图;

29.图5是根据本文所示和所述的一个或多个实施方式,具有沿着腔体的侧壁和底板沉积的脱粘层的重构的晶片级和/或面板封装件的实施方式的截面示意图;

30.图6是根据本文所示和所述的一个或多个实施方式,具有沿着腔体的底板沉积的脱粘层的重构的晶片级和/或面板级封装件的实施方式的截面示意图;和

31.图7是根据本文所示和所述的一个或多个实施方式,具有包封剂的重构的晶片级和/或面板级封装件的截面示意图,所述包封剂位于玻璃基材上以及围绕微电子部件。

具体实施方式

32.现将对附图所示的各个实施方式进行详细说明。只要可能,在所有附图中将使用相同的附图标记来表示相同或类似的部分。附图中的部件不一定按比例绘制,而是重点在于说明示例性实施方式的原理。

33.在各个实施方式中,玻璃制品包括玻璃基材以及在玻璃基材中形成的腔体。在一些实施方式中,玻璃基材包括与玻璃芯体层熔合的玻璃包覆层,并且玻璃包覆层在蚀刻剂中具有比玻璃芯体层更高的蚀刻速率。在各个实施方式中,所述腔体形成于玻璃包覆层中。在各个实施方式中,在腔体中设置有微电子部件,并且包封剂对玻璃基材进行密封,以使得微电子部件被包封在腔体内。在各个实施方式中,玻璃制品在腔体与微电子部件之间不含粘合剂。

34.在各个实施方式中,一种形成晶片级或面板级包封的封装件的方法包括:在玻璃基材中的腔体内沉积微电子部件。在一些实施方式中,玻璃基材包括与玻璃芯体层熔合的玻璃包覆层,并且玻璃包覆层在蚀刻剂中具有比玻璃芯体层更高的蚀刻速率。在一些实施方式中,所述方法还可以包括:使包封剂对玻璃基材密封,以使得微电子部件被包封在腔体内。在各个实施方式中,晶片级或面板级包封的封装件在腔体与微电子部件之间不含粘合剂。

35.在一些实施方式中,一种集成电路封装件包括如本文所述的玻璃制品。例如,集成电路封装件包括位于玻璃制品的一个或多个腔体的每个腔体中的微电子装置(例如,集成电路芯片)。该集成电路封装件可得益于如本文所述的玻璃制品。例如,这样的玻璃制品能够将微电子装置精确地放置于在玻璃制品中形成的腔体内,并且防止微电子装置在加工和包封期间位移而无需在微电子装置与玻璃制品之间使用粘合剂。

36.术语“连接”意为两个构件直接或间接地彼此结合。这种结合本质上可以是静止的或者本质上是可移动的。这种结合可以通过两个构件或两个构件和任何另外的中间构件实现,这些构件可以彼此一体地形成为单个整体,或者两个构件或两个构件与任何另外的中间构件彼此附接。这种结合本质上可以是永久性的,或者本质上可以是可拆卸或可松脱的。

37.术语“玻璃”和“玻璃组合物”涵盖玻璃材料和玻璃陶瓷材料,如这两类材料通常被理解的那样。同样地,术语“玻璃结构”涵盖包含玻璃的结构。术语“重构晶片级和/或面板级封装件”涵盖包括晶片级封装件和面板级封装件的任何尺寸的重构基材封装件。

38.术语“由

……

形成”可意为包含、基本上由

……

组成或由

……

组成中的一种或多种

情况。例如,由特定材料形成的部件可包含该特定材料,基本上由该特定材料组成,或者由该特定材料组成。

39.除非另有说明,否则本文所用的方向术语——例如上、下、右、左、前、后、顶部、底部、垂直、水平——仅仅是参照绘制的附图而言,并不用来暗示绝对的取向。

40.除非另有明确说明,否则本文所述的任何方法不应理解为其步骤需要按具体顺序进行,或者要求使任何设备具有特定取向。因此,如果方法权利要求没有实际叙述其步骤要遵循的顺序,或者任何设备没有实际叙述各组件的顺序或取向,或者权利要求书或说明书中没有另外具体陈述步骤限于具体顺序,或者没有叙述设备组件的具体顺序或取向,那么在任何方面都不应推断顺序或取向。这适用于解释上的任何可能的非表达性基础,包括:涉及步骤安排的逻辑问题、操作流程、组件的顺序或组件的取向问题;由语法组织或标点派生的明显含义问题和说明书中描述的实施方式的数量或类型问题。

41.除非上下文另外清楚地说明,否则,本文所用的单数形式“一个”、“一种”以及“该/所述”包括复数指代。因此,例如,提到的“一种”部件包括具有两种或更多种这类部件的方面,除非文本中有另外的明确表示。并且,当在词语“或”的后面没有“任一”(或指示“或”明确表示为排他性的其他类似语言——例如,x或y中的仅一种等)的情况下使用词语“或”时,其应被解释为包含性的(例如,“x或y”表示x或y中的一种或两种)。

42.术语“和/或”也应被解释为包含性的(例如“x和/或y”意为x或y中的一种或两种)。在“和/或”或者“或”用作三个或更多个条目的组的连接的情况下,该组应被解释为仅包括一个条目,所有条目在一起,或这些条目的任何组合或数量。另外,说明书和权利要求中使用的术语,例如具有、具备、涵盖和含有应被理解为与术语包含和包括同义。

43.所公开的范围应理解为包含任何及所有子范围或各个范围包含的任何和所有的单个值,并且为描述这些子范围或单个值的权利要求提供支持。例如,陈述的1至10的范围应被理解为在最小值1与最大值10之间的任何及所有子范围或者它们之间的单个值(包括和/或不包括端点),并且为描述这些子范围或单个值的权利要求提供支持;也即,以最小值1或更大的数值开始并以最大值10或更小的数值结束的所有子范围(例如5.5至10、2.34至3.56等)或者1至10的任何值(例如3、5.8、9.9994等)。

44.附图应被解释为例示了按比例绘制的一个或多个实施方式和/或未按比例绘制的一个或多个实施方式。这意味着附图可被解释为,例如,示出的:(a)所有事物均按比例绘制,(b)所有事物均未按比例绘制,或(c)一个或多个特征按比例绘制而一个或多个特征未按比例绘制。因此,附图可单独或彼此组合地为描述任何例示的特征的大小、比例和/或其他尺寸提供支持。此外,所有这些大小、比例和/或其他尺寸应被理解为可在任一个方向上变化0

‑

100%,并因此对描述这些数值或者可由这些数值形成的任何及所有范围或子范围的权利要求提供支持。

45.权利要求中所述的术语应当通过参考广泛使用的通用词典和/或相关技术词典中的相关条目,本领域技术人员通常理解的含义等来确定它们的普通和惯用含义,并且应理解为,由这些来源中的任何一个或组合所赋予的最广泛的含义(例如,应组合两个或更多个相关词典的条目以提供条目组合的最广泛含义等)仅受以下例外的约束:(a)如果术语的使用方式比其普通和惯用含义更广泛,则该术语应具有其普通和惯用含义加上额外的扩展含义,或(b)如果术语已明确定义为通过在术语后面的短语“本文件中使用的术语应意为”或

类似的语言(例如,“该术语意为”、“该术语定义为”、“出于本公开的目的,该术语是指”等等)来描述该术语,则该术语明确定义为具有不同的含义。提到具体实例时使用的“即”、词语“发明”等并不意味着援引例外情况(b)或以其他方式来限制所述的要求保护的术语的范围。除了例外情况(b)所适用的情形外,本文件中的任何内容均不应视为放弃或拒绝权利要求的范围。

46.集成电路(ic)封装是半导体装置制造的后端工艺,其中,半导体材料块被封装在支承箱中,所述支承箱提供了从芯片到印刷电路板的电连接,并且防止了半导体材料的物理损坏和腐蚀。所述箱也被称为“封装件”,其支承将装置连接到电路板的电触头。该过程常被称为封装,但是也可被称为半导体装置组装、包封或密封。

47.晶片级封装或晶片级芯片规模封装(wlp)是ic(例如芯片或管芯)仍是晶片的部分时对ic进行封装的技术,这与将晶片剖切成各个电路(切块)然后再将其封装的更为常规的方法形成对照。wlp能够以晶片级实现晶片制造、封装、测试和老化的集成,从而简化了装置从硅开始到客户出货所经历的制造过程。wlp可包括:扩展晶片制造过程以包括装置互连和装置保护过程。大多数其他种类的封装工艺先对晶片进行切块,然后将单独的管芯放置在塑料封装件中并附接焊料凸块。wlp涉及在ic仍在晶片中时,将封装件的顶部和底部外层以及焊料凸块附接于ic,然后对晶片进行切块。

48.wlp的一种类型是扇入(fi),其所有的接触端子均在管芯的占用面积内。当调整接触端子的布局以匹配下一级基材的设计时,这种构造可具有显著限制。扇出(fo)是另一种类型的wlp,其代表管芯级封装与fi wlp之间的折衷。fo wlp涉及对半导体晶片进行切块,然后将单个化ic嵌在重构或人工模制的晶片中。在重构晶片上,各管芯彼此分开一定的距离,该距离足够地大以允许使用标准wlp工艺来制造所需的fo再分布层(rdl)。fo wlp提供了将引线节距小的较小的管芯连接到引线节距较大的印刷电路板的一种方式。扇出型面板级封装(fo plp)可以用作fo wlp的替代。面板级封装(plp)可以比wlp更加划算,因为可使用现有的印刷电路板(pcb)和相关产业的工艺和设备,而不是fo wlp所需的更加昂贵的半导体加工设备。

49.在包括常规载体的工艺(plp或wlp中的任一种)中,由于加工温度和/或微电子部件周围的环氧化合物的流动和固化,微电子部件可能位移,这降低了管芯精度。然而,增加精度需求要求减少或消除微电子部件位移。本文所述的各个实施方式通过精确蚀刻尺寸精确设置的腔体来确保微电子部件在施加和固化包封剂(例如环氧化合物)期间处于适当位置,减少或消除了微电子部件的位移,同时消除了对管芯附接膜(daf)的需要。

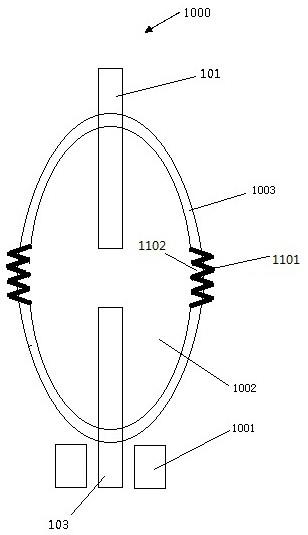

50.图1是玻璃基材100的一些实施方式的截面示意图。玻璃基材100包括玻璃芯体层110,其与第一或上玻璃包覆层105和第二或下玻璃包覆层107连接。玻璃基材100包括多个玻璃层并且可被认为是玻璃层压件。在一些实施方式中,层105、107、110熔合在一起而在它们之间不具有任何粘合剂、聚合物层、涂层等。在另一些实施方式中,层105、107、110使用粘合剂等连接(例如粘合)在一起。

51.玻璃基材100可具有任何合适的组成并且可使用任何合适的方法来制造。合适的玻璃组合物的实例可包括碱土金属铝硼硅酸盐玻璃、锌硼硅酸盐玻璃和钠钙玻璃以及玻璃陶瓷,例如富含氧化镁、氧化钇、氧化铍、氧化铝或氧化锆的那些。一般而言,玻璃基材100以及玻璃基材中的层105、107、110中的任一者可具有任何组成或者可以使用下述文献中公开

的任何方法制造:2016年5月17日授权的题为“machining of fusion

‑

drawn glass laminate structures containing a photomachinable layer(含有可光加工层的熔合拉制玻璃层压结构的机械加工)”的第9,340,451号美国专利;以及2017年3月16日公开的题为“glass article and method for forming the same(玻璃制品及其形成方法)”的第2017/0073266号美国专利申请公开,这些文献各自通过引用全文纳入本文。

52.玻璃基材100被构造成使玻璃包覆层105、107中的至少一者和玻璃芯体层110具有不同的物理尺寸和/或物理性质,从而允许相对于玻璃芯体层110选择性地移除至少一个玻璃包覆层105、107,以形成尺寸精确设置的腔体425,所述腔体425的尺寸和形状可被设置用于接收微电子部件。

53.玻璃基材100的一个可广泛变化的方面是层105、107、110的厚度。例如,层105、107、110可全部具有相同厚度或不同厚度,或者其中的两个层可具有相同厚度,而第三层具有不同厚度。在一些实施方式中,玻璃包覆层105、107中的一者或两者的厚度可以小于被封装的微电子部件的厚度。

54.在一些实施方式中,玻璃包覆层105、107中的一者或两者为5微米至50微米厚,5微米至20微米厚,或约10微米至约15微米厚。在另一些实施方式中,包覆层105、107中的一者或两者为至少5微米厚或至少10微米厚。在另一些实施方式中,包覆层105、107中的一者或两者不超过50微米厚,不超过20微米厚,或者不超过15微米厚。这些厚度一般小于通常经历fo wlp或plp加工的微电子部件的厚度。但应理解,玻璃包覆层105、107可具有其他厚度,尤其是当与厚度小于或大于所公开的厚度的微电子部件一起使用时。

55.玻璃基材100的另一个可广泛变化的方面是层105、107、110的玻璃组成。例如,层105、107、110可全部具有相同的玻璃组成或不同的玻璃组成,或者其中的两个层可具有相同的玻璃组成,而第三层具有不同的玻璃组成。一般而言,玻璃包覆层105、107中的一者或两者的玻璃组成不同于玻璃芯体层110的玻璃组成。这向玻璃包覆层105、107提供了某些性质,使得它们适于形成腔体425。

56.在一些实施方式中,层105、107、110的玻璃组成可不同,以使得层105、107、110在蚀刻剂中的耐久性不同。例如,在实施方式中,玻璃包覆层105、107中的一者或两者在蚀刻剂中的溶解速率(或蚀刻速率)可以与玻璃芯体层110不同。层105、107、110之间的不同耐久性使得可在玻璃基材100的表面中形成腔体425。例如,玻璃包覆层105、107在蚀刻剂中可具有足够高的溶解速率,以使得它们可被蚀刻而形成腔体425。另一方面,玻璃芯体层110在蚀刻剂中可具有足够低的溶解速率,以使得其基本上不易被蚀刻。因此,玻璃芯体层110可起到蚀刻停止的作用以限制使用蚀刻剂能将玻璃基材100蚀刻到的深度。

57.在一些实施方式中,玻璃包覆层105、107中的一者或两者在蚀刻剂中的溶解速率大于玻璃芯体层110的溶解速率。例如,玻璃芯体层110在蚀刻剂中的溶解速率可以为零或足够接近零,以使得其不易被蚀刻到任何显著的程度。

58.应理解,可对图1所示的玻璃基材100的实施方式进行多种改变。例如,在一些实施方式中,玻璃基材100可仅包括两个玻璃层105、110。在另一些实施方式中,玻璃基材100可包括四个或更多个玻璃层。还考虑了多种其他变化形式。

59.在一些实施方式中,在玻璃基材100中形成腔体425以将玻璃基材转变成如本文所述的结构化制品。可使用图2所示的方法在玻璃基材100的表面中形成腔体425。在一些实施

方式中,该方法包括:在玻璃基材100的表面上形成掩模215。例如,在玻璃包覆层105和/或玻璃包覆层107的表面上形成掩模215。可通过印刷(例如,喷墨印刷、凹版印刷、丝网印刷或另外的印刷工艺)或另外的沉积工艺来形成掩模215。在一些实施方式中,掩模215耐蚀刻剂(例如,将要用于在玻璃基材100中蚀刻出腔体425的蚀刻剂)。例如,掩模215可包含丙烯酸酯、多官能丙烯酸酯正乙烯基己内酰胺或另外合适的掩模材料。在一些实施方式中,掩模215由包含底漆并且所述底漆用于增强掩模与玻璃基材100之间的粘性的油墨材料形成。这种增强的粘性可减少蚀刻剂在掩模215与玻璃基材100之间渗漏,这可有助于实现本文所述的精确腔体。

60.在一些实施方式中,掩模215包括一个或多个开口区域,在所述开口区域处,玻璃基材100保持不被覆盖。掩模215的开口区域可具有与要在玻璃基材100中形成的腔体245的所需图案对应的图案。例如,掩模215的图案可以是规则重复的矩形形状的阵列(例如,用于接收如本文所述的微电子部件)。在这样的实施方式中,通过掩模215来图案化的形状可紧密对应于微电子部件的形状。也可使用其他形状,并且所述形状可紧密对应于微电子部件的形状或者能够将微电子部件稳固地保持在玻璃基材100上的位置中。因此,掩模215可被构造成蚀刻掩模,从而能够如本文所述选择性地蚀刻玻璃包覆层105和/或玻璃包覆层107,并且在玻璃基材100中形成腔体425。

61.在一些实施方式中,将其上设置有掩模215的玻璃基材100暴露于蚀刻剂220。例如,如图2所示,使玻璃包覆层105和/或玻璃包覆层107接触蚀刻剂220,由此选择性地蚀刻未被掩模215覆盖的相应的玻璃包覆层的暴露部分,并且在玻璃基材中形成腔体425,由此将基材转变成成形制品。因此,在形成腔体425后,玻璃基材100可被称为成形制品。在一些实施方式中,将其上设置有掩模215的玻璃基材100暴露于处于蚀刻温度下的蚀刻剂220并持续一定的蚀刻时间。例如,蚀刻温度为20℃、22℃、25℃、30℃、35℃、40℃、45℃或50℃,或者由所述数值的任何组合限定的任何范围。较低的蚀刻温度可有助于在蚀刻期间保持掩模215的完整性,而这可使蚀刻时间增加和/或改进如本文所述的腔体形状。附加或替代性地,蚀刻时间可以是10分钟、15分钟、20分钟、25分钟、30分钟、35分钟、40分钟、45分钟、50分钟、55分钟、60分钟、65分钟、70分钟、75分钟、80分钟、85分钟、或90分钟,或者由所述数值的任何组合限定的任何范围。相对较长的蚀刻时间(例如,大于10分钟的蚀刻时间)能够实现如本文所述的腔体425的基本上垂直的侧壁。

62.在一些实施方式中,玻璃包覆层105和/或玻璃包覆层107比玻璃芯体层110蚀刻至少快1.5倍,至少快2倍,至少快5倍,至少快10倍,至少快20倍,或至少快60倍。如本文中所用,术语“蚀刻速率”是指每单位时间的厚度。例如,在一些实施方式中,蚀刻速率可以是8μm/分钟。附加或替代地,蚀刻剂中的玻璃包覆层的溶解速率与蚀刻剂中的玻璃芯体层的溶解速率的比值大于或等于10且小于或等于65。例如,该比值可以大于或等于10,大于或等于15,大于或等于20,大于或等于25,大于或等于30,大于或等于35,大于或等于40,大于或等于45,大于或等于50,大于或等于55,或者大于或等于60。该比值可以小于或等于65,小于或等于60,小于或等于55,小于或等于50,小于或等于45,小于或等于40,小于或等于35,小于或等于30,小于或等于25,小于或等于20,或者小于或等于15。在一些实施方式中,该比值可以是由所述数值的任何组合限定的任何范围。

63.在一些实施方式中,所述形成腔体425包括:基本上完全蚀刻穿过玻璃包覆层105

和/或玻璃包覆层107,以在腔体的底部处暴露一部分玻璃芯体层110,如图3所示。因此,腔体425的侧壁305由玻璃包覆层105和/或玻璃包覆层107限定,并且腔体的底板310由玻璃芯体层110限定。在一些实施方式中,在所述形成腔体425期间,玻璃芯体层110基本上不被蚀刻。因此,玻璃芯体层110起到决定腔体425的深度的蚀刻停止作用。

64.在一些实施方式中,每个腔体425的底板310基本上是平坦的。例如,沿着腔体425的周界的第一位置处的腔体425的第一深度与沿着腔体425的周界并且与第一位置相对(例如,直径上相对)的第二位置处的腔体425的第二深度之间的差异为至多3μm,至多2μm,至多1μm,至多0.9μm,至多0.8μm,至多0.7μm,至多0.6μm,至多0.5μm,至多0.4μm,至多0.3μm,至多0.2μm,或者至多0.1μm。在一些实施方式中,该差异可以是由所述数值的任何组合限定的任何范围。这种低的深度差可通过玻璃芯体层110所提供的蚀刻停止来实现。例如,腔体425的深度可以主要由玻璃包覆层105和/或玻璃包覆层107的厚度t来决定,并且不会因为蚀刻温度和/或蚀刻时间改变而显著改变。

65.在一些实施方式中,腔体425的侧壁305基本上是垂直的。例如,在腔体425的侧壁305与底板310之间形成的角θ(如图3所示)为90

°

,或者75

°

至90

°

。在一些这样的实施方式中,腔体的深度为至少2μm、至少5μm、至少10μm、至少12μm或者至少约15μm。在一些实施方式中,该深度可以是由所述数值的任何组合限定的任何范围。这种低的侧壁角可通过增加蚀刻时间来实现,而玻璃芯体层110所提供的蚀刻停止使得增加蚀刻时间成为可能。例如,可以延长蚀刻时间以在腔体的底部附近移除侧壁与底板之间的相交处的材料而不显著增加腔体的深度。相比于常规的湿法蚀刻工艺,移除这些材料可得到更直(例如垂直)的侧壁。

66.在一些实施方式中,在形成腔体425后,从玻璃基材100移除掩模215。例如,所述移除掩模215包括:使掩模与溶剂接触,由此从玻璃基材的表面移除掩模。在一些实施方式中,溶剂是水。例如,所述移除掩模215包括:将其上设置有掩模215的玻璃基材100浸没到水中,由此从玻璃基材的表面移除掩模。图3

‑

4分别是在其中形成有腔体425并且从其中移除了掩模215的玻璃基材100的截面示意图和透视图。在玻璃基材100内形成腔体425的另外的详细内容可在2017年11月6日提交的题为“precision structured glass articles,integrated circuit packages,optical devices,microfluidic devices,and methods for making the same(结构精密的玻璃制品、集成电路封装件、光学装置、微流体装置及其制造方法)”的第62/582,297号专利申请中找到,所述文献通过引用全文纳入本文。

67.图3

‑

4所示的腔体425具有与微电子部件700的形状对应的矩形形状(如在图4中可见)。但应理解,腔体425可具有任何合适的形状,并且可取决于待固定在其中的具体微电子部件而变化。例如,腔体425可具有正方形形状、圆形形状或任何其他多边形或非多边形形状。

68.如图5所示,在各个实施方式中,可以沿着每个腔体425的侧壁305和底板310设置涂层,该涂层为脱粘层505的形式。当玻璃制品作为载体移除时,该布置能够从腔体425容易地移除位于腔体425内的微电子部件。另外,当密封剂流动到腔体425中并且围绕微电子部件流动时,这种布置将能够在加工后使密封剂与玻璃载体脱粘,这将在下文有更详细的描述。然而,还考虑了可以从腔体425的侧壁305移除脱粘层505,例如,如图6所示,和/或从玻璃基材的顶表面移除脱粘层505(未示出)。在一些实施方式中,例如,如图5和6所示的实施方式,除了沉积在腔体425内,脱粘层505还可沉积在相邻腔体425之间的玻璃包覆层105的

表面上。在另一些实施方式中,脱粘层505可以沿着相邻腔体425之间的玻璃包覆层105的顶表面沉积,但是不在腔体425内沉积。

69.脱粘层505有时被称为离型层,其可以是能够在玻璃基材100与包封剂702(示于图7)之间实现临时结合的任何合适的层。在一些实施方式中,脱粘层505例如可以是光热转换离型涂层(lthc),或者uv或ir烧蚀层。可以将脱粘层505施加于玻璃基材100,并且当施加于玻璃基材时,其是化学和热稳定的,以完全经受得住加工条件。

70.在从包封剂702移除玻璃基材100之前,可以烧蚀或以其他方式分解脱粘层505以使玻璃基材100与包封剂702松脱。脱粘层505例如可通过将脱粘层材料旋涂或喷涂到玻璃基材100上来形成。在一些实施方式中,取决于脱粘层505的具体成分组成,可以对脱粘层505进行固化。也可以采用形成脱粘层505的其他方法。

71.在各个实施方式中,脱粘层505的厚度为1μm至5μm,或2μm至3μm。例如,脱粘层505的厚度可以为1μm、1.2μm、1.5μm、1.7μm、1.9μm、2.0μm、2.1μm、2.2μm、2.3μm、2.4μm、2.5μm、2.6μm、2.7μm、2.8μm、2.9μm、3.0μm、3.2μm、3.5μm、3.7μm、3.9μm、4.0μm、4.2μm、4.5μm、4.7μm或5.0μm。在一些实施方式中,该厚度可以是由所述数值的任何组合限定的任何范围。在另一些实施方式中,脱粘层505的厚度可以大于3μm,但是附加的厚度可能导致微电子部件在腔体中额外位移。

72.在一些实施方式中,微电子部件700被放置在腔体425内,并且包封剂702可直接围绕腔体425的微电子部件700填充。例如,在各个实施方式中,腔体425的宽度w

c

可以比微电子部件700的宽度w

m

大0.5μm至1.5μm。例如,宽度w

c

可以比微电子部件700的宽度w

m

大0.5μm、0.6μm、0.7μm、0.8μm、0.9μm、1.0μm、1.1μm、1.2μm、1.3μm、1.4μm或1.5μm。在一些实施方式中,该宽度差异可以是由所述数值的任何组合限定的任何范围。不囿于理论,认为至少部分的腔体壁与微电子部件700之间的少量的空间能够使玻璃基材和微电子部件二者在加工期间膨胀并接触,但不会因为腔体与微电子部件700之间的接触而产生附加应力,同时防止了容差范围之外的微电子部件700的位移。另外,腔体与微电子部件的宽度差异允许包封剂702进一步包围微电子部件700,从而将微电子部件700固定就位。

73.在一些实施方式中,腔体425的侧壁305可以具有相对于腔体425的底板310的角θ(示于图3),该角θ小于90

°

,从而能够使包封剂702在微电子部件700与侧壁305之间沉积。换言之,在微电子部件700与侧壁305之间填充有包封剂702的实施方式中,每个腔体425在玻璃基材的顶表面处的宽度可以大于沿着腔体425的底板310的宽度。在另一些实施方式中,腔体425的侧壁305相对于腔体425的底板310的角θ可以等于90

°

。然而,侧壁相对于腔体底板的具体角可以变化。

74.在一些实施方式中,微电子部件700是硅基ic芯片、天线、传感器等。更具体地,例如但非限制,微电子部件700可以是mems传感器、mems镜、量子点、图像传感器或led。在各个实施方式中,所述微电子部件700的厚度大于或等于玻璃包覆层105的厚度。换言之,在一些实施方式中,微电子部件700的厚度大于或等于腔体425的深度。在这样的实施方式中,微电子部件700不与玻璃包覆层105的表面齐平,因此,包封剂702能够围绕微电子部件700流动并将它们固定就位。

75.包封剂702可以是任何类型的模制化合物,包括但不限于由环氧树脂、酚类硬化剂、二氧化硅、催化剂、颜料和脱模剂组成的复合材料,以及本领域已知和使用的其他模制

化合物。所选择的具体的包封剂702可以根据其玻璃化转变温度、吸湿率、挠曲模量/强度、热膨胀系数、热导率以及与其中包封的微电子部件的加工步骤和最终应用相关的粘附性质而变化。在本文所述的各个实施方式中,包封剂包含环氧化合物。

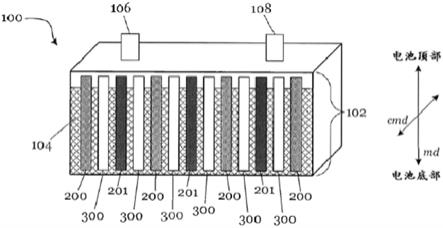

76.在一些实施方式中,玻璃制品可以用作集成电路封装件,尤其是玻璃扇出型封装件。例如,可从基础晶片切块出微电子部件700,将微电子部件700放置在腔体425中以形成重构的晶片级和/或面板级封装件200,如图5

‑

7所示。腔体425可被构造成接收任何合适的微电子部件700。在一些实施方式中,微电子部件700是硅基ic芯片、天线、传感器等。

77.在玻璃基材100中蚀刻了腔体425以及任选地在玻璃基材100的一个或多个表面上沉积脱粘层505之后,在每个对应的腔体425中沉积微电子部件700。如上所述,可取的是,使微电子部件700在玻璃包覆层105和/或玻璃包覆层107的顶表面上方延伸。一旦微电子部件700在腔体425内沉积,则包封剂702对玻璃基材密封以使得微电子部件700被包封在腔体425内。

78.在一些实施方式中,例如,包封剂702是环氧化合物的实施方式中,通过使环氧化合物沿着玻璃基材的顶表面(例如,在图7中沿着玻璃包覆层105的顶表面)以及围绕微电子部件700流动,并且对环氧化合物进行固化,包封剂702对玻璃基材进行密封。取决于所使用的具体的包封剂,可以采用使包封剂702对玻璃基材进行密封的其他方法。

79.在一些实施方式中,在环氧化合物得到固化后,可使管芯与玻璃基材脱粘,从而暴露出固定在包封剂702上的微电子部件700。脱粘可根据本领域已知的技术来进行,并且可以取决于所使用的脱粘层的类型。在一些实施方式中,可以进一步加工管芯,例如,通过研磨或抛光管芯的非活性侧来产生平坦表面。还可能具有并且考虑了其他加工步骤。

80.在本文所述的各个实施方式中,所述封装件在腔体425与微电子部件700之间不含粘合剂。例如,虽然常规晶片级封装件采用管芯附接膜(daf)将微电子部件700结合到腔体425,但是本文所述的实施方式在腔体425与微电子部件700之间提供了精确配合,从而能够在包封剂流动和固定期间,将微电子部件700保持就位而无需使用daf或其他粘合剂。因此,本文所述的各个实施方式减少或消除了由于包封剂的流动和固化造成的管芯位移,同时,由于不需要daf或其他粘合剂来将微电子部件固定就位,因此进一步简化了制造方法。

81.在各个实施方式中,重构的晶片级和/或面板级封装件被描述成包括具有多个腔体的玻璃基材,以及定位在玻璃基材中的所述多个腔体的每个腔体中的微电子部件。应注意,这种重构的晶片级和/或面板级封装件可以具有其中定位有或不定位有微电子部件的额外的腔体。例如,在一些实施方式中,重构的晶片级和/或面板级封装件包括多个腔体,并且在所述多个腔体的每个腔体中定位有微电子部件,以及包括一个或多个其中未定位有微电子部件的额外腔体。在另一些实施方式中,重构的晶片级和/或面板级封装件包括多个腔体,并且在所述多个腔体的每个腔体中定位有微电子部件,并且重构的晶片级和/或面板级封装件不包括额外腔体。

82.权利要求中所述的主题不与本文件中描述或例示的任何实施方式、特征或特征的组合同范围,并且不应被解释为与其同范围。即使在本文件中仅例示和描述了特征或特征组合的一个实施方式也如此。

83.对本领域的技术人员显而易见的是,可以在不偏离所要求保护的主题的精神或范围的情况下进行各种修改和变动。因此,所要求保护的主题不受所附权利要求书及其等同

形式以外的任何内容所限。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。