用于发光二极管中的表面复合速度降低的外延层的再生长

1.非临时转换中的交叉引用

2.本技术要求2019年3月29日提交的美国申请第62/826,683号和2020年3月29日提交的美国申请第16/833,614号的优先权。美国申请第62/826,683号和美国申请第16/833,614号的内容出于所有目的通过引用以其整体并入本文。

3.背景

4.本公开内容的方面涉及发光二极管(led)的设计。随着led的物理尺寸被减小,由于表面复合(surface recombination)导致的效率损失作为影响整体性能的因素变得越来越重要。从层状外延结构(layered epitaxial structure)蚀刻台面(mesa)通常导致包括表面缺陷的经蚀刻的台面端面(etched mesa facet)。这样的不期望的特征倾向于增加表面复合速度并且引起暗电流,这降低led的光转换效率。需要解决在经蚀刻的台面中显示出的表面复合问题的技术,以改善led的效率。

5.附图简述

6.通过实例的方式来说明本公开内容的方面。

7.图1图示了示出被配置为led的经蚀刻的抛物线台面的基本部件的简化图;

8.图2a图示了多于一个垂直台面;

9.图2b图示了具有梯形轮廓的多于一个台面;

10.图3图示了根据本公开内容的实施方案的、在多于一个台面的经蚀刻的端面上作为另外的外延层生长的再生长半导体层;

11.图4描绘了在n型掺杂半导体材料、多量子阱层(multiple quantum well layer)、p型掺杂半导体材料和再生长层的接合处的特写区域(close up area);

12.图5图示了根据本公开内容的实施方案的部分地填充相邻台面之间的空隙的再生长半导体层;

13.图6图示了根据本公开内容的实施方案的第二再生长半导体层,其作为另外的外延层在第一再生长半导体层上生长;

14.图7描绘了在led的n型掺杂半导体材料、多量子阱层和p型掺杂半导体材料以及在led的端面上生长的第一再生长层和第二再生长层的接合处的特写区域;

15.图8是沿着图7中所示的半导体结构的横轴的能带图;

16.图9图示了根据本公开内容的实施方案,在第一再生长半导体层生长之前在台面端面上生长以提供光滑膜(smooth film)的过渡层;

17.图10是根据本公开内容的多种实施方案,呈现用于在配置为led的台面的经蚀刻的端面上再生长外延层的说明性步骤的流程图;

18.图11a和图11b图示了在示例性的清洁工艺期间的台面阵列,所述清洁工艺可以在一个或更多个再生长半导体层的生长之前进行;

19.图12提供了描绘已经经历退火工艺的台面阵列的图像;

20.图13a和图13b描绘了具有在台面端面上外延生长的再生长层的台面阵列;

21.图14a和图14b描绘了在再生长层在外延结构上的生长之前没有经历boe清洁工艺

的台面结构;

22.图15a提供了在台面侧壁的再生长层和外延层之间的界面的特写视图;

23.图15b

‑

图15d提供了在台面侧壁的再生长层和外延层之间的界面的元素布局(elemental mapping)的图像;

24.图16提供了示出贯穿在台面侧壁的再生长层和外延层之间的界面的深度的元素分布的图;

25.图17提供了在应用再生长层之前已经经历boe清洁工艺的台面结构的图像;

26.图18a提供了在台面侧壁的再生长层和外延层之间的界面的特写视图;

27.图18b

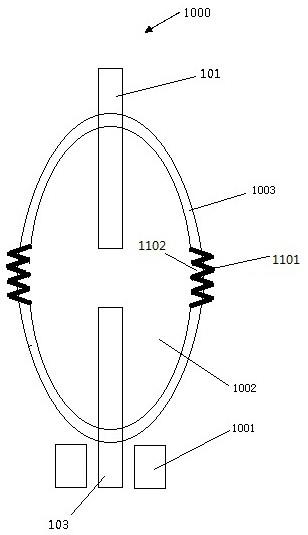

‑

图18d提供了在台面侧壁的再生长层和外延层之间的界面的元素布局的图像;以及

28.图19提供了示出贯穿在台面侧壁的再生长层和外延层之间的界面的深度的元素分布的图。

29.详细描述

30.本公开内容呈现了多种实施方案,其中外延层的再生长被用于以在经蚀刻的端面处提供改善的晶体界面的方式来钝化led台面的经蚀刻的端面,以减少悬挂键(dangling bond)和其他表面缺陷。这样做减少了因与表面状态相关联的非辐射复合而损失的电流,即在led台面的经蚀刻的端面处或在其附近。换句话说,表面复合速度可以被显著降低,并且由于表面复合导致的led的效率损失可以被大大减轻。

31.图1图示了包括抛物线台面结构的led 100的实例。根据本公开内容的实施方案,led 100发射非相干光。led 100可以是具有小于10微米的横向尺寸(lateral dimension)或直径的微led。led 100可以由无机材料诸如多层的半导体材料制成。例如,层状半导体发光器件可以包括多层的iii

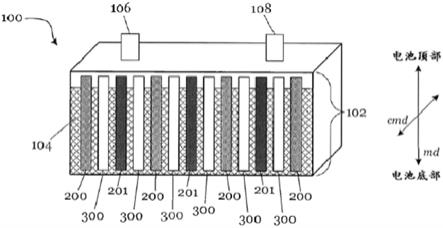

‑

v族半导体材料。iii

‑

v族半导体材料可以包括与v族元素诸如氮(n)、磷(p)、砷(as)或锑(sb)结合的一种或更多种iii族元素诸如铝(al)、镓(ga)或铟(in)。

32.层状半导体器件可以通过使用诸如分子束外延(mbe)、金属有机气相外延(movpe)(也被称为有机金属气相外延(omvpe)或金属有机化学气相沉积(mocvd))、或物理气相沉积(pvd)(例如脉冲激光沉积(pld))的技术在一个或更多个室中在衬底上生长多个外延层来制造。例如,半导体层可以在具有特定晶格取向的衬底上逐层生长,所述衬底诸如蓝宝石、石英、氮化镓(gan)、砷化镓(gaas)、磷化镓(gap)。可以在特定方向上切割硅衬底,以暴露特定平面作为生长表面。

33.led 100可以包括衬底层110,衬底层110可以包括例如氧化铝(al2o3)衬底(“蓝宝石”衬底)或gan衬底。半导体层120可以生长在衬底层110上。半导体层120可以包括iii

‑

v族材料,例如gan,并且可以是p掺杂的(例如,用mg、ca、zn或be掺杂)或n掺杂的(例如,用si或ge掺杂)。在图1中所示的实例中,层120是n型掺杂半导体材料。一个或更多个有源层130可以生长在半导体层120上。有源层130可以包括一个或更多个氮化铟镓(ingan)层、一个或更多个磷化铝铟镓(alingap)层或一个或更多个gan层,它们可以形成一个或更多个异质结构,诸如一个或更多个量子阱。此处,有源层130包括多量子阱(mqw)层。半导体层140可以生长在有源层130上。半导体层140可以包括iii

‑

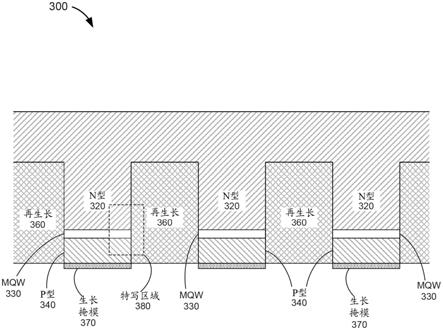

v族材料诸如gan,并且可以是p掺杂的(例如,用mg、ca、zn或be掺杂)或n掺杂的(例如,用si或ge掺杂)。在图1中所示的实例中,层140是p

型掺杂半导体材料。半导体层120和半导体层140夹住有源层130以形成发光二极管。例如,led 100可以包括位于掺杂有镁的p型gan层和掺杂有硅或氧的n型gan层之间的ingan层。在一些实施方案中,led 100可以包括位于掺杂有锌或镁的p型alingap层和掺杂有硒、硅或碲的n型alingap层之间的alingap层。

34.为了与二极管的半导体层120(例如,n

‑

gan层)接触并且为了从led 100更有效地提取由有源层130发射的光,半导体层可以被蚀刻以暴露半导体层120并形成包括层120

‑

140的台面结构。台面结构可以将载流子限制在器件的注入区域内。蚀刻台面结构可能导致台面侧壁的形成,该台面侧壁在本文中还被称为端面,其可能不平行于生长平面,或者在一些情况下正交于生长平面。反射层170可以形成在台面结构的侧壁上。反射层170可以包括氧化物层,诸如氧化硅(sio2)层,并且可以充当反射体以将发射的光反射出led 100。触点180可以形成在半导体层120上,并且可以充当led 100的电极,所述触点180可以包括金属,诸如al、au、ni、ti或其任何组合,或者非金属导电材料,在此图中被示出为n触点。此外,可以形成另一触点190,例如al/ni/au金属层,在此图中被示出为p触点,以与半导体层140欧姆接触,从而充当led 100的另一电极。

35.当电压信号被施加到触点层180和190时,电子和空穴可以在有源层430中复合,其中电子和空穴的复合可以导致光子发射。发射的光子的波长和能量可以取决于有源层130中的价带和导带之间的能带隙。例如,ingan有源层可以发射绿光或蓝光,而alingap有源层可以发射红光、橙光、黄光或绿光。发射的光子可以被反射层170反射,并且可以例如从图1中所示的底侧(例如,衬底110)离开led 100。

36.在一些实施方案中,led 100可以包括另一种形状的台面,所述另一种形状诸如平面形状、垂直形状、圆锥形状、半抛物线形状或抛物线形状,其中台面的基部区域(base area)可以是圆形的、矩形的、六边形的或三角形的。例如,led可以包括弯曲形状(例如,抛物面形状)和非弯曲形状(例如,圆锥形状)的台面。台面可以是截断的或未截断的。

37.图2a图示了多于一个垂直台面200a。与图1中所示的抛物线形台面相反,图2a中所示的台面200a具有垂直定向的侧壁或端面。与图1相比,台面200a的取向在图2a中也已经被翻转。此处,来自每个led的光从图的“顶部”侧离开台面结构。图2a中所示的多于一个台面200a可以形成为显示器贡献光的led阵列。例如,用于每个台面的光可以为显示器的一个像素或像素的一种颜色贡献光。

38.台面200a中的每一个可以是光源中的光发射器。在一些实施方案中,台面200a可以是由无机材料诸如多层的半导体材料制成的微led。层状半导体发光器件可以包括多层的iii

‑

v族半导体材料。iii

‑

v族半导体材料可以包括与v族元素诸如氮(n)、磷(p)、砷(as)或锑(sb)结合的一种或更多种iii族元素诸如铝(al)、镓(ga)或铟(in)。当iii

‑

v族半导体材料中的v族元素包括氮时,iii

‑

v族半导体材料被称为iii

‑

氮化物材料。层状半导体发光器件可以通过使用诸如气相外延(vpe)、液相外延(lpe)、分子束外延(mbe)或金属有机化学气相沉积(mocvd)的技术在衬底上生长多个外延层来制造。例如,半导体材料的层可以在具有特定晶格取向(例如,极性取向、非极性取向或半极性取向)的衬底上逐层生长,诸如gan衬底、gaas衬底或gap衬底,或者包括但不限于以下的衬底:蓝宝石、碳化硅、硅、氧化锌、氮化硼、铝酸锂、铌酸锂、锗、氮化铝、镓酸锂、部分被取代的尖晶石或共享β

‑

lialo2结构的四元四方氧化物(quaternary tetragonal oxide)的衬底,其中可以在特定方向上切割衬底,

以暴露特定平面作为生长表面。

39.在图2a中所示的实例中,台面200a中的每一个可以包括n型掺杂半导体层220和p型掺杂半导体层240。n型掺杂半导体层220可以包括iii

‑

v族材料,诸如gan,并且可以是p掺杂的(例如,用mg、ca、zn或be掺杂)或n掺杂的(例如,用si或ge掺杂)。p型掺杂半导体层240可以包括iii

‑

v族材料,诸如gan,并且可以是p掺杂的(例如,用mg、ca、zn或be掺杂)或n掺杂的(例如,用si或ge掺杂)。一个或更多个多量子阱(mqw)层230可以生长在n型掺杂半导体层220和p型掺杂半导体层240之间,以形成有源区。mqw层230在本文还可以被称为有源层(active layer)或有源层(active layers)。在一些实施方案中,mqw层230可以是或者可以包括一个或更多个量子点(qd)或量子线(qwire)层。由mqw层230形成的有源区可以形成台面200a的发光区。mqw层330可以包括iii

‑

v族材料,诸如一个或更多个ingan层、一个或更多个alingap层和/或一个或更多个gan层,它们可以形成一个或更多个异质结构。在示例性的实施方案中,台面200a中的每一个可以包括位于掺杂有镁的p型gan层和掺杂有硅或氧的n型gan层之间的ingan层。在其他实施方案中,台面200a中的每一个可以包括位于掺杂有锌或镁的p型alingap层和掺杂有硒、硅或碲的n型alingap层之间的alingap层。

40.在一些未示出的实施方案中,台面200a可以包括衬底,该衬底可以包括例如蓝宝石衬底或gan衬底。另外的部件,诸如p触点、n触点、反射体层、导电层等可以存在,然而,为了便于说明,没有被明确示出。

41.虽然图2a呈现了横截面视图,但是台面200a的阵列可以包括台面的二维阵列,每个台面对应于led器件。如先前所提及的,每个led可以具有小于10微米的横向尺寸或直径。根据多种实施方案,从平面图或自顶向下视图来看,两个相邻的台面之间的空隙或沟槽(trench)可以在0.05微米至7微米的范围内。这支持宽范围的间距(pitch distance),即在两个相邻台面之间的中心到中心距离。阵列中包含的台面的数目可以变化。在多种实施方案中,沿第一维度的台面的数目可以是数千个,并且沿第二维度的台面的数目也可以是数千个。仅作为实例,阵列可以包括1,500个台面乘1000个台面。在另一个实例中,阵列可以包括2,000个台面乘1500个台面。

42.虽然图2a图示了与圆柱形三维形状相关联的垂直台面的实例,但是其他形状是可能的。仅作为实例,图2b图示了具有梯形轮廓的多于一个台面200b。除了每个台面的形状之外,台面200b可以与台面200a相同。其他类型的台面也是可能的,包括具有更复杂轮廓的台面,诸如形状的组合,诸如矩形轮廓和梯形轮廓的组合。如所示出的,台面200a和200b两者沿着每个台面的表面形成端面250。根据本公开内容的多种实施方案,对于不同形状和轮廓的台面,可以采用在台面的端面上使用再生长半导体层来减少非辐射复合。

43.每个台面的端面250上的表面缺陷可能有助于不期望的表面复合,其降低了每个led的效率。在端面250处,n型掺杂半导体层220和p型掺杂半导体层240的原子晶格结构结果是突然结束。在这些表面处,半导体材料的原子缺少可以附接键的邻居。这导致以未配对的价电子为特征的“悬挂键”。这些悬挂键在半导体材料的带隙内产生以其他方式将不存在的能级,这在半导体材料的表面处或在半导体材料的表面附近引起非辐射电子

‑

空穴复合。这样的复合发生的容易性的量度是表面复合速度(srv)。因此,增加的srv与非辐射复合相关联,所述非辐射复合即在不产生光子的情况下电子和空穴的复合,这降低了led的效率。

44.当每个台面的物理尺寸被减小到10微米及以下的直径,并且更具体地,被减小到5

微米及以下的直径时,非辐射复合的作用尤其显著。在较大的led器件中,例如大于50微米的直径,受表面复合影响的led区域是成比例地小的。例如,假设扩散长度为1微米,表面复合的作用可能被限制于在约1微米的台面端面内的那些区域。对于具有50微米的直径的器件,只有器件的内部的一小部分在器件表面即台面端面的1微米以内。受表面复合影响的器件的区域合计不构成mqw层230的跨度的显著部分。换句话说,在mqw层230处期望的辐射复合(其释放光子)支配对于led器件的总复合事件的百分比。相比之下,对于具有非常小的物理尺寸例如直径为2微米的器件,假设扩散长度为1微米,受表面复合影响的区域可能相当显著。在这样的情况下,大百分比的总复合发生可能受到台面端面附近非辐射表面复合作用的影响。因此,对于微led,效率下降的可能性是特别严重的。

45.为了使问题恶化,led通常不能在足以避免与高表面复合速度相关联的问题的高电流密度操作。给定材料的扩散长度可以取决于器件操作的电流密度而变化。较高的电流密度(例如,以安培/cm2为单位)与较低的表面复合速度相关联。理论上,表面复合速度可以通过增加电流密度来降低。例如,激光器件可以在高电流密度操作,例如在千安培/cm2范围内,以降低表面复合速度。相比之下,led器件通常不能在如此高的电流密度操作。而是,led器件通常在1安培/cm2‑

100安培/cm2的范围内操作。因此,在非常高的电流密度操作可能是不可行的,并且对于降低led器件中表面复合速度的可选择的策略,需求甚至更大。根据本公开内容的多种实施方案,在微led的端面上的一个或更多个再生长半导体层可以用于降低表面复合速度以及显著地提高led效率。

46.图3提供了根据本公开内容的实施方案的多于一个台面300,其具有在多于一个台面300的经蚀刻的端面上作为另外的外延层生长的再生长半导体层360。多于一个台面300可以是或者可以包括与台面200a和台面200b的材料相似的材料。例如,台面300可以各自包括n型掺杂半导体层320、p型掺杂半导体层340和在n型掺杂半导体层320和p型掺杂半导体层340之间生长的mqw层330。

47.在本实施方案中,再生长半导体层360围绕台面的整个周边覆盖p型掺杂半导体层340、mqw层330和n型掺杂半导体层320的经蚀刻的端面并且与p型掺杂半导体层340、mqw层330和n型掺杂半导体层320的经蚀刻的端面接触。例如,图3中所示的每个垂直台面可以具有大致圆柱形的形状。因此,再生长半导体层360可以完全包围每个垂直台面,使得每个台面的圆柱形形状的周边侧壁被再生长半导体层360覆盖。图3中呈现的横截面视图图示了这样的布置。在该图中所示的特定实施方案中,再生长半导体层360完全地填充相邻台面之间的空隙。

48.再生长半导体层360的生长可以使用多种技术来执行,包括例如分子束外延(mbe)、金属有机气相外延(movpe)或物理气相沉积(pvd),诸如脉冲激光沉积(pld)。然而,在台面的经蚀刻的表面上生长再生长半导体层360作为另外的外延层以降低表面复合速度的一般策略不必限于诸如mbe或movpe的特定的生长技术。

49.可以使用多种表面准备技术来去除缺陷或以其他方式改善用于外延再生长的台面端面表面的状况。这些表面准备可以包括等离子体清洁、高真空或超高真空中的热解吸、h2、nh3、磷化氢、高温时的砷化氢超压、原位cl2蚀刻等。在mocvd的情况下,表面准备技术可以包括例如在高温时的退火(例如,在约900摄氏度的范围内)。在mbe的情况下,表面准备技术可以包括,例如,(1)使用氢气h2的原位清洁和/或在超高真空(uhv)中的退火,例如,在低

于10

‑7帕斯卡的压力;以及(2)镓(ga)闪蒸或ga抛光。

50.除了清洁和去除材料,还可以重建表面。例如,可以使用采用接近再生长材料的生长温度的延长的高温步骤、用第v族材料的加压处理,以便构建有序的表面。表面重建的进展可以使用原位技术来监测,所述原位技术诸如反射高能电子衍射(rheed)或椭圆测量术(se)。还可以使用快速猝灭步骤和/或可以为随后的沉积步骤提高温度。

51.可以使用再生长掩模370来确保区域选择性生长。如图3中所示,在再生长步骤之前,再生长掩模370可以被沉积在每个台面的顶部上(在图3的底侧上示出,因为台面的取向在图中被“翻转”)。虽然在图3和随后的图中未示出,但是p触点层可以存在于p型掺杂半导体层340上。再生长掩模370可以被沉积在这样的p触点层(例如,金属层)上。根据多种实施方案,再生长掩模370可以包括诸如sio2或sin

x

的材料。再生长掩模370确保再生长半导体层360仅在选定的位置生长。在建立一个或更多个再生长半导体层360之后,可以蚀刻掉再生长掩模370。另外地或可选择地,可以使用其他技术来从不期望再生长的位置去除不想要的或过多的再生长材料。这样的去除技术可以包括平面化,例如化学机械平面化(cmp)。

52.一个或更多个再生长半导体层360的外延生长可以被设计成考虑许多因素。在一些情况下,材料可能在再生长界面处引起局部应变。在其他情况下,最初的生长层可能变得扩散。一个或更多个再生长半导体层360可以被配置成用于:

53.·

能量景观(energy landscape)(例如,紧挨着原始晶体(original crystal)的大带隙材料);

54.·

缺陷密度以减少非辐射复合;

55.·

通过掺杂的静电控制(在原始材料中引起能带弯曲,以使少数载流子不太可能传输到界面陷阱(interface trap)中);

56.·

与原始材料的晶格匹配(例如,在纤锌矿上的纤锌矿或在111闪锌矿材料上的001纤锌矿);和/或

57.·

环境敏感性(例如,防止氧化的不含al的表面,或具有al表面并在随后的步骤中被有目的地氧化的成品表面(finish))。

58.根据一些实施方案,一个或更多个再生长半导体层360可以包括宽带隙(wbg)半导体材料和/或窄带隙(ngb)半导体材料。此处,wbg指的是具有相对大的带隙的半导体材料,例如,在2电子伏(ev)

‑

4电子伏的范围内。ngb指的是具有相对小的带隙的半导体材料,例如小于1.11ev。诸如硅的常规半导体具有在1ev

‑

1.5ev的范围内的带隙。在一些实施方案中,再生长半导体层360可以包括未掺杂的半导体材料。在其他实施方案中,再生长半导体层360可以包括掺杂的半导体材料。再生长半导体层360还可以包括“轻微掺杂的”半导体材料。例如,再生长半导体层360可以具有明显低于n型掺杂半导体层320(或p型掺杂半导体层340)的掺杂剂浓度的掺杂剂浓度。在多种实施方案中,再生长半导体层360可以包括选自以下的材料:具有高于有源层的铝含量的氮化铝(aln)、氮化铝镓(algan)、砷化铝镓(algaas)、磷化铝铟(alinp)、磷化铝镓铟(algainp),或氧化锌(zno)。

59.根据本公开内容的多种实施方案,可以选择再生长半导体层360的材料以匹配或类似于led的n型掺杂半导体层320和/或p型掺杂半导体层340的材料,使得实现“完美的”或接近完美的晶体界面。类似的材料允许在经蚀刻的台面结构的再生长半导体层360和n型掺杂半导体层320之间的界面(或在再生长半导体层360和p型掺杂半导体层340之间的界面)

上延续一致的晶格结构。这样的界面使悬挂键的出现最小化,以有效地降低表面复合速度(srv)。例如,如果n型掺杂半导体层320和p型掺杂半导体层340包括iii

‑

v族半导体材料,则再生长半导体层360还可以包括iii

‑

v族半导体材料。

60.用于一个或更多个再生长半导体层360的生长条件可以不同于用于led的蚀刻台面结构的n型掺杂半导体层320和p型掺杂半导体层340的生长条件。led的n型掺杂半导体层320和p型掺杂半导体层340从衬底层(例如,图1中的衬底层110)在向上方向上生长。相比之下,再生长半导体层360主要从台面结构的端面向外在横向方向上生长。因此,用于再生长半导体层360的生长条件可以被优化以增加横向生长速率,这与相对于衬底层的向上生长速率相反。对于横向生长速率的优化可以通过控制诸如再生长半导体层360的分子组成例如材料中第iii族元素与第v族元素的比率(“iii/v族比率”)、再生长发生的温度的因素,以及通过将边角料(offcut)对齐生长平面来实现。

61.例如,为一个或更多个再生长半导体层360选择的材料可以包括第iii族

‑

asp或第iii族

‑

n材料,包括alingap、alingap(as)、alingapn、alingan、(b)alingan。这些材料还可以使用诸如si、mg、c、te等的添加剂来掺杂。在其他实例中,为一个或更多个再生长半导体层360选择的材料可以包括第ii族

‑

第vi族材料,诸如zns和zno。可以采用可以不同于典型的生长平面生长条件的生长条件来沉积材料,以便:

62.1.与材料的原始端面相比,改变暴露的端面上的相对生长速率;

63.2.提高材料的品质;和/或

64.3.构建具有受控的厚度的异质结构。

65.作为实例,gan通常可以在mocvd中在高nh3分压的情况下生长,以便促进横向生长并抑制001方向上的生长,以获得光滑膜。然而,根据本公开内容的实施方案,再生长层/膜360可以替代地在显著较低的nh3分压的情况下生长,以便在器件(例如,led器件)的侧壁上获得光滑膜,或者当在具有高纵横比的沟槽内生长时抑制桥接。这样的沟槽的实例可以是在图2a和图2b中所示的每个台面200a和台面200b之间的空隙。

66.图4描绘了在图3中描绘的特写区域380的放大版本。如所示出的,特写区域380图示了n型掺杂半导体层320、mqw层330、p型掺杂半导体层340和再生长层360的接合处。根据实施方案,再生长层360可以包括掺杂的半导体材料。此处,可以对再生长半导体层360进行掺杂,以获得与充当绝缘体的再生长半导体层360相关联的费米能级,该绝缘体防止led的短路—即防止由在p型掺杂半导体层340和n型掺杂半导体层320之间穿过再生长半导体层360的电荷流动引起的短路。

67.例如,再次参照图4,如果n型掺杂半导体层320被用于再生长半导体层360,则图4中所示的结构可以具有第一p

‑

n结和潜在地第二p

‑

n结。第一p

‑

n结是led本身;也就是,跨过p型掺杂半导体层340和mqw层330的结。第二p

‑

n结将潜在地跨过p型掺杂半导体层340和再生长半导体层360(在该实例中,其包括n型掺杂半导体材料)形成。然而,可以为多个层选择材料和掺杂水平,从而控制相应的费米能级,使得第一p

‑

n结的导通电压显著地低于第二p

‑

n结的导通电压。在电荷电势的存在下,第一p

‑

n结将导通,而第二p

‑

n结将不导通。也就是说,电荷将相对于第一p

‑

n结流动,但相对于第二p

‑

n结不流动。因此,再生长半导体层360将充当防止led的短路的绝缘体。

68.图5图示了根据本公开内容的实施方案的具有多于一个台面的台面阵列500,该台

面具有部分地填充相邻台面之间的空隙的再生长半导体层560。此处,虽然相邻台面之间的空隙仅被部分地填充,但是再生长半导体层560仍然有效地钝化台面结构的暴露的端面。再次,类似的材料可以被用于允许在经蚀刻的台面结构的再生长半导体层560和n型掺杂半导体层520之间的界面(或在再生长半导体层560和p型掺杂半导体层520之间的界面)上延续一致的晶格结构。这在台面端面处,尤其是在mqw附近,显著地减少悬挂键的出现,从而减轻表面复合的有害作用。

69.在完全地填充和部分地填充相邻台面之间的空隙之间的选择可能涉及平衡与每种方法相关联的可行性相对于性能增益(performance gain)。影响相应的方法的可行性和性能增益的因素包括台面的间距(即,相邻台面之间的中心到中心的距离)和形状。

70.图6提供了根据本公开内容的实施方案的台面600的阵列,其具有第二再生长半导体层656,该第二再生长半导体层656作为另外的外延层在第一再生长半导体层660上生长。因此,通过采用两个或更多个不同的再生长半导体层,可以实现异质再生长结构。这可以被称为再生长半导体结构的“异质结构”变型。多个再生长半导体层可以包括不同的材料。仅作为实例,参照图6,第一再生长半导体层660可以包括宽带隙(wbg)材料,并且第二再生长半导体层665可以包括窄带隙(nbg)材料。在该实例中,wbg材料可以提供绝缘功能,以防止再生长半导体层用作用于电荷在led的p型掺杂半导体层640和n型掺杂半导体层620之间移动的导管。wbg材料还可以提供钝化功能,以避免在台面端面处的悬挂键,从而显著地降低表面复合速度。

71.根据某些实施方案,第一再生长半导体层660的wbg材料可以是未掺杂的、p型掺杂的或n型掺杂的。第二再生长半导体层665的nbg材料可以是未掺杂的、p型掺杂的、n型掺杂的或被掺杂的使得该材料处于中间间隙状态(mid

‑

gap state)。也就是说,通过仔细控制费米能级,甚至可以将nbg材料设计成充当绝缘体。这样的材料的多种组合是可能的。下文列出了这样的组合的一些实例。

[0072][0073]

[0074]

在第一特定实施方案中,第一再生长半导体层660包括未掺杂的wbg材料,并且第二再生长半导体层665包括处于中间间隙状态的nbg材料。在第二特定实施方案中,第一再生长半导体层660包括未掺杂的wbg材料,并且第二再生长半导体层665包括是p型掺杂的nbg材料。在第三特定实施方案中,第一再生长半导体层660包括未掺杂的wbg材料,并且第二再生长半导体层665包括是n型掺杂的nbg材料。

[0075]

异质结构的实例可以通过首先沉积对环境敏感的未掺杂的wbg材料,随后沉积对环境不太敏感的掺杂的材料nbg作为静电控制层来形成。在特定实施方案中,可以首先沉积10nm

‑

100nm的砷化铝(alas),随后沉积10nm

‑

100nm的掺杂有硅(si)的砷化镓(gaas)。

[0076]

另外地,可以采用多种技术来实现多个再生长半导体层。一种这样的技术是δ掺杂。δ掺杂包括在生长过程中使用高掺杂剂浓度的薄层,以获得类似δ函数的掺杂概况(doping profile)。例如,δ掺杂可以通过在例如分子束外延(mbe)期间生长中断的杂质沉积来实现。

[0077]

图7描绘了如从图6放大的特写区域680。特写区域680图示了n型掺杂半导体层620、mqw层630和p型掺杂半导体层640以及在台面结构的端面上生长的第一再生长层660和第二再生长层665的接合处。横轴或“切割线”可以被设想为跨过led的n型掺杂半导体层620(或p型掺杂半导体层640)、第一再生长层660和第二再生长层665的切割。

[0078]

图8提供了图7中所示的特写区域680的半导体结构的能带图800。此处,x轴是在图7中示出的相同的横轴,其跨过不同的材料切割,诸如led的n型掺杂半导体层620(或p型掺杂半导体层640)、第一再生长半导体层660和第二再生长半导体层665。y轴是电子的能量的大小。如所示出的,led的n型掺杂半导体层620可以包括窄带隙(nbg)材料,其特征在于在该材料的导带的下边界和价带的上边界之间的窄间隙。相比之下,并且根据本公开内容的实施方案,第一再生长半导体层660可以包括宽带隙(wbg)材料,其特征在于在该材料的导带的下边界和价带的上边界之间的宽间隙。此外,根据本公开内容的实施方案,第二再生长半导体层665可以包括nbg材料,其再次特征在于在该材料的导带的下边界和价带的上边界之间的窄间隙。

[0079]

根据本公开内容的多种实施方案,对用于不同层的材料的选择允许对整个结构实现静电控制。特别地,在相邻材料之间的界面附近的导带的下边界和价带的上边界的曲率可以通过选择多各种材料来控制。

[0080]

图9图示了根据本公开内容的实施方案的结构900,结构900提供了在第一再生长半导体层960生长之前在台面端面上生长以提供光滑膜的过渡层980。过渡层980也可以被认为是再生长层中的一个。因此,在图9中,一个或更多个再生长半导体层包括过渡层980、第一再生长半导体层960和第二再生长半导体层965。第一再生长半导体层960可以具有与第一再生长半导体层660相似的构造或材料,并且第二再生长半导体层965可以具有与第二再生长半导体层665相似的构造或材料。在某些情况下,为第一再生长半导体层960选择的材料可以以低迁移率为特征。例如,第一再生长半导体层960可以包括以低迁移率为特征的、包含铝(al)的材料。也就是说,一旦沉积,材料的分子就不能行进很远,并且因此不能移动到诸如坑(crater)等的位置来填充凹陷以及平整不光滑的表面。结果,当沉积不动的再生长材料的层时,不均匀性,即不期望的表面特征,倾向于被重复。为了解决这个问题,可以在台面端面上沉积具有相对高的迁移率的过渡层980,以提供在其上可以生长第一再生长

半导体层960的光滑的表面。根据一种实施方案,过渡层980可以包括适度地窄带隙材料。

[0081]

在一种实施方案中,第一再生长半导体层960可以包括宽带隙(wbg)材料,第二再生长半导体层965可以包括窄带隙(nbg)材料,并且过渡层980可以包括具有适度地窄带隙的材料,其比第一再生长层960的wbg材料窄,但是比第二再生长层965的nbg材料宽。例如,第一再生长半导体层960可以包括铝镓氮化物(al

x

ga1‑

x

n),第二再生长半导体层965可以包括氮化镓(gan),并且过渡层980可以包括氮化铝铟镓(alingan)。在该实例中,当第一再生长层960的铝(al)含量大于特定阈值时,例如当[aln]>0.2时(即,当x>0.2时),过渡层980可能是特别有用的。

[0082]

图10提供了呈现方法1000的流程图。方法1000提供了根据本公开内容的多种实施方案的用于在配置为led的台面的经蚀刻的端面上再生长诸如再生长层360、560、660、665、960和965的半导体层的说明性步骤。方法1000的以下讨论将参照仅用于说明性目的的图11a、图11b、图12、图13a和图13b进行讨论。

[0083]

方法1000可以包括步骤1010。在步骤1010,用于形成led的台面结构的外延结构的层可以在衬底上生长。例如,该层可以包括n型掺杂半导体层,诸如n型掺杂半导体层120、220、320、520、620和920,一个或更多个mqw层,诸如mqw层130、230、330、530、630和930,以及p型掺杂半导体层,诸如p型掺杂半导体层140、240、340、540、640和940。还可以形成另外的层。例如,诸如p金属层的导电层可以形成在p型掺杂半导体层的顶部上。

[0084]

在步骤1020,可以从外延结构蚀刻台面形状的阵列,这暴露了台面端面,诸如端面250。在一些实施方案中,蚀刻工艺,诸如在感应耦合等离子体(icp)蚀刻或反应离子蚀刻(rie)系统中的干法蚀刻,可以被用于蚀刻外延结构。蚀刻可以继续穿过导电层(如果存在的话)并且穿过下面的外延层中的一个或更多个层。例如,蚀刻可以继续穿过p型掺杂半导体层,穿过一个或更多个mqw层,并且到达n型掺杂半导体层。蚀刻可以停止在n型掺杂半导体层内的某处,尽管在一些应用中,蚀刻可以继续穿过整个n型掺杂半导体层并且在衬底处停止。任选地,在一些实施方案中,方法1000可以包括用于在蚀刻之后将导电层沉积到外延结构或台面结构上的步骤。

[0085]

在步骤1030,可以在台面的顶部上形成再生长掩模的层,诸如再生长掩模370的层。例如,这些再生长掩模可以形成在导电层(如果存在的话)上。在一些实施方案中,可以存在多于一层的再生长掩模。示例性的掩模层可以包括光敏材料(例如,光致抗蚀剂)和硬掩模材料(例如,sio2或si3n4)。

[0086]

方法1000还可以包括步骤1040。步骤1040可以包括一个或更多个处理步骤,诸如例如清洁、退火和闪蒸。步骤1040可以在一个或更多个再生长半导体层在经蚀刻的外延结构上生长之前进行,以去除亚表面损伤(subsurface damage)并且清洁再生长表面。可以在暴露的台面端面上进行一个或更多个处理步骤。

[0087]

图11a和图11b图示了可以在一个或更多个再生长半导体层的生长之前进行的示例性清洁工艺。图11a和图11b图示了经历亚表面损伤去除和清洁工艺的示例性台面形状。图11a提供了在清洁工艺期间台面1110的阵列的图像1100a。图11b提供了图像1100b,图像1100b提供了来自图像1100a的两个台面1110的特写视图。如由图像1100a和1100b所图示的,每个台面1110包括其上形成有端面1150的经蚀刻的外延层1120。

[0088]

由图像1110a和1110b图示的清洁工艺是改进的湿法蚀刻循环,其去除台面表面上

的亚表面损伤。清洁工艺为一个或更多个再生长半导体层的后续生长提供光滑的台面表面。使用湿法蚀刻循环、缓冲氧化物蚀刻(buffered oxide etch)(boe)或类似循环来清洁台面表面,在再生长之前去除表面上的氧化物或含氧层,并且减少异质界面处的表面陷阱。在一些实施方案中,湿法蚀刻工艺可以包括数字蚀刻,其中从暴露的台面侧壁中可控地去除约0.5nm

‑

20nm的半导体材料。由图像1110a和1110b图示的清洁工艺示出了在通过boe工艺对台面表面进行软回蚀(soft backetch)和清洁之后的台面端面。boe使用湿蚀刻剂,诸如缓冲蚀刻溶液,以从台面表面可控地去除材料。例如,清洁工艺可以包括20个湿法蚀刻循环。在湿法蚀刻循环期间,台面的表面可以被暴露于表面氧化,以形成覆盖经蚀刻的台面1110的表面的氧化物层。氧化物层可以小于2nm,并且在图像1110a和1110b中不可见。在台面表面的氧化之后,可以通过湿法蚀刻或气体蚀刻来去除氧化物连同任何亚表面损伤。

[0089]

如图像1100b中所示,生长掩模1170可以被用于在清洁工艺期间保护台面结构免受不期望的蚀刻。在一些实施方案中,生长掩模1170可以与在步骤1030应用的再生长掩模相同。在其他实施方案中,生长掩模1170可以是与在步骤1030应用的再生长掩模不同的掩模。如所示出的,图像1100a和1100b中使用的清洁工艺可以导致每个台面1110的大部分光滑的垂直侧壁。在一些情况下,湿法蚀刻工艺可以导致在硬掩模1170下的一些底切1175,例如,sio2或si3n4。

[0090]

在一些实施方案中,在步骤1040的一个或更多个处理还可以包括退火工艺。图12提供了描绘已经经历退火工艺的台面1210的阵列的图像1200。退火工艺可以在再生长层在外延结构上的生长之前进行。图像1200中描绘的台面1210已经在movpe反应器中经历原位再结晶工艺。这是在高温进行的,诸如例如在300℃和600℃之间。在通过pecvd、icpecvd、ald或溅射应用ii

‑

vi族或iii

‑

v族再生长层或其他层如sin、sio2、hfo、aln、al2o3、tio2之前,该工艺使台面表面再结晶并且减少表面陷阱。

[0091]

接着,方法1000可以包括步骤1050。在步骤1050,可以在台面端面上外延生长一个或更多个再生长半导体层,诸如再生长层360、560、660、665、960或965。图13a和图13b提供了具有在台面端面上外延生长的再生长层的台面阵列。图13a提供了描绘圆柱形台面1310a的图像1300a,圆柱形台面1310a具有围绕台面结构的表面生长的再生长层1360a。类似地,图13b提供了描绘矩形台面1310b的图像1300b,矩形台面1310b具有围绕台面结构的表面生长的再生长层1360b。再生长层1360a和1360b包括alinp,并且通过movpe形成。

[0092]

在台面结构上生长一个或更多个再生长半导体层之后,方法1000可以包括步骤1060。在步骤1060,可以去除再生长掩模。

[0093]

图14a

‑

图19提供了在外延结构上生长再生长层之前已经经历boe清洁工艺的台面结构相对于没有经历boe清洁工艺的台面结构的示例性比较。从图14a和图14b开始,图像1400a和1400b描绘了台面结构1410。如由图像1400a所示的,台面结构1410包括外延结构。外延结构包括n型掺杂半导体层1420、mqw层1430和p型掺杂半导体层1440。n型掺杂半导体层1420和p型掺杂半导体层1440可以是或者可以包括富al的包覆层,例如具有大于或等于40%的铝含量的alinp、algainp或algaas。图像1400b提供了台面结构1410的侧壁的特写视图。如由图像1400b所示的,再生长层1460已经生长在台面结构1410的侧壁上。再生长层1460可以包括znse。在再生长层1460的生长之前,台面结构1410经历uhv h清洁。然而,台面结构1410没有使用boe清洁工艺进行清洁,如上文描述的。

[0094]

图15a和图15b图示了在再生长层的生长之前没有充分去除亚表面损伤和清洁台面表面的影响。图15a提供了来自图14b的在台面侧壁的再生长层1460和外延层1520之间的界面1490的特写视图。外延层1520可以包括n型掺杂半导体层1420、mqw层1430和p型掺杂半导体层1440。如由界面1490所示的,薄氧化物层1585可以存在于外延层1520和再生长层1460之间。薄氧化物层1585可以例如在台面蚀刻和例如在空气中的晶片处理之后留下。不同的垂直堆叠的外延层1520在台面端面处可以具有不同的材料组成,导致不同的氧化物。例如,对于包括algaas层、algainp层、gainp层、gaas层的台面结构,gao和ino可以在台面表面处形成,其具有小于表面处的alo的结合能。通过例如湿法蚀刻工艺、在mbe室中采用h2的uhv真空清洁、软背溅射工艺(soft back sputter process)及类似工艺,gao和ino可以更容易被侵蚀和去除。主要问题可能是在不损坏台面端面的情况下去除用于富含al的外延层的alo基化合物。

[0095]

薄氧化物层1585可以在台面蚀刻工艺之后从前面的工艺步骤中留下。如果外延层1520包括较高浓度的铝,如它们在此处这样,则薄氧化物层1585可以在外延层1520上形成。由于在外延层1520中不同材料层之间的组成差异,不同类型的氧化物可以在侧壁处形成。因此,在一些实施方案中,不同的清洁工艺可以完全地去除在某些层(例如富含ga的层,如mqw层)处的氧化物(例如,gao或ino),诸如薄氧化物层1585,但是不去除在其他层诸如例如富含al的p型或n型包覆层处的其他氧化物(例如,alo)。还存在较大的氧化物层1580。氧化物层1580可以是在形成再生长层1460之后另外的al2o3的介电层沉积。氧化物层1580与再生长层1460接触。

[0096]

图15b、图15c和图15d提供了在再生长层1460和外延层1520之间的界面1490的元素布局的图像。元素布局示出了元素跨过材料的深度的存在。此处,图15b、图15c和图15d的图像示出了氧、锌和硒跨过界面1490的深度的元素分布。再生长层1460包括znse,因此在图15c和图15d中示出的锌和硒的存在指示再生长层1460的存在。图15b中提供的元素分布指示在图像1500b中描绘的界面1490处薄氧化物层1585和氧化物层1580的存在。通过对齐图15b、图15c和图15d,在外延层1520和再生长层1460之间薄氧化物层1585的存在是明显的。

[0097]

图16提供了贯穿图像1500中描绘的界面1490的深度的元素分布的图1600。图1600的x轴是从外延层1520延伸到再生长层1460的距离。y轴提供了贯穿深度的每种元素的原子百分比。如由图1600所示的,外延层1520在约0nm和30nm之间延伸到界面1490中。这由这些深度处的铝、铟和磷酸盐的存在来指示,这些深度对应于作为外延层1520的一部分的alinp包覆层。再生长层1460在界面1490中在约35nm和55nm之间延伸。这由对应于znse再生长层1460的这些深度处的锌和硒的存在来指示。如由在27nm和30nm之间的氧的增加所指示的,薄氧化物层1585在外延层1520和再生长层1460之间存在。氧化物层1580的存在通过在50nm处开始的氧的增加来指示。薄氧化物层1585的存在可能是不期望的,因为它可能导致非晶或多晶的过度生长,其具有比再生长层1460的良好晶体材料品质更多的载流子的陷阱。

[0098]

图17提供了在应用再生长层之前已经经历boe清洁工艺的台面结构1710的图像1700。在再生长层1760的生长之前,台面结构1710还经历uhv h清洁。如所示的,台面结构1710包括外延结构。外延结构包括n型掺杂半导体层1720、mqw层1730和p型掺杂半导体层1740。图18a提供了界面1790的特写视图。界面1790示出了在外延层1820和再生长层1760之间的界面。再生长层1760包括znse。如由界面1790所示的,在外延层1820和再生长层1760之

间不存在薄氧化物层。只有氧化物层1880在界面1790处与再生长层1760接触。

[0099]

图18b、图18c和图18d提供了在界面1790处的氧、锌和硒的元素分布。图18b描绘了氧的存在,从而指示在界面1790处的氧化物层1880的存在。图18c和图18d分别描绘了锌和硒的存在,从而指示在界面1790处的再生长层1760的存在。与图15b不同,在外延层1820和再生长层1760之间不存在薄氧化物层。

[0100]

图19中提供的图1900还图示了在外延层1820和再生长层1760之间薄氧化物层的缺少。图1900类似于图1600,因为它示出了跨过界面1790的深度的元素分布。类似于图1600,外延层1820在约0nm和30nm之间通过铝、铟和磷酸盐的存在被指示。接着,再生长层1760在30nm和50nm之间通过锌和硒的存在被指示。如由图1900所示的,在30nm和35nm之间不存在氧的增加,这指示在外延层1820和再生长层1760之间缺少薄氧化物层。氧化物层1880的存在通过氧的增加在55nm处开始被指示。

[0101]

上文讨论的方法、系统和装置是实例。多种实施方案可以酌情省略、替换或添加多种过程或部件。例如,在可选择的配置中,所描述的方法可以以不同于所描述的顺序来执行,和/或可以添加、省略和/或组合多个阶段。此外,关于某些实施方案描述的特征可以在多种其他实施方案中被组合。实施方案的不同方面和要素可以以相似的方式被组合。此外,技术不断发展,并且因此许多要素是实例,其不将本公开内容的范围限制于那些具体实例。

[0102]

在描述中给出了具体细节,以提供对实施方案的透彻理解。然而,可以在没有这些具体细节的情况下实施实施方案。例如,为了避免模糊实施方案,熟知的电路、过程、系统、结构和技术已经被示出而没有不必要的细节。此描述仅提供示例性的实施方案,并且不意图限制本发明的范围、适用性或配置。而是,实施方案的前述描述将为本领域技术人员提供用于实现多种实施方案的使能描述(enabling description)。在不脱离本公开内容的精神和范围的情况下,可以在要素的功能和布置方面进行多种改变。

[0103]

此外,一些实施方案被描述为过程,过程被描绘为流程图或框图。尽管每一个都可以将操作描述为顺序过程,但是许多操作可以并行或并发地被执行。此外,操作的顺序可以被重新排列。过程可以具有图中未包括的附加步骤。此外,可以通过硬件、软件、固件、中间件、微代码、硬件描述语言或其任何组合来实现方法的实施方案。当以软件、固件、中间件或微代码实现时,执行相关联的任务的程序代码或代码段可以被存储在诸如存储介质的计算机可读介质中。处理器可以执行相关联的任务。

[0104]

对于本领域技术人员来说,将明显的是,可以根据特定的要求进行实质性的变化。例如,还可以使用定制的硬件或专用的硬件,和/或可以以硬件、软件(包括便携式软件,诸如小程序(applet)等)或者两者来实现特定的要素。此外,可以采用到其他计算装置诸如网络输入/输出装置的连接。

[0105]

参考附图,可以包括存储器的部件可以包括非暂时性机器可读介质。术语“机器可读介质”和“计算机可读介质”可以指参与提供使机器以特定方式操作的数据的任何存储介质。在上文提供的实施方案中,多种机器可读介质可以涉及向处理单元和/或其他装置提供指令/代码以用于执行。另外地或可选择地,机器可读介质可以用于存储和/或携带这样的指令/代码。在许多实施方式中,计算机可读介质是物理存储介质和/或有形存储介质。这样的介质可以采取多种形式,包括但不限于非易失性介质、易失性介质和传输介质。计算机可读介质的常见形式包括例如磁介质和/或光学介质(诸如光盘(cd)或数字多功能盘(dvd))、

穿孔卡、纸带、具有孔图案的任何其他物理介质、ram、可编程只读存储器(prom)、可擦除可编程只读存储器(eprom)、闪存

‑

eprom、任何其他存储器芯片或盒、如下文描述的载波、或计算机可以从中读取指令和/或代码的任何其他介质。计算机程序产品可以包括代码和/或机器可执行指令,其可以表示过程、函数、子程序、程序、例程、应用(app)、子例程、模块、软件包、类、或指令、数据结构或程序语句的任何组合。

[0106]

本领域技术人员将理解,用于传送本文描述的消息的信息和信号可以使用多种不同的技术和技艺中的任何一种来表示。例如,在整个上文的描述中可以引用的数据、指令、命令、信息、信号、比特、符号和码片(chip)可以由电压、电流、电磁波、磁场或粒子、光场或粒子、或其任何组合来表示。

[0107]

如本文使用的术语“和”以及“或”可以包括多种含义,这些含义还被预期至少部分地取决于使用这样的术语的上下文。通常,“或”如果用于关联列表,诸如a、b或c,则意图表示a、b和c(此处以包含的意义使用)以及a、b或c(此处以排他的意义使用)。此外,如本文使用的术语“一个或更多个”可以用来以单数形式描述任何特征、结构或特性,或者可以用来描述特征、结构或特性的某种组合。然而,应当注意,这仅仅是说明性的实例,并且所要求保护的主题不限于该实例。此外,术语“......中的至少一个(at least one of)”如果用于关联列表,诸如a、b或c,则可以被解释为表示a、b和/或c的任何组合,诸如a、ab、ac、bc、aa、abc、aab、aabbccc等。

[0108]

此外,虽然已经使用硬件和软件的特定组合描述了某些实施方案,但是应当认识到,硬件和软件的其他组合也是可能的。某些实施方案可以仅以硬件实现,或者仅以软件实现,或者使用它们的组合来实现。在一个实例中,可以用包含计算机程序代码或指令的计算机程序产品来实现软件,所述计算机程序代码或指令可由一个或更多个处理器执行,用于执行在本公开内容中描述的任何或所有步骤、操作或过程,其中计算机程序可以被存储在非暂时性计算机可读介质上。本文描述的多种过程可以在相同的处理器上或者以任何组合在不同的处理器上实现。

[0109]

在装置、系统、部件或模块被描述为被配置成执行某些操作或功能的情况下,可以例如通过设计执行操作的电子电路、通过对可编程电子电路(诸如微处理器)进行编程以(诸如通过执行计算机指令或代码)执行操作、或者被编程为执行存储在非暂时性存储器介质上的代码或指令的处理器或核、或者它们的任何组合来完成这样的配置。过程可以使用多种技术(包括但不限于用于过程间通信的常规技术)进行通信,并且不同的过程对可以使用不同的技术,或者同一对过程可以在不同的时间使用不同的技术。

[0110]

因此,说明书和附图应被视为说明性的而不是限制性的。然而,将明显的是,在不脱离如在权利要求中阐述的更广泛的精神和范围的情况下,可以对其进行添加、删减、删除以及其他修改和改变。因此,尽管已经描述了具体实施方案,但是这些实施方案并不意图是限制性的。多种修改和等同物都在所附权利要求的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。