1.各种实施例一般地涉及电子组件、封装和制造电子组件的方法。

背景技术:

2.封装可以被指代为包封的电子组件,具有延伸出包封物的电连接并且可安装到电子外围设备,例如可安装在印刷电路板上。

3.封装成本是对于工业而言的重要驱动力。与此相关的是性能、尺寸和可靠性。不同的封装解决方案是多样的,并且必须应对应用的需要。

技术实现要素:

4.可能存在对于提供如下可能性的需要:在关注于降低处理复杂性的情况下制造电子组件,同时保持高的器件可靠性。

5.根据示例性实施例,提供了一种电子组件,其包括模制层和半导体管芯,半导体管芯包括低欧姆第一部分和高欧姆第二部分,其中第一部分具有有源区域并且第二部分被布置在模制层上。

6.根据另一示例性实施例,提供了一种封装,其包括:电子组件,电子组件包括电介质层和半导体管芯,半导体管芯包括低欧姆第一部分和高欧姆第二部分,其中第一部分具有有源区域并且第二部分被布置在电介质层上;以及包封物,其包封电子组件的至少一部分。

7.根据又一示例性实施例,提供了一种制造电子组件的方法,其中方法包括:提供包括多个半导体管芯的半导体晶片,每个半导体管芯包括低欧姆第一部分和高欧姆第二部分,其中每个第一部分具有有源区域;将第二部分布置在模制层上;以及此后将模制层上的半导体晶片分离成多个分离的电子组件,每个电子组件包括至少一个半导体管芯和模制层的部分。

8.根据示例性实施例,可以提供电子组件和对应的封装,其中半导体管芯被配备有低(或较低)欧姆部分和高(或较高)欧姆部分。有利地,高欧姆部分可以被(优选地直接)与(优选地实质上平面的或平坦的)电介质(优选地模制)层连接,而具有有源芯片区域的低欧姆部分可以背对所述电介质层。利用这种配置,由于半导体管芯和电介质层这两者都可以被制造得非常薄,因此可以制造高度紧凑的电子组件和封装。由于(多个)集成电路元件可以仅被布置在低欧姆部分中,因此在封装的电子组件的操作期间的欧姆损耗也可以是低的。高欧姆部分可以在制造期间提供支承,可以简化处理并且可以在完成电子组件或封装的制造之前被通过薄化而部分地移除。同时,在电介质层可以用作为支承的同时,有源区域的简单的电连接是可能的。通过使用简单的电介质层(特别是模制层)作为支承,可以显著地减少制造电子组件以及使电子组件单体化的付出。更进一步地,可以利用这样的构思实现可靠的器件到器件隔离以及改进的高频性能。

9.进一步的示例性实施例的描述下面,将解释电子组件、封装和方法的进一步的示例性实施例。

10.在本技术的上下文中,术语“电子组件”可以特别是涵盖半导体管芯(特别是功率半导体管芯)、有源电子器件(诸如晶体管)、无源电子器件(诸如电容或电感或欧姆电阻)、传感器(诸如麦克风、光传感器或气体传感器)、基于半导体的发光器件(诸如发光二极管(led)或激光器)、致动器(例如扬声器)以及微机电系统(mems)。特别是,电子组件可以包括在其表面部分中具有至少一个集成电路元件(诸如二极管或晶体管)的半导体管芯。

11.在本技术的上下文中,术语“半导体管芯”可以特别地指代半导体材料的裸片,其还可以包括半导体材料中的电绝缘结构和导电结构,并且其可以具有单片集成在半导体材料中的至少一个集成电路元件。因此,半导体管芯可以是其上制备有给定的功能电路的小块的半导体材料。这样的集成电路可以是例如使用诸如光刻的处理在单个半导体晶片上大批量地生产的。经处理的半导体晶片然后可以被分离成许多片,每片包含电路的一个拷贝。这些片中的每个可以被指代为半导体管芯。根据示例性实施例实现的半导体管芯可以是采用硅技术、氮化镓技术、碳化硅技术等形成的。

12.在本技术的上下文中,术语“低欧姆半导体部分”和“高欧姆半导体部分”可以特别地指代半导体管芯的具有不同的电导率值的不同的集成连接的部分。更具体地,与高欧姆半导体部分相比低欧姆半导体部分可以具有更高的电导率值。例如,低欧姆半导体部分可以是晶体半导体(特别是硅)部分,而高欧姆半导体部分可以是高电阻半导体(特别是硅)部分。在一个实施例中,低欧姆半导体部分和高欧姆半导体部分可以被在其之间的电介质层分离。在这样的实施例中,半导体管芯可以被体现为soi(绝缘体上硅)管芯。

13.在本技术的上下文中,术语“有源区域”可以特别地指代半导体管芯的其中单片集成有至少一个集成电路元件(例如晶体管、二极管等)的区段。

14.在本技术的上下文中,术语“电介质层”可以特别地指代由电绝缘材料制成的平坦的或片状的本体。例如,这样的电介质材料可以是模制化合物或诸如聚合物的另外的电介质。

15.在本技术的上下文中,术语“模制层”可以特别地指代由模制物或模制化合物材料制成的平坦的或片状的本体。例如,模制物可以包括树脂或者由树脂构成,树脂例如为环氧树脂。还可能的是模制物包括这样的树脂,以及附加地包括在树脂基质中的填充物颗粒。

16.在本技术的上下文中,术语“封装”可以特别地指代可以包括优选地安装在载体上一个或多个电子组件的电子器件(其中所述载体可以包括如下或者由如下构成:单个部分、经由包封或其它封装组件接合的多个部分、或者载体的子组装)。封装的所述(多个)构成部分可以是至少部分地由包封物包封的。可选地,一个或多个导电互连本体(诸如接合布线和/或夹具)可以被实现在封装中,例如用于将电子组件与载体电耦合。

17.在本技术的上下文中,术语“包封物”可以特别地指代围绕至少一部分电子组件(以及可选地围绕至少一部分载体)以提供机械保护、电绝缘以及可选地贡献于工作期间的热移除的实质上电绝缘的材料。特别是,所述包封物可以是模制化合物。模制化合物可以包括可流动并且可硬化材料的基质以及嵌入在其中的填充物颗粒。例如,填充物颗粒可以被用于调整模制组件的性质,特别是用于提高热导率。

18.在封装的实施例中,电介质层是模制层(特别是模制箔)或可固化的层(特别是温

度可固化的层)。

19.在实施例中,模制层包括模制箔或者由模制箔构成。当被体现为箔时,模制层可以是可弯曲的,并且可以仅在非常小的程度上贡献于电子组件和封装的厚度。例如,模制箔可以具有在从2μm到200μm的范围内的厚度。

20.在实施例中,模制层包括模制板或者由模制板构成。模制板可以提供更大的坚固性,但是也可能具有更大的厚度。例如,模制板可以是刚性的,并且可以具有在从250μm到1 mm的范围内的厚度。

21.在实施例中,模制层是双模制层(即具有恰好两层模制材料,其可以是互连的),例如可以包括模制板和模制箔或者由模制板和模制箔构成。双模制层的对应材料选择可以允许精细调节封装中的电子组件的性质。

22.在实施例中,模制层包括树脂基质(其特别是由环氧树脂制成)以及在树脂基质中的填充物颗粒(其特别是由金属氧化物制成)。基质材料可以是可固化的。填充物颗粒可以被用于调整模制材料的物理性质(诸如热导率、电绝缘性、热膨胀系数、高频性质等)。

23.在实施例中,有源区域具有至少一个集成电路元件。一个或多个电路元件可以被单片集成在半导体管芯(优选地,半导体管芯的低欧姆部分)中。后道工序(beol)结构的至少一个导电焊盘可以是与有源区域的至少一个集成电路元件耦合的暴露的导电区域,用于将电子组件连接到外部电子外围设备。

24.在实施例中,电子组件包括在模制层和半导体管芯之间的粘接层。所述粘接层可以抑制电子组件和封装的不合期望的剥离。

25.在实施例中,有源区域具有小于1μm的厚度,特别是具有在从50 nm到500 nm的范围内的厚度,更特别地具有在从100 nm到200 nm的范围内的厚度。因此,通过半导体技术处理的部分体积可以非常小。

26.在实施例中,半导体管芯实质上没有未被处理的半导体材料。这可以致使电子组件和封装高度紧凑,因为半导体管芯的整个厚度上的实质上全部的半导体材料可以贡献于形成功能集成电路元件。

27.在另一实施例中,半导体管芯具有未经处理的半导体材料,其具有小于150μm、特别是小于30μm的厚度。在这样的小的厚度的情况下,电子组件和封装的配置可以是仍然非常紧凑的。然而,保持一些未经处理的半导体材料可以避免在生产期间在晶片的薄化期间无意地损坏半导体管芯的有源区域的危险。

28.在实施例中,半导体管芯具有在从1μm到200μm的范围内、特别是在从10μm到40μm的范围内、更特别地在从20μm到30μm的范围内的厚度。特别是,可以使用非常薄的半导体管芯,例如具有小于50μm、优选地在从20μm到30μm的范围内的厚度的半导体管芯。如果厚度甚至显著小于20μm,则热移除可能变得更加困难。如果厚度变得显著大于30μm,则半导体材料(特别是硅材料)的电气影响可能变得更大。

29.在实施例中,半导体管芯的高欧姆第二部分由高电阻半导体材料——特别是具有至少500ωcm、特别是至少1000ωcm的电阻率的半导体材料——制成。有利地,可以以低的付出提供这样的高欧姆半导体。因此,更昂贵的低欧姆半导体部分(例如由晶体硅制成)可以被实质上限制于有源区域的延伸以将制造付出保持得低。无论如何,实现支承功能并且简化半导体晶片的处理的高欧姆半导体材料可以稍后被通过薄化而部分地移除,从而其更

高的电阻不损害封装的电子组件作为整体的性能和可靠性。例如,低欧姆半导体部分可以具有小于100ωcm、特别是小于10ωcm的电阻率。例如,低欧姆半导体部分的电阻率可以在从1ωcm到100ωcm的范围内,特别是在从1ωcm到10ωcm的范围内。

30.在实施例中,半导体管芯是绝缘体上硅(soi)管芯。绝缘体上硅(soi)技术可以被用于在分层的硅

‑

绝缘体

‑

硅衬底中制备硅半导体器件,以减少在器件内的寄生电容,由此改进性能。基于soi的半导体管芯具有特定的性质:硅结可以被布置在诸如二氧化硅的电绝缘体之上。替换地,用于制造根据示例性实施例的电子组件和封装的基底的电绝缘体可以是由诸如蓝宝石的另外的电介质材料制成的,从而根据这样的实施例的半导体管芯可以被指代为蓝宝石上硅管芯。可以根据所意图的应用作出对适当的绝缘体的选择。例如,对于射频(rf)应用而言蓝宝石可以是合适的选择。

31.在实施例中,电子组件包括在半导体管芯的主表面上的导电的后道工序(beol)结构,半导体管芯的该主表面与在模制层上的半导体管芯的另一主表面相对。beol可以是集成电路制造的一部分,其中各个集成电路元件(诸如晶体管、电容器等)与晶片上的布线(即金属化层(例如使用铜、铝等))互连。beol可以被认为是在晶片上沉积第一金属层时开始。因此,beol结构可以被直接连接到半导体管芯的有源区域。所提到的beol结构可以包括由如下构成的组中的至少之一:一个或多个焊盘、接触、绝缘层、金属层级、以及用于管芯到封装连接的接合部位。半导体管芯可以被夹在一侧上的电介质层或模制层与另一侧上的beol结构之间。

32.在实施例中,电子组件包括突出超过beol结构的至少一个导电突出部。这样的突出部可以包括例如柱、桩、凸块、球等,其突出超过beol结构的平坦基底。这样的突出部可以被配置用于在形成封装的基础(其可以具有用于利用其与电子组件间的焊料连接承载电子组件的载体)时或者在被安装(并且焊接)在诸如印刷电路板的安装基底上时促进电子组件的焊料连接。在一个实施例中,突出部可以具有低欧姆基底结构,低欧姆基底结构在其顶部上具有焊料帽。

33.在实施例中,半导体管芯是有源半导体管芯,特别是高频半导体管芯。被配置用于提供功率增益的半导体管芯可以是有源半导体管芯。这样的有源半导体管芯可以将功率注入到其所属于的电路,并且可以控制电路内的电流。用于有源半导体管芯的示例是晶体管管芯、整流器管芯或晶闸管管芯。就高频技术而言,半导体管芯例如可以被配置为在从大约20 khz到大约300 ghz的频率范围内工作。

34.在实施例中,电子组件或封装中的模制层已经完全固化,并且由在未固化状态下具有粘接性质的材料制成。例如,固化可以指代模制层材料的聚合和/或交联,更具体地指代其树脂(例如环氧树脂)的聚合和/或交联。在固化之前,模制层可以是粘性的,并且由此可以合适地附接到半导体管芯或半导体晶片。在固化(其可以是例如通过向模制层供给热能而触发的)之后,聚合或交联可以造成在模制层和(多个)半导体管芯之间形成本征连接,其中在固化时可以失去在模制层的外表面处的粘性性质。

35.在实施例中,封装包括载体,载体被包封物部分地包封并且与电子组件电连接。在本技术的上下文中,术语“载体”可以特别地指代支承结构(其可以是至少部分地导电的),其用作为用于要被安装在其上的一个或多个电子组件的机械支承,并且其还可以贡献于在(多个)管芯和封装的外围设备之间的电互连。换句话说,载体可以实现机械支承功能和电

连接功能。载体可以包括如下或者由如下构成:单个部件、经由包封或其它封装组件接合的多个部件、或者载体的子组件。

36.例如,载体可以是引线框类型的载体,即结构化的金属板。当载体形成引线框的一部分时,其可以包括管芯焊盘和一个或多个引线。

37.在另一实施例中,载体包括由中心电绝缘和导热层(诸如陶瓷层)构成的堆叠,该中心电绝缘和导热层在两个相对的主表面上被由相应的导电层(诸如铜层或铝层,其中相应的导电层可以是连续的或图案化的层)覆盖。特别是,载体也可以被体现为直接铜接合(dcb)衬底或直接铝接合(dab)衬底。

38.特别是,上面描述的在半导体管芯的主表面上的beol结构可以被电连接到至少部分地导电的载体。因此,beol结构和载体之间的连接可以同时提供在电子组件与载体之间的机械连接以及其间的电耦合这两者。

39.在实施例中,包封物是模制化合物,特别是具有与电介质层不同的不同材料性质的模制化合物。通过选择用于电子组件的模制层和封装的包封物的不同的材料,可以针对两个模制结构单独地调整所要求的性质的特定适配(在组件级上的处理期间支承半导体管芯,在封装级上可靠地机械保护和电解耦)。

40.模制化合物可以包括可流动的和可硬化的材料的基质以及嵌入在其中的填充物颗粒。例如,填充物颗粒可以被用于调整模制组件的性质,特别是用于提高热导率。例如,模制可以是通过注入模制、转印模制或加压模制完成的。

41.在实施例中,所述包封可以是在与晶片分离之后通过包封物进行的相应的电子组件的过模制。然而,用于从封装的外部接入被包封的半导体管芯的一个或多个电接触可以保持被暴露。这样的接触可以涉及如下的导电载体:在该载体上电子组件可以被安装在封装的内部中。

42.在实施例中,方法包括在进行布置之前将载体晶片暂时地连接到半导体晶片,以及在分离之前将载体晶片从半导体晶片移除。例如,这样的暂时的载体晶片可以是可以被多次重复使用的玻璃板。

43.在实施例中,方法包括在将半导体晶片连接在模制层上之前,特别是通过至少移除或排它地移除第二部分的材料来薄化半导体晶片。例如,薄化可以是通过研磨以机械方式实现的、通过激光烧蚀和/或以化学方式(例如通过湿法蚀刻)实现的。还可能的是可以组合上面提到的和/或其它的薄化技术中的至少两种技术。

44.在实施例中,方法包括在进行布置之前或之后将切分箔暂时地连接到模制层,并且在分离期间或之后将切分箔从电子组件移除。切分箔或切分带可以是在晶片切分——即在晶片级上的处理之后分离半导体材料的片——期间使用的箔或带。切分箔可以在分离或单体化处理期间将半导体管芯保持在一起。出于稳定性的目的,切分箔可以被安装到薄框架(例如由金属制成)。然后可以例如通过拾取和放置工具将所分离的半导体管芯从切分带移除。然后可以进一步处理在其一侧上具有模制层的被单体化的半导体管芯,例如,其可以被组装到安装基底和/或可以是被依照封装来包封的。

45.在实施例中,方法包括将半导体晶片的主表面上的导电后道工序(beol)结构上的导电突出部嵌入在暂时的(即稍后被移除的)粘接结构中,该粘接结构特别是将半导体晶片与载体晶片连接。暂时的粘接结构可以暂时地将载体晶片与半导体晶片连接,并且可以是

足够软的以暂时地容纳突出部而没有损坏的风险。可以在单体化之前将暂时的粘接结构从电子组件上移除,优选地没有残留物保留在电子组件处。

46.在实施例中,方法包括通过由机械锯切、激光锯切和蚀刻构成的组中的至少之一来进行分离。这些分离技术也可以被组合。

47.在实施例中,半导体管芯被配置为功率半导体管芯。因此,半导体管芯可以被用于例如汽车领域中的功率应用,并且可以例如具有至少一个集成的绝缘栅双极晶体管(igbt)和/或至少一个另一类型的晶体管(诸如mosfet、jfet等)和/或至少一个集成的二极管。这样的集成电路元件可以是例如采用硅技术制成的或者是基于宽带隙半导体(诸如碳化硅或氮化镓)制成的。半导体功率管芯或芯片可以包括一个或多个场效应晶体管、二极管、逆变器电路、半桥、全桥、驱动器、逻辑电路、进一步的器件等。

48.作为形成半导体管芯的基础的衬底或晶片,可以使用半导体衬底,优选地使用硅衬底。还可能的是实现锗衬底或iii

‑

v族半导体材料。例如,示例性实施例可以是采用氮化镓或碳化硅技术实现的。

49.更进一步地,示例性实施例可以利用标准的半导体处理技术,诸如适当的蚀刻技术(包括各向同性蚀刻技术和各向异性蚀刻技术,特别是等离子体蚀刻、干法蚀刻、湿法蚀刻)、图案化技术(其可能涉及光刻掩模)、沉积技术(诸如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、溅射等)。

50.根据结合随附附图的下面的描述和所附权利要求,上面的以及其它的目的、特征和优点将变得显而易见,在附图中,同样的部分或要素由同样的参考标号指代。

附图说明

51.被包括以提供对示例性实施例的进一步理解并且构成说明书的一部分的随附附图图示了示例性的实施例。

52.在附图中:图1图示根据示例性实施例的电子组件的横截面视图。

53.图2至图9图示在执行根据示例性实施例的在晶片级上制造电子组件的方法期间获得的结构的横截面视图。

54.图10图示根据示例性实施例的封装的横截面视图。

55.图11图示根据另一示例性实施例的封装的横截面视图。

具体实施方式

56.附图中的图示是示意性的并且不是按比例的。

57.在将参照各图更详细地描述示例性实施例之前,将基于已经开发的示例性实施例来总结一些一般考虑。

58.根据示例性实施例,提供了电子组件、封装和制造半导体组件的方法,其可以优选地基于薄晶片技术来操作。半导体组件的有源区域的(多个)单片集成的电路元件可以被布置在半导体晶片或管芯的低欧姆部分中。低欧姆硅部分可以被放置在高欧姆硅部分上。高欧姆硅(例如具有大约1k ohmcm的比电阻)在非常高的频率下(例如在ghz范围内)是极为有利的,其中高欧姆硅可以是本质上透明的。

59.线性和低损耗是高性能rf(射频)电路中的重要性能因素。

60.然而,有源集成电路元件和无源集成电路元件以及这些电路元件和迹线与半导体衬底的电容相互作用和电感相互作用可能造成性能限制。因此,一些组件要求移除或显著地薄化衬底。为此目的,可以使用载体技术来稳定薄晶片和芯片。

61.根据示例性实施例,昂贵的载体可以是不必要的,并且因此可以实现制造付出的减少。特别是,根据示例性实施例的电子组件或封装可以包括半导体管芯(例如有源rf半导体管芯),其在背部尺寸上具有少的或薄的未经处理的高欧姆硅,或者甚至实质上没有这样的硅。例如,对应的裸半导体管芯可以被配备有后道工序(beol)金属化结构,其具有到顶部侧的接触连接。此外,可以是可能的是在beol结构上提供凸块或柱(例如由铜制成)或球。

62.示例性实施例还可以在电子组件的背部侧处提供电介质(特别是模制)层或背部侧保护膜。这样的电介质层可以稳定电子组件或作为其预制件的晶片。该电介质层或膜可以优选地由具有粘接性质的类似模制的材料制成。

63.这样的结构可以被有利地使用在简单的并且成本有效的分离处理中,因为在此只需要隔离具有薄的模制膜的薄器件。因此对于单体化而言可以使用简单的分离方法。

64.有利地,示例性实施例可以使厚的永久玻璃板不必要,因为其例如可以足以将模制层或膜直接地或间接地附接到半导体管芯。

65.因此,示例性实施例可以使用半导体管芯和模制层的复合物,模制层作为隔离载体起作用。省略由玻璃、硅或陶瓷制成的常规的大体积载体晶片的机会可以减少电子组件的尺寸和制造付出。特别是,用于半导体管芯或芯片的单体化的高的锯切付出也可以是不必要的。这可以允许实现改进的器件到器件隔离和改进的rf性能,而且同时保持制造处理简单。

66.示例性实施例可以提供一种在有源芯片范围之外没有自由电荷载流子的电子组件,自由电荷载流子可能贡献于非线性、损耗和/或隔离限制。示例性实施例可以因此高度地适合于高性能rf器件、rf开关、lna(低噪声放大器)器件和毫米波器件。

67.利用模制或类似模制的膜或层替代常规的绝缘衬底可以减小电子组件的尺寸和制造付出。在对应的电子组件中,半导体管芯或芯片的背部侧可以被覆盖有模制化合物或塑料材料或塑料复合物的膜。所获得的电子组件可以被用作为芯片级别封装而不需要利用封装技术进行进一步处理。然而,还可能的是例如通过包封来封装所获得的电子组件。

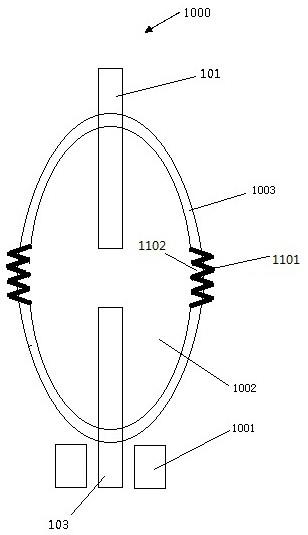

68.图1图示根据示例性实施例的电子组件100的横截面视图。

69.所图示的电子组件100包括作为基底的被构形为膜的模制层102。因此,在此将模制层102体现为模制箔106。裸半导体管芯104被附接在模制箔106的顶部上。半导体管芯104例如可以是硅芯片,并且可以包括低欧姆或较低欧姆的第一部分142和高欧姆或较高欧姆的第二部分144。例如,低(较低)欧姆的第一部分142可以由晶体硅制成。与此相反,高(较高)欧姆的第二部分144可以例如由高电阻硅制成。例如,高欧姆的第二部分144可以具有1kωcm的电阻率。与此相反,低欧姆的第一部分142可以具有显著更低的电阻率,例如10ωcm。

70.如所示出的那样,第一部分142具有有源区域140,其中可以单片集成有一个或多个集成电路元件(图1中未示出)。例如当半导体管芯104被配置用于功率半导体应用时,这样的集成电路元件可以例如是场效应晶体管或二极管。特别是,半导体管芯104可以是有源半导体管芯104,并且可以被配置用于高频应用。

71.第二部分144可以被直接连接到模制层102。然而,如在细节137中示出那样,还可能的是在模制层102和半导体管芯104的第二部分144之间布置粘接层154。如可以从细节137取得的那样,粘接层154可以被夹在模制层102和半导体管芯104之间以用于进一步促进模制层102和裸半导体管芯104之间的粘接。

72.没有单片集成的电路元件被形成在第二部分144中,其因此可以不含有源区域。

73.第二部分144与第一部分142的被直接连接到第二部分144的部分组合,因此构成具有厚度b(例如为略小于25μm)的未经处理的半导体材料。半导体管芯104的整个厚度d可以是例如25μm。低欧姆的第一部分142中的有源区域140的厚度l可以是d

‑

b。更具体地,有源区域140可以例如具有小于1μm(例如150 nm)的厚度l。第二部分144的竖向厚度d2可以大于第一部分142的竖向厚度d1。例如,d2可以是d1的至少10倍。因此,图1的图示不是真实按比例的。

74.在其前侧上,电子组件100包括被构形为层的导电后道工序(beol)结构110。beol结构110可以作为再分配层起作用,并且包括一个或多个电绝缘层141,该一个或多个电绝缘层141在其上和/或在其中具有导电迹线143。特别是,beol结构110可以包括焊盘146。beol结构110可以被直接形成在半导体管芯104的上主表面上。所述上主表面被布置成与半导体管芯104的下主表面相对,该下主表面可以与模制层102直接物理接触,或者可以仅通过粘接层154与模制层102分离开。所述beol结构110可以直接连接到半导体管芯104的有源侧,即有源区域140。

75.如所示出那样,导电突出部111为了连接目的而突出超过beol结构110。这些突出部111中的每个可以包括桩或柱131(例如铜柱)和在柱131的顶部上的可焊接材料(例如agsn或另外的可焊接合金)的焊料帽133。

76.例如,在图1中示出的情形下模制层102可以已经被固化(即可以被完全交联或聚合)。优选地,模制层102的材料被配置从而其在未固化的状态下具有粘接性质。该材料性质简化了在制造处理期间以及在固化之前的模制层102和半导体管芯104之间的连接。

77.如在图1的细节135中示出那样,模制层102可以包括树脂基质150(例如由环氧树脂制成)和嵌入在树脂基质150中的填充物颗粒152。填充物颗粒152可以由金属氧化物(例如氧化铝、氧化钙、氧化镁、氧化锰)、氧化硅和/或陶瓷材料(诸如氮化铝)制成。另外,其它的填充物颗粒152可以被用于调整模制层102的电导率、热导率、热膨胀系数等。

78.例如,在图1中示出的电子组件100可以被如像下面这样使用:其例如可以被表面安装在未示出的印刷电路板(pcb)上。然而,还可能的是包封电子组件100以形成封装120,如例如在图10和图11中示出那样。

79.图2至图9图示在执行根据示例性实施例的制造电子组件100的方法期间获得的结构的横截面视图。

80.参照图2,示出了被完全处理的器件晶片130。晶片130是如下的半导体晶片:其包括被沿着图2的水平方向并排地布置的多个仍然集成连接的半导体管芯104。晶片130被配置为绝缘体上硅(soi)晶片。这意味着晶片130具有其集成连接的半导体管芯104的低欧姆的第一部分142的层。该第一部分142的层由具有相对高的电导率的晶体硅材料制成。此外,晶片130具有集成连接的半导体管芯104的高欧姆的第二部分144的层。该第二部分144的层可以部分地由具有相对低的电导率的非晶硅材料制成。多个半导体管芯104中的每个因此

具有低欧姆的第一部分142和高欧姆的第二部分144,其中第一部分142具有有源区域140。为了说明的目的,图2并未真正按比例地反映各部分142、144的真实的厚度性质。实际上,第一部分142的厚度比第二部分144的厚度小得多(参见关于图1的描述)。

81.此外,第一部分142的层可以通过例如氧化硅层的电绝缘层153与第二部分144的层分离开。因此,晶片130是绝缘体上硅晶片。

82.晶片130包括多个仍然集成连接的半导体管芯104,每个半导体管芯104具有有源区域140,虽然在图2中仅示出一个半导体管芯104。每个半导体管芯104的有源区域140具有被连接到后道工序(beol)结构110的导电焊盘146(在图2中未示出,参见图1)的单片集成的电路元件148(例如晶体管、二极管、rf电路元件等)。每个有源区域140形成所配设的低欧姆的第一部分142的部分,并且可以具有例如在从100 nm到200 nm的范围内的厚度l。

83.beol结构110被提供在半导体晶片130的上主表面上。导电突出部111针对每个仍然集成连接的半导体管芯104而从beol结构110向上突出。

84.为了获得在图3中图示的结构,导电突出部111被嵌入在暂时的粘接结构138中。粘接结构138可以由热塑性粘接剂或uv(紫外辐射)可硬化粘接剂制成,其在表面张力下粘附并且可以稍后被移除而没有残留物。粘接结构138因此可以是非永久粘接。

85.更进一步地,载体晶片132(例如由玻璃制成)被利用在载体晶片132和半导体晶片130之间的粘接结构138而暂时地连接到半导体晶片130。

86.因此,图3图示通过粘接结构138将器件晶片130组装到可复原的载体晶片132。

87.参照图4,在图3中示出的结构被上下颠倒地示出,并且在器件晶片130的暴露的一侧处被薄化。为了获得在图4中示出的结构,通过移除高欧姆的第二部分144的材料的部分来执行半导体晶片130的薄化。在所示出的实施例中,既未移除电绝缘层153的材料也未移除低欧姆的第一部分142的材料。这在细节155中图示。

88.换句话说,图4示出从背部侧将器件晶片130薄化到例如25μm的目标硅厚度d的结果。所述薄化可以是例如通过机械处理和/或化学—机械处理和/或化学湿法蚀刻处理来实现的。

89.参照图5,在此被配置为模制膜或箔106的模制层102被在薄化之后附接到第二部分144的暴露的表面。可以例如通过层压、加压模制、转印模制或使用分离的粘接层(在图5中未示出,对比图1中的参考标记154)的粘接来将模制层102连接到晶片130。

90.因此,模制带或模制箔106被作为背部侧保护箔而组装或安装到晶片130的背部侧。另外,在其它实施例中,代替提供模制箔106而应用模制化合物或者除了提供模制箔106之外还应用模制化合物是可能的。更进一步地,随后可以执行诸如固化和/或退火的进一步的过程。

91.如在图6中示出那样,可能的是将切分箔134暂时地连接到模制层102。在一个实施例中,在已经执行根据图5的处理之后,可以将切分箔134附接到在晶片130上的模制层102。因此,图6图示将切分带或箔134组装或安装到先前已经被连接到器件晶片130的背部管芯保护模制箔106。

92.在另一实施例中,可以是有利地可能的是提供箔106、134作为预制的双箔,其然后被在一个处理中连接到(薄化的)晶片130(未示出)。

93.为了获得在图7中图示的结构,(可选的)载体晶片132可以然后被从半导体晶片

130移除,因为不再需要其作为用于处理的支承。然后还可以优选地在没有残留物的情况下移除非永久的粘接结构138。

94.因此,载体晶片130和粘接结构138可以被分开以用于准备随后的所制造的电子组件100的单体化。

95.参照图8,在模制层102上的半导体晶片130然后可以被分离成多个分离的电子组件100,每个电子组件100包括一个(或多个)半导体管芯104、模制层102的一部分以及beol结构110的一部分以及一个或多个突出部111。例如,所述分离可以是通过激光烧蚀实现的。更一般地,可以通过机械锯切、激光锯切和/或蚀刻来完成单体化。如所示出的那样,切分箔134仍然将单体化的电子组件100保持在一起。

96.因此,图8图示通过机械锯切、激光锯切或者激光锯切/烧蚀和机械锯切的组合来分离各个半导体芯片或管芯104。

97.如在图9中示出那样,然后可能的是例如通过拾取和放置工具(未示出)将电子组件100与切分箔134分开。

98.换句话说,在单体化处理之后可以进行拾取和放置过程,以用于将各个电子组件100带往目的地(例如包封工具),以用于随后创建如在图10或图11中示出的封装120。

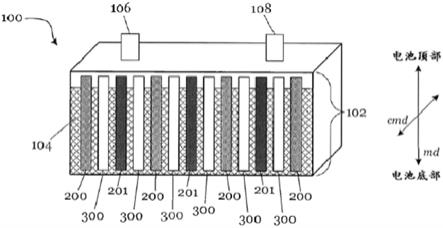

99.图10图示根据示例性实施例的封装120的横截面视图。

100.封装120可以是通过如下获得的:在图8和图9中图示的单体化处理之后利用模制类型的包封物122包封(特别是过模制)电子组件100(其可以是以与在图1或图9中示出的类似的方式构造的)。更具体地,包封物122可以是模制化合物。例如,包封物122可以是通过注入模制、加压模制、转印模制等形成的。

101.所图示的封装120因此包括具有电介质(例如模制)层102和半导体管芯104、以及beol结构110和突出部111的电子组件100。例如,电介质层102由温度可固化的材料制成。半导体管芯104包括晶体硅低欧姆第一部分142和高欧姆的第二部分144,该高欧姆的第二部分144可以由与第一部分142的材料相比具有更低的电导率的硅材料(例如至少部分地晶体、多晶和/或非晶的硅材料)制成。如所示出的那样,第一部分142具有带有单片集成的电路元件148的有源区域140。第二部分144被直接布置在电介质层102上(即在上方或下方)。模制类型的包封物122包封电子组件100以及载体124。一方面的包封物122的模制材料和另一方面的电介质层102的模制材料可以是不同的。

102.如已经提到的那样,封装120包括导电载体124,其可以是引线框类型的,例如被体现为图案化的铜片。替换地,载体124可以是印刷电路板(pcb)、直接铜接合(dcb)衬底、直接铝接合(dab)衬底等。

103.载体124被部分地由包封物122包封,并且是相对于包封物122部分地暴露的。导电连接结构145允许通过焊接将封装120与电子外围设备电连接,例如与封装120可以被安装在其上的安装基底(诸如印刷电路板(pcb),未示出)电连接。更进一步地,通过将电子组件100的突出部111的焊料帽133焊接到被构形为板的载体124的上表面上来将载体124与电子组件100电连接。作为结果,在半导体管芯104的一个主表面上的导电beol结构110被经由突出部111连接到载体124。

104.根据图10的封装120因此可以是基于超薄芯片形成的,在封装中没有载体板而仅具有模制箔106作为微小的支承。

105.图11图示根据另一示例性实施例的封装120的横截面视图。

106.图11的实施例与图10的实施例的不同之处特别是在于,根据图11,电介质层102是由模制板108和模制箔106构成的双模制层。模制箔106被布置在模制板108和半导体管芯104之间。

107.因此,根据图11的封装120可以是基于具有模制箔106和附加的模制板108作为附加支承的超薄芯片形成的。

108.应当注意,术语“包括”不排除其它的元素或特征,并且“一”或“一个”不排除多个。另外,可以组合与不同的实施例相关联地描述的元素。还应当注意,参考符号不应当被解释为限制权利要求的范围。此外,本技术的范围不意图被限制于说明书中描述的处理、机器、制造、物质组成、装置、方法和步骤的特定实施例。因此,所附权利要求意图将这样的处理、机器、制造、物质组成、装置、方法或步骤包括在其范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。