1.本发明实施例涉及显示技术领域,尤其涉及一种驱动电路、显示基板、显示装置及制作方法。

背景技术:

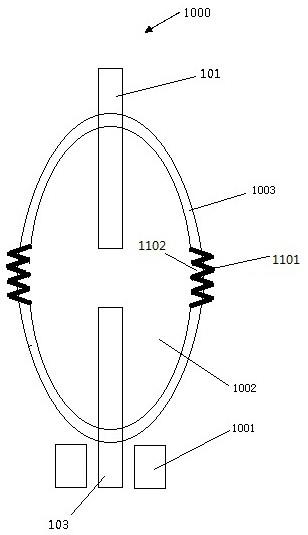

2.oled(有机发光二极管)显示装置的驱动电路包括:开关薄膜晶体管(sw tft)、驱动薄膜晶体管和电容等。请参考图1,为相关技术中的驱动电路的结构示意图,该驱动电路包括开关薄膜晶体管10,请同时参考图2,该开关薄膜晶体管10包括:半导体层11、栅极12、源极(source)13和漏极(drain)14,半导体层11包括:位于栅极12下方的沟道区域,位于栅极12左侧的导体化区域,以及,位于栅极12右侧的导体化区域,从图2中可以看出,位于栅极12左侧的导体化区域存在弯折,在开关薄膜晶体管10的工作过程中,载流子在从漏极14经沟道区域流到源极13的过程中,由于电场作用,载流子不是沿直线进行传输,而是在弯折区进行非直线运动,由于电场的非绝对均匀性,非直线运动的载流子会有发生碰撞的可能性,导致电荷载流子的损失,使得开关薄膜晶体管10的性能降低。

技术实现要素:

3.本发明实施例提供一种驱动电路、显示基板、显示装置及制作方法,用于解决现有的开关薄膜晶体管性能低的问题。

4.为了解决上述技术问题,本发明是这样实现的:

5.第一方面,本发明实施例提供了一种驱动电路,包括:

6.开关薄膜晶体管、驱动薄膜晶体管和电容;

7.所述开关薄膜晶体管包括栅极、半导体层、源极和漏极,所述开关薄膜晶体管的栅极用于与栅线连接,所述源极分别与所述驱动薄膜晶体管的栅极和所述电容连接,所述漏极用于与数据线连接;

8.所述半导体层包括:沟道区域以及位于所述沟道区域两端的第一导体化区域和第二导体化区域,所述沟道区域与所述开关薄膜晶体管的栅极存在交叠,所述第一导体化区域与所述源极存在交叠并连接,所述第二导体化区域与所述漏极存在交叠并连接,所述源极与所述沟道区域之间的所述第一导体化区域呈直线型或者大致呈直线型。

9.可选的,所述源极与所述沟道区域之间的所述第一导体化区域与所述数据线平行或大致平行。

10.可选的,整个所述第一导体化区域呈直线型或者大致呈直线型。

11.可选的,所述源极与所述沟道区域之间的所述第一导体化区域的长度,小于所述漏极与所述沟道区域之间的第二导体化区域的长度。

12.可选的,所述漏极与所述沟道区域之间的所述第二导体化区域呈l型,包括第一部分和第二部分,所述第一部分一端与所述沟道区域连接,另一端与所述第二部分连接,所述第二部分与所述开关薄膜晶体管的漏极存在交叠并连接。

13.可选的,所述第一部分与所述数据线平行或大致平行,所述第二部分与所述栅线平行或大致平行。

14.可选的,所述开关薄膜晶体管的栅极包括第三部分和第四部分,所述第三部分与所述栅线平行或大致平行,所述第三部分与所述开关薄膜晶体管的沟道区域存在交叠,所述第四部分的一端与所述第三部分连接,另一端与所述栅线连接。

15.可选的,所述第三部分和第四部分相互垂直,形成l型。

16.第二方面,本发明实施例提供了一种显示基板,包括上述第一方面所述的驱动电路。

17.第三方面,本发明实施例提供了一种显示装置,包括上述第二方面所述的显示基板。

18.第四方面,本发明实施例提供了一种驱动电路的制作方法,包括:

19.形成开关薄膜晶体管、驱动薄膜晶体管和电容;

20.所述开关薄膜晶体管包括栅极、半导体层、源极和漏极,所述开关薄膜晶体管的栅极用于与栅线连接,所述源极分别与所述驱动薄膜晶体管的栅极和所述电容连接,所述漏极用于与数据线连接;

21.所述半导体层包括:沟道区域以及位于所述沟道区域两端的第一导体化区域和第二导体化区域,所述沟道区域与所述开关薄膜晶体管的栅极存在交叠,所述第一导体化区域与所述源极存在交叠并连接,所述第二导体化区域与所述漏极存在交叠并连接,所述源极与所述沟道区域之间的所述第一导体化区域呈直线型或者大致呈直线型。

22.可选的,所述源极与所述沟道区域之间的所述第一导体化区域与所述数据线平行或大致平行。

23.可选的,整个所述第一导体化区域呈直线型或者大致呈直线型。

24.可选的,所述源极与所述沟道区域之间的所述第一导体化区域的长度,小于所述漏极与所述沟道区域之间的第二导体化区域的长度。

25.在本发明实施例中,源极与沟道区域之间的第一导体化区域呈直线型或者大致呈直线型,使载流子在从漏极经沟道区域流到源极的过程中沿直线进行传输,减少载流子发生碰撞的可能性,提高开关薄膜晶体管的性能。

附图说明

26.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

27.图1为相关技术中的驱动电路的结构示意图;

28.图2为图1中的驱动电路的局部放大示意图;

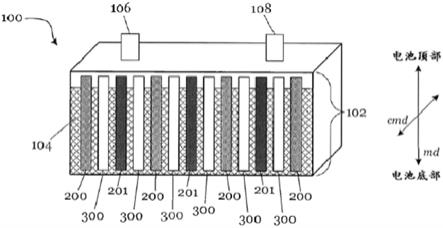

29.图3为本发明实施例的驱动电路的电路原理示意图;

30.图4为本发明实施例的驱动电路的结构示意图;

31.图5为图4中的驱动电路的局部放大示意图;

32.图6

‑

图11为本发明实施例中的显示基板的制作方法示意图。

具体实施方式

33.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

34.请参考图3和图4,本发明实施例提供一种驱动电路,包括:开关薄膜晶体管t2、驱动薄膜晶体管t1和电容c。

35.请同时参考图5,所述开关薄膜晶体管t2包括栅极102、半导体层101、源极103和漏极104,所述开关薄膜晶体管的栅极102用于与栅线连接,所述源极103分别与所述驱动薄膜晶体管t1的栅极和所述电容c连接,所述漏极104用于与数据线data连接;

36.所述半导体层101包括:沟道区域1011(位于栅极102下方)以及位于所述沟道区域1011两端的第一导体化区域1012和第二导体化区域1013,所述沟道区域1011与所述开关薄膜晶体管t2的栅极102存在交叠,所述第一导体化区域1012与所述源极103存在交叠并连接,所述第二导体化区域1013与所述漏极104存在交叠并连接,所述源极103与所述沟道区域1011之间的所述第一导体化区域1012呈直线型或者大致呈直线型。

37.在本发明实施例中,源极103与沟道区域1011之间的第一导体化区域1012呈直线型或者大致呈直线型,使载流子在从漏极104经沟道区域1011流到源极103的过程中沿直线进行传输,减少载流子发生碰撞的可能性,提高开关薄膜晶体管t2的性能。

38.本发明实施例中,可选的,请参考图5,所述源极103与所述沟道区域1011之间的所述第一导体化区域1012与所述数据线data平行或大致平行,以方便构图。

39.本发明实施例中,可选的,请参考图5,整个所述第一导体化区域1012(包括被源极103覆盖的部分,以及,源极103与沟道区域1011之间的部分)呈直线型或者大致呈直线型,从而进一步有利于载流子的传输。

40.请参考图2,相关的开关薄膜晶体管10中,源极13到沟道区域的距离较长,即沟道区域左侧的导体化区域的距离较长,导致电阻会稍大,从而导致源极13端电阻较大,也会造成源极13端的电学性能损失。

41.为解决上述问题,本发明实施例中,可选的,请参考图5,所述源极103与所述沟道区域之间的所述第一导体化区域1012的长度,小于所述漏极104与所述沟道区域1011之间的第二导体化区域1013的长度,该种结构下,源极103与所述沟道区域之间的所述第一导体化区域1012的距离较短,有利于减少源极103的电阻,从而有利于提高开关薄膜晶体管t2的性能。

42.需要说明的是,本发明实施例中,源极103与沟道区域1011之间,是指源极103靠近沟道区域1011的边界与沟道区域1011之间,漏极104与沟道区域1011之间,是指漏极104靠近沟道区域1011的边界与沟道区域1011之间。

43.本发明实施例中,可选的,请参考图5,所述漏极104与所述沟道区域1011之间的所述第二导体化区域1013呈l型,包括第一部分和第二部分,所述第一部分一端与所述沟道区域1011连接,另一端与所述第二部分连接,所述第二部分与所述开关薄膜晶体管t2的漏极103存在交叠并连接,由于漏极104直接与数据线data连接,可以直接输入电压,因而,即使所述漏极104与所述沟道区域1011之间的所述第二导体化区域1013呈弯折型,对漏极104端

的电学性能也影响较小。

44.本发明实施例中,可选的,请参考图5,所述第二导体化区域1013的第一部分与所述数据线data平行或大致平行,所述第二导体化区域1013的第二部分与所述栅线gate平行或大致平行,该种结构有利于构图。

45.本发明实施例中,可选的,请参考图5,所述开关薄膜晶体管t2的栅极102包括第三部分和第四部分,所述第三部分与所述栅线gate平行或大致平行,所述第三部分与所述开关薄膜晶体管t2的沟道区域1011存在交叠,所述第四部分的一端与所述第三部分连接,另一端与所述栅线gate连接。通过将开关薄膜晶体管t2的栅极102设置成部分与栅线gate并行,从而可以将半导体层101分割呈三部分(沟道区域1011、第一导体化区域1012和第二导体化区域1013),分割后的第一导体化区域1012呈直线型或者大致呈直线型,从而有利于载流子的传输。

46.本发明实施例中,可选的,所述栅极的第三部分和第四部分相互垂直,形成l型,从而有利于构图。

47.本发明实施例中,可选的,所述开关薄膜晶体管t2的栅极与栅线gate同层同材料设置。

48.进一步,可选的,所述开关薄膜晶体管t2的栅极、所述驱动薄膜晶体管t1的栅极均与栅线gate同层同材料设置。

49.本发明实施例中,可选的,所述开关薄膜晶体管t2的源极103和漏极104与数据线data同层同材料设置。

50.进一步,可选的,所述开关薄膜晶体管t2的源极103和漏极104、所述驱动薄膜晶体管t1的源极和漏极,均与数据线data同层同材料设置。

51.本发明实施例中,可选的,所述电容c的第一极板,与所述开关薄膜晶体管t2的半导体层、所述驱动薄膜晶体管t1的半导体层,同层同材料设置。

52.本发明实施例中的上述驱动电路可以应用于oled,lcd,qled(quantum dot light emitting diodes,量子点发光二极管),micro led等显示装置中。

53.本发明实施例还提供一种显示基板,包括上述任一实施例中的驱动电路。

54.本发明实施例还提供一种显示装置,包括上述显示基板。

55.本发明实施例还提供一种驱动电路的制作方法,包括:

56.步骤s11:形成开关薄膜晶体管、驱动薄膜晶体管和电容;

57.所述开关薄膜晶体管包括栅极、半导体层、源极和漏极,所述开关薄膜晶体管的栅极用于与栅线连接,所述源极分别与所述驱动薄膜晶体管的栅极和所述电容连接,所述漏极用于与数据线连接;

58.所述半导体层包括:沟道区域以及位于所述沟道区域两端的第一导体化区域和第二导体化区域,所述沟道区域与所述开关薄膜晶体管的栅极存在交叠,所述第一导体化区域与所述源极存在交叠并连接,所述第二导体化区域与所述漏极存在交叠并连接,所述源极与所述沟道区域之间的所述第一导体化区域呈直线型或者大致呈直线型。

59.可选的,所述源极与所述沟道区域之间的所述第一导体化区域与所述数据线平行或大致平行。

60.可选的,整个所述第一导体化区域呈直线型或者大致呈直线型。

61.可选的,所述源极与所述沟道区域之间的所述第一导体化区域的长度,小于所述漏极与所述沟道区域之间的第二导体化区域的长度。

62.请参考图6

‑

图11,为本发明一实施例的显示基板的制作方法的流程示意图,该制作方法包括:

63.步骤s21:请参考图6,形成不透光层201和透明导电层202的图形,其中,透明导电层的图形包括驱动电路中的电容c的一个极板;不透光层包括遮光层(shield)和走线,遮光层用于遮挡驱动薄膜晶体管的沟道区域,不透光层可以采用金属等材料形成,透明导电层可以采用ito等透明氧化物材料形成。

64.步骤s22:请参考图7,形成半导体层203的图形,本发明实施例中,半导体层203可以采用igzo等材料制成,在形成半导体层203的图形之后,还需要对除沟道区域之外的区域进行导体化。

65.需要说明的是,在形成半导体层203的图形之前还需要形成相关的绝缘层,步骤和图中为方便说明未示出。

66.步骤s23:请参考图8,形成栅金属层204的图形,栅金属层204的图形包括:开关薄膜晶体管的栅极、驱动薄膜晶体管的栅极、栅线等。

67.需要说明的是,在形成栅金属层204的图形之前还需要形成栅绝缘层,步骤和图中为方便说明未示出。

68.步骤s24:请参考图9,进行连接孔cnt的制备。即在栅绝缘层上形成连接孔cnt;

69.步骤s25:请参考图10,形成层间介质层(ild)的图形,层间介质层包括多个过孔;

70.步骤s26:请参考图11,形成源漏金属层(sd)205的图形。

71.上面结合附图对本发明的实施例进行了描述,但是本发明并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本发明的启示下,在不脱离本发明宗旨和权利要求所保护的范围情况下,还可做出很多形式,均属于本发明的保护之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。